## Si4133G RF Synthesizer for GSM/GPRS

DUAL-BAND RF FREQUENCY SYNTHESIZER WITH INTEGRATED VCOs FOR WIRELESS COMMUNICATIONS

### **PRODUCT DESCRIPTION**

The Si4133G is a monolithic integrated circuit that provides IF and dual-band, low-noise RF synthesis for GSM/DCS1800/PCS1900 applications. The unprecedented level of integration of the Si4133G addresses price-sensitive, low-power, high-performance requirements for personal wireless communications by substantially reducing external passive component count, eliminating external VCOs and varactor diodes, while also improving power efficiency. The highly integrated design generates a stable, low phase noise output by incorporating a proprietary self-tuning architecture that does not require external adjustments or laser trimming for component-tolerance matching.

The Si4133G has been optimized for GPRS (General Packet Radio Services) applications with industry leading settling times required for multi-slot data communications. Using an integer-N Phase Locked Loop (PLL), the Si4133G settles to 0.1 ppm frequency error in 140 µsec. The settling time of the synthesizer remains consistent even when hopping from one end of the synthesizable tuning range to the other.

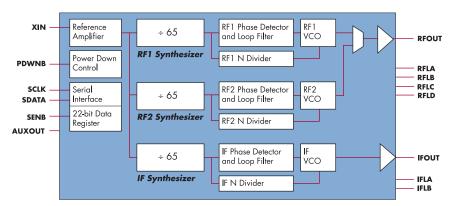

Unlike traditional approaches, the Si4133G includes three voltage-controlled oscillators, loop filters, reference and VCO dividers, and phase detectors. Channel selection and power-down settings are programmable through a three wire serial interface.

The Si4133G-X2 is a derivative of the Si4133G that has been optimized for use with the Hitachi BRIGHT transceiver family. Both versions come standard in a low-profile, small outline, 24-pin package (TSSOP) or 28-lead micro leadframe package (MLP).

## Si4133G RF Synthesizer Block Diagram

### **FEATURES**

- Dual-Band RF Synthesizers RF1: 900 MHz to 1.8 GHz RF2: 750 MHz to 1.5 GHz

- IF Synthesizer

IF: 500 MHz to 1.0 GHz

- Settling time 140 µsec for multi-slot data applications (GPRS classes 1–12)

- Dual synthesizer and single synthesizer derivatives available

- Fully integrated VCOs, loop filters, varactors and resonators

- Programmable power down modes

- Low integrated phase error 0.9 deg RMS

- 1 µA standby current

- 18 mA supply current

- 2.7 V to 3.6 V operation

- 0.35µ CMOS

## **APPLICATIONS**

- Triple-band GSM/DCS1800/PCS1900 handsets

- GPRS-capable handsets and data terminals

- HSCSD data terminals

- Wireless communications

## **PRODUCT BRIEF**

ENABLING THE GSM AND GPRS

MARKETS WITH A NEW STANDARD

IN SYNTHESIZER INTEGRATION

AND PERFORMANCE.

# INNOVATIVE DESIGN FOR FAST LOCK TIMES AND LOW POWER

The Si4133G uses a proprietary architecture that not only results in fast settling times, but also significantly reduces power consumption in a cellular handset. Lock times of 140 µsec (with a 200 kHz phase detector update rate) provide designers with a state of the art synthesis engine required for today's demanding GSM/GPRS requirements. Faster settling times also allow the system to wait longer before turning on the receiver, resulting in significant power savings and extended standby battery life. The integration of all the components of the frequency synthesis function into a monolithic CMOS device allows the designer to achieve greater control over the power consumption of the entire functional block with one control interface. With active consumption of 18 mA from a 3V supply, the Si4133G sets a new standard in power efficiency.

### **DEVELOPMENT TOOLS**

Design engineers can order the Si4133G-EVB or one of the derivative evaluation board kits. The kit provides an evaluation system of device performance using industry standard test equipment. The evaluation kit also includes software that completely automates device configuration and the test function from a standard PC.

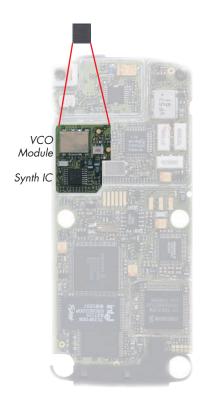

## 84% Area Reduction / 33% Cost Savings

The Si4133G dramatically reduces the number of components required to implement a complete dual-band RF frequency synthesizer function for wireless communications. This unprecedented level of integration can reduce board space by as much as 84% over traditional frequency synthesizer architectures using a dual-band frequency synthesizer IC, external VCOs, varactor diodes and up to 35 additional passive components. Designers can realize cost reductions of 33% over traditional solutions by designing with the Si4133G. The robustness and consistency of an integrated solution improves ease of manufacture and lowers test and assembly costs for high volume wireless applications.

| Traditional Solution          | 41                            | 402 mm <sup>2</sup> | 2 mm   |

|-------------------------------|-------------------------------|---------------------|--------|

| Silicon Laboratories Solution | 4                             | 64 mm <sup>2</sup>  | 1 mm   |

|                               | Number of Discrete Components | 101017 1100         | Height |

| SIZE COMPARISON               |                               |                     |        |

## **CONTACT INFORMATION**

### Silicon Laboratories Inc.

4635 Boston Lane • Austin, TX 78735

Toll Free: 1 (877) 444-3032 Email: RFinfo@silabs.com Web site: www.silabs.com

Silicon Laboratories and the Silicon Laboratories logos are trademarks of Silicon Laboratories Inc.

PB:Si4133G: MRT-8.000-11/00

### ORDERING INFORMATION

| Product*     | Description            |

|--------------|------------------------|

| Si4133G      | RF1/RF2/IF Synthesizer |

| Si4123G      | RF1/IF Synthesizer     |

| Si4122G      | RF2/IF Synthesizer     |

| Si4113G      | RF-Only Synthesizer    |

| Si4133G-X2** | RF1/RF2/IF Synthesizer |

**Data Sheets**

Si4133G-DS Si4133G Product Family Data Sheet (includes Si4133G/23G/22G/13G)

Si4133GX2-DS\*\* Si4133G-X2 Data Sheet

Si4133/36-EVB-DS Si4133G Evaluation Board Data Sheet

**Evaluation Boards\***

Si4133G-EVB Si4133G Evaluation Board Kit

Si4133GX2-EVB\*\* Si4133G-X2 Evaluation Board Kit

\* Available in either 24-pin TSSOP or 28-lead MLP

\*\* Optimized for use with Hitachi BRIGHT 2+ transceiver