# **Contents**

| Features                                       | . 1 |

|------------------------------------------------|-----|

| Pin Assignment                                 | . 1 |

| Block Diagram                                  | . 2 |

| Instruction Set                                | . 2 |

| Absolute Maximum Ratings                       | . 2 |

| Recommended Operating Conditions               | . 3 |

| DC Electrical Characteristics                  | . 3 |

| Endurance                                      | . 3 |

| Pin Capacitance                                | . 3 |

| AC Electrical Characteristics                  | . 4 |

| Operation                                      | . 5 |

| Receiving a Start-Bit                          | . 7 |

| Three-wire Interface (DI-DO direct connection) | . 7 |

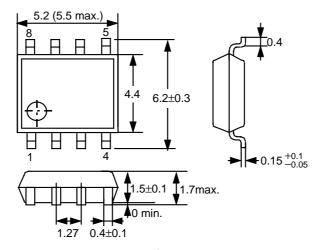

| Dimensions (Unit: mm)                          | . 8 |

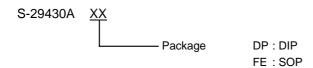

| Ordering Information                           | . 8 |

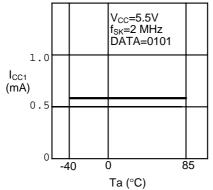

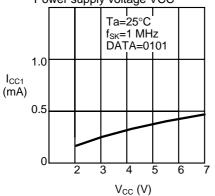

| Charcteristics                                 | . 9 |

| Frequently Asked Questions                     | .13 |

CMOS SERIAL E<sup>2</sup>PROM S-29430A

The S-29430A is high speed, low power 8K-bit serial E<sup>2</sup>PROM with a wide operating voltage range. It is organized as 512-word×16-bit. It is capable of sequential read, where addresses are automatically incremented in 16-bit blocks. The instruction code is compatible with the NM93C Series.

#### Features

Low power consumption Standby : 1 μA Max.

Operating : 1.2 mA Max. ( $V_{CC}$ =5.5 V)

: 0.4 mA Max. (V<sub>CC</sub>=2.5 V)

Wide operating voltage range Write: 2.5 to 5.5 V Read: 1.8 to 5.5 V

• Sequential read capable

# Endurance : 10<sup>5</sup> cycles/word Data retention : 10 years

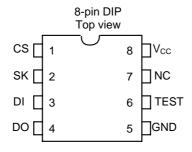

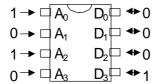

## ■ Pin Assignment

Figure 1

| CS       | Chip select input                |

|----------|----------------------------------|

| SK       | Serial clock input               |

| DI       | Serial data input                |

| DO       | Serial data output               |

| GND      | Ground (0 V)                     |

| $V_{CC}$ | Power supply                     |

| TEST     | Test pin (normally kept open)    |

|          | (can be connected to GND or Vcc) |

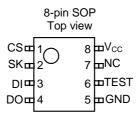

## ■ Block Diagram

■ Instruction Set

Table 1

| Instruction            | Start<br>Bit | Ope<br>code | Address                           | Data                                |

|------------------------|--------------|-------------|-----------------------------------|-------------------------------------|

| READ (Read data)       | 1            | 10          | XA <sub>8</sub> to A <sub>0</sub> | D <sub>15</sub> to D <sub>0</sub> * |

| WRITE (Write data)     | 1            | 01          | XA <sub>8</sub> to A <sub>0</sub> | D <sub>15</sub> to D <sub>0</sub>   |

| ERASE (Erase data)     | 1            | 11          | XA <sub>8</sub> to A <sub>0</sub> | _                                   |

| EWEN (Program enable)  | 1            | 00          | 11xxxxxxxx                        | _                                   |

| EWDS (Program disable) | 1            | 00          | 00xxxxxxx                         | _                                   |

x: Doesn't matter.

When 16-bit data of the specified address is output, the data of the next address is output.

## ■ Absolute Maximum Ratings

Table 2

| Parameter                      | Symbol            | Ratings                      | Unit     |

|--------------------------------|-------------------|------------------------------|----------|

| Power supply voltage           | V <sub>CC</sub>   | -0.3 to +7.0                 | V        |

| Input voltage                  | $V_{IN}$          | -0.3 to V <sub>CC</sub> +0.3 | <b>V</b> |

| Output voltage                 | V <sub>OUT</sub>  | -0.3 to V <sub>CC</sub>      | <b>V</b> |

| Storage temperature under bias | T <sub>bias</sub> | -50 to +95                   | °C       |

| Storage temperature            | T <sub>sta</sub>  | -65 to +150                  | °C       |

# **■** Recommended Operating Conditions

Table 3

| Parameter                 | Symbol          | Conditions                   | Min.                | Тур. | Max.                 | Unit |

|---------------------------|-----------------|------------------------------|---------------------|------|----------------------|------|

| Dower ownship wolfors     | \ <i>I</i>      | Read Operation               | 1.8                 |      | 5.5                  | V    |

| Power supply voltage      | V <sub>CC</sub> | Write Operation              | 2.5                 |      | 5.5                  | V    |

| Lligh lovel input valtage | \/              | V <sub>CC</sub> =2.5 to 5.5V | 0.8×V <sub>CC</sub> |      | V <sub>CC</sub>      | V    |

| High level input voltage  | $V_{IH}$        | V <sub>CC</sub> =1.8 to 2.5V | 0.8×V <sub>CC</sub> | _    | V <sub>CC</sub>      | V    |

| Low level input voltage   |                 | V <sub>CC</sub> =2.5 to 5.5V | 0.0                 |      | 0.2×V <sub>CC</sub>  | V    |

| Low level input voltage   | V <sub>IL</sub> | V <sub>CC</sub> =1.8 to 2.5V | 0.0                 |      | 0.15×V <sub>CC</sub> | V    |

| Operating temperature     | $T_{opr}$       |                              | -40                 |      | +85                  | °C   |

## ■ DC Electrical Characteristics

## Table 4

|                               |                  |             |      | V <sub>CC</sub> =5.0 V±10 % |      |      | V <sub>CC</sub> =2.5 to 3.3 V |      |      | V <sub>CC</sub> =1.8 to 2.5 V |      |      |

|-------------------------------|------------------|-------------|------|-----------------------------|------|------|-------------------------------|------|------|-------------------------------|------|------|

| Parameter                     | Symbol           | Conditions  | Min. | Тур.                        | Max. | Min. | Тур.                          | Max. | Min. | Тур.                          | Max. | Unit |

| Current consumption (READ)    | I <sub>CC1</sub> | DO unloaded | _    |                             | 1.2  |      |                               | 0.5  |      |                               | 0.4  | mA   |

| Current consumption (PROGRAM) | I <sub>CC2</sub> | DO unloaded | _    | _                           | 5.0  | _    | _                             | 2.0  | _    | _                             | _    | mA   |

## Table 5

| _                                    |                 |                                                                                                     | V <sub>CC</sub> =5   | .0 V±1 | 0 %  | V <sub>CC</sub> =2.5 to 4.5 V |      |      | V <sub>CC</sub> =1.8 to 2.5 V |      |      |      |

|--------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|----------------------|--------|------|-------------------------------|------|------|-------------------------------|------|------|------|

| Parameter                            | Symbol          | Conditions                                                                                          | Min.                 | Тур.   | Max. | Min.                          | Тур. | Max. | Min.                          | Тур. | Max. | Unit |

| Standby current consumption          | I <sub>SB</sub> | Input: V <sub>CC</sub> or GND                                                                       | _                    |        | 1.0  |                               |      | 1.0  | _                             |      | 1.0  | μΑ   |

| Input leakage current                | ILI             | V <sub>IN</sub> =GND to V <sub>CC</sub>                                                             | _                    | 0.1    | 1.0  | _                             | 0.1  | 1.0  | _                             | 0.1  | 1.0  | μΑ   |

| Output leakage current               | I <sub>LO</sub> | $V_{OUT}$ =GND to $V_{CC}$                                                                          | _                    | 0.1    | 1.0  | _                             | 0.1  | 1.0  | _                             | 0.1  | 1.0  | μΑ   |

| Low level output                     | .,              | CMOS I <sub>OL</sub> =100 μA                                                                        |                      |        | 0.1  |                               |      | 0.1  |                               | _    | 0.1  | V    |

| voltage                              | V <sub>OL</sub> | TTL I <sub>OL</sub> =2.1 mA                                                                         |                      | _      | 0.45 |                               |      | _    |                               | _    |      | V    |

| High level output voltage            | V <sub>OH</sub> | CMOS $V_{CC}$ =2.5 to 5.5 V $: I_{OH}$ =-100 $\mu$ A $V_{CC}$ =1.8 to 2.5 V $: I_{OH}$ =-10 $\mu$ A | V <sub>CC</sub> -0.7 |        | _    | V <sub>CC</sub> -0.7          |      | _    | V <sub>CC</sub> -0.3          |      |      | V    |

|                                      |                 | TTL, I <sub>OH</sub> =-400 μA                                                                       | 2.4                  | _      | _    | _                             | _    | _    | _                             | _    | _    | V    |

| Write enable latch data hold voltage | $V_{DH}$        |                                                                                                     | 1.5                  | _      |      | 1.5                           |      |      | 1.5                           | _    |      | ٧    |

## **■** Endurance

## Table 6

| Parameter | Symbol         | Min.            | Тур. | Max. | Unit        |

|-----------|----------------|-----------------|------|------|-------------|

| Endurance | N <sub>W</sub> | 10 <sup>5</sup> |      |      | cycles/word |

## ■ Pin Capacitance

## Table 7

(Ta=25°C, f=1.0 MHz, V<sub>CC</sub>=5 V)

|                    |                  |                       | (1u- | -20 0, 1- | 1.0 1411 12, | VCC-0 V) |

|--------------------|------------------|-----------------------|------|-----------|--------------|----------|

| Parameter          | Symbol           | Conditions            | Min. | Тур.      | Max.         | Unit     |

| Input Capacitance  | C <sub>IN</sub>  | V <sub>IN</sub> =0 V  |      |           | 8            | pF       |

| Output Capacitance | C <sub>OUT</sub> | V <sub>OUT</sub> =0 V | _    |           | 10           | pF       |

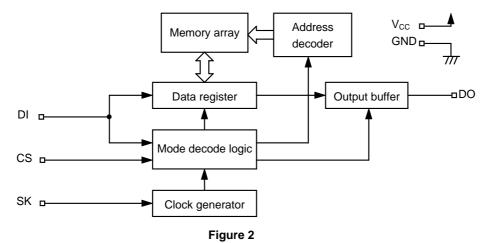

## ■ AC Electrical Characteristics

**Table 8 Measuring conditions**

| Input pulse voltage      | 0.1×V <sub>CC</sub> to 0.9×V <sub>CC</sub> |

|--------------------------|--------------------------------------------|

| Output reference voltage | 0.5×V <sub>CC</sub>                        |

| Output load              | 100pF                                      |

Table 9

|                          |                                     |                   | Read/Write operations                                     |      |      |       |                        |      | Read operation |      |     |

|--------------------------|-------------------------------------|-------------------|-----------------------------------------------------------|------|------|-------|------------------------|------|----------------|------|-----|

| Parameter                | Symbol                              | V <sub>CC</sub> = | V <sub>CC</sub> =5.0 V±10 % V <sub>CC</sub> =2.5 to 4.5 V |      |      | 4.5 V | $V_{CC}$ =1.8 to 2.5 V |      |                | Unit |     |

|                          |                                     | Min.              | Тур.                                                      | Max. | Min. | Тур.  | Max.                   | Min. | Тур.           | Max. |     |

| CS setup time            | t <sub>CSS</sub>                    | 0.2               | _                                                         |      | 0.4  | _     | _                      | 1.0  | _              | _    | μs  |

| CS hold time             | t <sub>CSH</sub>                    | 0.2               | _                                                         |      | 0.4  | _     | _                      | 1.0  | _              |      | μs  |

| CS setup time (CPU)      | t <sub>CSS (CPU)</sub>              | 0.2               | _                                                         |      | 0.4  | _     |                        | 1.0  | _              |      | μs  |

| CS hold time (CPU)       | t <sub>CSH (CPU)</sub>              | 0.2               | _                                                         |      | 0.4  | _     |                        | 1.0  | _              |      | μs  |

| CS deselect time         | t <sub>CDS</sub>                    | 0.2               | _                                                         |      | 0.2  | _     |                        | 0.4  | _              |      | μs  |

| Data setup time          | t <sub>DS</sub>                     | 0.2               | _                                                         |      | 0.4  | _     |                        | 0.8  | _              |      | μs  |

| Data hold time           | t <sub>DH</sub>                     | 0.2               |                                                           | _    | 0.4  |       | _                      | 0.8  |                | _    | μs  |

| 1 data output delay time | t <sub>PD1</sub>                    | _                 | _                                                         | 0.4  |      | _     | 8.0                    |      | _              | 2.0  | μs  |

| 0 data output delay time | t <sub>PD0</sub>                    | _                 | _                                                         | 0.4  |      | _     | 8.0                    |      | _              | 2.0  | μs  |

| Clock frequency          | f <sub>SK</sub>                     | 0.0               | _                                                         | 2.0  | 0.0  | _     | 0.5                    | 0.0  | _              | 0.2  | MHz |

| Clock pulse width        | t <sub>SKH</sub> , t <sub>SKL</sub> | 0.25              | _                                                         |      | 1.0  | _     |                        | 2.5  | _              |      | μs  |

| Output disable time      | $t_{HZ1}, t_{HZ2}$                  | 0                 | 50                                                        | 150  | 0    | 500   | 1000                   |      |                |      | ns  |

| Output enable time       | t <sub>SV</sub>                     | 0                 | 50                                                        | 150  | 0    | 500   | 1000                   |      |                | _    | ns  |

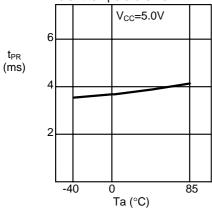

| Programming time         | t <sub>PR</sub>                     | _                 | 4.0                                                       | 10   |      | 4.0   | 10                     |      | _              |      | ms  |

Input data is retrieved on the rising edge of SK.

Output data is triggered on the rising edge of SK.

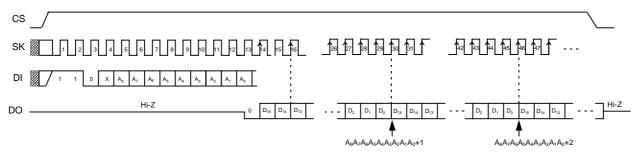

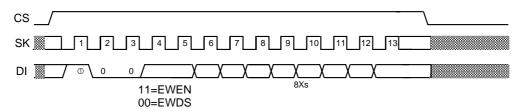

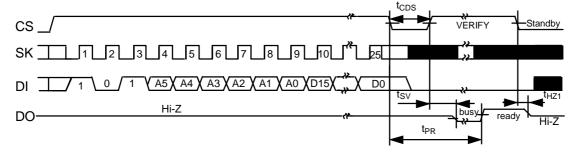

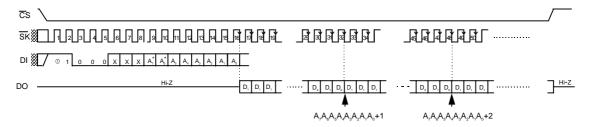

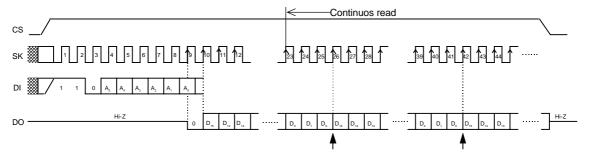

Figure 3 Timing Chart

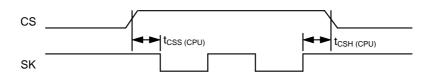

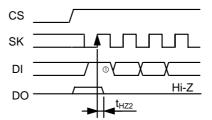

Figure 4 Timing Chart for  $t_{\text{CSS (CPU)}}$  and  $t_{\text{CSH (CPU)}}$  when CPU is connected

#### Operation

Instructions (in the order of start-bit, instruction, address, and data) are latched to DI in synchronization with the rising edge of SK after CS goes high. A start-bit can only be recognized when the high of DI is latched at the rising edge of SK after changing CS to high, it is impossible for it to be recognized as long as DI is low, even if there are SK pulses after CS goes high. Any SK pulses input while DI is low before receiving a start-bit are called "dummy clocks." The number of clocks transmitted by the serial interface in a CPU and the number of clocks needed for operation of the serial memory IC can be adjusted by inserting several dummy clocks before a start-bit. Instruction finishes when CS goes low, where it must be low between commands during tcds.

All input, including DI and SK signals, is ignored while CS is low.

#### 1. Read

The READ instruction reads data from a specified address. After A0 is latched at the rising edge of SK, DO output changes from a high-impedance state (Hi-Z) to low level output. 16-bit data is continuously output in synchronization with the rise of SK.

When all of the data ( $D_{15}$  to  $D_0$ ) in the specified address has been read, addresses are automatically incremented and the data in the next address can be read with the input of another SK clock. Thus, the data over whole area of the memory can be read by continuously inputting SK clocks as long as CS is high.

The last address (An  $\cdots$  A1 A0 = 1  $\cdots$  11) rolls over to the top address (An  $\cdots$  A1 A0 = 0  $\cdots$  00).

X : Optional

Figure 5 Read Timing

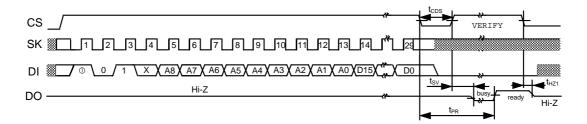

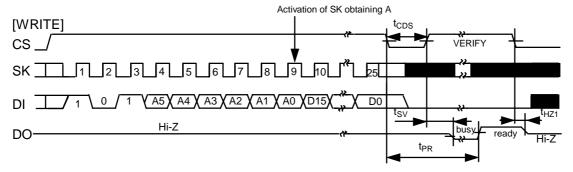

#### 2. Write (WRITE, ERASE)

There are two write instructions, WRITE, ERASE. Each automatically begins writing to the non-volatile memory when CS goes low at the completion of the specified clock input.

The write operation is completed in 10 ms ( $t_{PR}$  Max.), and the typical write period is less than 5 ms. In the S-29430A Series, it is easy to VERIFY the completion of the write operation in order to minimize the write cycle by setting CS to "H" and checking the DO pin after the write operation begins by setting CS to "L." VERIFY operations to detect changes in the DO output can be executed in succession. One is a change from "L" to "H" with CS="H." The other is a change from "L" to "H" after setting CS to "H" and returning CS to "L" repeatedly.

Because all SK and DI inputs are ignored during the write operation, any input of instruction will also be disregarded. When DO outputs high after completion of the write operation or if it is in the high-impedence state (Hi-Z), the input of instructions is available. Even if the DO pin remains high, it will enter the high-impedence state upon the recognition of a high of DI (start-bit) attached to the rising edge of an SK pulse.

#### 2.1 WRITE

This instruction writes 16-bit data to a specified address.

After changing CS to high, input a start-bit, op-code (WRITE), address, and 16-bit data. If there is a data overflow of more than 16 bits, only the last 16-bits of the data is considered valid. Changing CS to low will start the WRITE operation. It is not necessary to make the data "1" before initiating the WRITE operation.

Figure 6 WRITE Timing

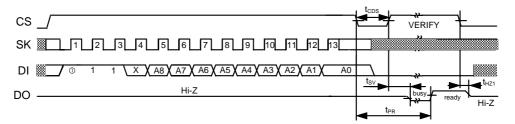

#### 2.2 ERASE

This command erases 16-bit data in a specified address.

After changing CS to high, input a start-bit, op-code (ERASE), and address. It is not necessary to input data. Changing CS to low will start the ERASE operation, which changes every bit of the 16 bit data to "1."

Figure 7 ERASE Timing

## 3. Write enable (EWEN) and Write disable (EWDS)

The EWEN instruction puts the S-29430A into write enable mode, which accepts WRITE, ERASE instructions. The EWDS instruction puts the S-29430A into write disable mode, which refuses WRITE, ERASE instructions.

The S-29430A powers on in write disable mode, which protects data against unexpected, erroneous write operations caused by noise and/or CPU malfunctions. It should be kept in write disable mode except when performing write operations.

Figure 8 EWEN/EWDS Timing

## ■ Receiving a Start-Bit

A start-bit can be recognized by latching the high level of DI at the rising edge of SK after changing CS to high (Start-Bit Recognition). The write operation begins by inputting the write instruction and setting CS to low. The DO pin then outputs low during the write operation and high at its completion by setting CS to high (Verify Operation). Therefore, only after a write operation, in order to accept the next command by having CS go high, the DO pin is switched from a state of high-impedance to a state of data output; but if it recognizes a start-bit, the DO pin returns to a state of high-impedance (see Figure 9).

Make sure that data output from the CPU does not interfere with the data output from the serial memory IC when you configure a 3-wire interface by connecting DI input pin and DO output pin. Such interference may cause a start-bit fetch problem.

Figure 9 Start bit latching timing

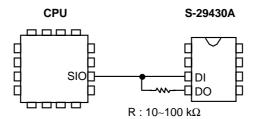

#### ■ Three-wire Interface (DI-DO direct connection)

Although the normal configuration of a serial interface is a 4-wire interface to CS, SK, DI, and DO, a 3-wire interface is also a possibility by connecting DI and DO. However, since there is a possibility that the DO output from the serial memory IC will interfere with the data output from the CPU with a 3-wire interface, install a resistor between DI and DO in order to give preference to data output from the CPU to DI (See Figure 10).

Figure 10 3-wire interface

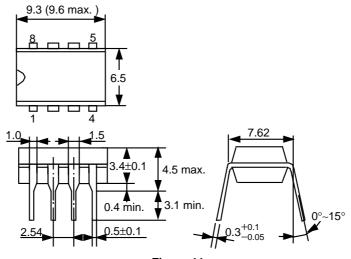

## ■ Dimensions (Unit: mm)

## 1. 8-pin DIP

Figure 11

## 2. 8-pin SOP

Figure 12

# Ordering Information

## **■** Characteristics

- 1. DC Characteristics

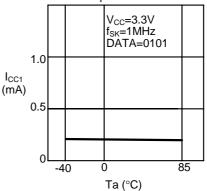

- Current consumption (READ) I<sub>CC1</sub> -Ambient temperature Ta

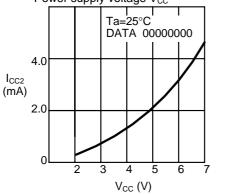

Current consumption (READ) I<sub>CC1</sub> -Power supply voltage VCC

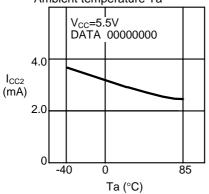

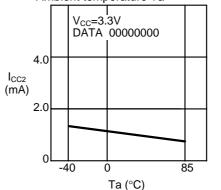

1.5 Current consumption (PROGRAM) I<sub>CC2</sub> - Ambient temperature Ta

1.7 Current consumption (PROGRAM)  $I_{CC2}$  - Power supply voltage  $V_{CC}$

1.2 Current consumption (READ) I<sub>CC1</sub> - Ambient temperature Ta

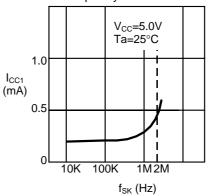

1.4 Current consumption (READ) I<sub>CC1</sub> - Clock frequency fsk

1.6 Current consumption (PROGRAM) I<sub>CC2</sub> - Ambient temperature Ta

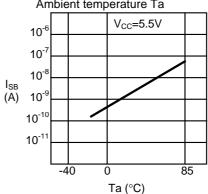

1.8 Standby current consumption I<sub>SB</sub> - Ambient temperature Ta

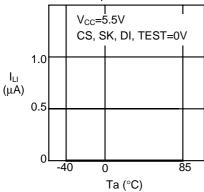

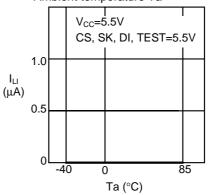

1.9 Input leakage current I<sub>LI</sub> - Ambient temperature Ta

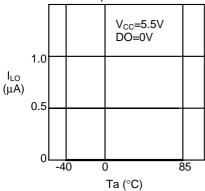

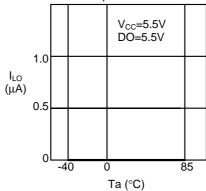

1.11 Output leakage current I<sub>LO</sub> - Ambient temperature Ta

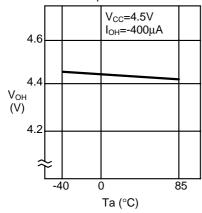

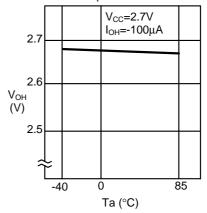

1.13 High level output voltage V<sub>OH</sub> - Ambient temperature Ta

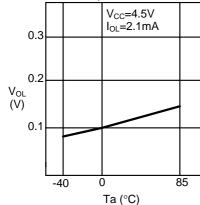

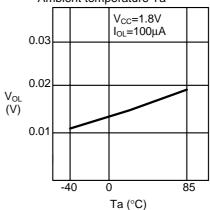

1.15 Low level output voltage  $V_{\text{OL}}$ -Ambient temperature Ta

1.10 Input leakage current I<sub>LI</sub> - Ambient temperature Ta

1.12 Output leakage current I<sub>LO</sub> - Ambient temperature Ta

1.14 High level output voltage V<sub>OH</sub> - Ambient temperature Ta

1.16 Low level output voltage  $V_{OL}$  - Ambient temperature Ta

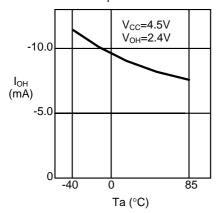

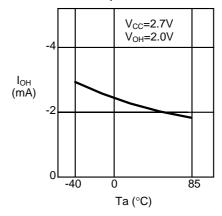

1.17 High level output current I<sub>OH</sub> - Ambient temperature Ta

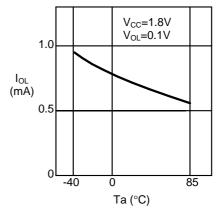

1.19 Low level output current I<sub>OL</sub>-Ambient temperature Ta

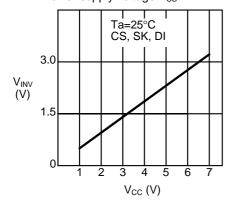

1.21 Input inversion voltage  $V_{\text{INV}}$  - Power supply voltage  $V_{\text{CC}}$

1.18 High level output current I<sub>OH</sub> - Ambient temperature Ta

1.20 Low level output current  $I_{OL}$  - Ambient temperature Ta

1.22 Input inversion voltage  $V_{\text{INV}}$  - Ambient temperature Ta

# CMOS SERIAL E<sup>2</sup>PROM S-29430A

## 2. AC Characteristics

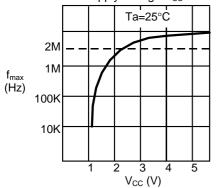

2.1 Maximum operating frequency  $f_{max}$  - Power supply voltage  $V_{CC}$

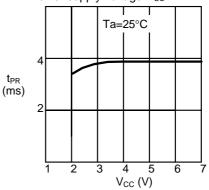

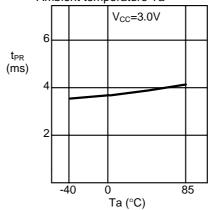

$\begin{array}{ccc} 2.3 & \text{Program time $t_{PR}$-} \\ & \text{Ambient temperature Ta} \end{array}$

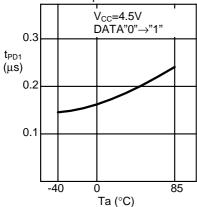

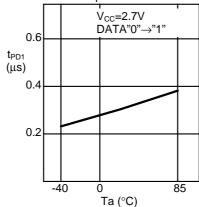

2.5 "1" Data output delay time t<sub>PD1</sub> - Ambient temperature Ta

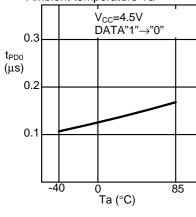

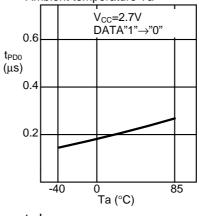

2.7 "0" Data output delay time t<sub>PD0</sub> - Ambient temperature Ta

$\begin{array}{ccc} 2.2 & \text{Program time $t_{PR}$-} \\ & \text{Power supply voltage $V_{CC}$} \end{array}$

$\begin{array}{ccc} 2.4 & \text{Program time $t_{PR}$-} \\ & \text{Ambient temperature Ta} \end{array}$

2.6 "1" Data output delay time t<sub>PD1</sub> - Ambient temperature Ta

2.8 "0" Data output delay time  $t_{\text{PD0}}$  - Ambient temperature Ta

Author: Ebisawa Takashi Date: 99/01/13 (Wednesday) 18:19 (modified: 99/01/14)

<Information level>

A: Public (Printing O.K.)

Index: C: quality, reliability

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal No.: Overall

Related documents:

# Question:

What about the reliability and quality of the EEPROM?

## Answer:

1. The EEPROM must have a quality that is "special in a sense" and that differs from that of the other ICs.

< What is this special quality?>

(1) Number of possible rewrites: 105 or 106

A specified minimum number of data rewrites must be assured.

(2) Data retention: 10 years

It must be ensured that written data ('1' and '0') will be stored for at least 10 years.

Ensuring (1) and (2) is very difficult in a technical sense, as well as in the sense that high quality must be maintained despite the need for mass production.

2. Why this guarantee is technically difficult

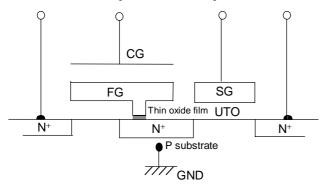

As shown in the figure below, the EEPROM functions as a non-volatile memory by holding charges in FG.

Source electrode Control gate electrode Select gate electrode Drain electrode

## [Data rewrite]

<u>Data rewrite</u> refers to the injection or removal of electrons into or from the FG. In this process, electrons pass through a thin oxide film (UTO). The oxide film inherently acts as an insulator, but in this case the film conducts electricity (electrons are transferred).

## [Data retention]

<u>Data retention</u> refers to the prevention of leakage of electrons stored in the FG. This must be assured for at least 10 years.

To meet the above stated contradictory properties, high-quality thin oxide films (UTO) must be manufactured. Such UTOs are very thin (on the order of 10 nm), and stably manufacturing them requires a very difficult technique.

## <Remarks>

Author: Ebisawa Takashi Date: 99/01/13 (Wednesday) 18:57 (modified: 99/01/13)

<Information level>

X: Working Index: A: General

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

# Question:

What about the distribution of application notes, usage notes, and malfunctions?

# Answer:

Distribution of application notes

All EEPROMS, including ours, may malfunction (false-writes may occur) due to an "operation in a low-voltage region upon power-on/off" or "improper recognition of a command due to a noise signal." This defect is particularly common in the voltage region of the microcomputer transmitting commands to the EEPROM, where the voltage is lower than the lowest operating voltage of the microcomputer.

To prevent this defect, usage notes have been prepared for the EEPROM.

- S-93C series, S29 series

- S-24CxxA series

- S-24CxxB series

## <Remarks>

Author: Ebisawa Takashi Date: 99/01/13 (Wednesday) 17:43 (modified: 99/01/13)

<Information level>

A: Public (Printing O.K.)

Index: A: General

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

# Question:

What are some applications of the serial EEPROM?

## Answer:

1. Applications of the EEPROM

The applications of the EEPROM can be roughly divided into the following types:

- Tuning memory, mode setting, ID codes: Arbitrary data can easily be rewritten and data can be retained during power-off.

- Replacement of a DIP switch (from a mechanical to an electronic switch): User costs are substantially reduced.

- Adjustment data for IC elements and other electronics: The accuracy of final products is increased. Adjustments, which had been performed manually, can be automated.

- 2. Specific examples of applications

Based on the above applications, general examples are shown below. Basically, the EEPROM (a non-volatile memory) is useful for electronic applications.

[Television] TV channel memory, screen setting data, data backup during power-off

S-24C series

[Video] VTR channel memory, program reservation data, image-quality adjustment data,

data backup during power-off

S-93Cx6A, S-29xx0A, S-24C series

[White goods] Maintenance data, adjustment data

S-93Cx6A, S-29xx0A, S-24C series

[Vehicle-mounted] Troubleshooting data, maintenance data, adjustment data: Air bags, ABS,

distance meters

S-93Cx6A, S-29xx0A, S-24C series

[Printers] Printer maintenance data

S-93Cx6A, S-29xx0A, S-24C series

[Modems] Replacement of DIP switches, software (firmware) data

S-93Cx6A, S-29xx0A, S-24C series

[Mobile telephones] Personal ID, telephone-number data, address data, adjustment data

S-24C series

[Pagers] Personal ID, telephone-number data, address data

S-93Cx6A, S-29Z series, S-24C series

[PC cards] LAN cards and modem cards, replacement of dip switches, software data

S-93C46A, S-29, S-24C series

## <Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

#### <Information level>

A: Public (Printing O.K.)

Index: D: Technical terms

#### <Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

#### Related documents:

## Question:

What about the basic terms (verify, ready/busy function)?

# Answer:

Verify, ready/busy (R/B) function

This is a function to find out about an actual write operation (time). There are two methods, a "monitoring method based on the output condition of the DO pin" and a "method for monitoring the output condition of the Ready/Busy pin." This function eliminates the need to wait 10 ms for writing to be completed, thereby minimizing the write time according to the performance of the IC (performance value: 4 ms to 5 ms; 1 ms is ensured for the S-24C series).

(Note) Note that this differs from a normal verify function, which checks written data for errors.

## <Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

A: Public (Printing O.K.)

Index: D: Technical terms

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

## Question:

What about the basic term (page write)?

# Answer:

Page write S-24C series

Writing to memory is normally executed in addresses. With the page write function, however, writing can be executed in pages (multiple addresses). This function can improve the efficiency of write commands and reduce writing time.

Ex.:S-24C04B (4 K = 512 addresses x 8 bits) 16-byte page write function

Writing in addresses: A write time of 10 msec. x 512 = 5.1 sec. is required.

Page write: 10 msec. x 512 / 16 = 320 msec.

However, compatibility with products from other companies must be confirmed.

<Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

A: Public (Printing)

Index: D: Technical terms

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

# Question:

What about the basic terms (Test pin, ORG pin)

## Answer:

TEST pin

This is an input pin used to enter a test mode when tests are conducted during an SII inspection process. This information is not provided to users. It can be used with a GND or Vcc connection, or in an open state (see note). This is important in maintaining compatibility with the pin layouts of other companies. Some users fear that the test mode may be inadvertently entered during operation, but such fears are unnecessary, as a potential of at least 10 V must be constantly supplied to enter the test mode.

(Note) Since the TEST pin has a C-MOS input structure, the GND or Vcc connection is most suited for this pin.

ORG (Organization) pin

Input pin used to specify a memory configuration. A normal memory has a "16 bit/1 address" data configuration and includes no ORG pin. Competing manufacturers, however, have released products that enable data to be switched between "x16" and "x8" using "H" or "L" of the ORG pin. Since this function is provided for the 93C series of the NS code, there is a compatibility problem. SII has not yet released products featuring this function.

<Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

A: Public (Printing O.K.)

Index: B: Technical

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

# Question:

Malfunction (false-write, illegal data)

# Answer:

[Malfunction of the EEPROM] (key words: false-store(illegal data)

The EEPROM may malfunction (false-store) due to power-on/off or noise from the microcomputer. The defect rate, however, is on the order of ppm. Even though, this could be a serious problem for the users and to the applications.

- This problem essentially results from users' design techniques, but the manufacturer should make efforts to prevent this defect. As the unit price continuously decreases, this is particularly important in discriminating us from our competitors.

- Improving the business techniques of the manufacturer

Malfunction basically results from a user's inappropriate operation, so the user is the responsible

party. We, however, must bear responsibility for defects in the IC. Thus, the best action to take

depends on whether the user or SII is responsible for the defect. In practice, however, it is difficult to

determine from a user's claim or inquiry, or through an agent, who is responsible for a defect.

In such a case, inform the Business Techniques section of the situation as soon as possible. In addition, see FAQ on other "malfunctions" for technical information.

<Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

A: Public (Printing O.K.)

Index: B: Technical

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

# Question:

Power-on clear in S-93CxxA, S-29xxxA, notes for power-on (malfunction)

## Answer:

1. This IC series has a built-in power-on clear circuit.

This circuit instantly initializes the EEPROM when the power voltage is activated. Since malfunction may occur if initialization has not been completed normally, the conditions specified below are required to activate the power voltage in order to operate the power-on clear circuit normally.

- 2. Notes on power-on

- ① Method for activating the power voltage

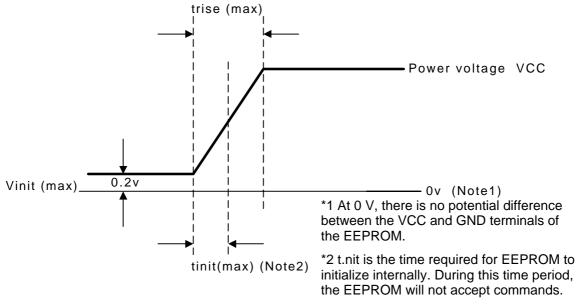

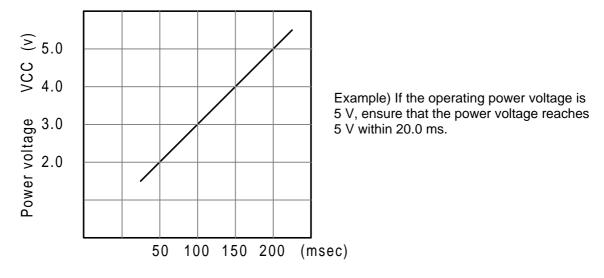

As shown in Fig. 1, activate the power voltage starting from a maximum of 0.2 V so that the power voltage reaches the operating value within the time specified as tRISE. If the operating power voltage is, for example, 5.0 V, tRISE = 200 ms, as shown in Fig. 2. Thus, the power voltage must be activated within 200 ms.

Fig. 1 Activation of the Power Voltage

Fig. 2 Maximum power-voltage activation time

t<sub>rise</sub> (max)

## ② Initialize time tinit

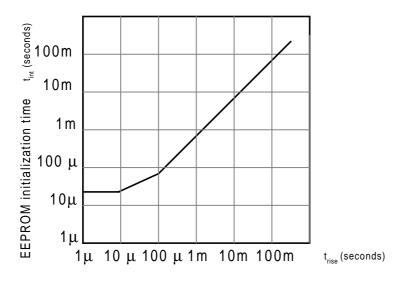

The EEPROM is instantly initialized when the power voltage is activated.

Since the EEPROM does not accept commands during initialization, the transmission of commands to the EEPROM must be started after this initialization time period.

Fig. 3 shows the time required to initialize the EEPROM.

Power-voltage activation time

Power-voltage activation time

## Fig. 3 EEPROM initialization time

When the power-on clear circuit has finished initialization normally, the EEPROM enters a programdisabled state. If the power-on clear circuit does not operate, the following situation is likely:

- In some cases, a previously entered command has been enabled. If, for example, a programenabled command has been enabled and the input terminal mistakenly recognizes a write command due to extraneous noise while the next command is being entered, writing may be executed.

The following may prevent the power-on clear circuit from operating:

- If the power lines of the microcomputer and EEPROM are separated from each other, and the output terminals of the microcomputer and EEPROM are wired or connected to each other, there may be a potential difference between the power lines of the EEPROM and microcomputer. If the voltage of the microcomputer is higher, a current may flow from the output terminal of the microcomputer to the power line of the EEPROM via a parasitic diode in the DO pin of the EEPROM. Therefore, the power voltage of the EEPROM has an intermediate potential to prevent power-on from being cleared.

- During an access to the EEPROM, the voltage may decrease due to power-off. Even if the

microcomputer has been reset due to a decrease in voltage, the EEPROM may malfunction if

EEPROM power-on clear operation conditions are not met. For the EEPROM power-on clear

operation conditions, see "Method for Activating the Power Voltage."

## <Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

B: For Distri & Rep (Printing N.G.)

Index: B: Technical

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

## Question:

False-writes in S-93C, S-29 series: inadvertent activation of CS (malfunction)

## Answer:

Inadvertent writing in the S-29 series

In the S-29 series, when a CS input is inadvertently activated during a write command, undefined data may be written. Relevant timings are shown below.

A command is composed of the following: "start bit + two command bits + address + (data)."

The figure below shows the timings in which commands are set (In the figure, the portion denotes the rising edge of SK.)

In the case of a write command, after a final address has been input and while 16-bit data is being input, undefined data is written when the CS input is changed from H to L.

Case in which, during a command entry, CS is changed from H to L with a timing that differs by a predetermined minimum number of clocks.

In the case of a write command, if the number of clocks is smaller than the predetermined value, data is loaded so as to be changed from D15 to D0. When, for example, CS is shifted from H to L after three clocks, data, which would otherwise have been stored in D15 to D13, is stored in D2 to D0, while undefined data is stored on the upper side a storage state in which the internal logic has been changed to either H or L). In addition, if the number of clocks is greater than the predetermined value, the last 16 pieces of data are stored correctly.

<Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

A: Public (Printing O.K.)

Index: A: General

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

# Question:

EEPROM compatibility table, cross reference

# Answer:

## **EEPROM** compatibility table

| Product name      | Key word            | NATIONAL        | ATMEL             | ST Micro electronic |

|-------------------|---------------------|-----------------|-------------------|---------------------|

|                   |                     | SEMICONDUCTOR   |                   |                     |

| S-29130ADPA       | EE,1KB,DIP,3W       | NM93C(S)46ZEN   | AT93C46-10PI-2.5  | ST93C46(7)AB6       |

| S-93C46ADP        | <b>↑</b>            | <b>↑</b>        | <b>↑</b>          | 1                   |

| S-29130AFJA-TB    | EE,1KB,SOP1,3W      | NM93C(S)46ZEM8  | AT93C46R-10SI-2.5 | ST93C46(7)TM6013TR  |

| S-93C46AFJ-TB     | <b>↑</b>            |                 | <b>↑</b>          | <b>↑</b>            |

| S-29130ADFJA-TB   | EE,1KB,SOP2,3W      |                 | AT93C46W-10SI-2.5 | ST93C46(7)AM6013TR  |

| S-93C46ADFJ-TB    | <b>↑</b>            |                 | <b>↑</b>          | <b>↑</b>            |

| S-29131ADPA       | EE,1KB,DIP,3W,PROT  | NM93C46ZEN      | AT93C46-10PI-2.5  | ST93C46(7)B6        |

| S-29131AFJA-TB    | EE,1KB,SOP1,3W,PROT | NM93C46ZEM8     | AT93C46R-10SI-2.5 | ST93C46(7)TM6013TR  |

| S-29220ADPA       | EE,2KB,DIP,3W       | NM93C(S)56ZEN   | AT93C56-10PI-2.5  | ST93C56(7)AB6       |

| S-29220AFJA-TB    | EE,2KB,SOP1,3W      | NM93C(S)56ZEM8  | AT93C56R-10SI-2.5 | ST93C56(7)TM6013TR  |

| S-29220ADFJA-TB   | EE,2KB,SOP2,3W      |                 | AT93C56W-10SI-2.5 | ST93C56(7)AM6013TR  |

| S-29221ADPA       | EE,2KB,DIP,3W,PROT  | NM93C56ZEN      | AT93C56-10PI-2.5  | ST93C56(7)B6        |

| S-29221AFJA-TB    | EE,2KB,SOP1,3W,PROT | NM93C56ZEM8     | AT93C56R-10SI-2.5 | ST93C56(7)TM6013TR  |

| S-29330ADPA       | EE,4KB,DIP,3W       | NM93C(S)66ZEN   | AT93C66-10PI-2.5  | ST93C66(7)AB6       |

| S-29330AFJA-TB    | EE,4KB,SOP1,3W      | NM93C(S)66ZEM8  | AT93C66R-10SI-2.5 | ST93C66(7)TM6013TR  |

| S-29330ADFJA-TB   | EE,4KB,SOP2,3W      |                 | AT93C66W-10SI-2.5 | ST93C66(7)AM6013TR  |

| S-29331ADPA       | EE,4KB,DIP,3W,PROT  | NM93C66ZEN      | AT93C66-10PI-2.5  | ST93C66(7)B6        |

| S-29331AFJA-TB    | EE,4KB,SOP1,3W,PROT | NM93C66ZEM8     | AT93C66R-10SI-2.5 | ST93C66(7)TM6013TR  |

| S-29430ADP        | EE,8KB,DIP,3W       |                 |                   |                     |

| S-29430AFE-TF     | EE,8KB,SOP1,3W      |                 |                   |                     |

| S-24C01ADPA-01    | EE,1KB,DIP,2W       |                 | AT24C01A-10PI-2.5 | ST24(25)C(W)01B6    |

| S-24C01AFJA-TB-01 | EE,1KB,SOP,2W       |                 | AT24C01A-10SI-2.5 | ST24(25)C(W)01M6TR  |

| S-24C02ADPA-01    | EE,2KB,DIP,2W       | NM24C02(03)LEN  | AT24C02-10PI-2.5  | ST24(25)C(W)02B6    |

| S-24C02AFJA-TB-01 | EE,2KB,SOP,2W       | NM24C02(03)LEM8 | AT24C02N-10SI-2.5 | ST24(25)C(W)02M6TR  |

| S-24C04ADPA-01    | EE,4KB,DIP,2W       | NM24C04(05)LEN  | AT24C04-10PI-2.5  | ST24(25)C(W)04B6    |

|                   |                     |                 |                   |                     |

| S-24C04AFJA-TB-01 | EE,4KB,SOP,2W           | NM24C04(05)LEM8  | AT24C04N-10SI-2.5 | ST24(25)C(W)04M6TR |

|-------------------|-------------------------|------------------|-------------------|--------------------|

| S-24C08ADPA-01    | EE,8KB,DIP,2W           | NM24C08(09)LEN   | AT24C08-10PI-2.5  | ST24(25)C(W)08B6   |

| S-24C08AFJA-TB-01 | EE,8KB,SOP,2W           | NM24C08(09)LEM8  | AT24C08N-10SI-2.5 | ST24(25)C(W)08M6TR |

| S-24C16ADPA-01    | EE,16KB,DIP,2W          | NM24C16(17)LEN   | AT24C16-10PI-2.5  | ST24(25)C(W)16B6   |

| S-24C16AFJA-TB-01 | EE,16KB,SOP,2W          | NM24C16(17)LEM8  | AT24C16N-10SI-2.5 | ST24(25)C(W)16M6TR |

| S-29L130AFE-TB    | EE,1KB,SOP1,3W,L/V      | NM93C(S)46XLZEM8 | AT93C46R-10SI-1.8 | ST93C46(7)TM6013TR |

| S-29L130ADFE-TB   | EE,1KB,SOP2,3W,L/V      |                  | AT93C46W-10SI-1.8 | ST93C46(7)AM6013TR |

| S-29L131ADFE-TB   | EE,1KB,SOP2,3W,L/V,PROT | NM93C(S)46XLZEM8 | AT93C46W-10SI-1.8 | ST93C46(7)AM6013TR |

| S-29L220AFE-TB    | EE,2KB,SOP1,3W,L/V      | NM93C(S)56XLZEM8 | AT93C56R-10SI-1.8 | ST93C56(7)TM6013TR |

| S-29L220ADFE-TB   | EE,2KB,SOP2,3W,L/V      |                  | AT93C56W-10SI-1.8 | ST93C56(7)AM6013TR |

| S-29L221ADFE-TB   | EE,2KB,SOP2,3W,L/V,PROT | NM93C(S)56XLZEM8 | AT93C56W-10SI-1.8 | ST93C56(7)AM6013TR |

| S-29L330AFE-TB    | EE,4KB,SOP1,3W,L/V      | NM93C(S)66XLZEM8 | AT93C66R-10SI-1.8 | ST93C66(7)TM6013TR |

| S-29L330ADFE-TB   | EE,4KB,SOP2,3W,L/V      |                  | AT93C66W-10SI-1.8 | ST93C66(7)AM6013TR |

| S-29L331ADFE-TB   | EE,4KB,SOP2,3W,L/V,PROT | NM93C(S)66XLZEM8 | AT93C66W-10SI-1.8 | ST93C66(7)AM6013TR |

## <Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13)

<Information level>

A: Public (Printing O.K.)

Index: D (Technical terms)

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal. No.: Overall

Related documents:

## Question:

What about the basic terms (memory protect, reset, CS)?

# Answer:

Memory protect, reset  $\rightarrow$ S-29xx1A, S-29x94A, S-29x55A

Function for prohibiting a write command from being executed in a certain region of the memory space.

This function is enabled by controlling the protect or reset input pin (select/deselect protect). This reset prevents the microcomputer from running uncontrollably and also prevents false-writes caused by noise in order to protect data.

Ex.: Storage of ID codes and product shipment adjustment data

(Note) S-29xx1A and S-29x94A protect 50% of memory, starting with the leading address.

CS, /CS (/CS: S-29x55A, S-29x94A)

CS is an input pin used to select the execution of a command. It is selected using "H" and deselected using "L" (the reverse is true for /CS)

$\rightarrow$  /CS is useful on the interface of the microcomputer (L active is mainly used for the microcomputer). Malfunction, however, is likely to be caused by noise upon power-on if a command is executed at the GND level.

<Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13(Wednesday))

<Information level>

A: Public (Printing O.K.)

Index: A: General

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal No.: Overall

#### Related documents:

## Question:

Concept of the compatibility, features, and markets of the S-29 series

## Answer:

[Compatibility of the EEPROM]

In terms of memory, most SII EEPROMs are compatible with our competitors' standard products in their operation codes. If another company's product is to be replaced by a corresponding SII product, the DC/AC specifications desired by the user must be carefully determined.

The key words for the products are given below.

Our competitor's 93C-series products are compatible with SII's S-29xx0A-series products, and our competitor's 24C-series products are compatible with SII's S-24C-series products.

The key word for each company is given below.

NM93C : National Semiconductor

AT93C : ATMEL 93C : Microchip

M93C : ST Micro electronic (formerly SGS Tomson ST93C)

CAT93C : Catalyst

AK93C : Asahi Kasei

BR93C : ROHM

## <Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13(Wednesday))

<Information level>

A: Public (Printing O.K.)

Index: A: General

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal No.: Overall

Related documents:

# Question:

How are operation codes classified?

# A:

# [EEPROM operation codes]

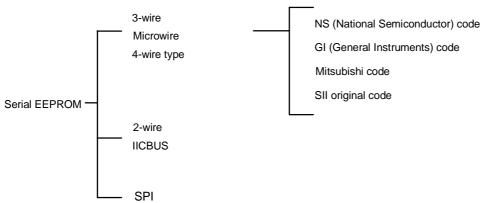

In the serial EEPROM, the operation codes can be classified into several types. Our competitors have released products compatible with each type of operation code. The key words of the operation codes are given below.

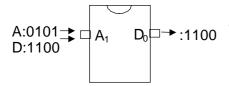

## 1. Serial and parallel

Data reading and writing are divided into serial and parallel types.

#### ex.: Parallel

Addresses and data are processed in parallel.

[Advantage]

Fast processing

Addresses and data are processed in serial.

[Advantages]

The size can be reduced due to the reduced number of I/O terminals, and fewer wires are required for the substrate.

The package can be downsized and manufactured inexpensively.

#### 2. 3-wire type, microwire, 4-wire type

Composed of four pins, including three input pins CS, SK, and DI, and an output pin DO. Since DI and DO can be directly coupled together, the EEPROM can be virtually composed of three pins (the 4-wire type includes an additional Ready/Busy pin, but is still referred to as a "3-wire type").

① NS code: The key word is "93Cx." Compatible with SII S-29xxOA.

General code used by many competing companies. Mass produced and low in cost.

② GI code

General Instrument Inc.'s original code. Its markets continue to dwindle.

- ③ Mitsubishi code: The key word is "M6M8."Compatible with SII S-29x55A. Serial-port direct-coupling type in which commands and data are composed of x8 units. Intended for the TV and VTR markets and primarily sold as a set with Mitsubishi microcomputers.

- SII original code: S-29x9xA

Serial-port direct-coupling type in which commands and data are composed of x8 units. Intended for technology-oriented users.

3. 2-wire type, IICBUS: The key word is "24C." Compatible with SII S-24CxxA. Composed of two pins: an input pin (SCL) and an I/O pin (SDA). Phillips Inc. owns a relevant patent.

[Advantages] Fewer wires are required, and the microcomputer port can be shared with another IICBUS. TV set maker will be main market.

4. SPI: The key word is "25C." Not compatible with SII. Under development. Composed of four pins: three input pins CS, SCK, and SI, and an input pin SO. In the case of the EEPROM, the advantages are high speed (5 MHz at 5v) and a high capacity (128 Kbytes).

#### <Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13(Wednesday))

<Information level>

A: Public (Printing O.K.)

Index: D: Technical Terms

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal No.: Overall

Related documents:

# Question:

What are the basic operation codes?

# Answer:

[Terms required to understand EEPROM data sheets (1)] Basic commands

- <u>Data read</u>, READ

- Reads data from a specified address

- <u>Data write</u>, WRITE or PROGRAM Writes data to a specified address

- Data erase, ERASE

Erases data at a specified address (all "1"'s)

- Chip write, WRAL

Writes the same (word) data in all address spaces

- Chip erase, ERAL

Erases data in all address spaces (all "1"'s)

- Program disable, EWDS or PDS

Prohibits write operations (WRITE), and prevents false-writes caused by noise or uncontrollable running of the CPU

- <u>Program enable</u>, EWES or PEN Enables write operations (WRITE)

## [Note]

When the power to the EEPROM is turned on, the internal circuit of the IC is reset and the program disable mode is entered. Thus, following power-on, the program enable command must be entered in order to write data.

# Memory space: In the case of the S-29130A (64 words X 16 bits)

<Remarks>

Author: Kano Tomoo Date: 98/11/12 (Thursday) 10:17 (modified: 99/01/13(Wednesday))

#### <Information level>

A: Public (Printing O.K.)

Index: D: Technical terms

#### <Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal No.: Overall

#### Related documents:

# Question:

What about the basic terms. (continuous read, sequential read)?

# Answer:

- Continuous read, sequential read →S-93C series, S-29 series, S-24C series Function by which data is read from a specified address using a read command, followed by the output of the next address. This is useful when there is a large amount of user data (ex.: ID codes).

- <u>Serial-port direct coupling</u>, <u>microcomputer interface</u>, <u>8-bit command</u> →S-29x9xA, S-29x55A, S-2900A

The serial port is a serial I/O port provided for a microcomputer. A device that can be easily and directly coupled to this port is referred to as a "serial-port direct-coupling type" or a "microcomputer interface."

- 1. The EEPROM is configured as follows for simple direct coupling:

- ① Data is input at the rising edge of the SK input clock, and output at its falling edge.

- ② Commands and data are input and output in 8 bits.

- 2. A microcomputer with a serial port communicates in 8 bits (8 clocks).

This configuration can substantially reduce the number of programs required for the microcomputer. The advantages are easy programming and a reduced ROM capacity.

<Remarks>

Creator: Takashi Ebisawa Date: 98/01/13 (Wednesday) 10:51 (modified: 99/01/13(Wednesday))

<Information level>

A: Public (Printing O.K.)

Index: D: Technical terms

<Product>

Division name: 01 IC

Category 1: 12 Memory

Category 2: 2. Serial EEPROM

Cal No.: Overall

Related documents:

# Question:

What is the EEPROM?

# Answer:

- 1. Electrically Erasable Programmable Read Only Memory

- Why this memory is referred to as "read only" despite the fact that it enables data to be rewritten?

The EEPROM requires a longer time for writing than a RAM, so it is used exclusively for reading.

- What is the "memory"?

Elements storing data. Data is generally represented by the digits "0" and "1."

- What is the "ROM"?

Read Only Memory

Reference: RAM is Random Access read write Memory.

## <Remarks>