# **Contents**

| Features                                      | . 1  |

|-----------------------------------------------|------|

| Block Diagram                                 | .2   |

| Pin Description                               | . 4  |

| Pad Assignment                                |      |

| Pad Coordinates                               | .7   |

| Operation                                     | . 9  |

| Interface                                     | . 15 |

| Examples of LCD Drive Output                  |      |

| Waveform                                      | . 18 |

| Examples of External Bias Resistor Connection |      |

| vs LCD Drive Waveform                         | . 19 |

| Command Explanation                           | . 20 |

| Command                                       | . 28 |

| Absolute Maximum Ratintgs                     | . 29 |

| DC Charasteristics                            | . 29 |

| Timing Charasteristics                        | . 32 |

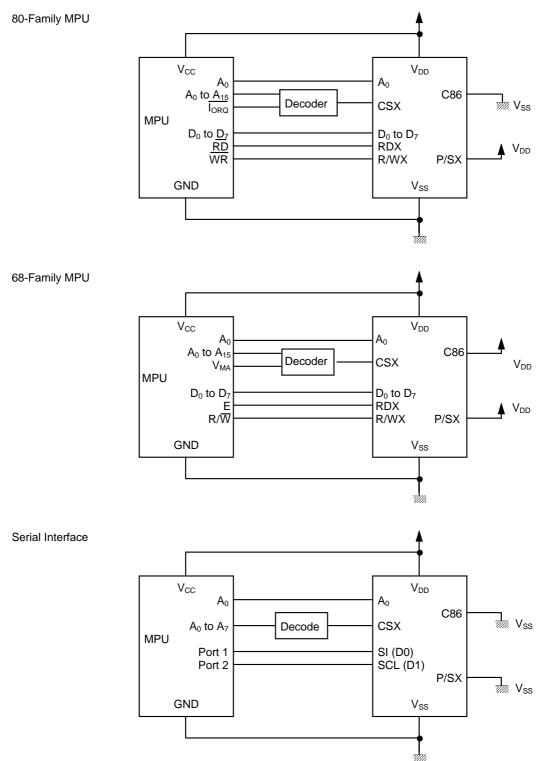

| Examples of Connection to MPU                 |      |

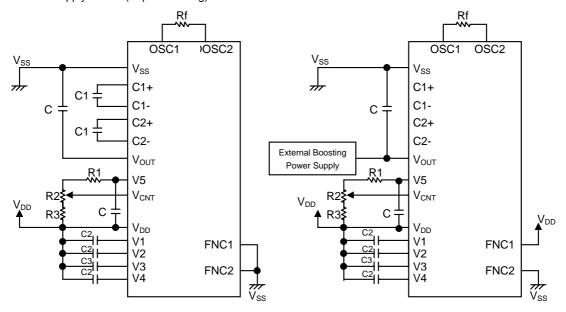

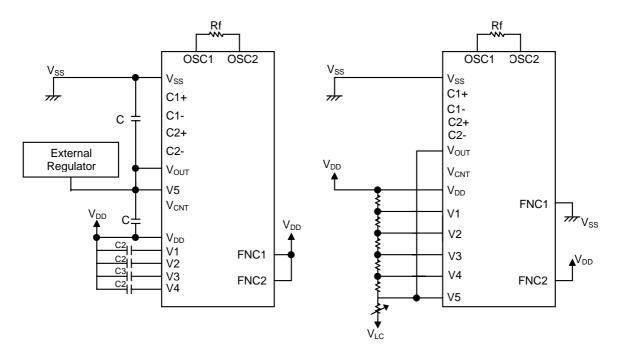

| Examples of Application Circuit of            |      |

| LCD Power Supply                              | . 36 |

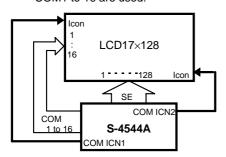

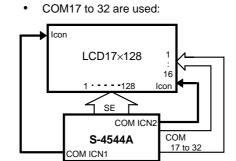

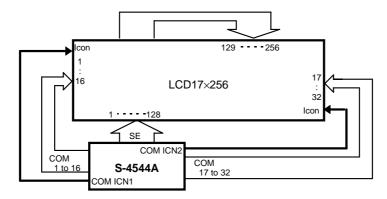

| Examples of Connection to LCD Panels          |      |

LCD Controller-Driver S-4544A

The S-4544A is a 17- or 33-common, 128-segment output graphic (bit map) LCD controller-driver with built-in 8-bit and serial interfaces. The internal 65 x 128 bit display data RAM can directly access the 8-bit and the serial data bus, making the display of both graphics and characters possible. It displays the data independently of the CPU through the built-in oscillating circuit or clock input. It has a wide variety of command instructions which minimize the load onto the CPU. It also features a wide voltage range and the low power consumption during display, making the S-4544A a suitable display for system applications in portable electronics.

#### ■ FEATURES

Interface

8-bit 80/68-Family Microcomputer Interface Serial Interface

Driver Output

128 segments

17 commons: Command Setting

33 commons: Default

Display Data RAM 65×128 bits

· Display Clock

Both built-in CR oscillating circuit and external clock input are available. Oscillating Frequency: 18 kHz

Duty Cycle

1/17: Command Setting

1/33: Default

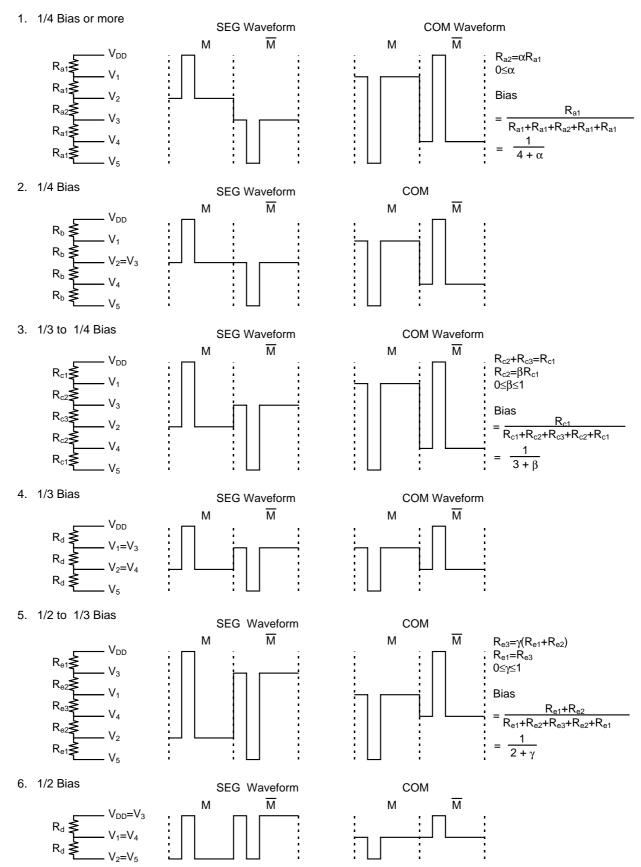

LCD Bias Resistor

Internal 1/6.7: Default

Internal 1/5: Command Setting Internal 1/4: Command Setting

External 1/2 to 1/4

#### Commands

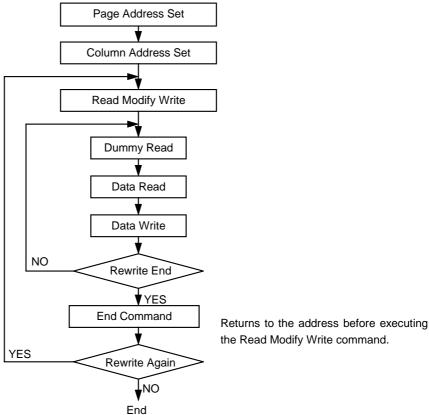

Display ON/OFF, Display Start Line Set, Page Address Set, Column Address Set, Status Read, Display All-Lit, Display Normal/Reverse, Display Data Read/Write, ADC Select, Duty Cycle Selection, Alternate Common Output, Reset, Power Save, Read/Modify/Write, Bias Select, Icon Only Display

Voltage Range

Logic: -2.4 V to -5.5 V LCD drive: -2.7 V to -11.0 V

Low Current Consumption (Low Power Consumption) typ. 110μA for CR oscillation 18 kHz, Vss=-5V. Dual Booster and V5=-8V

· Delivered on

Gold bumps (bare chips)

TCP

Other

Power Save Current Consumption:

1 μA or less (actually 1 nA or less)

Smooth scrolling Blinking is possible

Dual/Triple Booster

Built-in 1/4, 1/5, 1/6.7 Bias Resistor Built-in LCD Power Supply Circuit

Built-in LCD Drive Voltage Command Fine

Adjustment Circuit

2 Internal Icon Common Output Systems

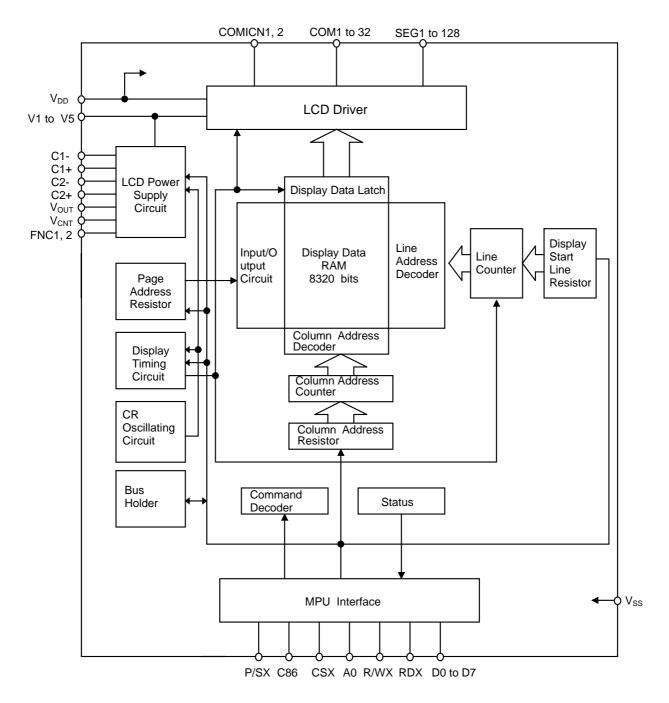

### ■ BLOCK DIAGRAM

### 1. Block Overview

Figure 1 Block Overview

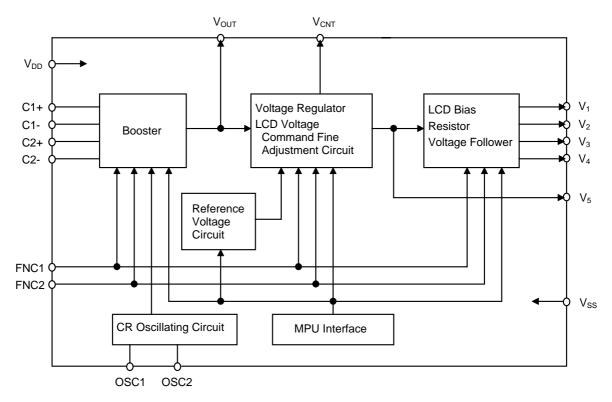

# 2. LCD Power Supply Circuit Block Diagram

Figure 2 LCD Power Supply Circuit Block Diagram

## ■ PIN DESCRIPTION

# 1. Logic Circuit Power Supply Pins

**Table 1 Logic Circuit Power Supply Pins**

| Pin No. | Pin Name | Description                                             |  |  |  |  |

|---------|----------|---------------------------------------------------------|--|--|--|--|

| 20 , 39 | VSS      | Negative power supply: Usually connected to -3 or -5 V. |  |  |  |  |

| 10 , 58 | VDD      | Positive power supply: Usually connected to 0 V.        |  |  |  |  |

## 2. Control Pins

Table 2 Control Pins

| Pin No. | Pin Name | Description                                                                                                                                                                                                |  |  |  |  |  |  |  |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 12      | CSX      | Chip-select input Active "L"                                                                                                                                                                               |  |  |  |  |  |  |  |

| 13      | A0       | Display data or display control command change Usually connected to the lowermost bit of the MPU address bus A0="0": DB0 to DB7: Control command input. A0="1": DB0 to DB7: Display data input and outputs |  |  |  |  |  |  |  |

| 14      | R/WX     | [68-family MPU] Read/write signal input R/WX="H": Read R/WX="L": Write [80-family MPU] Write signal input                                                                                                  |  |  |  |  |  |  |  |

|         |          | Active "L" Data bus output state                                                                                                                                                                           |  |  |  |  |  |  |  |

| 15      | RDX      | [68-family MPU] Enable clock signal input Active "H"                                                                                                                                                       |  |  |  |  |  |  |  |

|         |          | [80-family MPU] Read signal input Active "L" Data bus output state                                                                                                                                         |  |  |  |  |  |  |  |

| 16      | P/SX     | Parallel/serial interface change P/SX="H": 8-bit parallel interface P/SX="L": Serial interface                                                                                                             |  |  |  |  |  |  |  |

| 17      | C86      | MPU interface select C86="H": 68-family interface C86="L": 80-family interface                                                                                                                             |  |  |  |  |  |  |  |

| 25      | D0       |                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 26      | D1       | P/SX="H": 8-bit configuration data bus connection                                                                                                                                                          |  |  |  |  |  |  |  |

| 28      | D2       | 3-state input/output configuration                                                                                                                                                                         |  |  |  |  |  |  |  |

| 29      | D3       | P/SX="L": Serial interface connection                                                                                                                                                                      |  |  |  |  |  |  |  |

| 31      | D4       | D0 Serial data input                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 32      | D5       | D1 Serial clock input                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 34      | D6       | D2 Serial data output                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 35      | D7       |                                                                                                                                                                                                            |  |  |  |  |  |  |  |

# 3. CR Oscillation Pins

**Table 3 CR Oscillation Pins**

| Pin No. | Pin Name | Description                                                      |

|---------|----------|------------------------------------------------------------------|

| 18      | OSC2     | CR oscillating circuit output. Connects oscillation resistor Rf. |

| 19      | OSC1     | CR oscillating circuit input. Connects oscillation resistor Rf.  |

# 4. LCD Drive Voltage Pins

Table 4 LCD Drive Voltage Pins

| Pin No. | Pin Name | Description                                                                                                                            |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| 37      | FNC2     | LCD power supply circuit operation control pin 2. Connected to VDD or VSS only.                                                        |

| 38      | FNC1     | LCD power supply circuit operation control pin 1. Connected to VDD or VSS only.                                                        |

| 42      | VOUT     | Boosting voltage output                                                                                                                |

| 46      | C2-      | 2nd-step boosting capacitor negative connection                                                                                        |

| 49      | C2+      | 2nd-step boosting capacitor positive connection                                                                                        |

| 50      | C1-      | 1st-step boosting capacitor negative connection                                                                                        |

| 51      | C1+      | 1st-step boosting capacitor positive connection                                                                                        |

| 57      | VCNT     | LCD power supply voltage control                                                                                                       |

| 59      | V1       | LCD drive bias voltage  Outputs LCD drive bias voltage when using a built-in LCD power supply circuit.                                 |

| 60      | V2       | 1/4 bias 1/5 bias 1/6.75 bias<br>V1 1/4×V5 1/5×V5 1/6.75×V5                                                                            |

| 61      | V3       | V2 2/4×V5 2/5×V5 2/6.75×V5<br>V3 2/4×V5 3/5×V5 4.75/6.75×V5                                                                            |

| 62      | V4       | <ul> <li>V4 3 / 4×V5 4 / 5×V5 5.75 / 6.75×V5</li> <li>Inputs LCD drive bias voltage when using an external LCD power supply</li> </ul> |

| 63      | V5       | circuit.<br>VDD≥ V1, V2, V3, V4≥ V5, VSS≥V5                                                                                            |

# 5. Driver Output Pins

**Table 5 Driver Output Pins**

| Pin No.                | Pin Name           | Description                                                                   |

|------------------------|--------------------|-------------------------------------------------------------------------------|

| 84 to 211              | SEG1 to SEG128     | Segment drive output                                                          |

| 66 to 81<br>213 to 228 | COM1 to COM32      | Common drive output                                                           |

| 229<br>82              | COMICN1<br>COMICN2 | Icon common drive output: COMICN1 and COMICN2 output the same phase waveform. |

## 6. Other Pins Table 6

| Pin No.                                                                         | Pin Name | Description                                       |

|---------------------------------------------------------------------------------|----------|---------------------------------------------------|

| 1 to 9 24, 27, 30 33, 36, 40, 41 43 to 45, 47, 48 52 to 54, 64, 65 83, 212, 230 | Dummy    | Dummy: Insulated from the inside of the IC.       |

| 11                                                                              | TEST4    |                                                   |

| 21                                                                              | TEST0    | IO delli constant                                 |

| 22                                                                              | TEST1    | IC delivery test. Cannot be wired to the outside. |

| 23                                                                              | TEST2    | Open when in use.                                 |

| 55                                                                              | TEST3    | Opon whom in doo.                                 |

| 56                                                                              | TEST5    |                                                   |

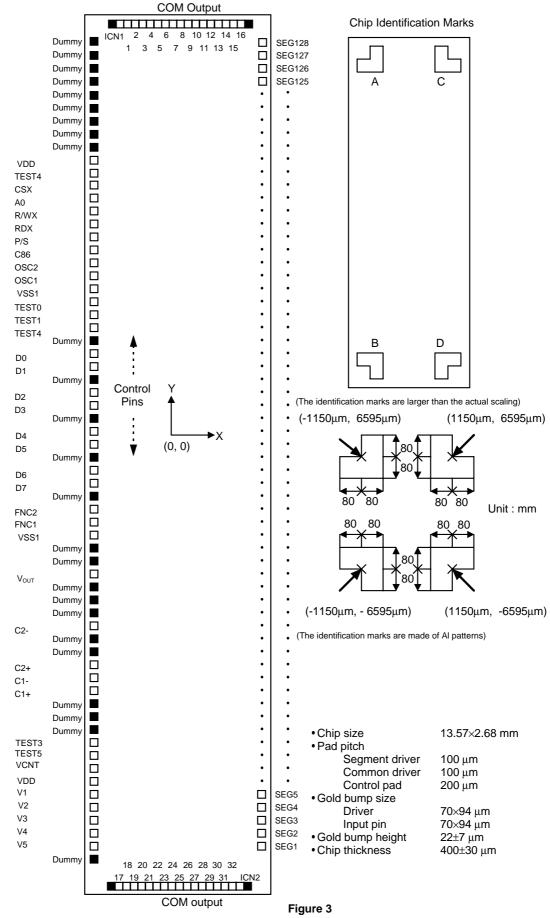

#### **■ PAD ASSIGNMENT**

Seiko Instruments Inc.

## ■ PAD COORDINATES

Table 7-1 Pad Coordinates Unit:  $\mu m$  (The origin is the center of the chip)

|     |          |       |       | Unit: μm (The origin is the ce |          |       |       |

|-----|----------|-------|-------|--------------------------------|----------|-------|-------|

| No. | Pin Name | X     | Υ     | No.                            | Pin Name | Х     | Υ     |

| 1   | Dummy    | -1191 | 6250  | 64                             | Dummy    | -1191 | -6350 |

| 2   | Dummy    | -1191 | 6050  | 65                             | Dummy    | -900  | -6636 |

| 3   | Dummy    | -1191 | 5850  | 66                             | COM17    | -800  | -6636 |

| 4   | Dummy    | -1191 | 5650  | 67                             | COM18    | -700  | -6636 |

| 5   | Dummy    | -1191 | 5450  | 68                             | COM19    | -600  | -6636 |

| 6   | Dummy    | -1191 | 5250  | 69                             | COM20    | -500  | -6636 |

| 7   | Dummy    | -1191 | 5050  | 70                             | COM21    | -400  | -6636 |

| 8   | Dummy    | -1191 | 4850  | 71                             | COM22    | -300  | -6636 |

| 9   | Dummy    | -1191 | 4650  | 72                             | COM23    | -200  | -6636 |

| 10  | VDD      | -1191 | 4450  | 73                             | COM24    | -100  | -6636 |

| 11  | TEST4    | -1191 | 4250  | 74                             | COM25    | 0     | -6636 |

| 12  | CSX      | -1191 | 4050  | 75                             | COM26    | 100   | -6636 |

| 13  | A0       | -1191 | 3850  | 76                             | COM27    | 200   | -6636 |

| 14  | R/WX     | -1191 | 3650  | 77                             | COM28    | 300   | -6636 |

| 15  | RDX      | -1191 | 3450  | 78                             | COM29    | 400   | -6636 |

| 16  | P/SX     | -1191 | 3250  | 79                             | COM30    | 500   | -6636 |

| 17  | C86      | -1191 | 3050  | 80                             | COM31    | 600   | -6636 |

| 18  | OSC2     | -1191 | 2850  | 81                             | COM32    | 700   | -6636 |

| 19  | OSC1     | -1191 | 2650  | 82                             | COMICN2  | 800   | -6636 |

| 20  | VSS      | -1191 | 2450  | 83                             | Dummy    | 900   | -6636 |

| 21  | TEST0    | -1191 | 2250  | 84                             | SEG1     | 1191  | -6350 |

| 22  | TEST1    | -1191 | 2050  | 85                             | SEG2     | 1191  | -6250 |

| 23  | TEST2    | -1191 | 1850  | 86                             | SEG3     | 1191  | -6150 |

| 24  | Dummy    | -1191 | 1650  | 87                             | SEG4     | 1191  | -6050 |

| 25  | D0 Î     | -1191 | 1450  | 88                             | SEG5     | 1191  | -5950 |

| 26  | D1       | -1191 | 1250  | 89                             | SEG6     | 1191  | -5850 |

| 27  | Dummy    | -1191 | 1050  | 90                             | SEG7     | 1191  | -5750 |

| 28  | D2 ,     | -1191 | 850   | 91                             | SEG8     | 1191  | -5650 |

| 29  | D3       | -1191 | 650   | 92                             | SEG9     | 1191  | -5550 |

| 30  | Dummy    | -1191 | 450   | 93                             | SEG10    | 1191  | -5450 |

| 31  | D4       | -1191 | 250   | 94                             | SEG11    | 1191  | -5350 |

| 32  | D5       | -1191 | 50    | 95                             | SEG12    | 1191  | -5250 |

| 33  | Dummy    | -1191 | -150  | 96                             | SEG13    | 1191  | -5150 |

| 34  | D6       | -1191 | -350  | 97                             | SEG14    | 1191  | -5050 |

| 35  | D7       | -1191 | -550  | 98                             | SEG15    | 1191  | -4950 |

| 36  | Dummy    | -1191 | -750  | 99                             | SEG16    | 1191  | -4850 |

| 37  | FNC2     | -1191 | -950  | 100                            | SEG17    | 1191  | -4750 |

| 38  | FNC1     | -1191 | -1150 | 101                            | SEG18    | 1191  | -4650 |

| 39  | VSS      | -1191 | -1350 | 102                            | SEG19    | 1191  | -4550 |

| 40  | Dummy    | -1191 | -1550 | 103                            | SEG20    | 1191  | -4450 |

| 41  | Dummy    | -1191 | -1750 | 104                            | SEG21    | 1191  | -4350 |

| 42  | VOUT     | -1191 | -1950 | 105                            | SEG22    | 1191  | -4250 |

| 43  | Dummy    | -1191 | -2150 | 106                            | SEG23    | 1191  | -4150 |

| 44  | Dummy    | -1191 | -2350 | 107                            | SEG24    | 1191  | -4050 |

| 45  | Dummy    | -1191 | -2550 | 108                            | SEG25    | 1191  | -3950 |

| 46  | C2-      | -1191 | -2750 | 109                            | SEG26    | 1191  | -3850 |

| 47  | Dummy    | -1191 | -2950 | 110                            | SEG27    | 1191  | -3750 |

| 48  | Dummy    | -1191 | -3150 | 111                            | SEG28    | 1191  | -3650 |

| 49  | C2+      | -1191 | -3350 | 112                            | SEG29    | 1191  | -3550 |

| 50  | C1-      | -1191 | -3550 | 113                            | SEG30    | 1191  | -3450 |

| 51  | C1+      | -1191 | -3750 | 114                            | SEG31    | 1191  | -3350 |

| 52  | Dummy    | -1191 | -3950 | 115                            | SEG32    | 1191  | -3250 |

| 53  | Dummy    | -1191 | -4150 | 116                            | SEG33    | 1191  | -3150 |

| 54  | Dummy    | -1191 | -4350 | 117                            | SEG34    | 1191  | -3050 |

| 55  | TEST3    | -1191 | -4550 | 118                            | SEG35    | 1191  | -2950 |

| 56  | TEST5    | -1191 | -4750 | 119                            | SEG36    | 1191  | -2850 |

| 57  | VCNT     | -1191 | -4950 | 120                            | SEG37    | 1191  | -2750 |

| 58  | VDD      | -1191 | -5150 | 121                            | SEG38    | 1191  | -2650 |

| 59  | V1       | -1191 | -5350 | 122                            | SEG39    | 1191  | -2550 |

| 60  | V2       | -1191 | -5550 | 123                            | SEG40    | 1191  | -2450 |

| 61  | V3       | -1191 | -5750 | 124                            | SEG41    | 1191  | -2350 |

| 62  | V4       | -1191 | -5950 | 125                            | SEG42    | 1191  | -2250 |

| 63  | V5       | -1191 | -6150 | 126                            | SEG43    | 1191  | -2150 |

|     |          |       | 0.00  | . = 0                          | _ ===:   | 1101  | 2100  |

**Table 7-2 Pad Coordinates**

| No. | Pin Name       | Х    | Υ     | No.        | Pin Name         | Х            | Υ            |

|-----|----------------|------|-------|------------|------------------|--------------|--------------|

| 127 | SEG44          | 1191 | -2050 | 470        | 05000            | 4404         | 2450         |

| 128 | SEG44<br>SEG45 | 1191 | -1950 | 179<br>180 | SEG96<br>SEG97   | 1191         | 3150<br>3250 |

| 129 | SEG46          | 1191 | -1850 | 181        | SEG97<br>SEG98   | 1191         | 3350         |

| 130 | SEG47          | 1191 | -1750 |            |                  | 1191         |              |

| 131 | SEG47<br>SEG48 | 1191 | -1650 | 182        | SEG99            | 1191         | 3450         |

| 132 | SEG49          | 1191 | -1550 | 183<br>184 | SEG100<br>SEG101 | 1191<br>1191 | 3550<br>3650 |

| 133 | SEG50          | 1191 | -1450 | 185        | SEG101           | 1191         | 3750         |

| 134 | SEG50<br>SEG51 | 1191 | -1350 | 186        | SEG102<br>SEG103 |              |              |

| 135 | SEG52          | 1191 | -1250 | 187        | SEG103<br>SEG104 | 1191<br>1191 | 3850<br>3950 |

| 136 | SEG53          | 1191 | -1150 | 188        | SEG105           | 1191         | 4050         |

| 137 | SEG54          | 1191 | -1050 | 189        | SEG105           | 1191         | 4150         |

| 138 | SEG55          | 1191 | -950  | 190        | SEG107           | 1191         | 4250         |

| 139 | SEG56          | 1191 | -850  | 191        | SEG107           | 1191         | 4350         |

| 140 | SEG57          | 1191 | -750  | 192        | SEG109           | 1191         | 4450         |

| 141 | SEG58          | 1191 | -650  | 193        | SEG110           | 1191         | 4550         |

| 142 | SEG59          | 1191 | -550  | 194        | SEG111           | 1191         | 4650         |

| 143 | SEG60          | 1191 | -450  | 195        | SEG112           | 1191         | 4750         |

| 144 | SEG61          | 1191 | -350  | 196        | SEG113           | 1191         | 4850         |

| 145 | SEG62          | 1191 | -250  | 197        | SEG114           | 1191         | 4950         |

| 146 | SEG63          | 1191 | -150  | 198        | SEG115           | 1191         | 5050         |

| 147 | SEG64          | 1191 | -50   | 199        | SEG116           | 1191         | 5150         |

| 148 | SEG65          | 1191 | 50    | 200        | SEG117           | 1191         | 5250         |

| 149 | SEG66          | 1191 | 150   | 201        | SEG118           | 1191         | 5350         |

| 150 | SEG67          | 1191 | 250   | 202        | SEG119           | 1191         | 5450         |

| 151 | SEG68          | 1191 | 350   | 203        | SEG120           | 1191         | 5550         |

| 152 | SEG69          | 1191 | 450   | 204        | SEG121           | 1191         | 5650         |

| 153 | SEG70          | 1191 | 550   | 205        | SEG122           | 1191         | 5750         |

| 154 | SEG71          | 1191 | 650   | 206        | SEG123           | 1191         | 5850         |

| 155 | SEG72          | 1191 | 750   | 207        | SEG124           | 1191         | 5950         |

| 156 | SEG73          | 1191 | 850   | 208        | SEG125           | 1191         | 6050         |

| 157 | SEG74          | 1191 | 950   | 209        | SEG126           | 1191         | 6150         |

| 158 | SEG75          | 1191 | 1050  | 210        | SEG127           | 1191         | 6250         |

| 159 | SEG76          | 1191 | 1150  | 211        | SEG128           | 1191         | 6350         |

| 160 | SEG77          | 1191 | 1250  | 212        | Dummy            | 900          | 6636         |

| 161 | SEG78          | 1191 | 1350  | 213        | COM16            | 800          | 6636         |

| 162 | SEG79          | 1191 | 1450  | 214        | COM15            | 700          | 6636         |

| 163 | SEG80          | 1191 | 1550  | 215        | COM14            | 600          | 6636         |

| 164 | SEG81          | 1191 | 1650  | 216        | COM13            | 500          | 6636         |

| 165 | SEG82          | 1191 | 1750  | 217        | COM12            | 400          | 6636         |

| 166 | SEG83          | 1191 | 1850  | 218        | COM11            | 300          | 6636         |

| 167 | SEG84          | 1191 | 1950  | 219        | COM10            | 200          | 6636         |

| 168 | SEG85          | 1191 | 2050  | 220        | COM9             | 100          | 6636         |

| 169 | SEG86          | 1191 | 2150  | 221        | COM8             | 0            | 6636         |

| 170 | SEG87          | 1191 | 2250  | 222        | COM7             | -100         | 6636         |

| 171 | SEG88          | 1191 | 2350  | 223        | COM6             | -200         | 6636         |

| 172 | SEG89          | 1191 | 2450  | 224        | COM5             | -300         | 6636         |

| 173 | SEG90          | 1191 | 2550  | 225        | COM4             | -400         | 6636         |

| 174 | SEG91          | 1191 | 2650  | 226        | COM3             | -500         | 6636         |

| 175 | SEG92          | 1191 | 2750  | 227        | COM2             | -600         | 6636         |

| 176 | SEG93          | 1191 | 2850  | 228        | COM1             | -700         | 6636         |

| 177 | SEG94          | 1191 | 2950  | 229        | COMICN1          | -800         | 6636         |

| 178 | SEG95          | 1191 | 3050  | 230        | Dummy            | -900         | 6636         |

# **Chip Identification Mark Coordinates (AI pattern)**

| Chip<br>Identification<br>Mark | х              | Y | Chip<br>Identification<br>Mark | х            | Y |

|--------------------------------|----------------|---|--------------------------------|--------------|---|

| A<br>B                         | -1150<br>-1150 |   | C<br>D                         | 1150<br>1150 |   |

#### **■** OPERATION

#### 1. Powering ON

Input the Display OFF command immediately after the CPU starts to operate at powering ON. Unnecessary character display can be prevented by inputting the Display OFF command. Connect and fix pins C86, P/SX, FNC1 and FNC2 to the  $V_{DD}$  or  $V_{SS}$ .

Recommended Command Setting Sequence at Powering ON:

- ① Display Screen Setting

- Display OFF

D0: 0 Display OFF Once the display OFF is engaged, unnecessary characters are not displayed.

· Display All-Lit ON/OFF

D0: 0 Display All-Lit OFF Normal display operation and the oscillation start.

- 2 LCD Power Supply Circuit Operation Setting

- LCD Power Supply Circuit ON

D0: 1 LCD Power Supply Circuit ON

- · Bias Select

- LCD Drive Voltage Fine Adjustment Data Setting

- Icon Only Display OFF/Booster Drive Frequency Setting

D2: 0 Normal Display

D0, 1: Boosted Voltage Control Data

- Reference Voltage Temperature Compensation Coefficient Select

- 3 LCD Screen Setup

- End Command Input

- Duty Select/Alternate Common Output Select

- Display Normal/Reverse

- · Display Start Line Setting

- · Common Output Sequence Setting

- Icon Only Display

- Display Start

- · Display Data Write

- Display ON

D0: 0 Display ON (Display starts)

[Note] Since the display data RAM is uncertain at powering ON, write "L" or data to be displayed in all display data RAMs before turning the display ON.

### 2. Powering OFF

In order to prevent unnecessary characters from being displayed during shutdown of the power, always input the display OFF command from the CPU, next shut down the power.

Recommended Command Setting Sequence at Powering OFF:

① Display OFF

D0: 1 Display OFF

2 LCD Power Supply Circuit OFF

D0: 0 LCD Power Supply Circuit OFF

#### 3. MPU Interface Select

In the S-4544A, the parallel interface or the serial interface can be selected.

**Table 8 Interface Selection**

| P/SX Pin Logic | C86 Pin Logic | MPU Interface       |  |  |

|----------------|---------------|---------------------|--|--|

| н              | _             | 80-family Interface |  |  |

| 11             | Н             | 68-family Interface |  |  |

| L              | don't care    | Serial Interface    |  |  |

#### 3.1 Parallel Interface

Table 9 Connection Relationship between MPU and Pins

| S-4544A Pin Name          | A0 | RDX | R/WX | CSX | D0 to D7 |

|---------------------------|----|-----|------|-----|----------|

| 68-Family MPU Signal Name | A0 | Е   | R/W  | cs  | D0 to D7 |

| 80-Family MPU Signal Name | A0 | RD  | WR   | cs  | D0 to D7 |

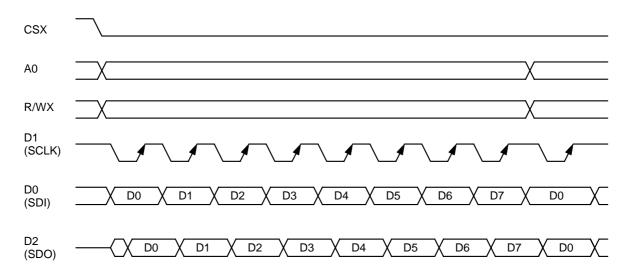

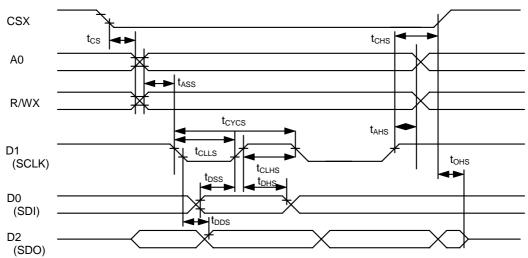

#### 3.2 Serial Interface

P/SX : "L" Serial interface "H" Parallel Interface CSX : "L" Chip Active "H" Chip Reset R/WX : "L" WRITE Command "H" READ Command A0 : "L" Command Data "H" Display Data

D0 : Serial Data Input (SDI)

D1 : Serial Clock Input (SCLK)

D2 : Serial Data Output (SDO)

D3 to D7 : Open RDX : Open C86 : Open

By setting P/SX to "L." the serial interface is selected.

The instruction code is the same as for the parallel interface. In this case, the RDX pin should be "Open."

By setting CSX to "H," the serial interface circuit is reset and the counter is initialized. By setting CSX to "L," the serial interface circuit enters an operating state.

The commands and displayed data are written at the rising edge of the serial clock. Data is input in the order D0 to D7 in 8-bit data. The status and displayed data are read at the falling edge of the serial clock. Further displayed data reading needs dummy reading.

| A0 | R/WX | Operation               |   |

|----|------|-------------------------|---|

| L  | L    | Inputs the command      | • |

| Н  | Н    | Reads the display data  |   |

| L  | Н    | Reads the status        |   |

| Н  | L    | Writes the display data |   |

When the serial interface is selected, the D2 pin (SDO: Serial Data Output Pin) goes "H" during reset.

Status reading in a reset operation is invalidated when the serial interface is selected. However, "H" is output to the D2 pin (SDO: Serial Data Output Pin) . Serial clock wiring must be made by considering external noise and reflecting noise. Be sure to check the operation of the equipment.

#### 4. Command Execution Time

The command is completely executed within the cycle time (tcyc) according to the timing characteristics of the command input. Therefore, commands can be input continuously without confirming the busy flag at the Status Read mode. Reinputting the command within the cycle time is inhibited.

### 5. Chip Select

The MPU interface is turned to "Active" by setting CSK pin to "L"

Table 10 Chip Select Logic

| CSX          | State   | Description                                                         |

|--------------|---------|---------------------------------------------------------------------|

| "H"          | Standby | D0 to D7 : High impedance A0 : Invalid RDX : Invalid R/WX : Invalid |

| " <u>L</u> " | Active  | All pins are valid                                                  |

#### 6. Data Bus Select

Table 11 Data Bus Select

|    | 68-Family | 80-Family |      | - Description                     |  |

|----|-----------|-----------|------|-----------------------------------|--|

| A0 | R/WX      | RDX       | R/WX | Безсприон                         |  |

| 1  | 1         | 0         | 1    | Reads from Display Data RAM       |  |

| 1  | 0         | 1         | 0    | Writes to Display Data RAM        |  |

| 0  | 1         | 0         | 1    | Status Read                       |  |

| 0  | 0         | 1         | 0    | Command Read to internal register |  |

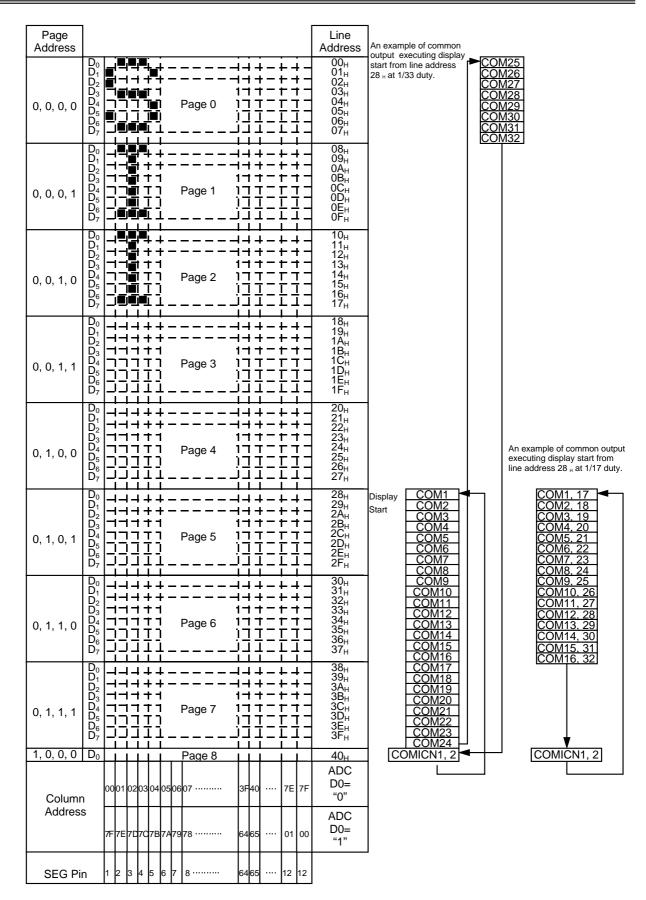

### 7. Display Data RAM

The S-4544A has Display Data RAM (8-bits  $\times$  8-pages x 128 columns +128 columns =8320 bits]. It is possible to use the not-used area for display as normal SRAM. The Display /data RAM is made of dual-port RAM. The read/write access form the MPU interface is performed independently of the read access to the LC display.

At the moment power is turned on, the contents of the Display Data RAM are uncertain. Following turning on power, write "0" in all bits of the Display Data RAM or write the display data with display OFF and then turn the display ON.

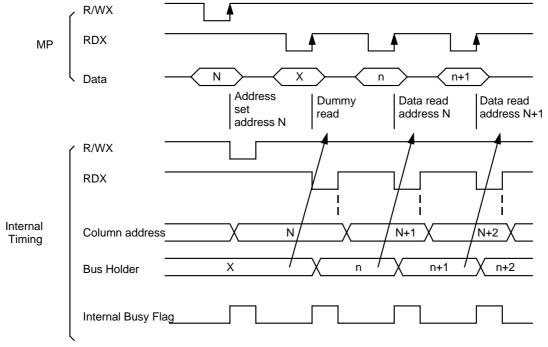

#### 8. Reading and Writing Display Data From MPU

The S-4544A reads and writes the display data through the internal bus holder. The display data is read to the bus holder from the Display Data RAM, and in the next read cycle on the data bus. Therefore, a dummy read cycle is needed before the first read cycle. When reading the display data after the column address set and the data write cycle, a dummy read is needed. Since the reading of the display data is executed using this bus holder, it is possible to read the data at high speed.

Display data is written to the Display Data RAM through the bus holder within a write cycle. Therefore, writing the display data does not need a dummy cycle.

After executing READ and WRITE commands, the column address is incremented by 1. When the cycle time represented with timing characteristics is met, READ and WRITE commands can be executed in succession. Increment of the column address stops at the upper address of the Display Data RAM.

### 9. Column Address

The column address of the Display Data RAM is used for reading/writing displayed data from/to the MPU. The column address is set by a command. When the displayed data RAM is accessed by the MPU, the address increments by one.

### 10. Page Address

The display RAM is composed of nine pages. When accessing the Display Data RAM from MPU, the page of the Display Data RAM is set by a command.

| Page D3 | D2 | D1 | D0 |   |                                 |

|---------|----|----|----|---|---------------------------------|

| 0       | 0  | 0  | 0  | 0 | Graphic display area            |

| 1       | 0  | 0  | 0  | 1 | Graphic display area            |

| 2       | 0  | 0  | 1  | 0 | Graphic display area            |

| 3       | 0  | 0  | 1  | 1 | Graphic display area            |

| 4       | 0  | 1  | 0  | 0 | Graphic display area            |

| 5       | 0  | 1  | 0  | 1 | Graphic display area            |

| 6       | 0  | 1  | 1  | 0 | Graphic display area            |

| 7       | 0  | 1  | 1  | 1 | Graphic display area            |

| 8       | 1  | 0  | 0  | 0 | Icon (annunciator) display area |

### 11. Display Start Line Address

The display start line address is a read start address of the Display Data RAM which corresponds to the COM0 output. Set the display start line address with the corresponding command. Use the Display Start Line Address set command in changing the display page or smooth scroll.

### 12. Reading the Display Data to LCD Panel

Regardless of the state of the MPU, the S-4544A reads the data to the LCD panel. That is, it reads a 1-line of the display data specified with the line address from the Display Data RAM to the display data latch in the display drive side. After reading 1-line address, the S-4544A increments the line address in synchronization with the common output. After reading 1-frame line address, the S-4544A reads the display data from the display start line address again.

### 13. Display Data Latch

The display data latch is the circuit for latching one line's display data from the Display Data RAM. The display data is output from this latch to the LCD drive circuit. Since the display ON/OFF, the display All-Lit ON/OFF and Display Normal/Reverse control the display data latch, it has no effect on the display RAM data.

### 14. CR Oscillation Circuit

A built-in CR oscillation circuit generates a fundamental clock which conforms to the display timing. The oscillating frequency "fosc" is approximately 18 kHz, when Rf=1  $M\Omega$ . Operation through external clock is possible when external clock is input to OSC1, and OSC2 is "Open"

| Frame Frequency |          |                            |  |  |  |  |  |

|-----------------|----------|----------------------------|--|--|--|--|--|

| 1/17 duty       | 66.17 Hz | at fosc = 18 kHz           |  |  |  |  |  |

| 1/33 duty       | 68 18 Hz | at fosc = $18  \text{kHz}$ |  |  |  |  |  |

#### 15. LCD Drive Circuit

Has LCD drive output pins (i.e., 32 for common output, 2 for icon common, and 128 for segment output) and generates a 2-frame AC drive waveform (type B). 2 icon common output pins which are configured oppositely to the chip generate a drive waveform at the same timing. The icon display can be assigned the top or the bottom of the LCD panel. When the icon display is in no use, turn the icon common output to "Open."

### 16. LCD Power Supply Circuit

The LCD power supply circuit consists of a doubler/tripler, an LCD voltage adjustment circuit, an LCD bias resistor, and a voltage follower. The LCD voltage adjustment circuit consists of a voltage regulator and an LCD voltage command fine adjustment circuit. The LCD power supply circuit can be controlled by pins FNC1 and 2 and the LCD power supply circuit ON/OFF command. Internal or external power supply for the doubler/tripler, voltage regulator, and LCD voltage adjustment circuit can be changed with pins FNC1 and 2.

When turning OFF the LCD power supply circuit with the ON/OFF command, the S-4544A can stop the LCD power supply circuit.

When turning OFF all of built-in LCD power supply circuits with FNC1 = "L," FNC2 = "H," the LCD power supply circuit, however, can run at LCD bias voltage V1 through V5 generated by external bias resistors.

| FNC1 | FNC2 | Doubler/<br>Tripler | Voltage<br>Regulator | Voltage Follower/<br>LCD Bias Resistor | Notes                                          |

|------|------|---------------------|----------------------|----------------------------------------|------------------------------------------------|

| L    | L    | Valid               | Valid                | Valid                                  | Use all of internal LCD power supply circuits. |

| L    | Н    | Invalid             | Invalid              | Invalid                                | Use external bias resistors.                   |

| Н    | L    | Invalid             | Valid                | Valid                                  | Use the external power supply circuit.         |

| Н    | Н    | Invalid             | Invalid              | Valid                                  | Externally create and input V5 voltage.        |

Notes:

- Always connect FNC1 and 2 to VDD or VSS.

- Externally-connected pins VOUT and V1 through V5 are not used as a drive power supply of other circuit.

- Externally connecting the power supply, with the built-in LCD power supply circuit ON may lead to a breakdown.

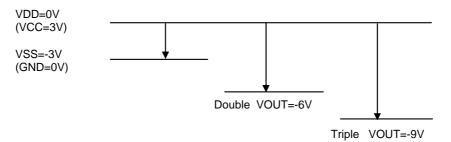

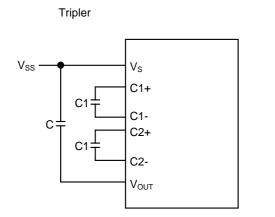

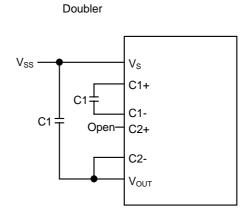

#### 16.1 Doubler/Tripler

The voltage is boosted below VDD on a VDD basis and output to the VOUT.

To boost the voltage 3 times, connect a specified capacitor between C1+ and C1-, C2+ and C2-, and VSS and VOUT. Use the booster in the range of VSS=-2.4 to -3.6V.

To boost the voltage twice, connect a capacitor between C1+ and C1- as well as between VSS and VOUT, and connect C2- to VOUT. Turn C2+ to "Open." Use the booster in the range of VSS=-2.4 to -5.5V.

Figure Example of Booster Output

### 16.2 LCD Voltage Adjustment

There are two methods of adjusting the LCD voltage as follows:

# 16.2.1 Voltage Regulator

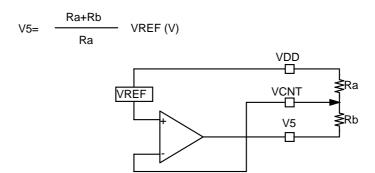

Voltage regulator output V5 is adjusted by externally-attached Ra and Rb.

V5 can be calculated as a resistor division ratior of built-in reference voltage VREF. The VREF with a temperature characteristics from approximately - 0.13%/°C to +0.01%/°C can compensate the LCD temperature characteristics. The value of the VREF differs depending upon the temperature compensation coefficient of the reference voltage for which the command is selected.

When a volume resistance is used in the resistor, V5 can be set variably. Feedback voltage noises occurring at the  $V_{CNT}$  pin directly affects on V5. Take appropriate measures against noises.

#### 16.2.2 LCD Voltage Command Fine Adjustment Circuit

The contrast can be adjusted by adjusting V5. It is also adjusted through a corresponding command input. V5 is set by the lower 4 bits of the data bus and can be adjusted to 16 steps. It is effective to adjust V5 together with the LCD voltage command fine adjustment circuit and the voltage regulator. First, set the fine adjustment data to (0, 1, 1, 1) or (1, 0, 0, 0), and adjust to the optimum contrast using a voltage regulator. The values Ra and Rb are calculated from the fine adjustment voltage width and minimum voltage of V5 to be set. When the LCD voltage command fine adjustment circuit is not in use, set the minimum voltage to (0, 0, 0, 0).

| _D3    | D2     | D1     | D0     | V5                      |         |

|--------|--------|--------|--------|-------------------------|---------|

| 0      | 0      | . 0    | 0      | Minimum Voltage Setting | Default |

| 0<br>1 | 1<br>0 | 1<br>0 | 1<br>0 |                         |         |

| 1      | 1      | :<br>1 | 1      | Maximum Voltage Setting |         |

### 16.3 LCD Bias Voltage

A built-in LCD bias resistor creates bias voltage for the LCD drive. The LCD bias can be selected among 1/6.7, 1/5, and 1/4 with the corresponding command. Since the bias voltage is supplied via the voltage follower to the LCD driver, current consumption is significantly reduced.

When FNC1 is "L" and FNC2 is "H," it is possible to connect the externally-attached bias resistor directly to pins V1 through V5. A 1/2 or more bias ratio can be freely supplied as an LCD drive voltage. Regardless of the level, the voltage can be inputted to pins V1 through V4.

When using an externally-attached bias resistor, the S-4544A stops the voltage follower. Select an appropriate value of resistance of the bias resistor according to the size of the LCD panel and LC capacity.

#### 16.4 Voltage Follower

The voltage follower buffers the LCD bias voltage created by the built-in bias resistor, and supplies it to the LCD drive circuit. At the same time, the LCD bias voltage is output to pins V1 through V4. Thus, connect a capacitor in accordance with the size and capacity of the LCD panel to stabilize the LCD bias voltage. It is not possible to output the LCD bias voltage from pins V1 through V5 or supply the LCD bias voltage to other circuits.

### 16.5 Reference Voltage Circuit

The reference voltage circuit generates VREF reference voltage of the voltage regulator. There are two values of VREF depending upon the temperature coefficient. For details, refer to "COMMAND EXPLANATION, 20. Reference Voltage Temperature Compensation Coefficient Selection."

#### **■ INTERFACE**

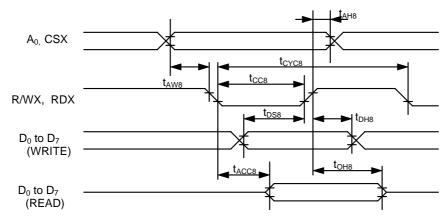

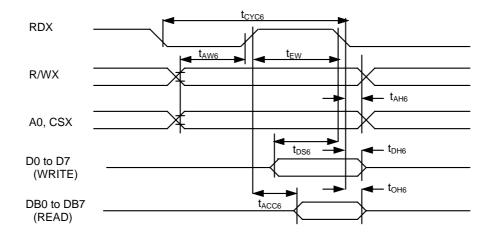

## 1. Parallel Interface

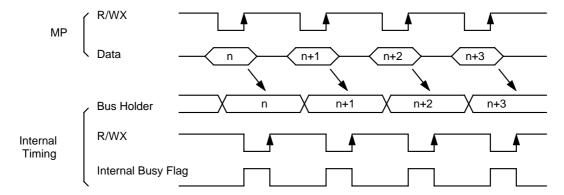

## 1.1 Display Data Write (Example of the 80-Family interface)

### 1.2 Display Data Read (Example of the 80-Family interface)

Figure4 Parallel Interface Examples

## 2. Serial interface

| A0 | R/WX | D0 (SDI)      | D2 (SDO)         |

|----|------|---------------|------------------|

| 0  | 0    | Command Write | Status Read      |

| 0  | 1    | Invalid       | Status Read      |

| 1  | 0    | Data Write    | Status Read      |

| 1  | 1    | Invalid       | Data Read (Note) |

|    |      |               |                  |

Note: Data Read needs a dummy read.

Figure 5 Serial interface Display Data Write/Read Timing

Figure 6 Display Data RAM vs Addresses

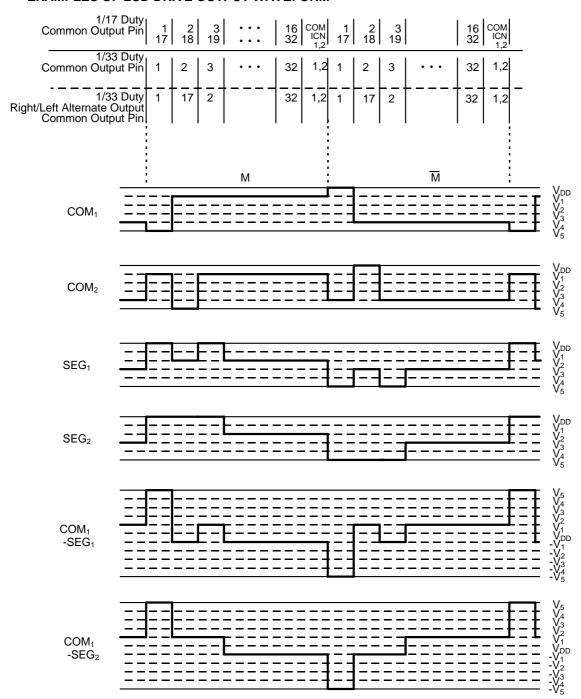

## ■ EXAMPLES OF LCD DRIVE OUTPUT WAVEFORM

Figure 7 Examples of LCD Drive Output Waveform 1/5 Bias

## ■ EXAMPLES OF EXTERNAL BIAS RESISTOR CONNECTION VS LCD DRIVE WAVEFORM

Figure 8 Examples of External Bias Resistors vs LCD Drive Waveform

#### **■ COMMAND EXPLANATION**

#### 1. Display ON/OFF

| Ī | A0 | RDX | R/WX | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|----|-----|------|----|----|----|----|----|----|----|----|

|   | 0  | 1   | 0    | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  |

D0:0: Regardless of the contents of the display data RAM, the LCD screen is compelled to be all-off (including the icon display).

D0:1: The LCD screen is compelled to be normally displayed in accordance with the contents of the display data RAM.

The state is changed to the "Power Save" after turning on the Display All-Lit ON with the display OFF.

### 2. Display Start Line

|   | A0 | RDX | R/WX | D7 | D6 | D5      | D4           | D3            | D2           | D1           | D0      |

|---|----|-----|------|----|----|---------|--------------|---------------|--------------|--------------|---------|

| ſ | 0  | 1   | 0    | 0  | 1  | D<br>A5 | isplay<br>A4 | Start I<br>A3 | Line A<br>A2 | ddress<br>A1 | 3<br>A0 |

| A5 | A4 | A3 | A2 | A1 | A0 | Line Address    |

|----|----|----|----|----|----|-----------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0               |

| 0  | 0  | 0  | 0  | 0  | 1  | 1               |

| •  |    |    | •  |    |    | •               |

|    | •  | •  | •  |    |    | •               |

|    |    |    |    |    |    | •               |

| 1  | 1  | 1  | 1  | 1  | 1  | 3F <sub>H</sub> |

The line address of the display data RAM indicating the display start line is set. The display start line corresponds to COM1. The display area read from the display data RAM corresponds to the number of the lines set by the Duty select command. The line address is automatically incremented in synchronization with the common output. Changing the display start line using this command allows for page change on the display screen as well as vertical smooth scroll.

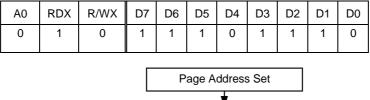

## 3. Page Address Set

|   | A0 | RDX | R/WX | D7 | D6 | D5 | D4 | D3 | D2    | D1    | D0 |

|---|----|-----|------|----|----|----|----|----|-------|-------|----|

| ĺ | 0  | 1   | 0    | 1  | 0  | 1  | 1  | Р  | age A | ddres | s  |

|   |    |     |      |    |    |    |    | A3 | A2    | A1    | A0 |

| A3 | A2 | A1 | A0 | Page |

|----|----|----|----|------|

| 0  | 0  | 0  | 0  | 0    |

| 0  | 0  | 0  | 1  | 1    |

| 0  | 0  | 1  | 0  | 2    |

|    |    |    |    | •    |

|    |    |    |    | •    |

| 0  | 1  | 1  | 1  | 7    |

| 1  | 0  | 0  | 0  | 8    |

The page address is set when accessing the display data RAM from the MPU. It is possible to access the display data RAM from the MPU with the page address and the column address commands. Even if the page address is changed, there is no change in the display screen during operation. Page 8 is assigned to the icon display. D0 only is valid.

### 4. Column Address Set

| A0   | RDX   | R/WX | D7 | D6  | D5   | D4 | D3                              | D2 | D1             | D0             |

|------|-------|------|----|-----|------|----|---------------------------------|----|----------------|----------------|

| 0    | 1     | 0    | 0  | 0   | 0    | 1  | 0                               |    | nn Ad<br>per 3 | dress:<br>bits |

|      |       |      |    |     |      |    |                                 | A6 | A5             | A4             |

| 0    | 1     | 0    | 0  | 0   | 0    | 0  | Column Address:<br>Lower 4 bits |    |                |                |

|      |       |      |    |     |      |    | А3                              | A2 | A1             | Α0             |

| Llnr | ner 3 | ·    | ·  | Low | or 4 | ·  |                                 | ·  | ·              |                |

| l  | Upper 3 | }  |    | Low | er 4 |    |                 |

|----|---------|----|----|-----|------|----|-----------------|

| A6 | A5      | A4 | А3 | A2  | A1   | A0 | Column Address  |

| 0  | 0       | 0  | 0  | 0   | 0    | 0  | 0 <sub>H</sub>  |

| 0  | 0       | 0  | 0  | 0   | 0    | 1  | 1 <sub>H</sub>  |

| •  | •       |    | •  |     | •    | •  | i               |

| •  | •       | •  | •  | •   | •    | •  | i               |

| •  | •       | •  | •  | •   | •    | •  | •               |

| 1  | 1       | 1  | 1  | 1   | 1    | 0  | 7E <sub>H</sub> |

| 1  | 1       | 1  | 1  | 1   | 1    | 1  | 7F <sub>H</sub> |

| 1  | 1       | 1  | 1  | 1   | 1    | 1  | 7F <sub>H</sub> |

The column address is set when accessing the display data RAM from the MPU. When accessing the display data RAM from the MPU, the column address is incremented. When accessing the successive column address from the MPU, it is possible to access the display data without setting the column address each time. The automatic increment stops at 7FH after accessing the top column address 7FH. The page address is not incremented.

While the Read Modify Write command is being executed, a set of Column Address Setting commands is neglected.

#### 5. Status Read

| A0 | RDX | R/WX | D7 | D6 | D5 | D4  | D3  | D2 | D1 | D0 |

|----|-----|------|----|----|----|-----|-----|----|----|----|

| 0  | 0   | 1    |    |    |    | Sta | tus |    |    |    |

D7: BUSY =0: Can accept a command.

=1: Internal operation or reset state. Does not accept a command.

D6 : ADC =0 : ADC Reverse

=1: ADC Normal

Make sure that this polarity is contrary to that of the ADC Select command.

D5 : ON/OFF=0 : Display ON

=1 : Display OFF

Make sure that this polarity is contrary to that of Display ON/OFF command.

D4 : RESET =0 : Normal display operation state

=1: Internal reset operation state with reset command.

D3 : PS =0 : Normal display operation state

=1: Power Save state

D2 : MD =0 : Normal display operation state

=1: Icon only display state

D1 : INVD =0 : Display Normal

=1: Display Reverse

D0 : FDM =0 : Normal display

=1: Display All-Lit ON

During power-save, display ON/OFF, PS and FDM are individually output.

When selecting a parallel interface, the status read can also be executed during reset operation.

When a serial interface is selected, the status read is invalid during reset operation. However, "H" is output from the SDO pin during reset operation.

#### 6. Write Data

| A0 | RDX | R/WX | D7 | D6    | D5      | D4      | D3      | D2   | D1  | D0 |

|----|-----|------|----|-------|---------|---------|---------|------|-----|----|

| 1  | 1   | 0    |    | Write | data ii | n the c | display | data | RAM |    |

The 8-bit display data is written in the display data RAM. After writing the display data, the column address is automatically incremented. To write the display data in succession after setting the 1st column address to be written by the COLUMN ADDRESS SETTING command, the column address is not needed to be set each time. The icon display data is valid for only D0.

#### 7. Read Data

| A0 | RDX | R/WX | D7 | D6   | D5   | D4     | D3     | D2     | D1    | D0 |

|----|-----|------|----|------|------|--------|--------|--------|-------|----|

| 1  | 0   | 1    |    | Read | data | from t | he dis | play d | ata R | λM |

The 8-bit display data is read from the display data RAM. After the display data is read, the column address is automatically incremented. To read the display data in succession after setting the 1st column address to be read by the COLUMN ADDRESS SETTING command, the column address is not needed to be set each time. When reading the display data immediately after setting the COLUMN ADDRESS SETTING, dummy read is needed once.

#### 8. ADC Select

| A0 | RDX | R/WX | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|-----|------|----|----|----|----|----|----|----|----|

| 0  | 1   | 0    | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

D0 : 0 Normal Clockwise output. Column addresses 00H to 7FH correspond to segment outputs 1 to 128.

D0 : 1 Reverse Counterclockwise output. Column addresses 00H to 7FH correspond to segment outputs 128 to 1.

Normal or reverse can be selected for the correlation between the column address of the display data RAM and the segment output terminal. The ADC Select command selects normal or reverse in accordance with the relationship between the column address of the display data RAM and the segment output. This minimizes restrictions in the segment output wiring and IC assignment.

### 9. Display Normal/Reverse

| A0 | RDX | R/WX | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|-----|------|----|----|----|----|----|----|----|----|

| 0  | 1   | 0    | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 0  |

D0 : 0 Normal Display data "1" makes the display be lit

D0 : 1 Reverse Display data "0" makes the display be lit

Lit or non-lit on each dot of the LCD panel can be reversed without rewriting the contents of the display data RAM.

The icon display is not reversed.

### 10. Display All-Lit ON/OFF

| A0 | RDX | R/WX | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|-----|------|----|----|----|----|----|----|----|----|

| 0  | 1   | 0    | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  |

The Display All-Lit ON command makes it possible to light the entire display regardless of the contents of the display data RAM. The display RAM data, however, does not change.

Through display all-lit OFF, the LCD screen returns to normal display operation and precedes the Display Normal/Reverse command.

When inputting the Display OFF command in the display all-lit ON state, it is changed to Power Save mode.

D0 : 0 Display All-Lit OFF Normal display

D0 : 1 Display All-Lit ON Forces the LCD panel to be entirely lit.

## 11. Duty Select, Alternate Common Output

| A0 | RDX | R/WX | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|-----|------|----|----|----|----|----|----|----|----|

| 0  | 1   | 0    | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  |

D0 : 0 1 / 17 Duty

D0 : 1 1 / 33Duty

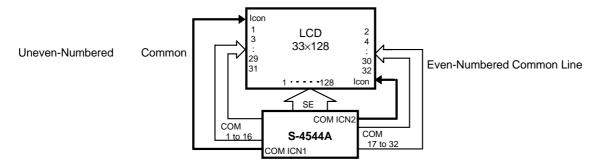

${\sf D1}$ : 0 The common is output to the common pin in a numerical order.

D1: 1 The common is alternately output to right and left of the chip.

## 11.1 1/17 Duty Common Output Order

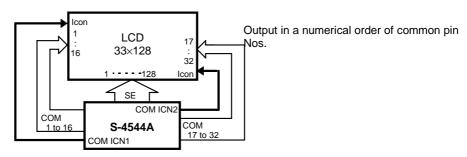

Output Order Output in accordance with Common Pin Nos.

|    | Output pin Nos. |  |

|----|-----------------|--|

| 1  | COM1, 17        |  |

| 2  | COM2, 18        |  |

| 3  | COM3, 19        |  |

| •  | •               |  |

| •  | •               |  |

| 15 | COM15, 31       |  |

| 16 | COM16, 32       |  |

| 17 | COMICN1, 2      |  |

|    |                 |  |

At 1/17 duty, the common is output according only to the pad No. Right and left alternate output are not set. Commons at right and left of the chip are simultaneously output.

### 11.2 1/33 Duty Common Output Order

| Output Order | Output in accordance with Common Pin Nos. Output pin Nos. | Right and Left Common Alternate Output Output pin Nos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | COM1                                                      | COM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2            | COM2                                                      | COM17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3            | COM3                                                      | COM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •            | •                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | •                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16           | COM16                                                     | COM9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17           | COM17                                                     | COM25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •            | ı                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | r                                                         | The state of the s |