# **Contents**

| Features                           | 1  |

|------------------------------------|----|

| Block Diagram                      | 1  |

| Terminal Description               | 2  |

| Operating Frequency                | 2  |

| Absolute Maximum Ratintgs          | 3  |

| DC Electrical Charasteristics      | 3  |

| AC Electrical Charasteristics      | 4  |

| Operation                          | 6  |

| Command                            | 13 |

| Frequency Characteristics          | 18 |

| Application Circuit Examples       | 19 |

| Connection Between Two LCD Drivers | 20 |

| LCD Panel Configuration            | 20 |

| Ordering Information               |    |

| Pad Layout                         |    |

# **DOT MATRIX LCD DRIVER**

The S-4520BA is a driver IC for use with a dot matrix LCD (Liquid Crystal Display). It has an 80 family/68 family MPU interface, a display RAM, a CR oscillation circuit, 61 segment driver output, and 16 common driver output. Since it features wide operating voltage range and low power consumption, it is suitable as an LCD driver for portable equipment.

#### **■** Features

- Wide operating voltage range

Logic power supply voltage: -2.4 to -7.0 V

LCD drive voltage: -3.5 to -13.0 V

- Built-in CR oscillation circuit: 18 kHz

- 61-segment, 16-common LCD driver circuit

- Built-in display RAM (8-bit×61-segment×4-page)

- 80 family/68 family MPU interface

- Duty ratio from 1/16 and 1/32 selectable

- Master mode and slave mode selectable

- Supply form Al pad chip Au bump chip

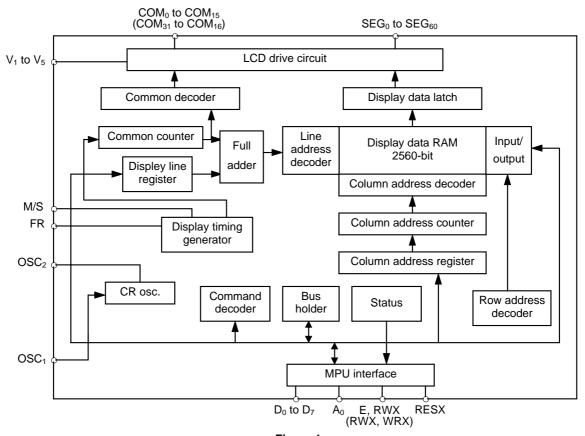

### ■ Block Diagram

Figure 1

# **■ Terminal Description**

Table 1

| Pin No.   | Name                                   | Description                                                                                                                                                                                                                     |  |  |  |  |

|-----------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 78        | V <sub>SS</sub>                        | egative power supply                                                                                                                                                                                                            |  |  |  |  |

| 87        | $V_{DD}$                               | Positive power supply                                                                                                                                                                                                           |  |  |  |  |

| 90 to 95  | V <sub>5</sub> to V <sub>1</sub>       | LCD drive power supply. Apply correct voltage to each terminal according to this order : $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5$                                                                                       |  |  |  |  |

| 73        | A <sub>0</sub>                         | Display data/display command switching input. Normally connect the last bit of MPU address bus. $A_0$ = "0": $D_0$ to $D_7$ are command inputs and status outputs. $A_0$ = "1": $D_0$ to $D_7$ are display data inputs/outputs. |  |  |  |  |

| 74        | OSC <sub>1</sub>                       | CR oscillation circuit input . Connect R <sub>f</sub> in master operation. NC in slave operation. [Note]  In 80 family, RDX and WRX are each OR'ed with CSX.  In 68 family, E is ANDed with the invert of CSX.                  |  |  |  |  |

| 75        | OSC <sub>2</sub>                       | CR oscillation circuit output or display clock input .  Master operation: CR oscillation circuit output. Connect R <sub>f</sub> .  Slave operation: Display clock input. Connect OSC <sub>2</sub> of the master IC.             |  |  |  |  |

|           | E                                      | Enable clock signal input (68 family MPU). Active "H".                                                                                                                                                                          |  |  |  |  |

| 76        | RDX                                    | Read signal input (80 family MPU). Active "L". RDX "L" puts the data bus in output status.                                                                                                                                      |  |  |  |  |

| 77        | R/WX                                   | Read/write signal input (68 family MPU).  R/WX= "H": Read  R/WX= "L": Write                                                                                                                                                     |  |  |  |  |

|           | WRX                                    | Write signal input (80 family MPU). Active "L".                                                                                                                                                                                 |  |  |  |  |

| 79 to 86  | D <sub>0</sub> to D <sub>7</sub>       | 3-state input/output. 8-bit bidirectional data bus connection pins.                                                                                                                                                             |  |  |  |  |

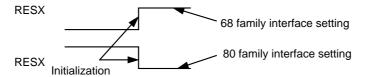

| 88        | RESX                                   | Interface mode selection and reset. The S-4520BA is reset at the rising and falling edge of RESX signal. Interface mode is selected by RESX level after the S-4520BA is reset.  RESX= "H"                                       |  |  |  |  |

| 89        | FR                                     | Alternating signal input/output.  M/S= "H": FR signal output  M/S= "L": FR signal input                                                                                                                                         |  |  |  |  |

| 93        | M/S                                    | Mode selection.  M/S= "H": Master mode  M/S= "L": Slave mode                                                                                                                                                                    |  |  |  |  |

| 12 to 72  | SEG <sub>60</sub> to SEG <sub>0</sub>  | Segment drive output.                                                                                                                                                                                                           |  |  |  |  |

| 96 to 100 | COM <sub>0</sub> to COM <sub>15</sub>  | Common drive output (master mode). Outputs from COM $_0$ to COM $_{15}$ . Scans from pin No.96 $\rightarrow$ 100 $\rightarrow$ 1 $\rightarrow$ 11.                                                                              |  |  |  |  |

| 1 to 11   | COM <sub>31</sub> to COM <sub>16</sub> | Common drive output (slave mode). Outputs from COM $_{16}$ to COM $_{31}$ . Scans from pin No.11 $\rightarrow$ 1 $\rightarrow$ 100 $\rightarrow$ 96.                                                                            |  |  |  |  |

# **■** Operating Frequency

Table 2

| Operating     | frequency      | Segment | Common | Note                                 |

|---------------|----------------|---------|--------|--------------------------------------|

| Internal osc. | External clock | driver  | driver |                                      |

| 18 kHz        | 18 kHz         | 61      | 16     | External clock is used only in slave |

|               |                |         |        | mode                                 |

# ■ Absolute Maximum Ratings

Table 3

| Parameter             | Symbol               | Ratings                      | Unit     |

|-----------------------|----------------------|------------------------------|----------|

| Supply voltage        | V <sub>SS</sub>      | -8.0 to +0.4                 | V        |

| LCD drive voltage 1   | $V_5$                | -14.5 to +0.4                | <b>V</b> |

| LCD drive voltage 2   | $V_1, V_2, V_3, V_4$ | V <sub>5</sub> to +0.4       | V        |

| Input voltage         | $V_{IN}$             | V <sub>SS</sub> -0.4 to +0.4 | V        |

| Output voltage        | $V_{OUT}$            | V <sub>SS</sub> -0.4 to +0.4 | V        |

| Power dissipation     | $P_D$                | 250                          | mW       |

| Operating temperature | T <sub>opr</sub>     | −30 to +85                   | °C       |

| Storage temperature   | T <sub>stg</sub>     | −65 to +150                  | °C       |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **■ DC Electrical Characteristics**

Table 4

|                               |                                 | (Unless otl                                         | nerwise specifi      | ed : V <sub>DD</sub> = | 0 V, V <sub>SS</sub> =-5. | 0±0.5 V | , Ta=-20 to 75 °C)                                                             |

|-------------------------------|---------------------------------|-----------------------------------------------------|----------------------|------------------------|---------------------------|---------|--------------------------------------------------------------------------------|

| Parameter                     | Symbol                          | Conditions                                          | Min.                 | Тур.                   | Max.                      | Unit    | Note                                                                           |

| Operating voltage             | V <sub>SS</sub>                 |                                                     | -7.0                 | -                      | -2.4                      | V       | Note 1, 2                                                                      |

| Recommended operating voltage | V <sub>SS</sub>                 |                                                     | -5.5                 | -5.0                   | -4.5                      | ٧       | Note 14                                                                        |

|                               | $V_5$                           |                                                     | -13.0                | -                      | -3.5                      | V       | Note 1, 2                                                                      |

| LCD drive voltage             | $V_1$ , $V_2$                   |                                                     | 0.6×V <sub>5</sub>   | -                      | $V_{DD}$                  | V       |                                                                                |

|                               | V <sub>3</sub> , V <sub>4</sub> |                                                     | V <sub>5</sub>       | -                      | 0.4×V <sub>5</sub>        | V       |                                                                                |

| High level input voltage      | $V_{\text{IHT}}$                |                                                     | V <sub>SS</sub> +2.0 | -                      | $V_{DD}$                  | V       | Note 3, 13                                                                     |

| - ngi i o roi input roitago   | $V_{IHC}$                       |                                                     | 0.2×V <sub>SS</sub>  | -                      | $V_{DD}$                  | V       | Note 4, 13                                                                     |

| Low level input voltage       | $V_{ILT}$                       |                                                     | V <sub>SS</sub>      | -                      | V <sub>SS</sub> +0.8      | V       | Note 3, 13                                                                     |

| 2011 lovel input veitage      | $V_{ILC}$                       |                                                     | $V_{SS}$             | -                      | 0.8×V <sub>SS</sub>       | V       | Note 4, 13                                                                     |

| High level output             | $V_{OHT}$                       | I <sub>OH</sub> =-3.0 mA                            | V <sub>SS</sub> +2.4 | -                      | -                         | V       | Note 5                                                                         |

| voltage                       | V <sub>OHC1</sub>               | I <sub>OH</sub> =-2.0 mA                            | V <sub>SS</sub> +2.4 | -                      | -                         | V       | FR                                                                             |

| voitage                       | $V_{OHC2}$                      | I <sub>OH</sub> =-120 μA                            | 0.2×V <sub>SS</sub>  | -                      | -                         | V       | OSC <sub>2</sub>                                                               |

| Low level output              | $V_{OLT}$                       | I <sub>OL</sub> =3.0 mA                             | -                    | -                      | V <sub>SS</sub> +0.4      | V       | Note 5                                                                         |

| voltage                       | $V_{OLC1}$                      | I <sub>OL</sub> =2.0 mA                             | -                    | -                      | V <sub>SS</sub> +0.4      | V       | FR                                                                             |

| voltage                       | $V_{OLC2}$                      | I <sub>OL</sub> =120 μA                             | -                    | -                      | 0.8×V <sub>SS</sub>       | V       | OSC <sub>2</sub>                                                               |

| Input leakage current         | I <sub>IL</sub>                 |                                                     | -1.0                 | -                      | 1.0                       | μΑ      | Note 6                                                                         |

| Output leakage current        | I <sub>OL</sub>                 |                                                     | -3.0                 | -                      | 3.0                       | μΑ      | Note 7                                                                         |

| LCD driver ON                 |                                 | V <sub>5</sub> =-5.0 V                              | -                    | 5.0                    | 7.5                       | kΩ      | SEG <sub>0</sub> to SEG <sub>61</sub><br>COM <sub>0</sub> to COM <sub>15</sub> |

| resistance                    | R <sub>ON</sub>                 | Ta=25°C $V_5=-3.5 \text{ V}$                        | -                    | 10.0                   | 50.0                      | kΩ      | Note 8                                                                         |

| Standby current               | Is                              |                                                     | -                    | 0.05                   | 1.0                       | μΑ      | Note 9                                                                         |

| Current consumption           | I <sub>DD1</sub>                | During display, $V_{5}=-5.0V$ $R_{f}=1$ $M\Omega$   | -                    | 9.5                    | 15.0                      | μΑ      | Note 10                                                                        |

| Current consumption           | I <sub>DD2</sub>                | During access, t <sub>CYC</sub> =20 kHz             | 0 -                  | 300                    | 500                       | μΑ      | Note 11                                                                        |

| Oscillating frequency         | fosc                            | $R_f=1.0 M\Omega$ , $V_{SS}=-5.0 V$                 | 15                   | 18                     | 21                        | kHz     |                                                                                |

| Oscillating frequency         | iosc                            | $R_f=1.0 \text{ M}\Omega$ , $V_{SS}=-3.0 \text{ V}$ | 11                   | 16                     | 21                        | kHz     |                                                                                |

| Reset time                    | t <sub>R</sub>                  |                                                     | -                    | -                      | 1000                      | μs      | Note 12                                                                        |

- Note 1 Make sure  $V_{DD_1}V_1,V_2,V_3,V_4$ , and  $V_5$  have the relationship:  $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5$ .

- Note 2 Drastic fluctuation by power supply voltage, input signal voltage noise, etc. causes malfunction and normal operation can not be guaranteed. In any case, avoid intentionally changing the power supply voltage during operation.

- TTL input pins:  $A_0$ ,  $D_0$  to  $D_7$ , E(RDX), R/WX(WRX). CMOS input pins: FR, M/S, RESX. Note 3

- Note 4

- Note 5  $D_0$  to  $D_7$

- Input pins: A<sub>0</sub>, E(RDX), R/WX(WRX), OSC<sub>1</sub>,OSC<sub>2</sub>(slave mode), M/S, RESX. Note 6

- Input and output pins at high impedance: FR, D<sub>0</sub> to D<sub>7</sub>. Note 7

- This is the resistance when applying 0.1 V between the LCD drive output pins (SEG<sub>0</sub> to SEG<sub>60</sub>, COM<sub>0</sub> to COM<sub>15</sub>) and Note 8 the LCD drive power pins (V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, and V<sub>4</sub> pins). R<sub>ON</sub> is measured between the LCD drive power pins and the LCD drive output pins whose electric potential is the same as that of the LCD drive power pins.

- Note 9 Current consumption when circuits, for example the oscillation circuit, the MPU interface, etc, are not operating.

- Note 10 Current consumption by LCD panel and parasitic capacitance is not included.

- Note 11 Current consumption when writing vertically-striped display data at t<sub>CYC</sub>=200 kHz. After the termination of command, the current consumption value is I<sub>DD1</sub>.

- Note 12 Reset time is from the point where RESX changed to the time when the reset operation is over and normal operation becomes available.

- Note 13 This is the inversion level of the input signal. Make the input signal go through the entire power supply voltage range applied for the S-4520BA. If the input signal does not go the full range, current consumption will increase.

- Note 14 When using a power supply voltage other than  $-5.0\pm0.5$  V, the value is different. Check the power supply voltage.

#### ■ AC Electrical Characteristics

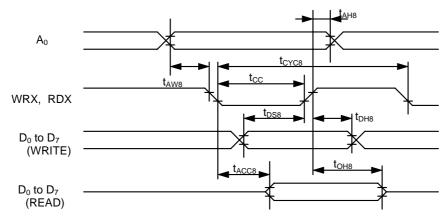

- 1. Raed/write with 80 family MPU

- V<sub>SS</sub>=-5 V

Table 5

(Ta=-20 to 75 °C,  $V_{SS}$ =-5 V±10%)

| Parameter           | Sym.              | Signal         | Conditions | Min.     | Max.   | Unit  |

|---------------------|-------------------|----------------|------------|----------|--------|-------|

| i arameter          | Oyiii.            | Olgilai        | Conditions | IVIII I. | iviax. | Offic |

| Address hold time   | t <sub>AH8</sub>  | ^              |            | 10       |        | ns    |

| Address setup time  | t <sub>AW8</sub>  | $A_0$          |            | 20       |        | ns    |

| System cycle time   | t <sub>CYC8</sub> | WDV DDV        |            | 1000     |        | ns    |

| Control pulse width | t <sub>CC</sub>   | WRX, RDX       |            | 200      |        | ns    |

| Data setup time     | t <sub>DS8</sub>  |                |            | 100      |        | ns    |

| Data hold time      | t <sub>DH8</sub>  | D ( D          |            | 10       | _      | ns    |

| RDX access time     | t <sub>ACC8</sub> | $D_0$ to $D_7$ | CL=100pF   | _        | 110    | ns    |

| Output disable time | t <sub>OH8</sub>  |                | CL=100pF   | 50       | 130    | ns    |

V<sub>SS</sub>=-3 V

Table 6

(Ta=-20 to 75 °C,  $V_{SS}$ =-3 V±10%)

| Parameter           | Sym.              | Signal         | Conditions | Min. | Max. | Unit |

|---------------------|-------------------|----------------|------------|------|------|------|

| Address hold time   | t <sub>AH8</sub>  | ^              |            | 20   |      | ns   |

| Address setup time  | t <sub>AW8</sub>  | $A_0$          |            | 40   |      | ns   |

| System cycle time   | t <sub>CYC8</sub> | WDV DDV        |            | 2000 | _    | ns   |

| Control pulse width | t <sub>CC</sub>   | WRX, RDX       |            | 400  | _    | ns   |

| Data setup time     | t <sub>DS8</sub>  |                |            | 200  | _    | ns   |

| Data hold time      | t <sub>DH8</sub>  | D 45 D         |            | 20   | _    | ns   |

| RDX access time     | t <sub>ACC8</sub> | $D_0$ to $D_7$ | CL=100pF   |      | 220  | ns   |

| Output disable time | t <sub>OH8</sub>  |                | CL=100pF   | 25   | 260  | ns   |

Figure 2 Read/write timing with 80 family MPU

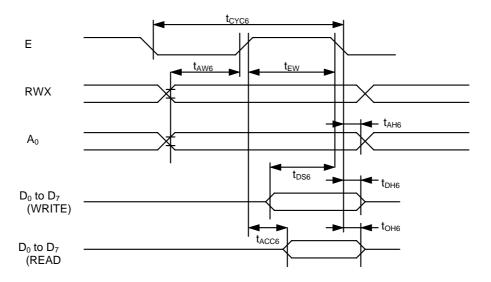

# 2. Read/write with 68 family MPU

• V<sub>SS</sub>=-5 V

Table 7

(Ta=-20 to 75 °C,  $V_{SS}$ =-5  $V\pm10\%$ )

| Parameter           | Sym.              | Signal         | Conditions | Min. | Max. | Unit |

|---------------------|-------------------|----------------|------------|------|------|------|

| System cycle time   | t <sub>CYC6</sub> | _              |            | 1000 |      | ns   |

| Address hold time   | t <sub>AH6</sub>  | A <sub>0</sub> |            | 10   | _    | ns   |

| Address setup time  | t <sub>AW6</sub>  | RWX            |            | 60   | _    | ns   |

| Data setup time     | t <sub>DS6</sub>  |                |            | 100  | _    | ns   |

| Data hold time      | t <sub>DH6</sub>  | D ( D          |            | 10   | _    | ns   |

| Access time         | t <sub>ACC6</sub> | $D_0$ to $D_7$ | CL=100pF   | _    | 110  | ns   |

| Output disable time | t <sub>OH6</sub>  |                | CL=100pF   | 50   | 130  | ns   |

| Enable pulse width  | t <sub>EW</sub>   | Е              | READ       | 120  | _    | ns   |

| Litable pulse width | LEW               | =              | WRITE      | 120  | _    | ns   |

• V<sub>SS</sub>=-3 V

#### Table 8

(Ta=-20 to 75 °C,  $V_{SS}$ =-3  $V\pm10\%$ )

| Parameter           | Sym.              | Signal         | Conditions | Min. | Max. | Unit |

|---------------------|-------------------|----------------|------------|------|------|------|

| System cycle time   | t <sub>CYC6</sub> | _              |            | 2000 |      | ns   |

| Address hold time   | t <sub>AH6</sub>  | A <sub>0</sub> |            | 20   |      | ns   |

| Address setup time  | t <sub>AW6</sub>  | RWX            |            | 120  | _    | ns   |

| Data setup time     | t <sub>DS6</sub>  |                |            | 220  | _    | ns   |

| Data hold time      | t <sub>DH6</sub>  |                |            | 20   | _    | ns   |

| Access time         | t <sub>ACC6</sub> | $D_0$ to $D_7$ | CL=100pF   | _    | 220  | ns   |

| Output disable time | t <sub>OH6</sub>  |                | CL=100pF   | 25   | 260  | ns   |

| Enoble pulse width  | +                 | Е              | READ       | 240  |      | ns   |

| Enable pulse width  | t <sub>EW</sub>   |                | WRITE      | 240  |      | ns   |

Figure 3 Read/write timing with 68 family MPU

### ■ Operation

#### 1. Power-on

After power-on, initialization is executed by either the rising or the falling edge of the RESX input. MPU Interface mode is selected by the level after RESX signal changes.

When initialization by RESX and the selection of an interface are not executed at power-on, a malfunction may occur. Since chattering in RESX causes poor initialization and erroneous selection of MPU interface, input the signal without chattering. For details, refer to Reset and MPU Interface Selection in this section.

#### 2. Reset

The S-4520BA can be initialized through RESX input or Reset command.

**Duty Select**

**ADC Select**

8

Read Modify Write

The initialization items through RESX input are listed in Table 9. Initialization through RESX input is executed at the signal change point, either rising or falling. At that time, it is possible to select the MPU Interface. When executing RESX input during operation at power-on, it is necessary to set the signal polarity to fixed MPU. Initialization through Reset command executes ②, ④, and ⑤ in Table 9. Be aware of the difference in initialization items between reset through RESX input and initialization through Reset command.

|     | Item                   | Status |

|-----|------------------------|--------|

| ①   | Display                | OFF    |

| 2   | Display Start Line Set | 1st    |

| 3   | Display all-lit        | OFF    |

| 4   | Column Address Counter | 0      |

| (5) | Page Address Register  | 3      |

|     |                        |        |

Table 9 Initialization at power-on

### 3. MPU interface selection

The selection of the S-4520B Series interface is determined by RESX signal logic after RESX signal input. It is possible to connect directly to either the 68 family or the 80 family MPU.

1/32

**OFF**

Forward

Table 10

| Interface | Pin            |     |      |                                |  |

|-----------|----------------|-----|------|--------------------------------|--|

|           | 73             | 76  | 77   | 79~86                          |  |

| 68 family | A <sub>0</sub> | E   | R/WX | D <sub>0</sub> ~D <sub>7</sub> |  |

| 80 family | $A_0$          | RDX | WRX  | D <sub>0</sub> ~D <sub>7</sub> |  |

#### 4. Status

The internal operation status of S-4520BA is monitored for four kinds of status. The status is output in  $D_4$  through  $D_7$ . For the monitoring method and function, refer to the Command functions section.

Table 11

| Item              | Output pin     |                         | Status                             |

|-------------------|----------------|-------------------------|------------------------------------|

| Busy flag         | $D_7$          | "1": Command operation, | Reset operation "0": Command ready |

| ADC select        | $D_6$          | "1": Forward            | "0": Reverse                       |

| Display<br>ON/OFF | D <sub>5</sub> | "1": Display all-lit    | "0": Normal display status         |

| Reset             | $D_4$          | "1": Resetting          | "0": Normal operation status       |

# 5. Busy flag

During internal operation, for example command operation, the busy flag is "1", and commands other than Status Read are not received. The Busy flag is output in D7 through the Status Read command. When accessing the S-4520BA by the signal which specifies the value of read cycle and write cycle timing, the busy flag "0" is not required to be confirmed.

#### 6. Data bus

Table 12

|       | 68 family<br>R/WX | 80 fa | amily | Operation                         |  |  |

|-------|-------------------|-------|-------|-----------------------------------|--|--|

| $A_0$ |                   | RDX   | WRX   | Operation                         |  |  |

| 1     | 1                 | 0 1   |       | Read from Display Data RAM        |  |  |

| 1     | 0                 | 1     | 0     | Write to Display Data RAM         |  |  |

| 0     | 1                 | 0     | 1     | Status Read                       |  |  |

| 0     | 0                 | 1 0   |       | Command Read to internal register |  |  |

#### 7. Display Data RAM

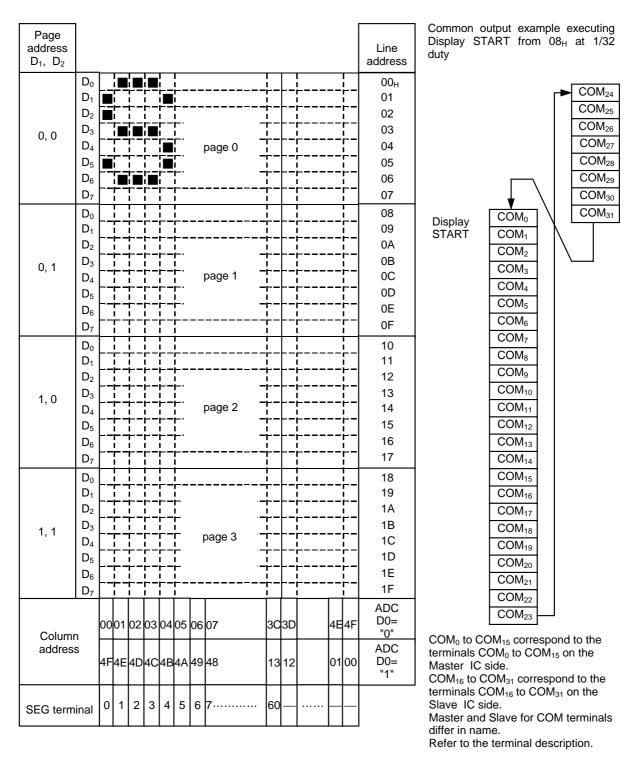

The S-4520BA has Display Data RAM (8 bits X 4 pages X 80 columns=2560 bits). As the memory area for display, 8 bits X 4 pages X 61 columns (segments)=1952 bits is valid. It is possible to use the not-used area for display as normal SRAM. The Display Data RAM is in dual port RAM and enables access from the MPU through Page address and Column address. To the LCD driver side, the one line's common output is read by Line address. The correspondence between Page address, Column address, and Line address is shown in Figure 6.

Display data reading /writing from/to the MPU interface and display data reading to the LCD display are executed independently; one is executed through command, the other is executed synchronizing with the LCD display clock.

At power-on, the display RAM data is not fixed. After power-on, clear the display RAM or write the display data with display OFF and turn the display ON.

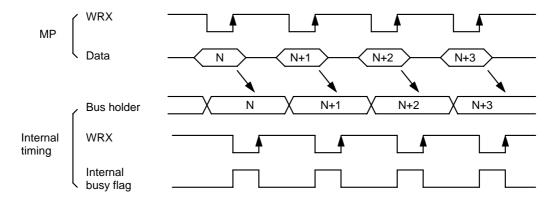

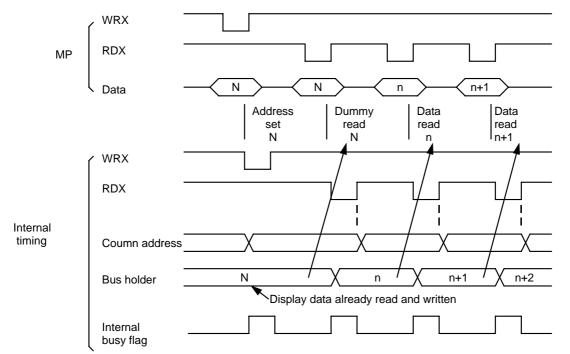

## 8. Reading and writing of display data

The S-4520BA reads and writes the display data through the internal bus holder. The display data is read to the bus holder from the display data RAM, and in the next read cycle on the data bus. Therefore, a dummy read cycle is needed before the first read cycle. When reading the display data after the address set and the data write cycle, a dummy read is needed. Since the reading of the display data is executed using this bus holder, it is possible to read the data at high speed.

Display data is written to the display data RAM through the bus holder within a write cycle. Therefore, writing the display data does not need a dummy cycle.

#### 9. Column address

The column address of the display data RAM is that for writing and reading of the display data. Setting the column address is executed through a command. When accessing the display data RAM from the MPU, the address is incremented by one.

#### 10. Page address

The display RAM is composed of four pages. When accessing the display data RAM from MPU, the page of the display data RAM is set a command.

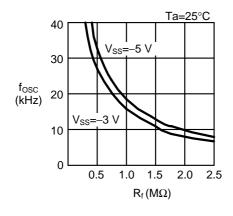

#### 11. CR oscillation circuit

The S-4520BA is built-in a CR oscillation circuit. Oscillation frequency is approximately 18 kHz at Rf 1M $\Omega$

#### 12. LCD drive circuit

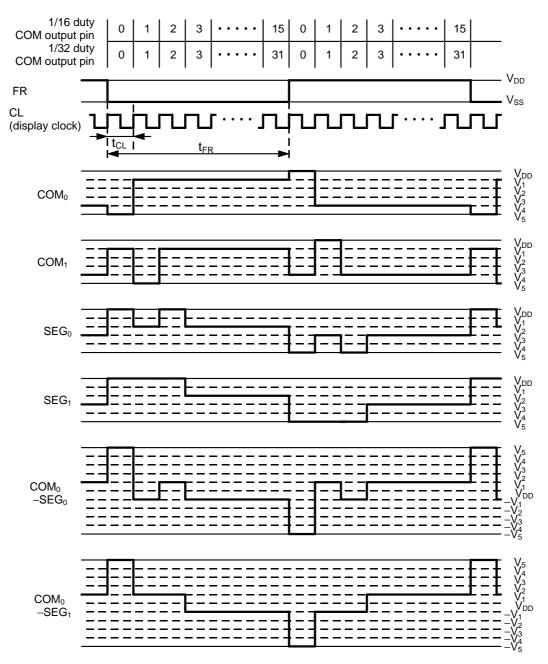

The S-4520BA has a 16 common and a 61 segment driver output. An LCD drive waveform which is a two-frame AC drive method (B) type is generated. Refer to Figure 7, LCD drive waveform.

#### 13. Display timing circuit

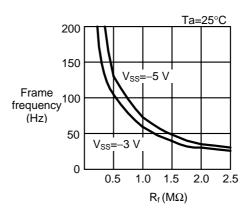

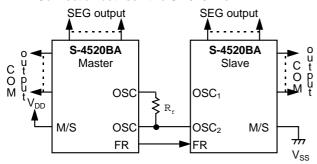

The display timing is generated by the clock using a CR oscillation circuit or an external clock, and a frame signal FR.

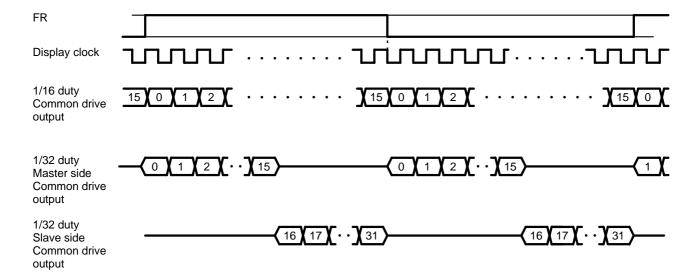

When configuring an LCD panel with more than two S-4520BA, the S-4520BA on the slave side syncronizes to the falling of FR signal. So, on the slave side of the S-4520, the LCD drive waveform is synchronized only by input of the FR signal on the master side. As shown in Figure 8, the display drive output on the slave side, after the common output COM15 on master side, is executed in COM16 through COM31. The FR signals are that of the duty 50 % of synchronized to the COM output timing.

#### 14. Line address

This is the address for reading the LCD RAM data to the LCD data latch. The line address is incremented synchronizing with the common output. The display start line is set with a command.

#### 15. Display data latch

The display data latch is the circuit for latching one line's display data from the display RAM. The display data is output from this latch to the LCD drive circuit. Since the display ON/OFF and the display all-lit ON/OFF control the display data latch, it has no effect on the display RAM data.

#### 16. Master/Slave selection

Master and slave selection is executed through the master/slave terminal logic. The Master IC and the Slave IC have different terminal functions.

Table 13

| Product name |        | M/S             | FR     | COM output                             | OSC <sub>1</sub> | OSC <sub>2</sub> |

|--------------|--------|-----------------|--------|----------------------------------------|------------------|------------------|

| S-4520BA     | Master | $V_{DD}$        | Output | COM <sub>0</sub> to COM <sub>15</sub>  | Input            | Output           |

|              | Slave  | V <sub>SS</sub> | Input  | COM <sub>31</sub> to COM <sub>16</sub> | NC               | Input            |

Note 1 CR oscillation circuit: In slave operation, OSC<sub>1</sub> is at high impedance. OSC<sub>2</sub> is connected to OSC<sub>2</sub> on the master side as a display clock input terminal.

Note 2 Common output: Master operation is output counterclockwise from terminal No.96 to No.11.

Slave operation is output clockwise from terminal No.11 to No.96.

Figure 4 Display data write timing (80 family interface)

Figure 5 Display data read timing (80 family interface)

Note: For the display data RAM of the S-4520BA, the memory area corresponding to SEG terminal 0 to 60 is valid as display data.

The other area is usable as normal SRAM.

Figure 6 Correspondence between display data and address

Figure 7 LCD driver waveform example

Note: Common drive output orders on the Master side and the Slave side

|             | Common drive output order       |

|-------------|---------------------------------|

| Master side | Counterclockwise from pad No.96 |

| Slave side  | Clockwise from pad No.11        |

Figure 8 FR and Common drive output waveform

Table 14 Column, frame cycle

| Item            | Display duty | Cycle |  |

|-----------------|--------------|-------|--|

| t <sub>CL</sub> | duty 1/16    | 16/f  |  |

| Column cycle    | duty 1/32    | 8/f   |  |

| t <sub>FR</sub> | duty 1/16    | 256/f |  |

| Frame cycle     | duty 1/32    | 256/f |  |

f=CR oscillation frequency

#### ■ Command

The S-4520BA can set the command functions with combinations of  $A_0$ , R/WX (68 family MPU), RDX and WRX (80 family MPU). The command setting is executed according to the internal timing. If the Display data read timing diagram, the Display data write timing diagram, and the timing characteristic diagram in the operation description are satisfied, it is possible to input through the commands without confirming the busy flag. Therefore, high speed operation and MPU load reduction are attainable. For the command list, refer to Table 17.

#### 1. Display ON/OFF

The logic  $D_0$  controls the display ON/OFF. In display OFF, the screen is compelled to be all-off regardless of the display RAM data. The display RAM data does not change.

In display ON, normal display is on according to the display RAM data. When the display ON command is input, display OFF is canceled.

When setting display all-lit ON in the display OFF status, it changes to Power save mode (see the Power Save command.)

#### 2. Display start line set

The line address of the display data RAM which indicates the display start line is set. The display start line corresponding to COM0, as shown in the figure, indicates the correspondence between the display data RAM and the address. The display area read from the display data RAM corresponds to the number of the lines for the duty set using the Duty select command. The line address is automatically incremented synchronizing with the common output. Changing the display START line using this command enables a smooth scroll on the screen or a page change.

#### 3. Page address set

The page address is set when accessing the display data RAM from the MPU. It is possible to access the display data RAM from the MPU using the page address and the column address. Refer to the figure which shows the correspondence between the display data RAM and the address. Even if the page address is changed, it has no influence, such as chaging of the screen during operation.

### 4. Column address set

The column address is set when accessing the display data RAM from the MPU. When accessing the display data RAM from the MPU, the column address is incremented by one. When accessing the successive column address from the MPU, it is possible to access the display data without setting the column address each time. The automatic increment stops at 80 after accessing the top column address 79. The page address is not incremented.

#### 5. Status read

It is possible to read four kinds of status using this command.

#### Table 19 Status

|        | Shows the command ready during the S-4520BA command operation.                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Busy   | "1": Shows that the IC inside is executing a command operation or a reset operation.  When the Busy flag is output, the command is not received. If the cycle time of the command is satisfied with the specified value, Busy flag confirmation is not needed.  "0": Shows that the command is ready |  |  |  |  |  |  |  |  |

| ADC    | Shows forward or reverse correspondence between column address and segment output terminal of the display data RAM  The setting is executed using the ADC select command.                                                                                                                            |  |  |  |  |  |  |  |  |

| ABO    | "1": Forward The column addresses 0 <sub>H</sub> to 3C <sub>H</sub> corresponds to the segment output terminals 0 to 60.  "0": Reverse The column address 13 <sub>H</sub> to 4F <sub>H</sub> corresponds to the segment output terminals 60 to 0.                                                    |  |  |  |  |  |  |  |  |

| ON/OFF | Shows the display ON/OFF status. Note: it is the reverse to the polarity of Display ON/OFF command.                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| ON/OFF | "0" : Shows the display ON status. Display normal operation status "1" : Shows the display OFF status. Display all-OFF status.                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|        | Shows that the S-4520BA is executing initialization by RESX input or Reset command.                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Reset  | "0" : Normal operation "1" : Reset operation                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

## 6. Write data

The 8-bit display data is written in the display data RAM. After writing the display data, the column address is automatically incremented. When writing the successive display data after setting the first column address Seiko Instruments Inc.

using the column address set command, it is unnecessary to set the column address each time.

#### 7. Read data

The 8-bit display data is read from the display data RAM. After reading the display data, the column address is automatically incremented. When reading the successive display data after setting the first column address using the column address set command, it is unnecessary to set the column address each time. For reading display data just after the column address set, a dummy read is needed.

#### 8. ADC select

Forward or reverse is selectable for the correspondence between the column address and the segment output terminal of the display data RAM. When configuring an LCD panel with more than two ICs, it is possible to reverse the segment output order from the MPU. Since the segment output terminals of an S-4520BA go from 0 to 60, the valid column address for the display data of the reverse select side IC is 13<sub>H</sub> to 4F<sub>H</sub>. Refer to the correspondence between the display data RAM and the address in Figure 6.

D<sub>0</sub> D: "0" Forward The column addresses 0<sub>H</sub> to 3C<sub>H</sub> correspond to the segment output terminals 0 to 60.

D: "1" Reverse The column addresses  $13_H$  to  $4F_H$  correspond to the segment output terminals 60 to

0.

#### 9. Display all-lit ON/OFF

Display all-lit ON makes the display be entirely lit. All common outputs become selectable status. Segment output is compelled to be all-lit output. The display RAM's data, however does not change.

Through Display all-lit OFF, the screen returns to normal display operation.

When inputting the Display OFF command in the display all-lit ON status, it changes to Power save mode. Refer to the Power save command.

#### 10. Duty select

The duty for the LCD drive output is selected.

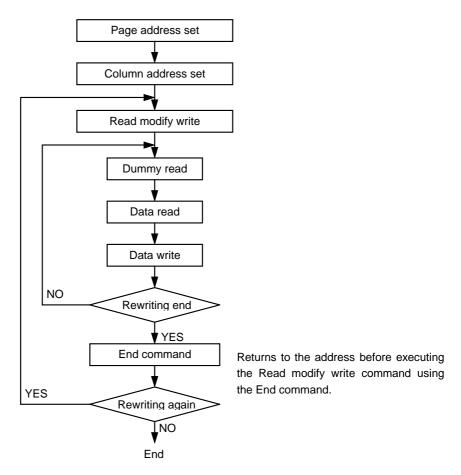

#### 11. Read modify write

The read modify write command is valid when partly altering or rewriting the display data RAM, for example the cursor indication, the blinking indication, etc. After inputting the Read modify write command, column address of the display data RAM is incremented only when inputting the display data write command. In Read data command, it is possible to rewrite the display data of the column address which is read, without increment of the column address. Furthermore, when reading and writing of the display data is successively executed, the successive address of the display data RAM is rewritten within the same page. A dummy read is needed when reading the display data.

Read modify write command is valid until the End command is input. When inputting the End command, the column address returns to the address before the Read modify command was input.

During the Read modify write command operation, all commands are usable except the Column address set command.

#### 12. End command

This command cancels Read modify write. The column address of the display data returns to the address before Read modify write was executed.

Figure 9 Command sequence for cursor indication

#### 13. Reset command

This command resets the address of the display data RAM as followings. After resetting, display starts according to the reset value.

- Resets the Display START Line to the 1st line.

- Resets the page address to 3.

Be aware that the functions are limited in comparison with resetting through the reset signal. At power-on, reset through the RESX input. For details, refer to the description of reset operation.

#### 14. Power Save mode

When setting display all-OFF using the Display OFF command and executing the Display all-lit ON command, it changes to the Power save mode. When displaying in all-lit status and executing the Display OFF command, it also changes to the Power save mode. In the Power save mode,

- Current consumption is reduced and a value near that at standstill is attainable.

- The LCD drive circuit is stopped. The Segment and Common outputs are fixed at V<sub>DD</sub> level.

- Input is prohibited and the OSC<sub>2</sub> terminal floats.

- Content of the display data RAM, the command and the address before the power save mode do not change.

The Power save status is canceled through the Display ON or the Display all-lit commands.

When the LCD driver voltage is generated by division of external resistance, the electric current is passed through this divided resistance regardless of the ICs. When reducing this current, attach a switching transistor which cuts the current flowing to the external resistance.

Table 16 Power save command

| Table to 1 over save command |                 |                          |  |  |  |  |  |  |  |

|------------------------------|-----------------|--------------------------|--|--|--|--|--|--|--|

| Command                      | combination     | Chahua                   |  |  |  |  |  |  |  |

| Dipslay                      | Display all-lit | Status                   |  |  |  |  |  |  |  |

| ON                           | OFF             | Normal display operation |  |  |  |  |  |  |  |

| ON                           | ON              | All-lit display          |  |  |  |  |  |  |  |

| OFF                          | OFF             | All-off                  |  |  |  |  |  |  |  |

| OFF                          | ON              | Power save               |  |  |  |  |  |  |  |

Table 17 Display commands

|                           |                |     |             |                |                | Code                                                                                                                                      |           |                |                 |                |                              |                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------------------------|----------------|-----|-------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|-----------------|----------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Command                   | A <sub>0</sub> | RDX | R/WX<br>WRX | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub>                                                                                                                            | $D_4$     | D <sub>3</sub> | D <sub>2</sub>  | D <sub>1</sub> | D <sub>0</sub>               | Function                                                                                                                                                                                                                                                                                                                            |  |  |

| Display ON/OFF            | 0              | 1   | 0           | 1              | 0              | 1                                                                                                                                         | 0         | 1              | 1               | 1              | 0 / 1                        | Selects normal display or all off on the screen.  D <sub>0</sub> : 1 ON. Normal display operation using the display data RAM.  D <sub>0</sub> : 0 OFF. Display OFF status regardless of the display RAM data. Power Save mode is entered by display OFF and display all-lit ON.                                                     |  |  |

| Display START<br>Line     | 0              | 1   | 0           | 1              | 1              | 0                                                                                                                                         | Displ     | •              | ART I<br>e Tabl | e 22)          | ldress                       | Sets the line address of the display data RAM to be displayed at the top line of the screen (COM <sub>0</sub> output). Address setting ranges from 0 to 31.                                                                                                                                                                         |  |  |

| Page Address<br>Set       | 0              | 1   | 0           | 1              | 0              | 1                                                                                                                                         | 1         | 1              | 0               | add<br>(S      | age<br>Iress<br>See<br>e 23) | Sets up the page address of the display data RAM in order to access the display data RAM from the MPU. Address setting ranges from 0 to 3.                                                                                                                                                                                          |  |  |

| Column<br>Address Set     | 0              | 1   | 0           | 0              |                |                                                                                                                                           |           |                | mn ad<br>Tabl   | dress<br>e 24) |                              | Sets up the column address of the display data RAM in order to access the display data RAM from the MPU. Address setting ranges from 0 to 79.                                                                                                                                                                                       |  |  |

| Status Read               | 0              | 0   | 1           | ≺ O C B        | A D C          | 0 N / 0 F F                                                                                                                               | R E S E T | 0              | 0               | 0              | 0                            | Reads the status. BUSY 1: Command operation 0: Command ready ADC 1: Column address forward 0: Column address invert 1: Display all-off status ON/OFF 0: Normal display status RESET 1: Resetting 0: Normal operation                                                                                                                |  |  |

| Write Display<br>Data     | 1              | 1   | 0           | Write Data     |                | Writes the data Do through Dr on the display data RAM.  Sets the display RAM's address using Page Address Set and Colum Address Set. When |           |                |                 |                |                              |                                                                                                                                                                                                                                                                                                                                     |  |  |

| Read Display<br>Data      | 1              | 0   | 1           |                |                |                                                                                                                                           | Read      | l Data         |                 |                |                              | Reads the data D <sub>0</sub> through D <sub>7</sub> from the display data RAM. accessing the display data RAM, the column addressis automatically incremented.                                                                                                                                                                     |  |  |

| ADC Select                | 0              | 1   | 0           | 1              | 0              | 1                                                                                                                                         | 0         | 0              | 0               | 0              | 0 / 1                        | Used to invert the column address of the display data RAM, after which the correspondence between the display RAM's addresses and segment output terminals is inverted.  D <sub>0</sub> : 0 Forward SEG0 terminal=column address 0 (00 <sub>H</sub> )  D <sub>0</sub> : 1 Invert SEG0 terminal=column address 79 (4F <sub>H</sub> ) |  |  |

| Display all-lit<br>ON/OFF | 0              | 1   | 0           | 1              | 0              | 1                                                                                                                                         | 0         | 0              | 1               | 0              | 0 / 1                        | Selects normal display operation or all-lit display operation.  D <sub>0</sub> : 0 Normal display operation  D <sub>0</sub> : 1 All-lit display operation  The screen is changed to all-lit status. Power Save mode is entered through display OFF and display all-lit ON.                                                          |  |  |

| Duty Select               | 0              | 1   | 0           | 1              | 0              | 1                                                                                                                                         | 0         | 1              | 0               | 0              | 0<br>/<br>1                  | Selects the LCD drive output duty. D <sub>0</sub> : 0 1/16 duty D <sub>0</sub> : 1 1/32 duty                                                                                                                                                                                                                                        |  |  |

| Read Modify<br>Write      | 0              | 1   | 0           | 1              | 1              | 1                                                                                                                                         | 0         | 0              | 0               | 0              | 0                            | Increments the column address of display data RAM only when display data is written but not when it is read.                                                                                                                                                                                                                        |  |  |

| End                       | 0              | 1   | 0           | 1              | 1              | 1                                                                                                                                         | 0         | 1              | 1               | 1              | 0                            | Cancels Read Modify Write mode and increments the column address of the display data RAM when display data is written and read.                                                                                                                                                                                                     |  |  |

| Reset                     | 0              | 1   | 0           | 1              | 1              | 1                                                                                                                                         | 0         | 0              | 0               | 1              | 0                            | Resets the address of the display data RAM as follows: • Resets the Display START Line to the 1st line. • Resets the page address to 3.                                                                                                                                                                                             |  |  |

Table 18 Display START line address

| $D_4$          | $D_3$          | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Line a Linea |

|----------------|----------------|----------------|----------------|----------------|--------------|

| A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | $A_0$          | Line address |

| 0              | 0              | 0              | 0              | 0              | 0            |

| 0              | 0              | 0              | 0              | 1              | 1            |

|                |                |                |                |                | •            |

|                | •              | •              | •              | •              | •            |

|                |                |                |                |                | •            |

| 1              | 1              | 1              | 1              | 1              | 31           |

Table 19 Page address

| D <sub>1</sub> | D <sub>0</sub> | Pago addross |  |  |  |

|----------------|----------------|--------------|--|--|--|

| A <sub>1</sub> | $A_0$          | Page address |  |  |  |

| 0              | 0              | 0            |  |  |  |

| 0              | 1              | 1            |  |  |  |

| 1              | 0              | 2            |  |  |  |

| 1              | 1              | 3            |  |  |  |

Table 20 Column address

| D <sub>6</sub> | D <sub>5</sub> | $D_4$ | $D_3$ | $D_2$          | D <sub>1</sub> | $D_0$ | Column address |

|----------------|----------------|-------|-------|----------------|----------------|-------|----------------|

| A <sub>6</sub> | A <sub>5</sub> | $A_4$ | $A_3$ | A <sub>2</sub> | A <sub>1</sub> | $A_0$ | Column address |

| 0              | 0              | 0     | 0     | 0              | 0              | 0     | 0              |

| 0              | 0              | 0     | 0     | 0              | 0              | 1     | 1              |

| •              |                |       |       |                |                |       | •              |

| •              | •              | •     | •     | •              | •              | •     | •              |

|                | •              |       |       |                |                |       | •              |

| 1              | 0              | 0     | 1     | 1              | 1              | 1     | 79             |

# **■** Frequency Characteristics

# 1. Oscillation frequency

# 2. Frame frequency

# ■ Application Circuit Examples

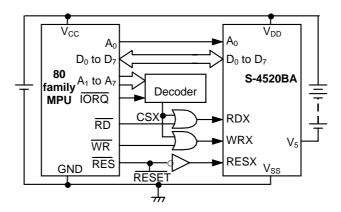

# 1. 80 family MPU interface

Note: S-4520BA has no CSX terminal. Logic for RDX and WRX must be set outside.

Figure 10

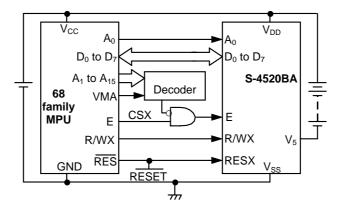

## 2. 68 family MPU interface

Note: S-4520BA has no CSX terminal. Logic for E must be set outside.

Figure 11

## ■ Connection Between Two LCD Drivers

1. Connection between two S-4520BAs

Figure 12

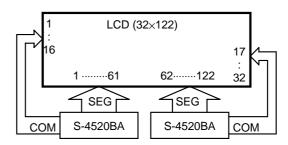

## **■ LCD Panel Configuration**

One character has 5x8 dots. One kanji has 16×16 dots.

1. 1/16 duty 12 characters, 2 lines

Figure 13

## 2. 1/16 duty 24 characters, 4 lines

Figure 14

# ■ Ordering Information

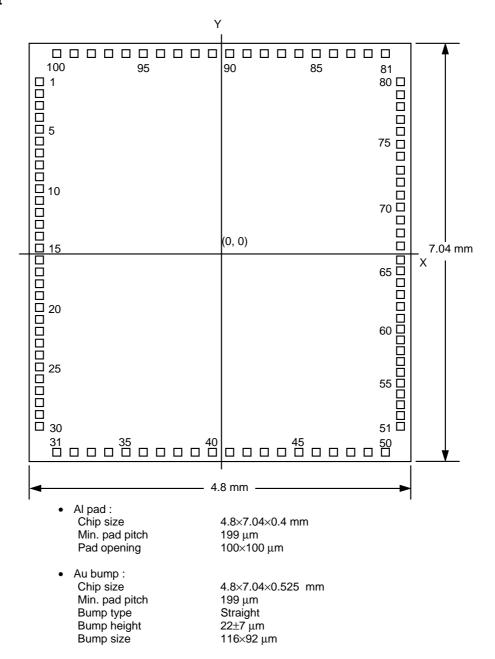

# ■ Pad Layout

Figure 15

Table 21 Pad coordinate

| PAD<br>No. | PAD<br>Name          | X (μm) | Y (μm) | PAD<br>No. | PAD<br>Name       | X (μm) | Υ (μm) | PAD<br>No. | PAD<br>Name          | X (μm) | Υ (μm) |

|------------|----------------------|--------|--------|------------|-------------------|--------|--------|------------|----------------------|--------|--------|

|            | COM <sub>5</sub>     |        |        | 30         | SEG <sub>42</sub> | -2241  | -3038  | 70         | SEG <sub>2</sub>     | 2241   | 827    |

| 1          | (COM <sub>26</sub> ) | -2241  | 2987   | 31         | SEG <sub>41</sub> | -1896  | -3361  | 71         | SEG₁                 | 2241   | 1027   |

|            | COM <sub>6</sub>     |        |        | 32         | SEG <sub>40</sub> | -1697  | -3361  | 72         | SEG <sub>0</sub>     | 2241   | 1269   |

| 2          | (COM <sub>25</sub> ) | -2241  | 2788   | 33         | SEG <sub>39</sub> | -1497  | -3361  | 73         | A <sub>0</sub>       | 2241   | 1528   |

|            | COM <sub>7</sub>     |        |        | 34         | SEG <sub>38</sub> | -1298  | -3361  | 74         | OSC₁                 | 2241   | 1728   |

| 3          | (COM <sub>24</sub> ) | -2241  | 2588   | 35         | SEG <sub>37</sub> | -1098  | -3361  | 75         | OSC <sub>2</sub>     | 2241   | 1927   |

|            | COM <sub>8</sub>     |        |        | 36         | SEG <sub>36</sub> | -899   | -3361  |            | Е                    |        | 2427   |

| 4          | (COM <sub>23</sub> ) | -2241  | 2389   | 37         | SEG <sub>35</sub> | -699   | -3361  | 76         | (RDX)                | 2441   | 2127   |

|            | COM <sub>9</sub>     |        |        | 38         | SEG <sub>34</sub> | -500   | -3361  | 77         | R/WX                 | 2441   | 2226   |

| 5          | (COM <sub>22</sub> ) | -2241  | 2199   | 39         | SEG <sub>33</sub> | -300   | -3361  | 77         | (WRX)                | 2441   | 2326   |

|            | COM <sub>10</sub>    |        |        | 40         | SEG <sub>32</sub> | -101   | -3361  | 78         | V <sub>SS</sub>      | 2241   | 2587   |

| 6          | (COM <sub>21</sub> ) | -2241  | 1990   | 41         | SEG <sub>31</sub> | 99     | -3361  | 79         | D <sub>0</sub>       | 2241   | 2787   |

|            | COM <sub>11</sub>    |        |        | 42         | SEG <sub>30</sub> | 299    | -3361  | 80         | D <sub>1</sub>       | 2241   | 2986   |

| 7          | (COM <sub>20</sub> ) | -2241  | 1790   | 43         | SEG <sub>29</sub> | 498    | -3361  | 81         | D <sub>2</sub>       | 1895   | 3364   |

|            | COM <sub>12</sub>    |        |        | 44         | SEG <sub>28</sub> | 698    | -3361  | 82         | $D_3$                | 1695   | 3364   |

| 8          | (COM <sub>19</sub> ) | -2241  | 1591   | 45         | SEG <sub>27</sub> | 897    | -3361  | 83         | $D_4$                | 1496   | 3364   |

|            | COM <sub>13</sub>    |        |        | 46         | SEG <sub>26</sub> | 1097   | -3361  | 84         | $D_5$                | 1296   | 3364   |

| 9          | (COM <sub>18</sub> ) | -2241  | 1391   | 47         | SEG <sub>25</sub> | 1296   | -3361  | 85         | D <sub>6</sub>       | 1097   | 3364   |

|            | COM <sub>14</sub>    |        |        | 48         | SEG <sub>24</sub> | 1496   | -3361  | 86         | $D_7$                | 897    | 3364   |

| 10         | (COM <sub>17</sub> ) | -2241  | 1192   | 49         | SEG <sub>23</sub> | 1695   | -3361  | 87         | $V_{DD}$             | 698    | 3364   |

|            | COM <sub>15</sub>    |        |        | 50         | SEG <sub>22</sub> | 1895   | -3361  | 88         | RESX                 | 498    | 3364   |

| 11         | (COM <sub>16</sub> ) | -2241  | 992    | 51         | SEG <sub>21</sub> | 2241   | -3038  | 89         | FR                   | 299    | 3364   |

| 12         | SEG <sub>60</sub>    | -2241  | 649    | 52         | SEG <sub>20</sub> | 2241   | -2839  | 90         | $V_5$                | 99     | 3364   |

| 13         | SEG <sub>59</sub>    | -2241  | 450    | 53         | SEG <sub>19</sub> | 2241   | -2639  | 91         | V <sub>3</sub>       | -101   | 3364   |

| 14         | SEG <sub>58</sub>    | -2241  | 250    | 54         | SEG <sub>18</sub> | 2241   | -2440  | 92         | $V_2$                | -300   | 3364   |

| 15         | SEG <sub>57</sub>    | -2241  | 51     | 55         | SEG <sub>17</sub> | 2241   | -2240  | 93         | M/S                  | -500   | 3364   |

| 16         | SEG <sub>56</sub>    | -2241  | -149   | 56         | SEG <sub>16</sub> | 2241   | -2041  | 94         | $V_4$                | -699   | 3364   |

| 17         | SEG <sub>55</sub>    | -2241  | -445   | 57         | SEG <sub>15</sub> | 2241   | -1841  | 95         | V <sub>1</sub>       | -899   | 3364   |

| 18         | SEG <sub>54</sub>    | -2241  | -644   | 58         | SEG <sub>14</sub> | 2241   | -1642  |            | COM <sub>0</sub>     |        |        |

| 19         | SEG <sub>53</sub>    | -2241  | -844   | 59         | SEG <sub>13</sub> | 2241   | -1442  | 96         | (COM <sub>31</sub> ) | -1098  | 3364   |

| 20         | SEG <sub>52</sub>    | -2241  | -1043  | 60         | SEG <sub>12</sub> | 2241   | -1243  |            | COM <sub>1</sub>     |        |        |

| 21         | SEG <sub>51</sub>    | -2241  | -1243  | 61         | SEG <sub>11</sub> | 2241   | -1043  | 97         | (COM <sub>30</sub> ) | -1298  | 3364   |

| 22         | SEG <sub>50</sub>    | -2241  | -1442  | 62         | SEG <sub>10</sub> | 2241   | -844   |            | COM <sub>2</sub>     |        |        |

| 23         | SEG <sub>49</sub>    | -2241  | -1642  | 63         | SEG <sub>9</sub>  | 2241   | -644   | 98         | (COM <sub>29</sub> ) | -1497  | 3364   |

| 24         | SEG <sub>48</sub>    | -2241  | -1841  | 64         | SEG <sub>8</sub>  | 2241   | -445   |            | COM <sub>3</sub>     | 400=   | 0007   |

| 25         | SEG <sub>47</sub>    | -2241  | -2041  | 65         | SEG <sub>7</sub>  | 2241   | -245   | 99         | (COM <sub>28</sub> ) | -1697  | 3364   |

| 26         | SEG <sub>46</sub>    | -2241  | -2240  | 66         | SEG <sub>6</sub>  | 2241   | -46    | 400        | COM <sub>4</sub>     | 4000   | 0004   |

| 27         | SEG <sub>45</sub>    | -2241  | -2440  | 67         | SEG₅              | 2241   | 154    | 100        | (COM <sub>27</sub> ) | -1896  | 3364   |

| 28         | SEG <sub>44</sub>    | -2241  | -2639  | 68         | SEG <sub>4</sub>  | 2241   | 428    |            |                      |        |        |

| 29         | SEG <sub>43</sub>    | -2241  | -2839  | 69         | $SEG_3$           | 2241   | 628    |            |                      |        | İ      |

# • The terminals for which the name differs between Master and Slave

| Mode        | 74               | 75                  | 96 to 100, 1 to 11                     | Note      |

|-------------|------------------|---------------------|----------------------------------------|-----------|

| Master Mode | OSC <sub>1</sub> | OSC <sub>2</sub>    | COM <sub>0</sub> to COM <sub>15</sub>  | M/S = "H" |

| Slave Mode  | NC               | OSC <sub>2</sub> *1 | COM <sub>31</sub> to COM <sub>16</sub> | M/S = "L" |

\*1 : Connect to OSC<sub>2</sub> of the master IC.