# **REF102**

# Precision VOLTAGE REFERENCE

# **FEATURES**

- +10V ±0.0025V OUTPUT

- VERY LOW DRIFT: 2.5ppm/°C max

- EXCELLENT STABILITY: 5ppm/1000hr typ

- EXCELLENT LINE REGULATION: 1ppm/V max

- EXCELLENT LOAD REGULATION: 10ppm/mA max

- LOW NOISE: 5µVp-p typ, 0.1Hz to 10Hz

- WIDE SUPPLY RANGE: 11.4VDC to 36VDC

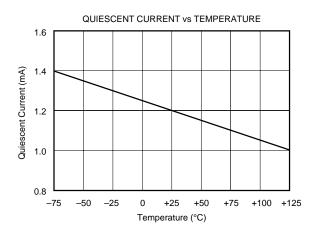

- LOW QUIESCENT CURRENT: 1.4mA max

- PACKAGE OPTIONS: HERMETIC TO-99, PLASTIC DIP, SOIC

# **DESCRIPTION**

The REF102 is a precision 10V voltage reference. The drift is laser-trimmed to 2.5ppm/°C max (CM grade) over the industrial temperature range and 5ppm/°C max (SM grade) over the military temperature range. The REF102 achieves its precision without a heater. This results in low power, fast warm-up, excellent stability, and low noise. The output voltage is extremely insensitive to both line and load variations and can be externally adjusted with minimal effect on drift and stability. Single supply operation from 11.4V to 36V and excellent overall specifications make the REF102 an ideal choice for demanding instrumentation and system reference applications.

# **APPLICATIONS**

- PRECISION-CALIBRATED VOLTAGE STANDARD

- D/A AND A/D CONVERTER REFERENCE

- PRECISION CURRENT REFERENCE

- ACCURATE COMPARATOR THRESHOLD REFERENCE

- DIGITAL VOLTMETERS

- TEST EQUIPMENT

- PC-BASED INSTRUMENTATION

Printed in U.S.A. October, 1993

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

# **ELECTRICAL**

At  $T_A$  = +25°C and  $V_S$  = +15V power supply, unless otherwise noted.

|                                                                         |                                                               | REF102A, R |                 | REF102B, S  |       | REF102C, M |             |        |     |                |                                     |

|-------------------------------------------------------------------------|---------------------------------------------------------------|------------|-----------------|-------------|-------|------------|-------------|--------|-----|----------------|-------------------------------------|

| PARAMETER                                                               | CONDITIONS                                                    | MIN        | TYP             | MAX         | MIN   | TYP        | MAX         | MIN    | TYP | MAX            | UNITS                               |

| OUTPUT VOLTAGE Initial vs Temperature (1)                               | T <sub>A</sub> = 25°C                                         | 9.99       |                 | 10.01<br>10 | 9.995 |            | 10.005<br>5 | 9.9975 |     | 10.0025<br>2.5 | V<br>ppm/°C                         |

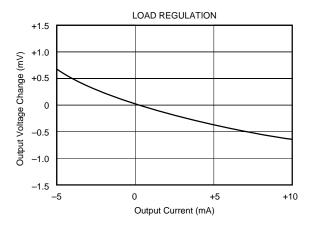

| vs Supply (Line Regulation) vs Output Current                           | V <sub>S</sub> = 11.4V to 36V                                 |            |                 | 2           |       |            | 1           |        |     | 1              | ppm/V                               |

| (Load Regulation)                                                       | $I_L = 0mA \text{ to } +10mA$<br>$I_L = 0mA \text{ to } -5mA$ |            |                 | 20<br>40    |       |            | 10<br>20    |        |     | 10<br>20       | ppm/mA<br>ppm/mA                    |

| vs Time M Package P, U Packages (2) Trim Range (3) Capacitive Load, max | T <sub>A</sub> = 25°                                          | ±3         | 5<br>20<br>1000 |             | *     | *<br>*     |             | *      | *   |                | ppm/1000hr<br>ppm/1000hr<br>%<br>pF |

| NOISE                                                                   | (0.1Hz to 10Hz)                                               |            | 5               |             |       | *          |             |        | *   |                | μVp-p                               |

| OUTPUT CURRENT                                                          | (01111210110112)                                              | +10, –5    |                 |             | *     | -          |             | *      |     |                | mA                                  |

| INPUT VOLTAGE<br>RANGE                                                  |                                                               | +11.4      |                 | +36         | *     |            | *           | *      |     | *              | V                                   |

| QUIESCENT CURRENT                                                       | (I <sub>OUT</sub> = 0)                                        |            |                 | +1.4        |       |            | *           |        |     | *              | mA                                  |

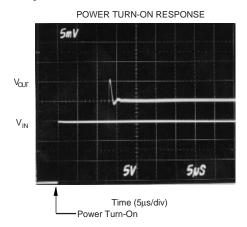

| WARM-UP TIME (4)                                                        | (To 0.1%)                                                     |            | 15              |             |       | *          |             |        | *   |                | μs                                  |

| TEMPERATURE RANGE Specification REF102A, B, C REF102R, S                |                                                               | –25<br>–55 |                 | +85<br>+125 | *     |            | *           | *      |     | *              | °C                                  |

$<sup>\</sup>ensuremath{\,\boldsymbol{\ast}\,}$  Specifications same as REF102A/R.

NOTES: (1) The "box" method is used to specify output voltage drift vs temperature. See the Discussion of Performance section. (2) Typically 5ppm/1000hrs after 168hr powered stabilization. (3) Trimming the offset voltage affects drift slightly. See Installation and Operating Instructions for details. (4) With noise reduction pin floating. See Typical Performance Curves for details.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

# **ORDERING INFORMATION**

| PRODUCT  | PACKAGE           | TEMPERATURE<br>RANGE | MAX INITIAL<br>ERROR (mV) | MAX DRIFT<br>(ppm/°C) |

|----------|-------------------|----------------------|---------------------------|-----------------------|

| REF102AU | 8-Pin SOIC        | −25°C to +85°C       | ±10                       | ±10                   |

| REF102AP | 8-Pin Plastic DIP | −25°C to +85°C       | ±10                       | ±10                   |

| REF102BP | 8-Pin Plastic DIP | −25°C to +85°C       | ±5                        | ±5                    |

| REF102AM | Metal TO-99       | −25°C to +85°C       | ±10                       | ±10                   |

| REF102BM | Metal TO-99       | −25°C to +85°C       | ±5                        | ±5                    |

| REF102CM | Metal TO-99       | −25°C to +85°C       | ±2.5                      | ±2.5                  |

| REF102RM | Metal TO-99       | −55°C to +125°C      | ±10                       | ±10                   |

| REF102SM | Metal TO-99       | −55°C to +125°C      | ±5                        | ±5                    |

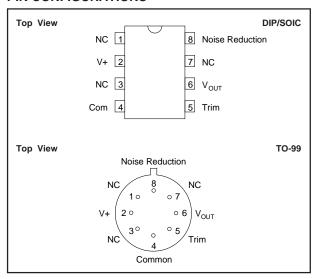

### **PIN CONFIGURATIONS**

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ABSOLUTE MAXIMUM RATINGS**

|                          | +40V                        |

|--------------------------|-----------------------------|

| Operating Temperature    |                             |

| P,U                      |                             |

| M                        |                             |

| Storage Temperature F    | Range                       |

| P,U                      | 40°C to +85°C               |

| M                        |                             |

| Lead Temperature (sol    | dering, 10s) +300°C         |

| (SC                      | OIC, 3s)+260°C              |

| Short-Circuit Protection | n to Common or V+Continuous |

# **PACKAGE INFORMATION**

| PRODUCT  | PACKAGE           | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|-------------------|------------------------------------------|

| REF102AU | 8-Pin SOIC        | 182                                      |

| REF102AP | 8-Pin Plastic DIP | 006                                      |

| REF102BP | 8-Pin Plastic DIP | 006                                      |

| REF102AM | Metal-TO-99       | 001                                      |

| REF102BM | Metal-TO-99       | 001                                      |

| REF102CM | Metal-TO-99       | 001                                      |

| REF102RM | Metal-TO-99       | 001                                      |

| REF102SM | Metal-TO-99       | 001                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

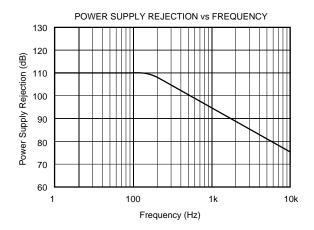

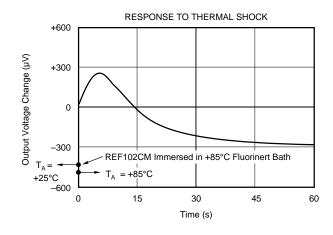

# **TYPICAL PERFORMANCE CURVES**

At  $T_A$  = +25°C,  $V_S$  = +15V, unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25$ °C,  $V_S = +15$ V, unless otherwise noted.

# TYPICAL REF102 REFERENCE NOISE 200 vV 18 4 (\frac{1}{1}) = \frac{1}{2} = \frac{1}{

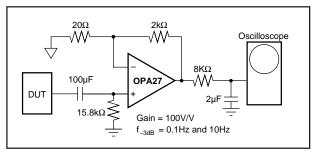

Low Frequency Noise (1s /div) (See Noise Test Circuit)

Noise Test Circuit.

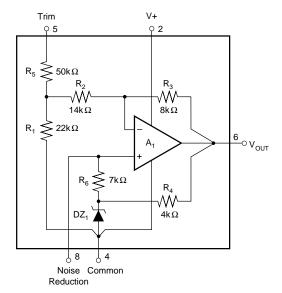

# THEORY OF OPERATION

Refer to the diagram on the first page of this data sheet. The 10V output is derived from a compensated buried zener diode  $DZ_1$ , op amp  $A_1$ , and resistor network  $R_1$ – $R_6$ .

Approximately 8.2V is applied to the non-inverting input of  $A_1$  by  $DZ_1$ .  $R_1$ ,  $R_2$ , and  $R_3$  are laser-trimmed to produce an exact 10V output. The zener bias current is established from the regulated output voltage through  $R_4$ .  $R_5$  allows user-trimming of the output voltage by providing for small external adjustment of the amplifier gain. Because the TCR of  $R_5$  closely matches the TCR of  $R_1$ ,  $R_2$  and  $R_3$ , the voltage trim has minimal effect on the reference drift. The output voltage noise of the REF102 is dominated by the noise of the zener diode. A capacitor can be connected between the Noise Reduction pin and ground to form a low-pass filter with  $R_6$  and roll off the high-frequency noise of the zener.

# DISCUSSION OF PERFORMANCE

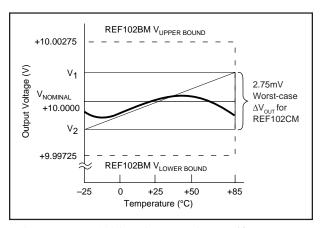

The REF102 is designed for applications requiring a precision voltage reference where both the initial value at room temperature and the drift over temperature are of importance to the user. Two basic methods of specifying voltage reference drift versus temperature are in common usage in the industry—the "butterfly method" and the "box method." The REF102 is specified with the more commonly used "box method." The "box" is formed by the high and low specification temperatures and a diagonal, the slope of which is equal to the maximum specified drift.

Since the shape of the actual drift curve is not known, the vertical position of the box is not exactly known either. It is, however, bounded by  $V_{\rm UPPER\ BOUND}$  and  $V_{\rm LOWER\ BOUND}$  (see Figure 1). Figure 1 uses the REF102CM as an example. It has a drift specification of 2.5ppm/°C maximum and a specification temperature range of -25°C to +85°C. The "box" height,  $V_1$  to  $V_2$ , is 2.75mV.

FIGURE 1. REF102CM Output Voltage Drift.

# INSTALLATION AND OPERATING INSTRUCTIONS

### **BASIC CIRCUIT CONNECTION**

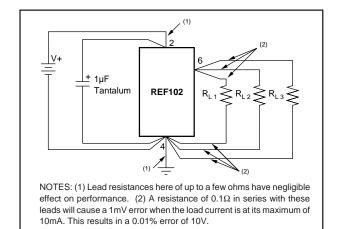

Figure 2 shows the proper connection of the REF102. To achieve the specified performance, pay careful attention to layout. A low resistance star configuration will reduce voltage errors, noise pickup, and noise coupled from the power supply. Commons should be connected as indicated being sure to minimize interconnection resistances.

FIGURE 2. REF102 Installation.

### OPTIONAL OUTPUT VOLTAGE ADJUSTMENT

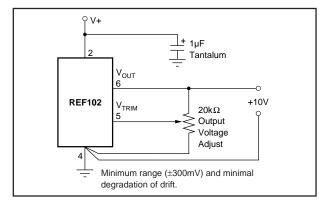

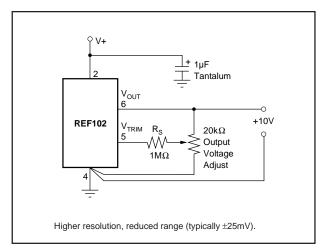

Optional output voltage adjustment circuits are shown in Figures 3 and 4. Trimming the output voltage will change the voltage drift by approximately 0.008ppm/°C per mV of trimmed voltage. In the circuit in Figure 3, any mismatch in TCR between the two sections of the potentiometer will also affect drift, but the effect of the  $\Delta TCR$  is reduced by a factor of five by the internal resistor divider. A high quality potentiometer, with good mechanical stability, such as a cermet, should be used. The circuit in Figure 3 has a minimum trim range of  $\pm 300$ mV. The circuit in Figure 4 has less range but provides higher resolution. The mismatch in TCR between  $R_S$  and the internal resistors can introduce some slight drift. This effect is minimized if  $R_S$  is kept significantly larger than the 50k $\Omega$  internal resistor. A TCR of 100ppm/°C is normally sufficient.

FIGURE 3. REF102 Optional Output Voltage Adjust.

FIGURE 4. REF102 Optional Output Voltage Fine Adjust.

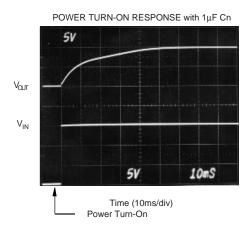

# **OPTIONAL NOISE REDUCTION**

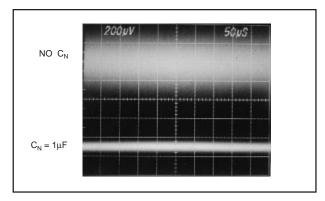

The high-frequency noise of the REF102 is dominated by the zener diode noise. This noise can be greatly reduced by connecting a capacitor between the Noise Reduction pin and ground. The capacitor forms a low pass filter with  $R_6$  (refer to the figure on the first page of the data sheet) and attenuates the high-frequency noise generated by the zener. Figure 5 shows the effect of a 1µF noise reduction capacitor on the high frequency noise of the REF102.  $R_6$  is typically  $7k\Omega$  so the filter has a –3dB frequency of about 22Hz. The result is a reduction in noise from about  $800\mu Vp$ -p to under  $200\mu Vp$ -p. If further noise reduction is required, use the circuit in Figure 14.

FIGURE 5. Effect of 1 $\mu$ F Noise Reduction Capacitor on Broadband Noise ( $f_{-3dB} = 1$ MHz).

# APPLICATIONS INFORMATION

High accuracy, extremely low drift, outstanding stability, and low cost make the REF102 an ideal choice for all instrumentation and system reference applications. Figures 6 through 14 show a variety of useful application circuits.

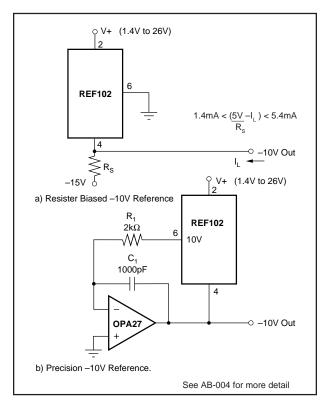

FIGURE 6. –10V Reference Using a) Resistor or b) OPA27.

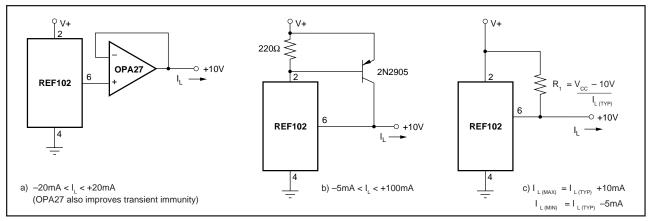

FIGURE 7.  $\pm 10V$  Reference With Output Current Boosted to: a)  $\pm 20mA$ , b)  $\pm 100mA$ , and c)  $I_{L~(TYP)} \pm 10mA$ ,  $\pm 5A$ .

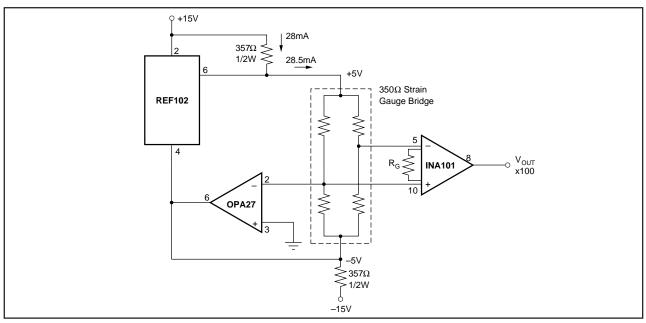

FIGURE 8. Strain Gauge Conditioner for  $350\Omega$  Bridge.

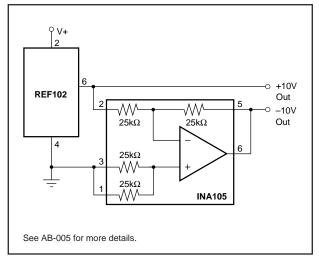

FIGURE 9. ±10V Reference.

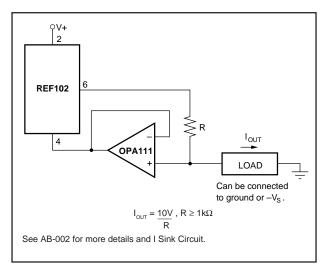

FIGURE 10. Positive Precision Current Source.

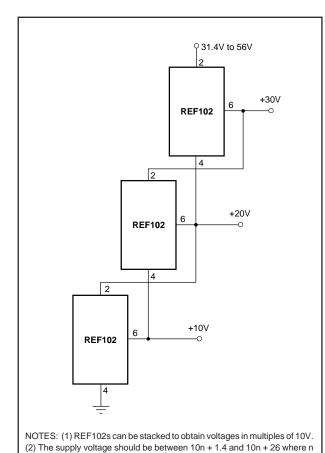

FIGURE 11. Stacked References.

delivered to the lower REF102.

is the number of REF102s. (3) Output current of each REF102 must not exceed its rated output current of +10, -5mA. This includes the current

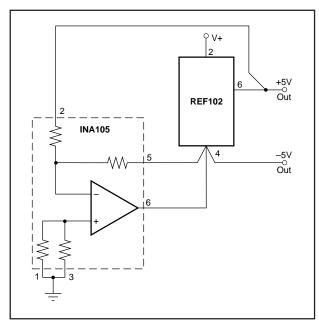

FIGURE 12. ±5V Reference.

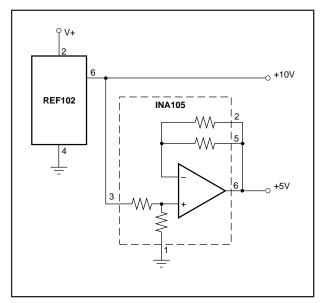

FIGURE 13. +5V and +10V Reference.

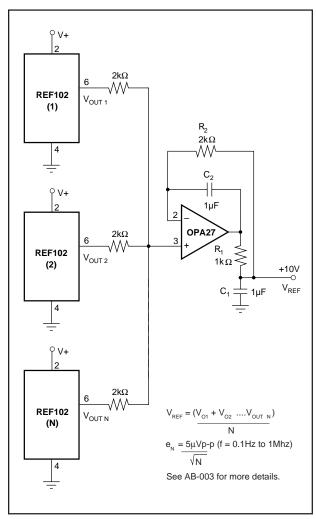

FIGURE 14. Precision Voltage Reference with Extremely Low Noise.

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated