# I<sup>2</sup>CBus SERIAL INTERFACE REAL TIME CLOCK

**RS5C372A**

# **APPLICATION MANUAL**

**ELECTRONIC DEVICES DIVISION**

#### NOTICE

- 1. The products and the product specifications described in this application manual are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to Ricoh sales representatives for the latest information thereon.

- 2. This application manual may not be copied or otherwise reproduced in whole or in part without prior written consent of Ricoh.

- 3. Please be sure to take any necessary formalities under relevant laws or regulations before exporting or otherwise taking out of your country the products or the technical information described herein.

- 4. The technical information described in this application manual shows typical characteristics of and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under Ricoh's or any third party's intellectual property rights or any other rights.

- 5. The products listed in this document are intended and designed for use as general electronic components in standard applications (office equipment, computer equipment, measuring instruments, consumer electronic products, amusement equipment etc.). Those customers intending to use a product in an application requiring extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of the product could result in human injury or death (aircraft, spacevehicle, nuclear reactor control system, traffic control system, automotive and transportation equipment, combustion equipment, safety devices, life support system etc.) should first contact us.

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire-containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. Anti-radiation design is not implemented in the products described in this application manual.

- 8. Please contact Ricoh sales representatives should you have any questions or comments concerning the products or the technical information.

# RS5C372A APPLICATION MANUAL CONTENTS

| OUTLINE                                        |    |

|------------------------------------------------|----|

| FEATURES                                       |    |

| BLOCK DIAGRAMS                                 |    |

| APPLICATIONS                                   |    |

| SELECTION GUIDE                                |    |

| PIN CONFIGURATION                              |    |

| PIN DESCRIPTIONS                               |    |

| ABSOLUTE MAXIMUM RATINGS                       |    |

| RECOMMENDED OPERATING CONDITIONS               |    |

| DC CHARACTERISTICS                             | 4  |

| AC CHARACTERISTICS                             | 5  |

| OUTLINE DESCRIPTION                            | 7  |

| FUNCTIONAL DESCRIPTIONS                        | g  |

| 1. Allocation of Internal Addresses ······     | g  |

| 2. Registers ·····                             | 10 |

| OPERATION                                      | 20 |

| Interfacing with the CPU·····                  | 20 |

| 2. Configuration of Oscillating Circuit ······ | 29 |

| 3. Oscillator Halt Sensing ·····               | 34 |

| 4. INTRA Output and INTRB Output Pins·····     |    |

| 5. Typical Applications ·····                  |    |

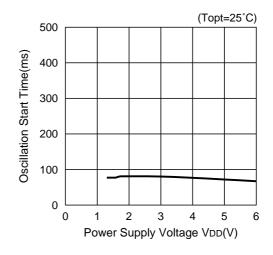

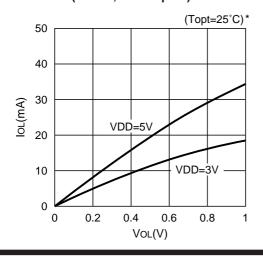

| 6. Typical Characteristic Measurements·····    |    |

| 7. Typical Software-based Operations ······    | 43 |

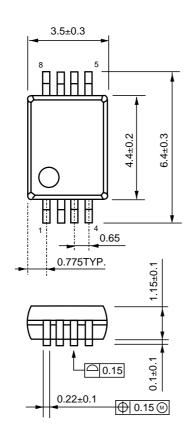

| PACKAGE DIMENSION ·····                        |    |

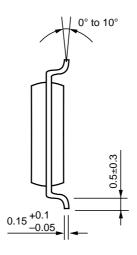

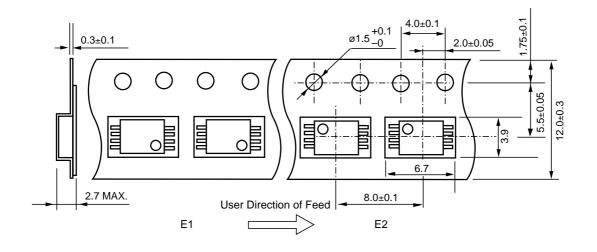

| TAPING SPECIFICATION                           | 46 |

|                                                |    |

# RIGOH

#### I<sup>2</sup>CBus SERIAL INTERFACE REAL TIME CLOCK

#### **RS5C372A**

#### **OUTLINE**

The RS5C372A is a CMOS type real-time clock which is connected to the CPU via 2-wires and capable of serial transmission of clock and calendar data to the CPU.

The RS5C372A can generate various periodic interrupt clock pulses lasting for long period (one month), and alarm interrupt can be made by days of the week, hours, and minutes by two incorporated systems. Since an oscillation circuit is driven at a constant voltage, it undergoes fluctuations of few voltage and consequently offers low current consumption (TYP. 0.5µA at 3V). It also provides an oscillator halt sensing function applicable for data validation at power-on and other occasions and 32kHz clock output for an external micro computer. The product also incorporates a time trimming circuit that adjusts the clock with higher precision by adjusting any errors in crystal oscillator frequencies based on signals from the CPU. The crystal oscillator may be selected from 32.768kHz or 32.000kHz types. Integrated into an ultra compact and ultra thin 8 pin SSOP package, the RS5C372A is the optimum choice for equipment requiring small sized and low power consuming products.

#### **FEATURES**

- Time keeping voltage: 1.45V to 6.0V

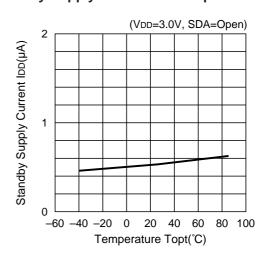

- Lowest supply current: 0.5μA TYP. (0.9μA MAX.) : 3V (25°C)

$(1.0\mu A MAX.) : 3V (-40 to +85^{\circ}C)$

- Connected to the CPU via only 2-wires (I<sup>2</sup>CBus Interface, MAX.400kHz, address 7bit)

- A clock counter (counting hours, minutes, and seconds) and a calendar counter (counting leap years, years, months, days, and days of the week) in BCD codes

- Interrupt to the CPU (period of one month to one second, interrupt flag, interrupt halt function) (INTRA, INTRB)

- Two systems of alarm functions (days of the week, hours, and minutes) (INTRA, INTRB)

- Oscillation halt sensing to judge internal data validity

- Clock output of 32.768kHz (32.000kHz) (output controllable via a register)

- Second digit adjustment by ±30 seconds

- Automatic leap year recognition up to the year 2099

- 12-hour or 24-hour time display selectable

- Oscillation stabilizing capacity (CG, CD) incorporated

- High precision time trimming circuit

- Oscillator of 32.768kHz or 32.000kHz may be used

- CMOS logic

- Package: 8pin SSOP

#### Note

- · I<sup>2</sup>CBus is a trademark of PHILIPS ELECTRONICS N.V.

- $\cdot$  Purchase of I<sup>2</sup>C components of Ricoh Company, Ltd. conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system comforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

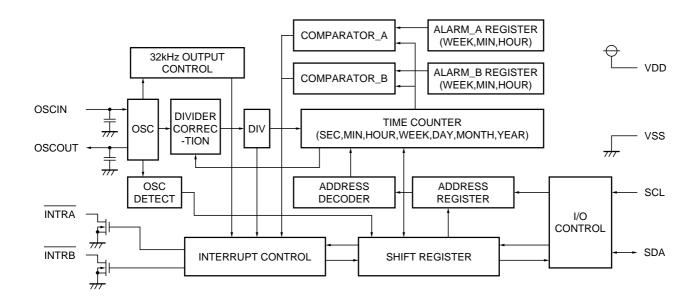

#### **BLOCK DIAGRAM**

#### **APPLICATIONS**

- Communication devices (multi function phone, portable phone, PHS or pager)

- OA devices (fax, portable fax)

- Computer (desk-top and mobile PC, portable word-processor, PDA, electric note or video game)

- AV components (portable audio unit, video camera, camera, digital camera or remote controller)

- Home appliances (rice cooker, electric oven)

- Other (car navigation system, multi-function watch)

#### **SELECTION GUIDE**

One of two RS5C372As can be selected based on IC direction on taping. (E2 is standard.)

Part Number: RS5C372A-E1, RS5C372A-E2

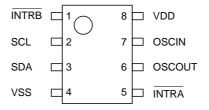

#### PIN CONFIGURATION

• 8pin SSOP (0.65mm pitch)

#### **PIN DESCRIPTIONS**

| Pin No. | Symbol          | Name                                                       | Description                                                                                                                                                                                                                                               |

|---------|-----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | SCL             | Serial clock line                                          | This pin is used to input shift clock pulses to synchronize data input/output to and from the SDA pin with this clock. Up to 6V beyond VDD may be input.                                                                                                  |

| 3       | SDA             | Serial data line                                           | This pin inputs and outputs written or read data in synchronization with shift clock pulses from the SCL pin. Up to 6V beyond VDD may be input. This pin functions as an Nch open drain output.                                                           |

| 5       | INTRA           | Interrupt output A                                         | This pin outputs periodic interrupt pulses and alarm interrupt (ALARM_A, ALARM_B) to the CPU. This pin is off when power is activated from 0V. This pin functions as an Nch open drain output.                                                            |

| 1       | INTRB           | Interrupt output B                                         | This pin outputs 32.768kHz clock pulses (when 32.768kHz crystal is used), periodic interrupt pulses to the CPU or alarm interrupt (ALARM_B). It outputs 32.768kHz when power source is activated from 0V. This pin functions as an Nch open drain output. |

| 7<br>6  | OSCIN<br>OSCOUT | Oscillator circuit input/output                            | These pins configure an oscillator circuit by connecting a 32.768kHz or 32.000kHz crystal oscillator between the OSCIN–OSCOUT pins.  (Any other oscillator circuit components are built into the RS5C372A.)                                               |

| 8 4     | VDD<br>VSS      | Positive power supply input<br>Negative power supply input | The VDD pin is connected to the positive power supply and Vss to the ground.                                                                                                                                                                              |

#### **ABSOLUTE MAXIMUM RATINGS**

(Vss=0V)

| Symbol          | Item                  | Conditions   | Ratings      | Unit |

|-----------------|-----------------------|--------------|--------------|------|

| Vdd             | Supply voltage        |              | -0.3 to +7.0 | V    |

| VI              | Input voltage         | SCL, SDA     | -0.3 to +7.0 | V    |

| Vo <sub>1</sub> | Output voltage 1      | SDA          | -0.3 to +7.0 | V    |

| Vo <sub>2</sub> | Output voltage 2      | INTRA, INTRB | -0.3 to +12  | ·    |

| PD              | Power dissipation     | Topt=25°C    | 300          | mW   |

| Topt            | Operating temperature |              | -40 to +85   | °C   |

| Tstg            | Storage temperature   |              | -55 to +125  | °C   |

#### ABSOLUTE MAXIMUM RATINGS

Absolute Maximum ratings are threshold limit values that must not be exceeded even for an instant under any conditions. Moreover, such values for any two items must not be reached simultaneously. Operation above these absolute maximum ratings may cause degradation or permanent damage to the device. These are stress ratings only and do not necessarily imply functional operation below these limits.

# **RECOMMENDED OPERATING CONDITIONS**

(Vss=0V, Topt=-40 to +85°C)

| Symbol | Item                  | Conditions   | MIN. | TYP.                   | MAX. | Unit |

|--------|-----------------------|--------------|------|------------------------|------|------|

| Vdd    | Supply voltage        |              | 2.0  |                        | 6.0  | V    |

| VCLK   | Time keeping voltage  |              | 1.45 |                        | 6.0  | V    |

| Fxt    | Oscillation frequency |              |      | 32.768<br>or<br>32.000 |      | kHz  |

| VPUP1  | Pull-up voltage 1     | SCL, SDA     |      |                        | 6.0  | V    |

| VPUP2  | Pull-up voltage 2     | ĪNTRĀ, ĪNTRB |      |                        | 10.0 | V    |

#### **DC CHARACTERISTICS**

$Unless \ otherwise \ specified: Vss=0V, Vdd=3V, Topt=-40 \ to \ +85^{\circ}C, Oscillation \ frequency=32.768 kHz, or \ 32.000 kHz (R_1=30 k\Omega)$

| Symbol | Item                                | Pin name             | Conditions                                                   | MIN.   | TYP. | MAX.   | Unit |

|--------|-------------------------------------|----------------------|--------------------------------------------------------------|--------|------|--------|------|

| Vih    | "H" input voltage                   | SCL, SDA             |                                                              | 0.8Vdd |      | 6.0    | V    |

| VIL    | "L" input voltage                   | SCL, SDA             |                                                              | -0.3   |      | 0.2Vdd | V    |

| Iol1   | Output current                      | ĪNTRĀ, ĪNTRB         | Vol1=0.4V                                                    | 1      |      |        | mA   |

| IOL2   | Output current                      | SDA                  | Vol2=0.6V                                                    | 6      |      |        | mA   |

| IILK   | Input leakage current               | SCL                  | VI=6V or Vss<br>VDD=6V                                       | -1     |      | 1      | μΑ   |

| Ioz    | Output off state<br>leakage current | SDA, ĪNTRĀ,<br>ĪNTRB | Vo=6V or Vss<br>Vdd=6V                                       | -1     |      | 1      | μΑ   |

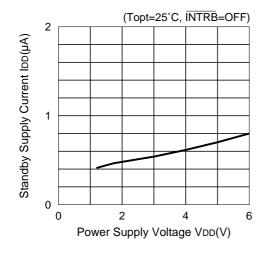

| Idd1   |                                     | VDD                  | VDD=3V, Topt=25°C<br>SCL, SDA=3V<br>Output=OPEN*1            |        | 0.5  | 0.9    | μA   |

| Idd2   | Standby current                     | VDD                  | VDD=3V,<br>Topt=-40 to +85°C<br>SCL, SDA=3V<br>Output=OPEN*1 |        |      | 1.0    | μА   |

| Idd3   |                                     | VDD                  | VDD=6V<br>SCL, SDA=6V<br>Output=Open*1                       |        | 0.8  | 2.0    | μA   |

| CG     | Internal oscillation capacitance 1  | OSCIN                |                                                              |        | 10   |        | pF   |

| CD     | Internal oscillation capacitance 2  | OSCOUT               |                                                              |        | 10   |        | pF   |

<sup>\*1)</sup> The mode outputs no clock pulses when output is open (output off state).

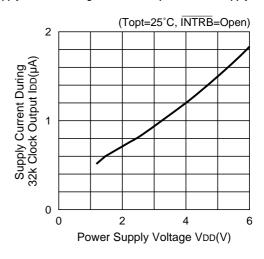

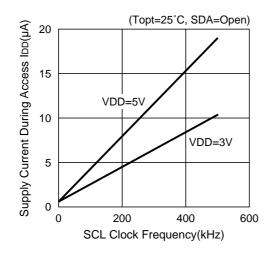

For consumption current (output: no load) when 32kHz pulses are output from INTRB, see "6. Typical Characteristic Measurements"

# **AC CHARACTERISTICS**

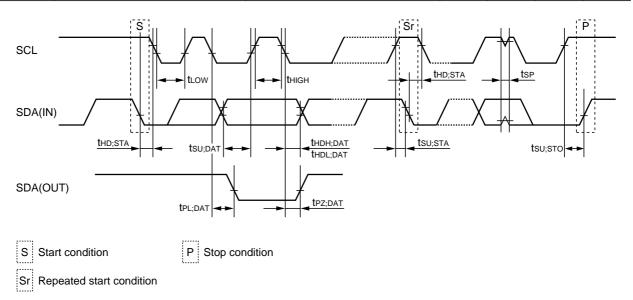

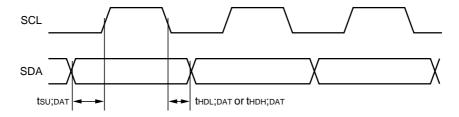

#### • VDD≥2.0V (supports standard mode I2CBus)

$\label{eq:Unless otherwise specified: Vss=0V, Topt=-40 to +85°C, Crystal=32.768kHz or 32.000kHz} I/O conditions: Vih=0.8 \times Vdd, Vil=0.2 \times Vdd, Vol=0.2 \times Vdd, Cl=50pF$

| Symbol    | Item                                              | Conditions | MIN. | TYP. | MAX. | Unit |

|-----------|---------------------------------------------------|------------|------|------|------|------|

| fscl      | SCL clock frequency                               |            | 0    |      | 100  | kHz  |

| tlow      | SCL clock "L" time                                |            | 4.7  |      |      | μs   |

| thigh     | SCL clock "H" time                                |            | 4.0  |      |      | μs   |

| thd; sta  | Start condition hold time                         |            | 4.0  |      |      | μs   |

| tsu; sto  | Stop condition setup time                         |            | 4.0  |      |      | μs   |

| tsu; sta  | Start condition setup time                        |            | 4.7  |      |      | μs   |

| tsu; dat  | Data setup time                                   |            | 250  |      |      | ns   |

| thdh; dat | "H" data hold time                                |            | 0    |      |      | ns   |

| thdl; dat | "L" data hold time                                |            | 35   |      |      | ns   |

| tpl; dat  | SDA "L" stable time after falling of SCL          |            |      |      | 2.0  | μs   |

| tpz; dat  | SDA off stable time after falling of SCL          |            |      |      | 2.0  | μs   |

| tr        | Rising time of SCL and SDA (input)                |            |      |      | 1000 | ns   |

| tf        | Falling time of SCL and SDA (input)               |            |      |      | 300  | ns   |

| tsp       | Spike width that can be removed with input filter |            |      |      | 50   | ns   |

<sup>\*)</sup> For detailed information refer to "OPERATION: 1.2 Transmission System of I<sup>2</sup>CBus."

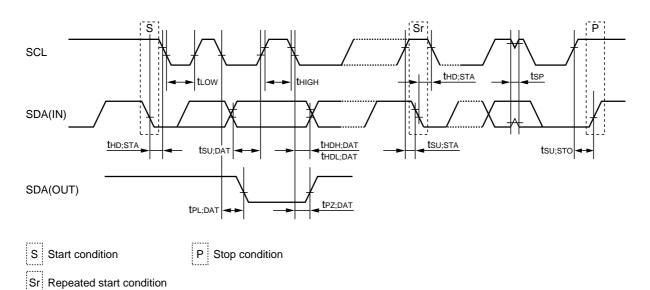

#### • VDD≥2.5V (supports fast mode I2CBus)

$\label{eq:Unless otherwise specified: Vss=0V, Topt=-40 to +85^{\circ}C, Crystal=32.768kHz or 32.000kHz \\ I/O \ conditions: Vih=0.8 \times Vdd, Vil=0.2 \times Vdd, Vol=0.2 \times Vdd, Cl=50pF$

| Symbol    | Item                                              | Conditions | MIN. | TYP. | MAX. | Unit |

|-----------|---------------------------------------------------|------------|------|------|------|------|

| fscl      | SCL clock frequency                               |            | 0    |      | 400  | kHz  |

| tlow      | SCL clock "L" time                                |            | 1.3  |      |      | μs   |

| tнісн     | SCL clock "H" time                                |            | 0.6  |      |      | μs   |

| thd; sta  | Start condition hold time                         |            | 0.6  |      |      | μs   |

| tsu; sto  | Stop condition setup time                         |            | 0.6  |      |      | μs   |

| tsu; sta  | Start condition setup time                        |            | 0.6  |      |      | μs   |

| tsu; dat  | Data setup time                                   |            | 100  |      |      | ns   |

| thdh; dat | "H" data hold time                                |            | 0    |      |      | ns   |

| thdl; dat | "L" data hold time                                |            | 35   |      |      | ns   |

| tpl; dat  | SDA "L" stable time after falling of SCL          |            |      |      | 0.9  | μs   |

| tpz; dat  | SDA off stable time after falling of SCL          |            |      |      | 0.9  | μs   |

| tr        | Rising time of SCL and SDA (input)                |            |      |      | 300  | ns   |

| tr        | Falling time of SCL and SDA (input)               |            |      |      | 300  | ns   |

| tsp       | Spike width that can be removed with input filter |            |      |      | 50   | ns   |

$\star$ ) For detailed information refer to "OPERATION: 1.2 Transmission System of I²CBus."

#### **OUTLINE DESCRIPTION**

#### 1. Interfacing with the CPU

The RS5C372A reads/writes data over I<sup>2</sup>CBus interface via 2-wires: SDA (data) and SCL (clock). Since the output of the I/O pin of SDA is open drain, data interfacing with a CPU with different supply voltage is possible by applying pull-up resistor on the circuit board. The maximum clock frequency of 400kHz of SCL enables data transfer in I<sup>2</sup>CBus fast mode.

#### 2. Clock function

The clock function of the RS5C372A allows write/read data from lower two digits of the dominical year to seconds to and from the CPU. When lower two digits of the dominical year are multiples of 4, the year is recognized as a leap year automatically. Up to the year 2099 leap years will be automatically recognized.

\*) The year 2000 is a leap year while the year 2100 is not.

#### 3. Alarm function

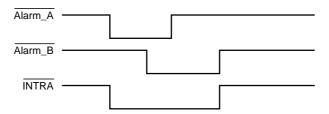

The RS5C372A has an alarm function that outputs an interrupt signal from INTRA or INTRB output pins to the CPU when the day of the week, hour or minute corresponds to the setting. These two systems of alarms (ALARM\_A, ALARM\_B), each may output interrupt signal separately at a specified time. The alarm may be selectable between on and off for each day of the week, thus allowing outputting alarm everyday or on a specific day of the week. The ALARM\_A is output from the INTRA pin while the ALARM\_B is output from either the INTRA or the INTRB pins. Polling is possible separately for each alarm system.

#### 4. High precision time trimming function

The RS5C372A has an internal oscillation circuit capacitance C<sub>G</sub> and C<sub>D</sub> so that an oscillation circuit may be configured simply by externally connecting a crystal. Either 32.768kHz or 32.000kHz may be selected as a crystal oscillator by setting the internal register appropriately. The RS5C372A incorporates a time trimming circuit that adjusts gain or loss of the clock from the CPU up to approx. ±189ppm (±194ppm when 32.000kHz crystal is used) by approximately 3ppm steps to correct discrepancy in oscillation frequency. (Error after correction: ±1.5ppm: 25°C) Thus by adjusting frequencies for each system,

- · Clock display is possible at much higher precision than conventional real-time clock while using a crystal with broader fluctuation in precision.

- · Even seasonal frequency fluctuation may be corrected by adjusting seasonal clock error.

- · For those systems that have temperature detection precision of clock function may be increased by correcting clock error according to temperature fluctuations.

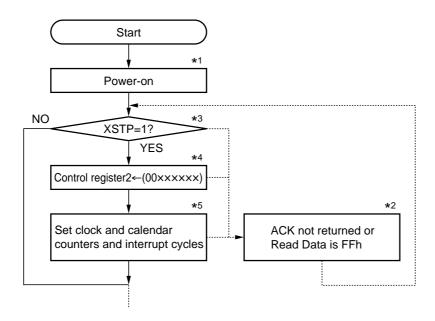

#### 5. Oscillation halt sensing

The oscillation halt sensing function uses a register to store oscillation halt information. This function may be used to determine if the RS5C372A supply power has been booted from 0V and if it has been backed up. This function is useful for determining if clock data is valid or invalid.

#### 6. Periodic interrupt

The RS5C372A can output periodic interrupt pulses in addition to alarm function from the INTRA and INTRB pins. This frequency may be selected from 2Hz (every 0.5 seconds), 1Hz (every second), 1/60Hz (every minute), 1/3600Hz (every hour) and monthly (1st of month).

Output wave form for periodic interrupt may be selected from regular pulse waveform (2Hz and 1Hz) and waveforms (every second, every minute, every hour and every month) that are appropriate for CPU level interrupt. Outputs may be selected either  $\overline{\text{INTRA}}$  or  $\overline{\text{INTRB}}$ . The RS5C372A has polling function that monitors pin status in the register.

#### 7. 32kHz clock output

The RS5C372A may output oscillation frequency from the INTRB pin. This clock output is set for output by default, which is set to on or off by setting the register.

#### Note

The year-digit counter of RS5C372A counts only lower two digits of a year and no counter is supplied for upper two digits. When you are going to use this product in a system that must cope with "2000 year problem" which shall be corrected by software.

# **FUNCTIONAL DESCRIPTIONS**

#### 1. Allocation of Internal Addresses

|   | Internal address |            |            | ress | Occidents                          | Data*1 |                  |              |                                         |      |        |                 |                 |  |

|---|------------------|------------|------------|------|------------------------------------|--------|------------------|--------------|-----------------------------------------|------|--------|-----------------|-----------------|--|

|   | <b>A</b> 3       | <b>A</b> 2 | <b>A</b> 1 | Ao   | Contents                           | D7     | D6               | D5           | D4                                      | D3   | D2     | D1              | D0              |  |

| 0 | 0                | 0          | 0          | 0    | Second counter                     | *2     | S40              | S20          | S10                                     | S8   | S4     | S2              | S1              |  |

| 1 | 0                | 0          | 0          | 1    | Minute counter                     | _      | M40              | M20          | M10                                     | M8   | M4     | M2              | M1              |  |

| 2 | 0                | 0          | 1          | 0    | Hour counter                       | _      | _                | H20<br>P/A   | H10                                     | Н8   | H4     | H2              | H1              |  |

| 3 | 0                | 0          | 1          | 1    | Day of the week counter            | _      | _                | _            | _                                       | _    | W4     | W <sub>2</sub>  | $W_1$           |  |

| 4 | 0                | 1          | 0          | 0    | Day counter                        | _      | _                | D20          | D10                                     | D8   | D4     | D <sub>2</sub>  | D1              |  |

| 5 | 0                | 1          | 0          | 1    | Month counter                      | _      | _                | _            | MO10                                    | MO8  | MO4    | MO <sub>2</sub> | MO1             |  |

| 6 | 0                | 1          | 1          | 0    | Year counter                       | Y80    | Y40              | Y20          | Y10                                     | Y8   | Y4     | Y2              | Y1              |  |

| 7 | 0                | 1          | 1          | 1    | Time trimming register             | XSL    | F6               | F5           | F4                                      | F3   | F2     | F1              | F <sub>0</sub>  |  |

| 8 | 1                | 0          | 0          | 0    | Alarm_A (minute register)          | _      | AM <sub>40</sub> | AM20         | AM <sub>10</sub>                        | AM8  | AM4    | AM <sub>2</sub> | AM <sub>1</sub> |  |

| 9 | 1                | 0          | 0          | 1    | Alarm_A (hour register)            | _      | _                | AH20<br>AP/A | AH10                                    | AH8  | AH4    | AH2             | AH1             |  |

| A | 1                | 0          | 1          | 0    | Alarm_A (day of the week register) | _      | AW6              | AW5          | AW4                                     | AW3  | $AW_2$ | AW1             | AW <sub>0</sub> |  |

| В | 1                | 0          | 1          | 1    | Alarm_B (minute register)          | _      | BM40             | BM20         | BM10                                    | BM8  | BM4    | BM <sub>2</sub> | BM1             |  |

| С | 1                | 1          | 0          | 0    | Alarm_B (hour register)            | _      | _                | BH20<br>BP/Ā | BH10                                    | ВН8  | BH4    | BH2             | BH1             |  |

| D | 1                | 1          | 0          | 1    | Alarm_B (day of the week register) | _      | BW6              | BW5          | BW4                                     | BW3  | BW2    | BW <sub>1</sub> | BW0             |  |

| Е | 1                | 1          | 1          | 0    | Control register 1                 | AALE   | BALE             | SL2          | SL1                                     | TEST | CT2    | CT1             | СТо             |  |

| F | 1                | 1          | 1          | 1    | Control register 2                 | _      | _                | 12/24        | ADJ* <sup>3</sup><br>XSTP* <sup>4</sup> | CLEN | CTFG   | AAFG            | BAFG            |  |

<sup>\*1)</sup> All the listed data can be read and written except for ADJ/XSTP.

<sup>\*2)</sup> The "-" mark indicates data which can be read only and set to "0" when read.

<sup>\*3)</sup> The ADJ/XSTP bit of the control register2 is set to ADJ for write and XSTP for read operation. The XSTP bit is set to "0" by writing data into the control register2 for normal oscillation.

$<sup>\</sup>star$ 4) When XSTP is set to "1", the  $\overline{\text{XSL}}$ , F6 to F0, CT2 to CT0, AALE, BALE, SL2, SL1,  $\overline{\text{CLEN}}$  and TEST bits are reset to "0".

#### 2. Registers

#### 2.1 Control Register 1 (at internal address Eh)

| D7   | D6   | D5  | D4  | D3   | D2  | D1  | D0  | _                     |

|------|------|-----|-----|------|-----|-----|-----|-----------------------|

| AALE | BALE | SL2 | SLı | TEST | CT2 | CT1 | СТо | (For write operation) |

| AALE | BALE | SL2 | SLı | TEST | CT2 | CT1 | СТо | (For read operation)  |

| 0    | 0    | 0   | 0   | 0    | 0   | 0   | 0   | Default*              |

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

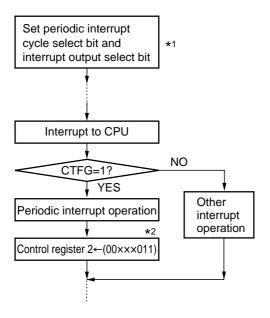

#### 2.1-1 AALE, BALE

#### Alarm\_A, Alarm\_B enable bits

| AALE, BALE | Description                                     |           |

|------------|-------------------------------------------------|-----------|

| 0          | Alarm_A (Alarm_B) Correspondence action invalid | (Default) |

| 1          | Alarm_A (Alarm_B) Correspondence action valid   |           |

#### 2.1-2 SL2, SL1

#### Interrupt output select bits

| SL2 | SL1 | Description                                                                        |           |

|-----|-----|------------------------------------------------------------------------------------|-----------|

| 0   | 0   | Outputs Alarm_A, Alarm_B, INT to the INTRA. Outputs 32k clock pulses to the INTRB. | (Default) |

| 0   | 1   | Outputs Alarm_A, INT to the INTRA. Outputs 32k clock pulses, Alarm_B to the INTRB. |           |

| 1   | 0   | Outputs Alarm_A, Alarm_B to the INTRA. Outputs 32k clock pulses, INT to the INTRB. |           |

| 1   | 1   | Outputs Alarm_A to the INTRA. Outputs 32k clock pulses, Alarm_B, INT to the INTRB. |           |

By setting SL1 and SL2 bits, two alarm pulses (Alarm\_A and alarm\_B), periodic interrupt output (INT), 32k clock pulses may be output to the  $\overline{\text{INTRA}}$  or  $\overline{\text{INTRB}}$  pins selectively.

#### 2.1-3 TEST

#### Test bit

| TEST | Description             |           |

|------|-------------------------|-----------|

| 0    | Ordinary operation mode | (Default) |

| 1    | Test mode               |           |

The test bit is used for IC test. Set the TEST bit to 0 in ordinary operation.

(Default)

#### 2.1-4 CT2, CT1, CT0

Periodic interrupt cycle select bit

| ОТО | 0.74 | ОТО | Description    |                                                                            |  |

|-----|------|-----|----------------|----------------------------------------------------------------------------|--|

| CT2 | CT1  | СТ0 | Wave form mode | Cycle and falling timing                                                   |  |

| 0   | 0    | 0   | _              | off ("H")                                                                  |  |

| 0   | 0    | 1   | _              | Fixed at "L"                                                               |  |

| 0   | 1    | 0   | Pulse mode     | 2Hz (Duty50%)                                                              |  |

| 0   | 1    | 1   | Pulse mode     | 1Hz (Duty50%)                                                              |  |

| 1   | 0    | 0   | Level mode     | Every second (synchronized with second count up)                           |  |

| 1   | 0    | 1   | Level mode     | Every minute (00 second of every minute)                                   |  |

| 1   | 1    | 0   | Level mode     | Every hour (00 minute(s) 00 second(s) of every hour)                       |  |

| 1   | 1    | 1   | Level mode     | Every month (the 1st day 00 A.M. 00 minute(s) 00 second(s) of every month) |  |

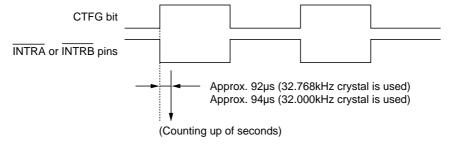

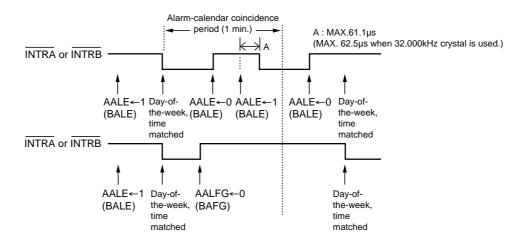

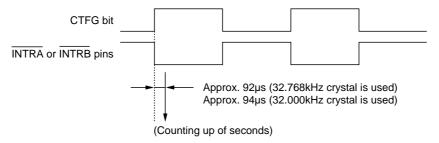

1) Pulse mode: Outputs 2Hz, 1Hz clock pulses. For relationships with counting up of seconds see the diagram below.

- \*) When 32.000kHz crystal is used, In the 2Hz clock pulse mode, 0.496s clock pulses and 0.504s clock pulse are output alternately. Duty cycle for 1Hz clock pulses becomes 50.4% ("L" duration is 0.496s while "H" duration is 0.504s).

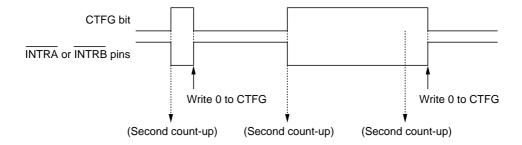

- 2) Level mode: One second, one minute or one month may be selected for an interrupt cycle. Counting up of seconds is matched with falling edge of interrupt output.

- 3) When the time trimming circuit is used, periodic interrupt cycle changes every 20 seconds.

Pulse mode: "L" duration of output pulses may change in the maximum range of ±3.784ms (±3.875ms when 32.000kHz crystal is used.)

For example, Duty will be 50±0.3784% (or 50±0.3875% when 32.000kHz crystal is used) at 1Hz.

Level mode: Frequency in one second may change in the maximum range of  $\pm 3.784$ ms ( $\pm 3.875$ ms when 32.000kHz crystal is used.)

Relation Between Mode Waveforms and CTFG Bit

#### Pulse mode

\*) Since counting up of seconds and the falling edge has a time lag of approx. 92µs (at 32.768kHz) (approx. 94µs when 32.000kHz crystal is used), time with apparently approx. one second of delay from time of the real-time clock may be read when time is read in synchronization with the falling edge of output.

#### • Level mode

#### 2.2 Control Register 2 (at internal address Fh)

| D7 | D6 | D5        | D4   | D3   | D2   | D1   | D0   |

|----|----|-----------|------|------|------|------|------|

| _  | _  | 12/24     | ADJ  | CLEN | CTFG | AAFG | BAFG |

| 0  | 0  | 12/24     | XSTP | CLEN | CTFG | AAFG | BAFG |

| 0  | 0  | Undefined | 1    | 0    | 0    | 0    | 0    |

(For write operation)

(For read operation)

Default\*

#### $2.2-1 \overline{12}/24$

12/24-hour Time Display System Selection bit

| T2/24 Description |                                                                      |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------|--|--|--|--|--|

| 0                 | 0 12-hour time display system (separate for mornings and afternoons) |  |  |  |  |  |

| 1                 | 24-hour time display system                                          |  |  |  |  |  |

Being set this bit at "0" indicates 12-hour display system while "1" indicates 24-hour system.

#### Time Display Digit Table

| 24-hour time display system | 12-hour time display system | 24-hour time display system | 12-hour time display system |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| 00                          | 12 (AM12)                   | 12                          | 32 (PM12)                   |

| 01                          | 01 (AM 1)                   | 13                          | 21 (PM 1)                   |

| 02                          | 02 (AM 2)                   | 14                          | 22 (PM 2)                   |

| 03                          | 03 (AM 3)                   | 15                          | 23 (PM 3)                   |

| 04                          | 04 (AM 4)                   | 16                          | 24 (PM 4)                   |

| 05                          | 05 (AM 5)                   | 17                          | 25 (PM 5)                   |

| 06                          | 06 (AM 6)                   | 18                          | 26 (PM 6)                   |

| 07                          | 07 (AM 7)                   | 19                          | 27 (PM 7)                   |

| 08                          | 08 (AM 8)                   | 20                          | 28 (PM 8)                   |

| 09                          | 09 (AM 9)                   | 21                          | 29 (PM 9)                   |

| 10                          | 10 (AM10)                   | 22                          | 30 (PM10)                   |

| 11                          | 11 (AM11)                   | 23                          | 31 (PM11)                   |

<sup>\*)</sup> Either the 12-hour or 24-hour time display system should be selected before writing time data.

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

#### 2.2-2 ADJ

#### ±30 Second Adjust Bit

| ADJ | Description             |  |  |  |  |

|-----|-------------------------|--|--|--|--|

| 0   | Ordinary operation      |  |  |  |  |

| 1   | Second digit adjustment |  |  |  |  |

- · The following operations are performed by setting the second ADJ bit to 1.

- 1) For second digits ranging from "00" to "29" seconds: Time counters smaller than seconds are reset and second digits are set to "00".

- 2) For second digits ranging from "30" to "59" seconds:

Time counters smaller than seconds are reset and second digits are set to "00". Minute digits are incremented by 1.

- · Second digits are adjusted within 122µs (within 125µs: when 32.000kHz crystal is used) from writing operation to ADI.

- · The ADJ bit is for write only and allows no read operation.

#### 2.2-3 XSTP

#### Oscillator Halt Sensing Bit

| XSTP | Description             |  |  |  |  |  |

|------|-------------------------|--|--|--|--|--|

| 0    | Ordinary oscillation    |  |  |  |  |  |

| 1    | Oscillator halt sensing |  |  |  |  |  |

(Default)

The XSTP bit senses the oscillator halt.

- · When oscillation is halted after initial power on from 0V or drop in supply voltage the bit is set to "1" and which remains to be "1" after it is restarted. This bit may be used to judge validity of clock and calendar count data after power on or supply voltage drop.

- · When this bit is set to "1",  $\overline{XSL}$ , F6 to F0, CT2, CT1, CT0, AALE, BALE, SL2, SL1,  $\overline{CLEN}$  and TEST bits are reset to "0".  $\overline{INTRA}$  will stop output and the  $\overline{INTRB}$  will output 32kHz clock pulses.

- · The XSTP bit is set to "0" by setting the control register 2 (address Fh) during ordinary oscillation.

#### 2.2-4 CLEN

#### 32kHz Clock Output Bit

| CLEN | Description                 |  |  |  |  |  |

|------|-----------------------------|--|--|--|--|--|

| 0    | 32kHz clock output enabled  |  |  |  |  |  |

| 1    | 32kHz clock output disabled |  |  |  |  |  |

By setting this bit to "0", output of clock pulses of the same frequency as the crystal oscillator is enabled.

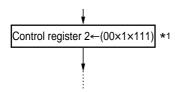

#### 2.2-5 CTFG

#### Periodic Interrupt Flag Bit

| CTFG | Description                         |  |  |  |  |  |

|------|-------------------------------------|--|--|--|--|--|

| 0    | Periodic interrupt output=OFF ("H") |  |  |  |  |  |

| 1    | Periodic interrupt output=ON ("L")  |  |  |  |  |  |

This bit is set to "1" when periodic interrupt pulses are output (INTRA or INTRB="L").

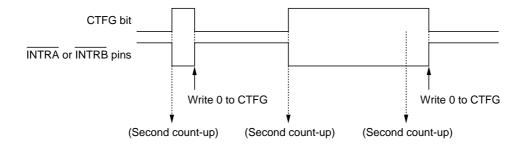

The CTFG bit may be set only to "0" in the interrupt level mode. Setting this bit to "0" sets either the INTRA or the INTRB to OFF ("H"). When this bit is set to "1" nothing happens.

#### 2.2-6 AAFG, BAFG

Alarm\_A (Alarm\_B) Flag Bit

| AAFG, BAFG | Description                                 |           |

|------------|---------------------------------------------|-----------|

| 0          | Unmatched alarm register with clock counter | (Default) |

| 1          | Matched alarm register with clock counter   |           |

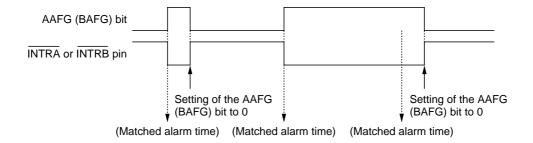

- · The alarm interruption is enabled only when the AALE, BALE bits are set to "1". This bit turns to "1" when matched time is sensed for each alarm.

- The AAFG, BAFG bit may be set only to "0". Setting this bit to "0" sets either the INTRA or the INTRB to the "H". When this bit is set to "1" nothing happens.

- · When the AALE, BALE bit is set to "0", alarm operation is disabled and "0" is read from the AAFG, BAFG bit.

#### Output Relationships Between the ALFG Bit and INTRA or INTRB

#### 2.3 Clock Counter (at internal address 0-2h)

· Time digit display (in BCD code)

Second digits: Range from 00 to 59 and carried to minute digits when incremented from 59 to 00.

Minute digits: Range from 00 to 59 and carried to hour digits when incremented from 59 to 00.

Hour digits : See descriptions on the  $\overline{12}/24$  bit (Section 2.2-1).

Carried to day and day-of-the-week digits when incremented from 11 p.m. to 12 a.m. or 23 to 00.

· Any registered imaginary time should be replaced with correct time as carrying to such registered imaginary time digits from lower-order ones cause the clock counter malfunction.

#### 2.3-1 Second digit register (at internal address 0h)

| D7 | D6        | D5        | D4        | D3        | D2        | D1             | D0        |                       |

|----|-----------|-----------|-----------|-----------|-----------|----------------|-----------|-----------------------|

| _  | S40       | S20       | S10       | S8        | S4        | S <sub>2</sub> | S1        | (For write operation) |

| 0  | S40       | S20       | S10       | S8        | S4        | S2             | S1        | (For read operation)  |

| 0  | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined      | Undefined | Default*              |

#### 2.3-2 Minute digit register (at internal address 1h)

| D7 | D6        | D5        | D4        | D3        | D2        | D1             | D0        |                       |

|----|-----------|-----------|-----------|-----------|-----------|----------------|-----------|-----------------------|

| _  | M40       | M20       | M10       | M8        | M4        | M <sub>2</sub> | M1        | (For write operation) |

| 0  | M40       | M20       | M10       | M8        | M4        | M <sub>2</sub> | M1        | (For read operation)  |

| 0  | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined      | Undefined | Default*              |

#### 2.3-3 Hour digit register (at internal address 2h)

| D7 | D6 | D5         | D4        | D3        | D2        | D1        | D0        |                       |

|----|----|------------|-----------|-----------|-----------|-----------|-----------|-----------------------|

|    | _  | P/A or H20 | H10       | Н8        | H4        | H2        | H1        | (For write operation) |

| 0  | 0  | P/A or H20 | H10       | Н8        | H4        | H2        | H1        | (For read operation)  |

| 0  | 0  | Undefined  | Undefined | Undefined | Undefined | Undefined | Undefined | Default*              |

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

#### 2.4 Day-of-the-week Counter (at internal address 3h)

- · Day-of-the-week digits are incremented by 1 when carried to 1-day digits.

- $\cdot\,$  Day-of-the-week digits display (incremented in septimal notation):

$(W_4, W_2, W_1) = (0,0,0) \rightarrow (0,0,1) \rightarrow \cdots \rightarrow (1,1,0) \rightarrow (0,0,0)$

- · The relation between days of the week and day-of-the-week digits is user changeable (e.g. Sunday=0,0,0).

- $\cdot$  The (W<sub>4</sub>, W<sub>2</sub>, W<sub>1</sub>) should not be set to (1, 1, 1).

| D7 | D6 | D5 | D4 | D3 | D2        | D1             | D0        |                       |

|----|----|----|----|----|-----------|----------------|-----------|-----------------------|

| _  | _  | _  | _  | _  | W4        | $W_2$          | W1        | (For write operation) |

| 0  | 0  | 0  | 0  | 0  | W4        | W <sub>2</sub> | W1        | (For read operation)  |

| 0  | 0  | 0  | 0  | 0  | Undefined | Undefined      | Undefined | Default*              |

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

#### 2.5 Calendar Counter (at internal address 4 to 6h)

· The automatic calendar function provides the following calendar digit displays in BCD code.

Day digits : Range from 1 to 31 (for January, March, May, July, August, October, and December).

Range from 1 to 30 (for April, June, September, and November).

Range from 1 to 29 (for February in leap years).

Range from 1 to 28 (for February in ordinary years).

Carried to month digits when cycled to 1.

Month digits: Range from 1 to 12 and carried to year digits when cycled to 1.

Year digits : Range from 00 to 99 and 00, 04, 08,..., 92, and 96 are counted as leap years.

· Any registered imaginary time should be replaced with correct time as carrying to such registered imaginary time digits from lower-order ones cause the clock counter malfunction.

#### 2.5-1 Day digit register (at internal address 4h)

| D7 | D6 | D5        | D4        | D3        | D2        | D1        | D0        |                       |

|----|----|-----------|-----------|-----------|-----------|-----------|-----------|-----------------------|

| _  | _  | D20       | D10       | D8        | D4        | D2        | D1        | (For write operation) |

| 0  | 0  | D20       | D10       | D8        | D4        | D2        | D1        | (For read operation)  |

| 0  | 0  | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined | Default*              |

#### 2.5-2 Month digit register (at internal address 5h)

| D7 | D6 | D5 | D4        | D3        | D2        | D1              | D0              |                       |

|----|----|----|-----------|-----------|-----------|-----------------|-----------------|-----------------------|

| _  | _  | _  | MO10      | MO8       | MO4       | MO <sub>2</sub> | MO <sub>1</sub> | (For write operation) |

| 0  | 0  | 0  | MO10      | MO8       | MO4       | MO <sub>2</sub> | MO <sub>1</sub> | (For read operation)  |

| 0  | 0  | 0  | Undefined | Undefined | Undefined | Undefined       | Undefined       | Default*              |

#### 2.5-3 Year digit register (at internal address 6h)

| D7        | D6        | D5        | D4        | D3        | D2        | D1        | D0        |                       |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------------|

| Y80       | Y40       | Y20       | Y10       | Y8        | Y4        | Y2        | Y1        | (For write operation) |

| Y80       | Y40       | Y20       | Y10       | Y8        | Y4        | Y2        | Y1        | (For read operation)  |

| Undefined | Default*              |

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

#### 2.6 Time Trimming Register (at internal address 7h)

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                       |

|-----|----|----|----|----|----|----|----|-----------------------|

| XSL | F6 | F5 | F4 | F3 | F2 | F1 | Fo | (For write operation) |

| XSL | F6 | F5 | F4 | F3 | F2 | F1 | Fo | (For read operation)  |

| 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Default*              |

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

#### 2.6-1 XSL bit

The XSL bit is used to select a crystal oscillator.

Set the  $\overline{\text{XSL}}$  to "0" (default) to use 32.768kHz.

Set the  $\overline{\text{XSL}}$  to "1" to use 32.000kHz.

#### 2.6-2 F<sub>6</sub> to F<sub>0</sub>

The time trimming circuit adjust one second count based on this register readings when second digit is 00, 20, or 40 seconds. Normally, counting up to seconds is made once per 32,768 of clock pulse (or 32,000 when 32.000kHz crystal is used) generated by the oscillator. Setting data to this register activates the time trimming circuit.

Register counts will be incremented as ((F5, F4, F3, F2, F1, F0)-1)×2 when F6 is set to "0".

Register counts will be decremented as  $(\overline{(F_5, F_4, F_3, F_2, F_1, F_0)}+1)\times 2$  when F6 is set to "1".

Counts will not change when  $(F_6, F_5, F_4, F_3, F_2, F_1, F_0)$  are set to  $(\star, 0, 0, 0, 0, 0, \star)$ .

For example, when 32.768kHz crystal is used.

When (F<sub>6</sub>, F<sub>5</sub>, F<sub>4</sub>, F<sub>3</sub>, F<sub>2</sub>, F<sub>1</sub>, F<sub>0</sub>) are set to (0, 0, 0, 0, 1, 1, 1), counts will change as:  $32,768+(7-1)\times2=32,780$  (clock will be delayed) when second digit is 00, 20, or 40.

When (F<sub>6</sub>, F<sub>5</sub>, F<sub>4</sub>, F<sub>3</sub>, F<sub>2</sub>, F<sub>1</sub>, F<sub>0</sub>) are set to (0, 0, 0, 0, 0, 0, 1), counts will remain 32,768 without changing when second digit is 00, 20, or 40.

When (F<sub>6</sub>, F<sub>5</sub>, F<sub>4</sub>, F<sub>3</sub>, F<sub>2</sub>, F<sub>1</sub>, F<sub>0</sub>) are set to (1, 1, 1, 1, 1, 1, 0), counts will change as:  $32,768+(-2)\times2=32,764$  (clock will be advanced) when second digit is 00, 20, or 40.

Adding 2 clock pulses every 20 seconds:  $2/(32,768\times20)=3.051$ ppm (or 3.125ppm when 32.000kHz crystal is used), delays the clock by approx. 3ppm. Likewise, decrementing 2 clock pulses advances the clock by 3ppm. Thus the clock may be adjusted to the precision of  $\pm 1.5$ ppm. Note that the time trimming function only adjust clock timing and oscillation frequency and 32kHz clock output is not adjusted.

#### 2.7 Alarm\_A, Alarm\_B Register (Alarm\_A: internal address 8 to Ah; Alarm\_B: internal address B to Dh)

#### 2.7-1 Alarm\_A minute register (internal address 8h)

| D7 | D6        | D5        | D4               | D3        | D2        | D1              | D0        |                       |

|----|-----------|-----------|------------------|-----------|-----------|-----------------|-----------|-----------------------|

| _  | AM40      | AM20      | AM <sub>10</sub> | AM8       | AM4       | AM <sub>2</sub> | AM1       | (For write operation) |

| 0  | AM40      | AM20      | AM <sub>10</sub> | AM8       | AM4       | AM <sub>2</sub> | AM1       | (For read operation)  |

| 0  | Undefined | Undefined | Undefined        | Undefined | Undefined | Undefined       | Undefined | Default*              |

#### 2.7-2 Alarm\_B minute register (internal address Bh)

| D7 | D6        | D5        | D4        | D3        | D2        | D1              | D0        |                       |

|----|-----------|-----------|-----------|-----------|-----------|-----------------|-----------|-----------------------|

| _  | BM40      | BM20      | BM10      | BM8       | BM4       | BM <sub>2</sub> | BM1       | (For write operation) |

| 0  | BM40      | BM20      | BM10      | BM8       | BM4       | BM <sub>2</sub> | BM1       | (For read operation)  |

| 0  | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined       | Undefined | Default*              |

#### 2.7-3 Alarm\_A hour register (internal address 9h)

| D7 | D6 | D5         | D4        | D3        | D2        | D1        | D0        |                       |

|----|----|------------|-----------|-----------|-----------|-----------|-----------|-----------------------|

| _  | _  | AH20, AP/A | AH10      | AH8       | AH4       | AH2       | AH1       | (For write operation) |

| 0  | 0  | AH20, AP/Ā | AH10      | AH8       | AH4       | AH2       | AH1       | (For read operation)  |

| 0  | 0  | Undefined  | Undefined | Undefined | Undefined | Undefined | Undefined | Default*              |

#### 2.7-4 Alarm\_B hour register (internal address Ch)

| D7 | D6 | D5         | D4        | D3        | D2        | D1        | D0        |                       |

|----|----|------------|-----------|-----------|-----------|-----------|-----------|-----------------------|

| _  | _  | BH20, AP/A | BH10      | BH8       | BH4       | BH2       | BH1       | (For write operation) |

| 0  | 0  | BH20, AP/A | BH10      | BH8       | BH4       | BH2       | BH1       | (For read operation)  |

| 0  | 0  | Undefined  | Undefined | Undefined | Undefined | Undefined | Undefined | Default*              |

#### 2.7-5 Alarm\_A day-of-the-week register (internal address Ah)

| D7 | D6        | D5        | D4        | D3        | D2              | D1        | D0              |                       |

|----|-----------|-----------|-----------|-----------|-----------------|-----------|-----------------|-----------------------|

| _  | AW6       | AW5       | AW4       | AW3       | AW <sub>2</sub> | AW1       | AW <sub>0</sub> | (For write operation) |

| 0  | AW6       | AW5       | AW4       | AW3       | AW2             | AW1       | AW <sub>0</sub> | (For read operation)  |

| 0  | Undefined | Undefined | Undefined | Undefined | Undefined       | Undefined | Undefined       | Default*              |

#### 2.7-6 Alarm\_B day-of-the-week register (internal address Dh)

| D7 | D6        | D5        | D4        | D3        | D2              | D1        | D0              |                       |

|----|-----------|-----------|-----------|-----------|-----------------|-----------|-----------------|-----------------------|

| _  | BW6       | BW5       | BW4       | BW3       | BW <sub>2</sub> | BW1       | BW <sub>0</sub> | (For write operation) |

| 0  | BW6       | BW5       | BW4       | BW3       | BW <sub>2</sub> | BW1       | BW <sub>0</sub> | (For read operation)  |

| 0  | Undefined | Undefined | Undefined | Undefined | Undefined       | Undefined | Undefined       | Default*              |

<sup>\*)</sup> The default means read value when XSTP bit is set to "1" by starting up from 0V, or supply voltage drop, etc.

- · Alarm\_A, Alarm\_B hour register D5 is set to 0 for AM and 1 for PM in the 12-hour display system at AP/ $\overline{A}$ . The register D5 indicates 10 digit of hour digit in 24-hour display system at AH<sub>20</sub>.

- · To activate alarm operation, any imaginary alarm time setting should not be left to avoid unmatching.

- · In hour digit display midnight is set to 12, noon is set to 32 in 12-hour display system. (See section 2.2-1)

- · AW<sub>0</sub> to AW<sub>6</sub> correspond to the day-of-the-week counter (W<sub>4</sub>, W<sub>2</sub>, W<sub>1</sub>) being set at (0, 0, 0) to (1, 1, 0).

- · No alarm pulses are output when all of AWo to AW6 are set to "0".

#### **Example of Alarm Time Settings**

|                                              |   |             | Day- | of-the- | week |   |             | 1       | 2-hour | syste  | m     | 24-hour system |        |        |       |

|----------------------------------------------|---|-------------|------|---------|------|---|-------------|---------|--------|--------|-------|----------------|--------|--------|-------|

| Alarm Time Settings                          |   | Mon.<br>AW1 |      |         |      |   | Sat.<br>AW6 | 10-hour | 1-hour | 10-min | 1-min | 10-hour        | 1-hour | 10-min | 1-min |

| 00:00 AM every day                           | 1 | 1           | 1    | 1       | 1    | 1 | 1           | 1       | 2      | 0      | 0     | 0              | 0      | 0      | 0     |

| 01:30 AM every day                           | 1 | 1           | 1    | 1       | 1    | 1 | 1           | 0       | 1      | 3      | 0     | 0              | 1      | 3      | 0     |

| 11:59 AM every day                           | 1 | 1           | 1    | 1       | 1    | 1 | 1           | 1       | 1      | 5      | 9     | 1              | 1      | 5      | 9     |

| 00:00 PM on<br>Monday through Friday         | 0 | 1           | 1    | 1       | 1    | 1 | 0           | 3       | 2      | 0      | 0     | 1              | 2      | 0      | 0     |

| 01:30 PM on Sunday                           | 1 | 0           | 0    | 0       | 0    | 0 | 0           | 2       | 1      | 3      | 0     | 1              | 3      | 3      | 0     |

| 11:59 PM on Monday,<br>Wednesday, and Friday | 0 | 1           | 0    | 1       | 0    | 1 | 0           | 3       | 1      | 5      | 9     | 2              | 3      | 5      | 9     |

Designation of days of the week and AW0 to AW6 in the above table is an example.

#### **OPERATION**

#### 1. Interfacing with the CPU

The RS5C372A employs the I<sup>2</sup>CBus system to be connected to the CPU via 2-wires. Connection and transfer system of I<sup>2</sup>CBus are described in the following sections.

Note

I<sup>2</sup>CBus is a trademark of PHILIPS ELECTRONICS N.V.

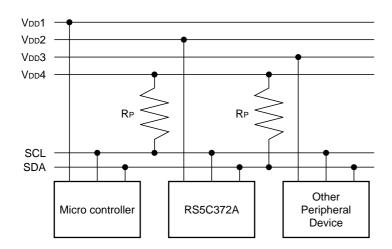

#### 1.1 Connection of I2CBus

2-wires, SCL and SDA which are connected to I<sup>2</sup>CBus are used for transmit clock pulses and data respectively. All ICs that are connected to these lines are designed that will be not be clamped when a voltage beyond supply voltage is applied to input or output pins. Open drain pins are used for output. This construction allows communication of signals between ICs with different supply voltages by adding a pull-up resistor to each signal line as shown in the figure below. Each IC is designed not to affect SCL and SDA signal lines when power to each of these is turned off separately.

- \*) For data interface, the following conditions must be met:

VDD4≥VDD1

VDD4≥VDD2

VDD4≥VDD3

- \*) When the master is one, the micro controller is ready for driving SCL to "H" and RP of SCL may not be required.

#### Cautions on Determining RP Resistance

- (1) Voltage drop at RP due to sum of input current or output current at off conditions on each IC pin connected to the I<sup>2</sup>CBus shall be adequately small.

- (2) Rising time of each signal shall be kept short even when all capacity of the bus is driven.

- (3) Current consumed in I<sup>2</sup>CBus is small compared to the consumption current permitted for the entire system.

When all ICs connected to I<sup>2</sup>CBus are CMOS type, condition (1) may usually be ignored since input current and off state output current is extremely small for the many CMOS type ICs.

Thus the maximum resistance of RP may be determined based on (2) while the minimum on (3) in most cases.

In actual cases a resistor may be place between the bus and input/output pins of each IC to improve noise margins in which case the RP minimum value may be determined by the resistance.

Consumption current in the bus to review (3) above may be expressed by the formula below:

Bus consumption current = (Sum of input current and off state output current of all devices in stand-by mode) × Bus stand-by duration

Bus stand-by duration + bus operation duration

Supply voltage  $\times$  bus operation duration  $\times$  2

RP resistance  $\times$  2  $\times$  (bus stand-by duration + bus operation duration)

+ supply voltage × bus capacity × charging/discharging times per unit time

Operation of "x 2" in the second member denominator in the above formula is derived from assumption that "L" duration of SDA and SCL pins are the half of bus operation duration. "x 2" in the numerator of the same member is because there are two pins of SDA and SCL. The third member, (charging/discharging times per unit time) means number of transition from "H" to "L" of the signal line.

Calculation example is shown below:

Pull-up resistor (RP)=10kΩ, Bus capacity=50pF (both for SCL and SDA), VDD=3V

In as system with sum of input current and off state output current of each pin= $0.1\mu$ A, I<sup>2</sup>CBus is used for 10ms every second while the rest of 990ms is in the stand-by mode. In this mode number of transitions of the SCL pin from "H" to "L" state is 100 while SDA 50, every second.

Bus consumption current

$$=$$

$\frac{0.1 \mu A \times 990 ms}{990 ms + 10 ms}$  +  $\frac{3V \times 10 ms \times 2}{10 k\Omega \times 2 \times (990 ms + 10 ms)}$  +  $3V \times 50 pF \times (100 + 50)$  =  $0.099 \mu A + 3.0 \mu A + 0.0225 \mu A = 3.12 \mu A$

Generally, the second member of the above formula is larger enough than the first and the third members, bus consumption current may be determined by the second member in many cases.

#### 1.2 Transmission System of I<sup>2</sup>CBus

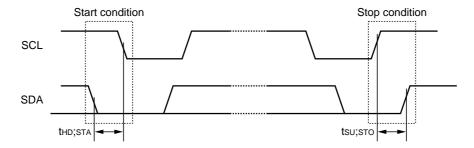

#### 1.2-1 Start and stop conditions

In I<sup>2</sup>CBus, SDA must be kept at a certain state while SCL is at the "H" state as shown below during data transmission.

The SCL and SDA pins are at the "H" level when no data transmission is made. Changing the SDA from "H" to "L" when the SCL and the SDA are "H" activates the start condition and access is started. Changing the SDA from "L" to "H" when the SCL is "H" activates stop condition and accessing stopped. Generation of start and stop conditions are always made by the master (see the figure below).

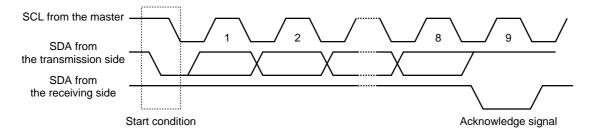

#### 1.2-2 Data transmission and its acknowledge

After start condition is entered, data is transmitted by 1byte (8bits). Any bytes of data may be serially transmitted. The receiving side will send an acknowledge signal to the transmission side each time 8bit data is transmitted.

The acknowledge signal is sent immediately after falling to "L" of SCL8bit clock pulses of data transmission, by releasing the SDA by the transmission side that has asserted the bus at that time and by turning the SDA to "L" by the receiving side. When transmission of 1byte data next to preceding 1byte of data is received the receiving side releases the SDA pin at falling edge of the SCL9bit of clock pulses or when the receiving side switches to the transmission side it starts data transmission. When the master is the receiving side, it generates no acknowledge signal after the last 1byte of data from the slave to tell the transmitter that data transmission has completed when the slave side (transmission side) continues to release the SDA pin so that the master will be able to generate stop condition.

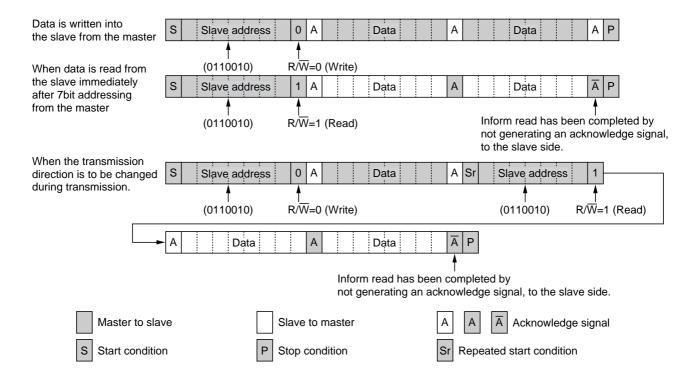

#### 1.2-3 Data transmission format in I<sup>2</sup>CBus

I<sup>2</sup>CBus generates no CE signals. In place of it each device has a 7bit slave address allocated. The first 1byte is allocated to this 7bit of slave address and to the command  $(R/\overline{W})$  for which data transmission direction is designated by the data transmission thereafter. 7bit address is sequentially transmitted from the MSB and 2 and after bytes are read, when 8bit is "H" and write when "L".

The slave address of the RS5C372A is specified at (0110010).

At the end of data transmission/receiving stop condition is generated to complete transmission. However, if start condition is generated without generating stop condition, repeated start condition is met and transmission/receiving data may be continued by setting the slave address again. Use this procedures when the transmission direction needs to be changed during one transmission.

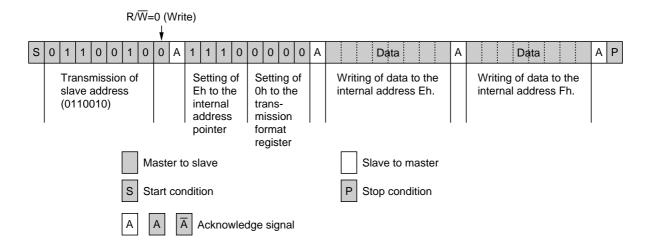

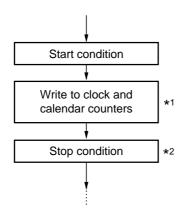

#### 1.2-4 Data transmission write format in the RS5C372A

Although the I<sup>2</sup>CBus standard defines a transmission format for the slave address allocated for each IC, transmission method of address information in IC is not defined. The RS5C372A transmits data the internal address pointer (4bit) and the transmission format register (4bit) at the 1byte next to one which transmitted a slave address and a write command. For write operation only one transmission format is available and (0000) is set to the transmission format register. The 3byte transmits data to the address specified by the internal address pointer written to the 2byte. Internal address pointer settings are automatically incremented for 4byte and after. Note that when the internal address pointer is Fh, it will change to 0h on transmitting the next byte.

Example of data writing (When writing to internal address Eh to Fh)

#### 1.2-5 Data transmission read format of the RS5C372A

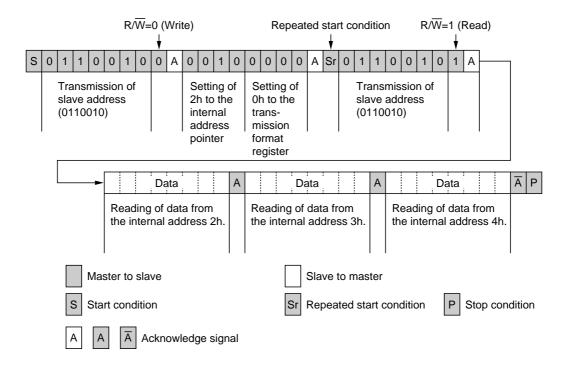

The RS5C372A allows the following three readout methods of data from an internal register.

1) The first method to reading data from the internal register is to specify an internal address by setting the internal address pointer and the transmission format register described 1.2-4, generate the repeated start condition (see section 1.2-3) to change the data transmission direction to perform reading. The internal address pointer is set to Fh when the stop condition is met. Therefore, this method of reading allows no insertion of the stop condition before the repeated start condition. Set 0h to the transmission format register.

Example 1 of data read (when data is read from 2h to 4h)

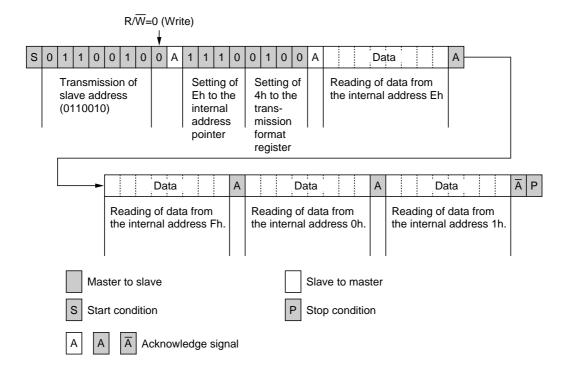

2) The second method to reading data from the internal register is to start reading immediately after writing to the internal address pointer and the transmission format register. Although this method is not based on the I<sup>2</sup>CBus standard in a strict sense it still effective to shorten read time to ease load to the master. Set 4h to the transmission format register when this method is used.

Example 2 of data read (when data is read from internal addresses Eh to 1h).

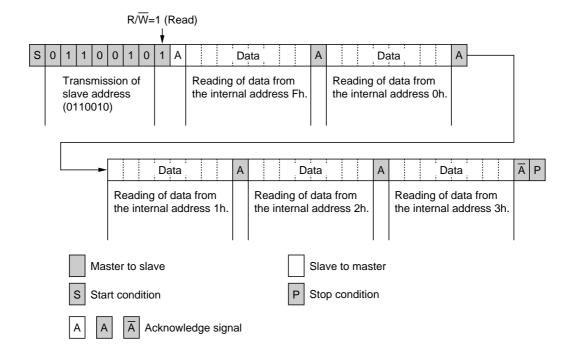

3) The third method to reading data from the internal register is to start reading immediately after writing to the slave address and the  $R/\overline{W}$  bit. Since the internal address pointer is set to Fh by default as described in 1), this method is only effective when reading is started from the internal address Fh.

Example 3 of data read (when data is read from internal addresses Fh to 3h).

#### 1.2-6 Data transmission under special condition

The RS5C372A holds the clock tentatively for duration from start condition to stop condition to avoid invalid read or write clock on carrying clock. When clock is carried during this period, which will be adjusted within approx. 61µs from stop condition. To prevent invalid read or write clock shall be made during one transmission operation (from start condition to stop condition). When 0.5 to 1.0 second elapses after start condition any access to the RS5C372A is automatically released to release tentative hold of the clock, set Fh to the address pointer, and access from the CPU is forced to be terminated (the same action as made stop condition is received: automatic resume function from the I²CBus interface). Therefore, one access must be completed within 0.5 seconds. The automatic resume function prevents delay in clock even if the SCL is stopped from sudden failure of the system during clock read operation.

Also a second start condition after the first condition and before the stop condition is regarded as the "repeated start condition." Therefore, when 0.5 to 1.0 seconds passed after the first start condition, access to the RS5C372A is automatically released.

If access is tried after automatic resume function is activated, no acknowledge signal will be output for writing while FFh will be output for reading.

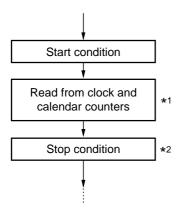

#### Access to the Real-time Clock

- 1) No stop condition shall be generated until clock read/write is started and completed.

- 2) One cycle read/write operation shall be completed within 0.5 seconds.

The user shall always be able to access the real-time clock as long as these two conditions are met.

Bad example of reading from seconds to hours (invalid read)

$(Start\ condition) \rightarrow (Read\ of\ seconds) \rightarrow (Read\ of\ minutes) \rightarrow (Stop\ condition) \rightarrow (Start\ condition) \rightarrow (Read\ of\ hour) \rightarrow (Stop\ condition)$

Assuming read was started at 05:59:59 P.M. and while reading seconds and minutes the time advanced to 06:00:00 P.M. At this time second digit is hold so the read as 05:59:59. Then the RS5C372A confirms (Stop condition) and carries second digit being hold and the time changes to 06:00:00 P.M. Then, when the hour digit is read, it changes to 6. The wrong results of 06:59:59 will be read.

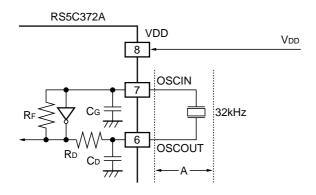

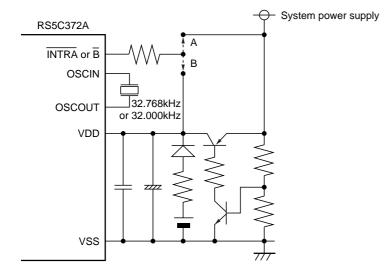

#### 2. Configuration of Oscillating Circuit and Time Trimming

#### 2.1 Configuration of Oscillating Circuit

Typical external device:

X'tal: 32.768kHz or 32.000kHz (R1= $30k\Omega$  TYP.) (CL=6pF to 8pF)

Typical values of internal devices:

$R_F=15M\Omega$  TYP.  $R_D=60k\Omega$  TYP.  $C_G$ ,  $C_D=10pF$  TYP.

The oscillation circuit is driven at a constant voltage of about 1.2V relative to the Vss level.

Consequently, it generates a wave form having a peak-to-peak amplitude of about 1.2V on the positive side of the Vss level.

#### Considerations on Crystal Oscillator

Basic characteristics of a crystal oscillator includes R1 (equivalent series resistance: ease of oscillation) and CL (load capacitance: rank of center frequency). R1=TYP. of  $30k\Omega$ , CL=6 to 8pF is recommended for the RS5C372A. Confirm recommended values to the manufacturer of the crystal oscillator used.

#### Considerations in Mounting Components Surrounding Oscillating Circuit

- 1) Mount the crystal oscillators in the closest possible position to the IC.

- 2) Avoid laying any signal or power line close to the oscillation circuit (particularly in the area marked with " $\leftarrow$  A  $\rightarrow$ " in the above figure).

- 3) Apply the highest possible insulation resistance between the OSCIN or OSCOUT pin and the PCB.

- 4) Avoid using any long parallel line to wire the OSCIN and OSCOUT pin.

- 5) Take extreme care not to cause condensation, which leads to various problems such as oscillation halt.

#### Other Relevant Considerations

- 1) When applying an external input of clock pulses (32.768kHz or 32.000kHz) to the OSCIN pin:

- DC coupling: Prohibited due to mismatching of input levels.

- AC coupling: Permissible except that unpredictable results may occur in oscillator halt sensing due to possible sensing errors caused by noises, etc.

- 2) Avoid using the oscillator output of the RS5C372A (from the OSCOUT pin) to drive any other IC for the purpose of ensuring stable oscillation.

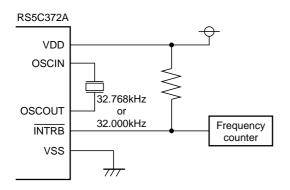

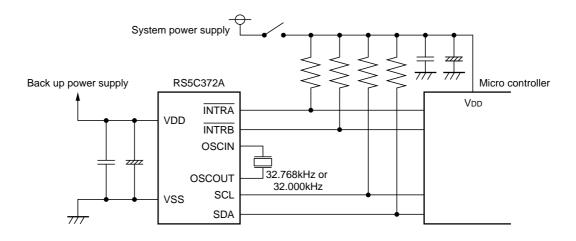

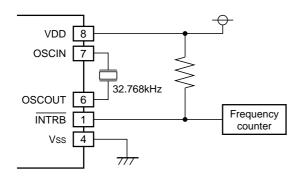

#### 2.2 Measurement of Oscillation Frequency

- \*1) Clock pulse of 32.768kHz or 32.000kHz is output from the INTRB output pin on powering on (XSTP is set to 1).

- \*2) Use a frequency counter having at least 6 digits (7digits or more recommended).

- $\star$ 3) Pull-up the  $\overline{\text{INTRB}}$  output pin to VDD.

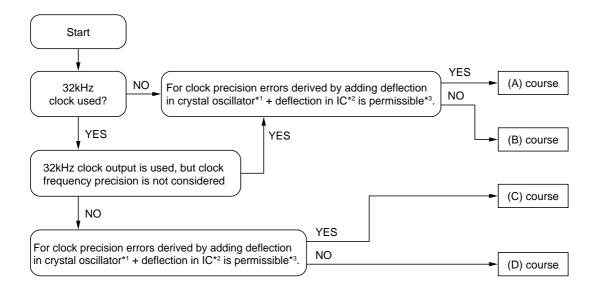

#### 2.3 Oscillation Frequency Adjustment

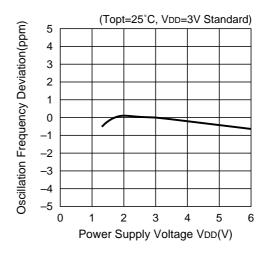

Adjustment amount of oscillation frequency may differ dependent on how the RS5C372A is used or how much clock error is permissible in the system it is installed. Use the flow chart shown below find an optimal oscillation frequency adjustment method.

- \*1) In general crystal oscillators are classified by their central frequency of CL (load capacitance) and available further grouped in several ranks as ±10, ±20 and ±50ppm of fluctuations in precision.

- \*2) Fluctuations in frequency due to the IC used is generally from ±5 to 10ppm at a room temperature.

- \*3) Clock precision here is at a room temperature and is subjected to change due to temperature characteristics of the crystal itself.

#### (A) course

Adjustment of clock is not made for IC (no adjustment) and any CL value may be used for the crystal oscillator. Precision fluctuations of a crystal oscillator may be selected as long as clock precision allows. Obtain the central frequency as described in section 2.2 using several crystal oscillator and ICs, determine an adjustment value as described in "2.4 Time Trimming Circuit" which shall be set to the RS5C372A.

#### (B) course

To keep clock precision within the range of (fluctuation in crys-tal oscillator + fluctuation in IC), clock shall be adjustment is required for each IC. On adjusting procedures see "2.4 Time Trimming Circuit." Available selection range for the frequency precision fluctuations and CL (load capacitance) for a crystal oscillator may be widened by adjusting clock frequency. Obtain the central frequency as described in section 2.2 using the crystal oscillator and IC to be used, determine if an adjustment is possible or not using the clock adjustment circuit, perform adjustment for each IC using the clock adjustment circuit. Up to ±1.5ppm may be adjusted at a room temperature.

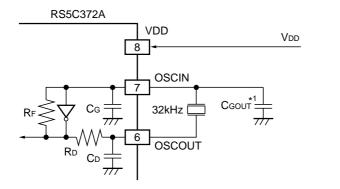

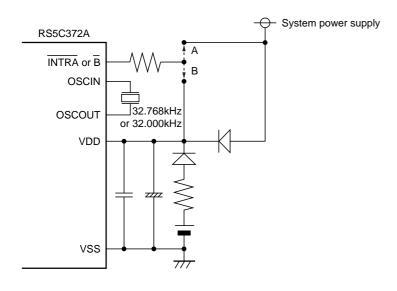

#### (C) course

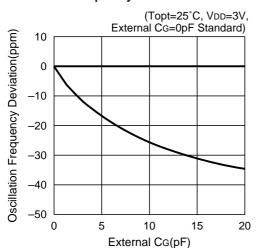

In (C) and (D) courses, adjustment of 32kHz clock output frequency as well as clock is necessary. Frequency adjustment for the crystal oscillator is made by adjusting both of CG and CD connected to the both ends of the oscillator. Since the RS5C372A incorporates the CG and CD, oscillating frequency is required using CL of the crystal oscillator as the reference.

Generally, relation between CL and CG or CD is as follows:

$$CL = \frac{CG \times CD}{CG + CD} + Cs$$

Cs: Board floating capacitance

Although a crystal oscillator having CL value of around 6 to 8pF is recommended for the RS5C372A, measure oscillation frequency as described in section 2.2 and if frequency is high (clock gains) switch to a crystal oscillator with smaller CL while if frequency is small (clock loses) switch to an oscillator with larger CL. Using these procedures select a crystal oscillator with optimal CL and set unadjusted value to the clock adjustment circuit. (See section 2.4, "Time Trimming Circuit".) We recommend to consult the crystal manufacturer on compatibility of CL values. High oscillation frequency (clock gains) may be adjusted by externally adding CGOUT as shown below.

#### \*1) CGOUT shall be from 0 to 15pF.

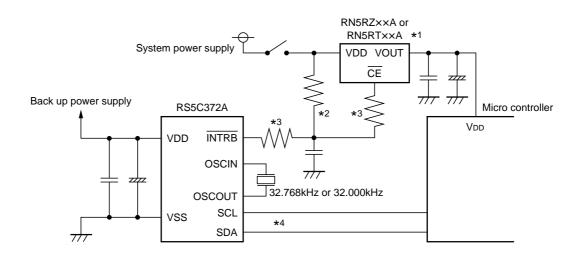

#### (D) course

Select a crystal oscillator as in the (C) course, then adjust clock error for each IC as in (B) course. For clock adjusting procedures, see "2.4 Time Trimming Circuit."

#### 2.4 Time Trimming Circuit

Using the time trimming circuit gain or lose of clock may be adjusted with high precision by changing clock pulses for one second every 20 seconds. When adjustment with this circuit is not necessary, set (F6, F5, F4, F3, F2, F1, F0) to  $(\star, 0, 0, 0, 0, 0, \star)$  to disable adjustment. ( $\star$  mark indicates 0 or 1.)

Adjustment amount may be calculated using the following formula.

#### 2.4-1 When oscillation frequency\*1 >target frequency\*2 (clock gains)

Adjustment amount\*3 =

$$\frac{\text{(Oscillation frequency - Target frequency + 0.1)}}{\text{Oscillation frequency} \times 3.051 \times 10^{-6}}$$

$\rightleftharpoons \text{(Oscillation frequency - Target frequency)} \times 10 + 1$

When 32.000kHz crystal oscillator is used, the same formula,

Adjustment amount =

$$\frac{\text{(Oscillation frequency - Target frequency + 0.1)}}{\text{Oscillation frequency } \times 3.125 \times 10^{-6}}$$

$= \text{(Oscillation frequency - Target frequency)} \times 10 + 1$

is used.

\*1) Oscillation frequency: Clock frequency output from the INTRB pin as in "2.2 Oscillation Frequency Measurement" at a room temperature.

\*2) Target frequency : A frequency to be adjusted to.

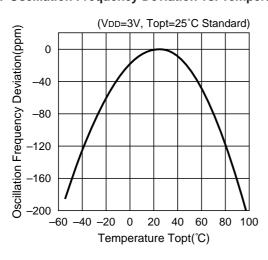

Since temperature characteristics of a 32.768kHz crystal oscillator are such that it will generally generates the highest frequency at a room temperature, we recommend to set the target frequency to approx. 32768.00Hz to 32768.10Hz (+3.05ppm to 32768Hz).

We also recommend setting of approx. 32000.00Hz to 32000.10Hz (3.125ppm to 32000Hz) also for the 32.000kHz crystal.

Note that this value may differ based on the environment or place where the device will be used.

\*3) Adjustment amount : A value to be set finally to F6 to F0 bits. This value is expressed in 7bit binary digits with sign bit (two's compliment).

#### 2.4-2 When oscillation frequency=target frequency (no clock gain or loss)

Set the adjustment value to 0 or +1, or -64 or -63 to disable adjustment.

#### 2.4-3 When oscillation frequency<target frequency (clock loses)

Adjustment amount =

$$\frac{\text{(Oscillation frequency - Target frequency)}}{\text{Oscillation frequency} \times 3.051 \times 10^{-6}}$$

$\Rightarrow$  (Oscillation frequency - Target frequency) × 10

Also a 32.000kHz crystal is used, the same formula,

Adjustment amount =

$$\frac{\text{(Oscillation frequency - Target frequency)}}{\text{Oscillation frequency} \times 3.051 \times 10^{-6}}$$

$\rightleftharpoons \text{(Oscillation frequency - Target frequency)} \times 10$

is used.

#### **Example of Calculations**

(1) When oscillation frequency=32768.85kHz ; target frequency=32768.05kHz Adjustment value=  $(32768.85-32768.05+0.1) / (32768.85\times3.051\times10^{-6}) = (32768.85+32768.05)\times10+1=9.001=9$

As this example shows, adjustments to be used when the clock gains shall be distance from 01h.

(2) When actual oscillation frequency=32763.95kHz; target frequency=32768.05kHz

Adjustment value= (32763.95–32768.05) / (32763.95×3.051×10⁻⁶) ≒ (32763.95–32768.05)×10=−41.015≒−41

To express −41 in 7bit binary digits with sign bit (two's compliment),

Thus, set (F6, F5, F4, F3, F2, F1, F0) to (1, 0, 1, 0, 1, 1, 1).

Subtract 41(29h) from 128(80h) in the above case, 80h–29h=57h.

Set (F6, F5, F4, F3, F2, F1, F0) to (0, 0, 0, 1, 0, 0, 1).

As this example shows, adjustments to be used when the clock loses shall be distance from 80h.

After adjustment, adjustment error against the target frequency will be approx. ±1.5ppm at a room temperature.

#### Notes

- 1) Clock frequency output from the INTRB pin will not change after adjustment by the clock adjustment circuit.