Network access

# RS8250/1/2/3/4/5 ATM Physical Interface Devices - ATM PHY

datasheet

PROVIDING

HIGH

SPEED

MULTIMEDIA

CONNECTIONS

### **Preliminary Information**

This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

# RS8250/1/2/3/4/5

### ATM Physical Interface Devices—ATM PHY

The RS825x is a family of six 155 Mbps (OC-3/STM-1) ATM-SONET Physical Layer (PHY) devices with an integrated, low-jitter PLL clock and data recovery circuit. These devices have optimized SONET framer functions for mapping ATM cells to SONET payloads for edge switch applications, and optional enhanced feature sets for ATM-WAN access applications. They provide ATM Forum compliant service termination, and map the 53-byte cells from an ATM switch fabric or an adaptation layer processor (SAR) into the SONET payload. Available in single, dual, and quad port packages, as well as LAN and WAN versions, the RS825x devices are tailored to meet a wide variety of ATM OC-3 applications, including WAN terminals, ATM LAN and WAN switches, ATM OC-3 NICs, and Ethernet-ATM uplink cards.

The RS825x family thus consists of six devices, with three devices in each of two categories, WAN and LAN. All references to the RS825x in this document apply to the entire family of RS825x devices, unless otherwise noted.

The RS825x uses an ATM Forum UTOPIA Level 2 compliant host interface designed for a multi-PHY environment. The ATM framer provides G.804 cell processing, with HEC generation, checking and alignment operations. Each port provides a 155 Mbps SONET termination with all of the counters needed for capturing both SONET and ATM error events as specified by the ATM Forum. A proprietary protection scheme allows for near-instantaneous switching between active and stand-by PHYs.

The RS825x family uses a Pseudo-Emitter Coupled Logic (PECL) line interface, that is compliant with the ATM Forum's WIRE definition. Thus, designers can connect directly to either fiber optic or Cat 5 Physical Media Dependent (PMD) devices. For diagnostics, three loopback modes are provided: source loopback, line loopback before the ATM processor, and line loopback at the UTOPIA block. In addition, the RS825x can generate BIP-8 errors and insert invalid HECs.

The WAN versions of the device (RS8250/2/4), support full compliance with the jitter requirements of Bellcore's GR-253-CORE, as well as support for Automatic Protection Switching (APS) using the K1/K2 overhead octets and a Bit Error Rate (BER) integrator. The WAN devices also support access to the S1 octet for system timing, as well as data transmission/reception over the Data Link message channels, D1-D3 and D4-D12.

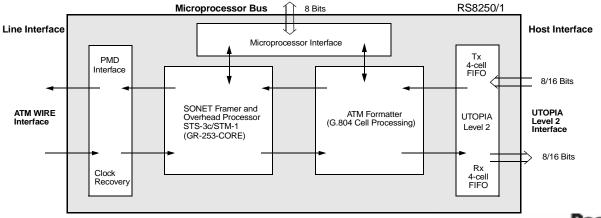

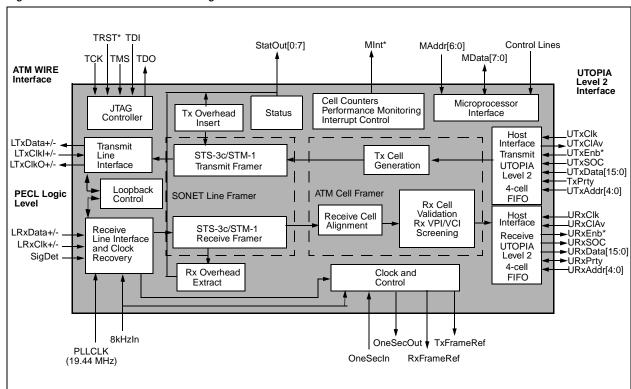

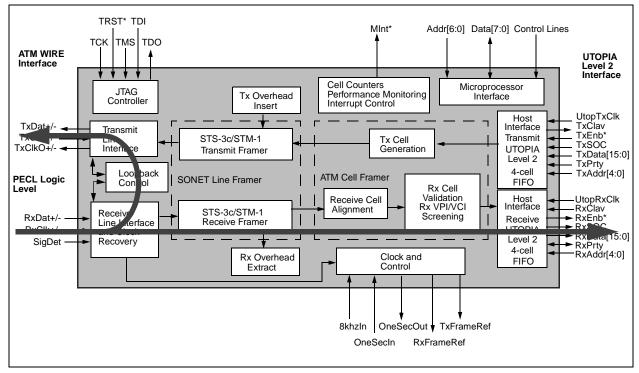

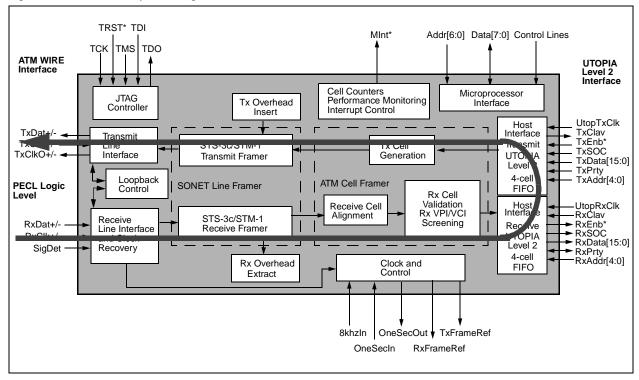

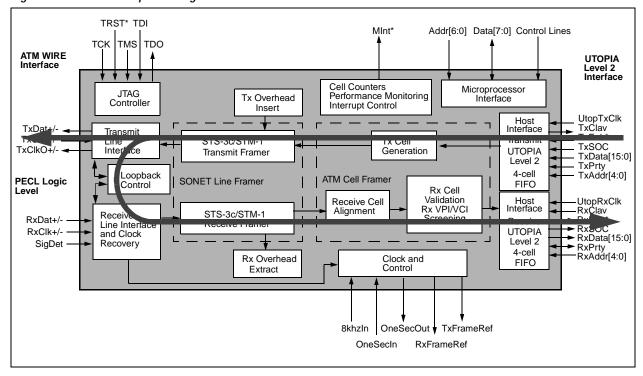

### RS8250/1 Functional Block Diagram

### **Distinguishing Features**

- Synthesizes a 155.52 MHz clock from an 8 kHz input.

- · UTOPIA Level 2 interface.

- Meets ITU, ANSI, and ATM Forum standards.

- ATM Forum WIRE interface for PMDs using PECL.

- D1-D3, D4-D12 external data link (WAN only).

- Supports APS (K1/K2 bytes)(WAN only).

- SRAM-style microprocessor interface for all control and configuration registers.

- Glueless interface to the Bt/RS823x segmentation and reassembly devices.

- JTAG (IEEE 1149.1a-1993) compliant

- 8 kHz and 19.44 MHz selectable sync inputs and outputs.

- SONET overhead processing.

- Automatic collection of one-second statistics.

- Low power consumption-500 mW/ port.

- · Rapid start after reset.

- · Reference software provided.

- 3.3 V, (-40° to 85° C).

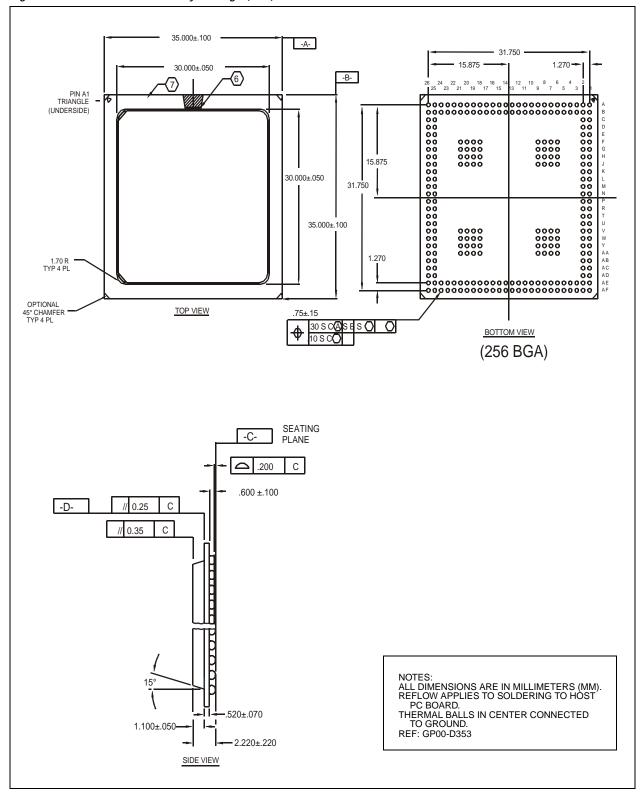

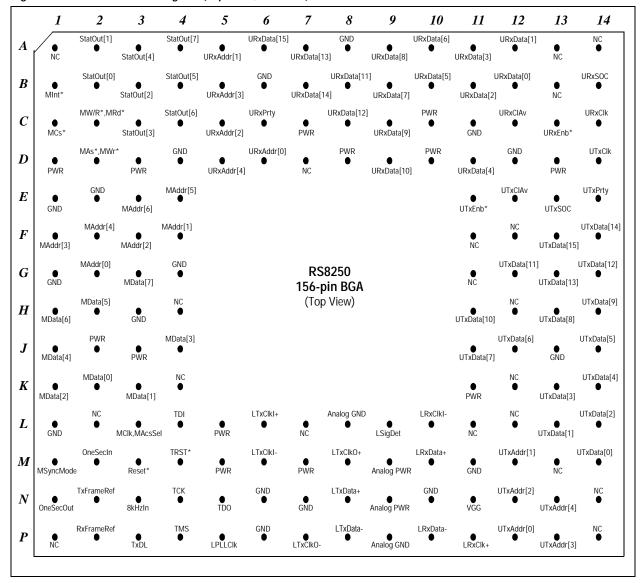

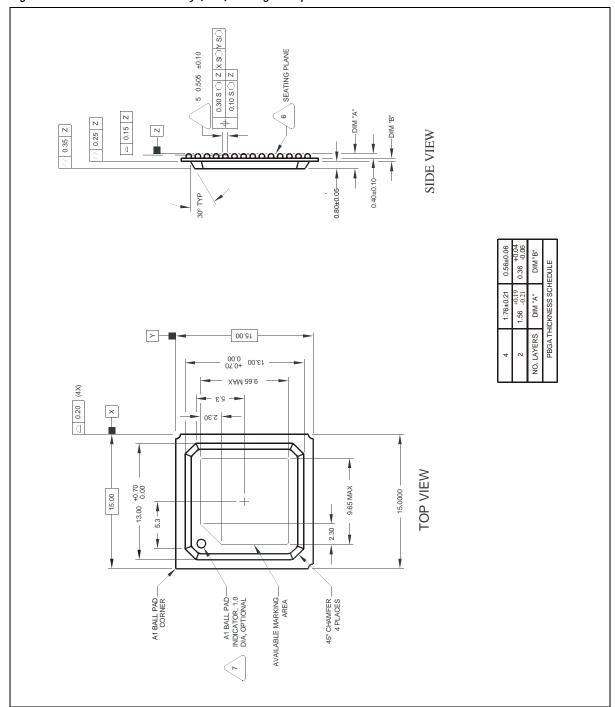

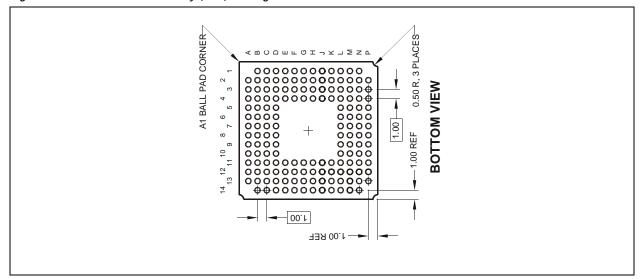

- Packages: 128-pin TQFP (RS8251), 156-pin BGA (RS8250), and 256-pin BGA (RS8252/3/4/5).

### **Applications**

- · Switches, Hubs, Routers

- · LAN NIC cards

- DSLAM uplinks

### **Ordering Information**

| Model Number | Manufacturing<br>Part Number | Product<br>Revision | Package            | Operating Temperature |

|--------------|------------------------------|---------------------|--------------------|-----------------------|

| RS8250EBGC   | 28250-14                     | С                   | 156-pin, 15 mm BGA | -40°C to 85°C         |

| RS8251ETFB   | 28251-13                     | В                   | 128-pin TPQFP      | -40°C to 85°C         |

| RS8252EBG    | R7171-11                     | А                   | 256-pin, 35 mm BGA | -40°C to 85°C         |

| RS8253EBG    | R7172-11                     | А                   | 256-pin, 35 mm BGA | -40°C to 85°C         |

| RS8254EBG    | R7173-11                     | А                   | 256-pin, 35 mm BGA | -40°C to 85°C         |

| RS8255EBG    | R7174-11                     | А                   | 256-pin, 35 mm BGA | -40°C to 85°C         |

| RS8254EBGB   | R7173-12                     | В                   | 256-pin, 35 mm BGA | -40°C to 85°C         |

Copyright © 1998 Rockwell Semiconductor Systems, Inc. All rights reserved.

Print date: September 1998

Rockwell Semiconductor Systems, Inc. reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or intellectual property rights of Rockwell Semiconductor Systems, Inc.

Rockwell Semiconductor Systems, Inc. products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Rockwell Semiconductor Systems, Inc. product can reasonably be expected to result in personal injury or death. Rockwell Semiconductor Systems, Inc. customers using or selling Rockwell Semiconductor Systems, Inc. products for use in such applications do so at their own risk and agree to fully indemnify Rockwell Semiconductor Systems, Inc. for any damages resulting from such improper use or sale.

Bt is a registered trademark of Rockwell Semiconductor Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

### RS825x Features

### Line Interface

- ATM Forum WIRE interface specification compliant

- PECL I/O, compatible with PMD optical and UTP interface devices

- · Clock recovery from NRZ input data

- Recovery of receive-octet alignment and octet clock from F6/28 framing pattern

- Select transmit clock from input or recovered receive clock

- PMD (line) and Framer (source) loopbacks for diagnostic testing

- · Loss of Signal (LOS) detection

- 8 kHz or 19.44 MHz reference clock

### **UTOPIA** Level 2 Interface

- · PHY cell to UTOPIA interface

- 50 MHz maximum data rate

- 8/16-bit data path interface

- Multi-PHY support

- · Mode-compatible with UTOPIA level 1

- · Configurable cell buffer depth

### SONET STS\_3c/STM-1 Framer

### **Section Overhead Octets Supported**

|            | Transmit                                | Receive                                      |

|------------|-----------------------------------------|----------------------------------------------|

| A1/A2      | F6/28 hex or disable 00                 | Monitor out of frame state machine           |

| J0         | 01 hex or 64-byte trace buffer          | Monitor Rx trace buffer, interrupt on change |

| Z0, Z0     | 02, 03 hex                              | Not checked                                  |

| B1         | Calculated, error insertion             | Checked, errors counted                      |

| D1, D2, D3 | 00 hex or external data link (WAN only) | External data link (WAN only)                |

### **Line Overhead Octets Supported**

|        | Transmit                                | Receive                                 |

|--------|-----------------------------------------|-----------------------------------------|

| H1/H2  | 620A/93FF hex pointer                   | Full GR.253 pointer processor           |

| H3     | Set to 00                               | Used in pointer processor               |

| B2     | Calculated, error insertion             | Checked, errors counted                 |

| K1/K2  | Insertable via register (WAN only)      | Checked, interrupt on change (WAN only) |

| D4-D12 | 00 hex or external data link (WAN only) | External data link (WAN only)           |

| S1     | Insertable via register (WAN only)      | Checked, interrupt on change (WAN only) |

| M1     | Line FEBE inserted                      | Checked, errors counted                 |

### **Path Overhead Octets Supported**

|    | Transmit                       | Receive                                      |

|----|--------------------------------|----------------------------------------------|

| J1 | 00 hex or 64-byte trace buffer | Monitor Rx trace buffer, interrupt on change |

| B3 | Calculated, error insertion    | Checked, errors counted                      |

| C2 | 13 hex for ATM mapping         | Checked for 01 or 13 hex                     |

| G1 | Path FEBE, RDI inserted        | Checked, errors counted, status              |

### **Sonet Framer Functions**

- Recovers frame location using F6/28 framing pattern.

- Processes pointer to locate payload envelope.

- · Provides OOF, LOP, and AIS status.

- Provides frame and payload position information to other blocks.

- Generates clocks and frame counters.

- · Maps cell data into payload envelope.

- Generates all section, line, and path overhead and alarms.

- Performs cell and frame scrambling before transmission.

- Detects and integrates alarms for reporting in status registers.

- Detects BIP and FEBE errors for error counters.

- Recovers D1-D3 and D4-D12 data link (WAN only).

### **Cell Alignment Framing Section**

- · Recovers cell alignment from HEC.

- · Performs HEC error correction.

- Matches idle/desired cell headers and generates write strobes and cell sync for UTOPIA interface.

- Generates cell status bits, cell counts, and error counts.

- · Reads cell data from the UTOPIA FIFO.

- Inserts headers and generates HEC.

- Inserts idle cells when no traffic is ready.

### Support for Automatic Protection Switching (APS) (WAN only)

- Register control allows for support of APS.

- K1/K2 Transmit control register allows transmission of any value.

- · Separate control bits for AIS, line FERF.

- K1/K2 receive status register allows observation of incoming octet values.

- Maskable interrupt on any change in received value.

- Software interrupt routine can easily implement APS protocol.

- Signal Fail/Signal Detect BER threshold monitoring.

### **Control and Status**

### Microprocessor Interface

- SRAM-like interface mode with high performance or low-power access selection

- Glueless RS8233/4 SAR interface mode

- 8-bit data bus

- · Open-drain interrupt output

### **Counters/Status and Interrupt Registers**

- · Summary interrupt indications

- · Configuration of interrupt enables

- · One-second status latching

- · One-second counter latching

- Eight general purpose outputs, configurable as status indicator pins

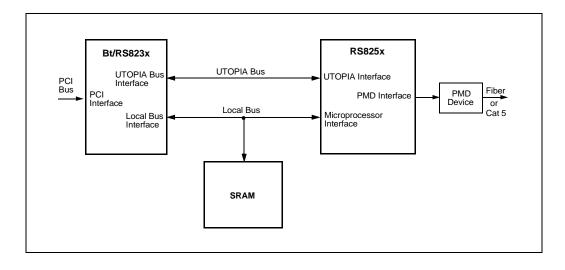

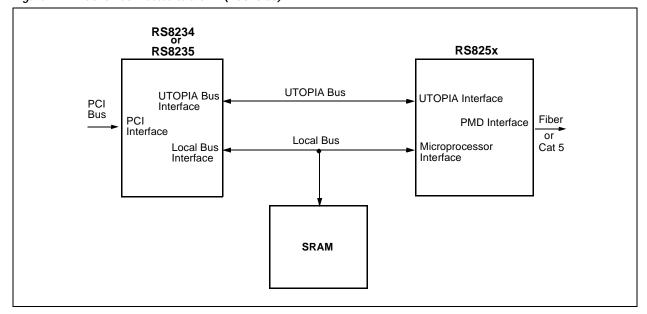

The following diagram is a Network Interface Card (NIC) application of the RS825x.

# **Table of Contents**

| List of Figures                                                                  | xi   |

|----------------------------------------------------------------------------------|------|

| List of Tables                                                                   | xiii |

| 1.0 Product Description                                                          | 1-1  |

| 1.1 RS825x Features                                                              | 1-2  |

| 1.2 Applications Overview                                                        | 1-3  |

| 1.3 Logic Diagram                                                                | 1-4  |

| 1.4 Pin Diagram and Definitions                                                  | 1-5  |

| 1.5 Block Diagram and Descriptions                                               | 1-15 |

| 2.0 Functional Description                                                       | 2-1  |

| 2.1 Line Interface         2.1.1 TTL/PECL Interface         2.1.2 PECL Interface | 2-3  |

| 2.2 Clock Circuits                                                               |      |

| 2.3 Serial-Parallel Conversion                                                   | 2-7  |

| 2.4 SONET/SDH Framer and Overhead Processor                                      | 2-8  |

| 2.4.1 Loss of Signal                                                             | 2-11 |

| 2.4.2.2 Loss of Frame                                                            |      |

| 2.4.2.3 B1                                                                       |      |

| 2.4.2.4 D1-D3                                                                    |      |

| 2.4.2.5 J0                                                                       |      |

| 2.4.3 Line Overhead                                                              |      |

| 2.4.3.1 H1, H2, and H3                                                           |      |

| 2.4.3.2 Loss of Pointer                                                          |      |

| 2.4.3.3 B2-1, B2-2, and B2-3                                                     |      |

| 2.4.3.4 APS Threshold (WAN only)         2.4.3.5 K1 and K2 (WAN only)            |      |

| 2.4.5.5 KT dHu KZ (WAIN UHIY)                                                    | ∠-10 |

|       | 2.4.3.6 Line RDI/AIS Detect              | 2-17  |

|-------|------------------------------------------|-------|

|       | 2.4.3.7 D4-12                            | 2-17  |

|       | 2.4.3.8 S1 (WAN only)                    | 2-17  |

|       | 2.4.3.9 M1                               | 2-18  |

|       | 2.4.4 Path Overhead                      |       |

|       | 2.4.4.1 J1                               |       |

|       | 2.4.4.2 B3                               |       |

|       | 2.4.4.3 C2                               |       |

|       | 2.4.4.4 G1                               |       |

|       | 2.4.5 SONET Frame Scrambler              |       |

| 2.5   | ATM Cell Processor                       | 2-22  |

|       | 2.5.1 ATM Cell Transmitter               |       |

|       | 2.5.1.1 HEC Generation                   |       |

|       | 2.5.2 ATM Cell Receiver                  |       |

|       | 2.5.2.1 Cell Delineation                 |       |

|       | 2.5.2.2 Cell Screening.                  |       |

|       | 2.5.3 Cell Payload Scrambler             | 2-25  |

| 2.6   | Data Link Interface                      | 2-26  |

|       | 2.6.1 Data Link Transmit                 | 2-27  |

|       | 2.6.2 Data Link Receive                  | 2-28  |

| 2.7   | UTOPIA Interface                         | 2-29  |

|       | 2.7.1 UTOPIA Transmit and Receive FIFOs  | 2-29  |

|       | 2.7.2 UTOPIA 8-bit and 16-bit Bus Widths | 2-30  |

|       | 2.7.3 UTOPIA Parity                      | 2-31  |

|       | 2.7.4 UTOPIA Multi-PHY Operation         | 2-31  |

|       | 2.7.5 Handshaking                        | 2-32  |

| 2.8   | Microprocessor Interface                 | 2-33  |

|       | 2.8.1 Status and Control                 | 2-33  |

|       | 2.8.2 Counters                           | 2-34  |

|       | 2.8.3 One-second Latching                | 2-34  |

|       | 2.8.4 Interrupts                         | 2-35  |

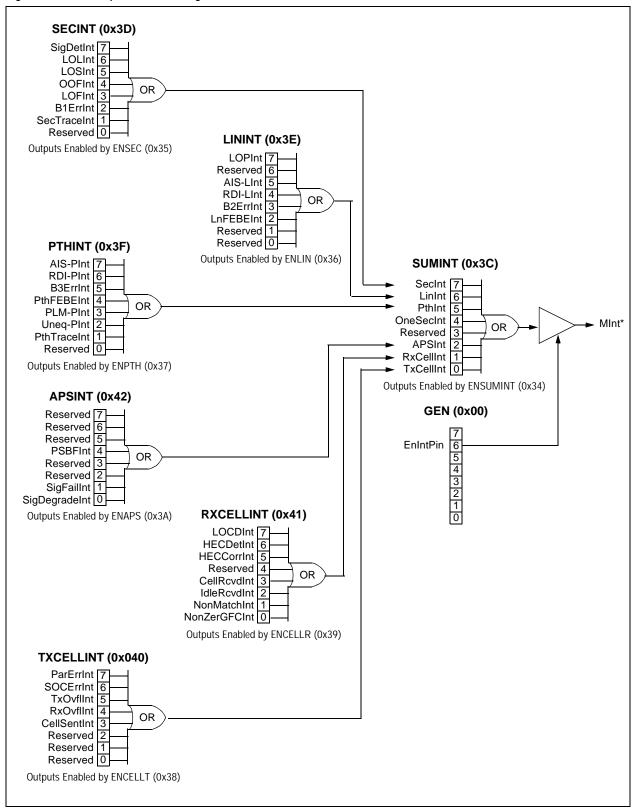

|       | 2.8.4.1 Interrupt Routing                | 2-35  |

|       | 2.8.4.2 Interrupt Servicing              | 2-38  |

| 2.9   | Loopback Modes                           | 2-39  |

|       | 2.9.1 Line Loopback                      | 2-39  |

|       | 2.9.2 UTOPIA Loopbacks                   | 2-40  |

|       | 2.9.3 Source Loopback                    | 2-41  |

| 20 1- | polications                              | 2 1   |

| _     | pplications                              |       |

|       | System Application                       |       |

| 3.2   | PECL Applications                        |       |

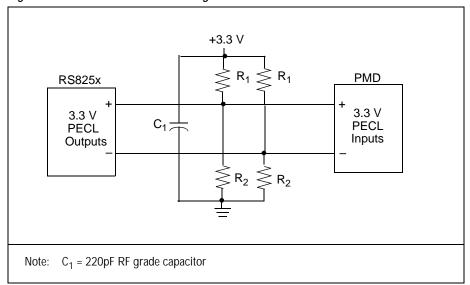

|       | 3.2.1 RS825x to 3.3 V PMD                |       |

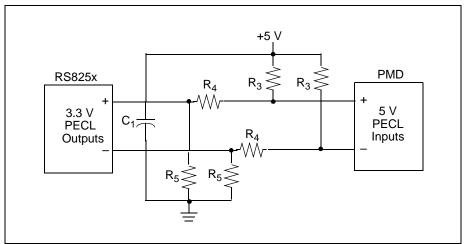

|       | 3.2.2 RS825x to 5 V PMD Inputs           | . 3-4 |

| ATM Physical Interface Devices—ATM PHY                                                                                                                    |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2.3 RS825x to 5 V PMD Outputs       3         3.2.4 PECL Layout       3         3.2.5 The RS825x/RS8235 Network Interface Card Reference Design       3 | -6 |

| 4.0 Registers                                                                                                                                             | -1 |

| 4.1 General Use Registers 4                                                                                                                               | -6 |

| 0x00—GEN (General Control Register)                                                                                                                       | -6 |

| 0x01—CLKREC (Clock Recovery Control Register)                                                                                                             |    |

| 0x02—OUTSTAT (Output Pin Control Register)                                                                                                                |    |

| 0x03—VERSION (Part Number/Version Status Register)4                                                                                                       |    |

| 4.2 Cell Transmit Control Registers                                                                                                                       |    |

| 0x04—CGEN (Cell Generation Control Register)                                                                                                              |    |

| 0x05—IDLPAY (Transmit Idle Cell Payload Control Register)                                                                                                 |    |

| 0x1C—TXHDR1 (Transmit Cell Header Control Register 1)                                                                                                     |    |

| 0x1D—TXHDR2 (Transmit Cell Header Control Register 2)                                                                                                     |    |

| 0x1E—TXHDR3 (Transmit Cell Header Control Register 3)                                                                                                     |    |

| 0x1F—TXHDR4 (Transmit Cell Header Control Register 4)       4-7         0x20—TXIDL1 (Transmit Idle Cell Header Control Register 1)       4-7              |    |

| 0x20—TXIDL1 (Transmit Idle Cell Header Control Register 2)                                                                                                |    |

| 0x22—TXIDL3 (Transmit Idle Cell Header Control Register 3)                                                                                                |    |

| 0x23—TXIDL4 (Transmit Idle Cell Header Control Register 4)                                                                                                |    |

| 4.3 Cell Receive Control Registers                                                                                                                        |    |

| 0x08—CVAL (Cell Validation Control Register)                                                                                                              |    |

| 0x24—RXHDR1 (Receive Cell Header Control Register 1)                                                                                                      |    |

| 0x25—RXHDR2 (Receive Cell Header Control Register 2)                                                                                                      |    |

| 0x26—RXHDR3 (Receive Cell Header Control Register 3)4-                                                                                                    |    |

| 0x27—RXHDR4 (Receive Cell Header Control Register 4)4-                                                                                                    |    |

| 0x28—RXMSK1 (Receive Cell Mask Control Register 1)                                                                                                        |    |

| 0x29—RXMSK2 (Receive Cell Mask Control Register 2)                                                                                                        | 18 |

| 0x2A—RXMSK3 (Receive Cell Mask Control Register 3)                                                                                                        | 19 |

| 0x2B—RXMSK4 (Receive Cell Mask Control Register 4)                                                                                                        |    |

| 0x2C—RXIDL1 (Receive Idle Cell Header Control Register 1)                                                                                                 |    |

| 0x2D—RXIDL2 (Receive Idle Cell Header Control Register 2)                                                                                                 |    |

| 0x2E—RXIDL3 (Receive Idle Cell Header Control Register 3)                                                                                                 |    |

| 0x2F—RXIDL4 (Receive Idle Cell Header Control Register 4)                                                                                                 |    |

| 0x30—IDLMSK1 (Receive Idle Cell Mask Control Register 1)       4-2         0x31—IDLMSK2 (Receive Idle Cell Mask Control Register 2)       4-2             |    |

| 0x31—IDLMSK3 (Receive Idle Cell Mask Control Register 3)                                                                                                  |    |

| 0x32—IDEMSK4 (Receive Idle Cell Mask Control Register 4)                                                                                                  |    |

|                                                                                                                                                           |    |

| 4.4 UTOPIA Control Registers                                                                                                                              |    |

| 0x0A—UTOP1 (UTOPIA Control Register 1)       4-2         0x0B—UTOP2 (UTOPIA Control Register 2)       4-2                                                 |    |

| -                                                                                                                                                         |    |

| 4.5 SONET Overhead Transmit Control Registers 4-2                                                                                                         |    |

| 0x06—ERRINS (Error Insertion Control Register)                                                                                                            | 26 |

|     | 0x07—ERRPAT (Error Pattern Control Register)                        | . 4-27 |

|-----|---------------------------------------------------------------------|--------|

|     | 0x0C—TXSEC (Transmit Section Overhead Control Register)             | . 4-27 |

|     | 0x68—TXSECBUF (Transmit Section Trace Circular Buffer)              |        |

|     | 0x0D—TXLIN (Transmit Line Overhead Control Register)                | . 4-28 |

|     | 0x0E—TXPTH (Transmit Path Overhead Control Register)                | . 4-29 |

|     | 0x69—TXPTHBUF (Transmit Path Trace Circular Buffer)                 |        |

|     | 0x10—TXK1 (Transmit K1 Overhead Control Register) (WAN Only)        | . 4-30 |

|     | 0x11—TXK2 (Transmit K2 Overhead Control Register) (WAN Only)        | . 4-30 |

|     | 0x12—TXS1 (Transmit S1 Overhead Control Register) (WAN Only)        | . 4-31 |

|     | 0x13—TXC2 (Transmit C2 Overhead Control Register)                   | . 4-31 |

| 4.6 | SONET Overhead Receive Control Registers                            | 4-32   |

|     | 0x6A—RXSECBUF (Receive Section Trace Circular Buffer)               |        |

|     | 0x6B—RXPTHBUF (Receive Path Trace Circular Buffer)                  |        |

|     | 0x09—APSTHRESH (APS Threshold Control Register) (WAN Only)          | . 4-33 |

|     | 0x14—RXK1 (Receive K1 Overhead Status Register) (WAN Only)          |        |

|     | 0x15—RXK2 (Receive K2 Overhead Status Register) (WAN Only)          | . 4-34 |

|     | 0x16—RXS1 (Receive S1 Overhead Status Register) (WAN Only)          | . 4-34 |

|     | 0x18—RXC2 (Receive C2 Overhead Status Register)                     | . 4-35 |

|     | 0x19—RXG1 (Receive G1 Overhead Status Register)                     | . 4-35 |

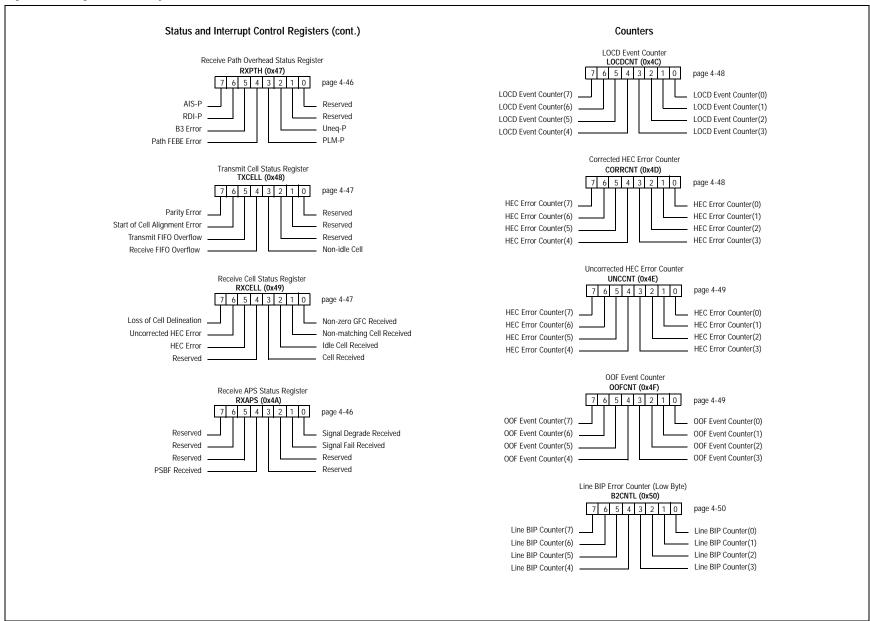

| 4.7 | Status and Interrupt Registers                                      | 4-36   |

|     | 0x34—ENSUMINT (Summary Interrupt Mask Control Register)             | . 4-36 |

|     | 0x35—ENSEC (Receive Section Interrupt Mask Control Register)        | 4-37   |

|     | 0x36—ENLIN (Receive Line Interrupt Mask Control Register)           | . 4-37 |

|     | 0x37—ENPTH (Receive Path Interrupt Mask Control Register)           | 4-38   |

|     | 0x3A—ENAPS (APS Interrupt Mask Control Register) (WAN Only)         | . 4-38 |

|     | 0x38—ENCELLT (Transmit Cell Interrupt Mask Control Register)        | . 4-39 |

|     | 0x39—ENCELLR (Receive Cell Interrupt Mask Control Register)         | . 4-40 |

|     | 0x3C—SUMINT (Summary Interrupt Indication Status Register)          | . 4-41 |

|     | 0x3D—SECINT (Receive Section Interrupt Indication Status Register)  | 4-42   |

|     | 0x3E—LININT (Receive Line Interrupt Indication Status Register)     | 4-42   |

|     | 0x3F—PTHINT (Receive Path Interrupt Indication Status Register)     | . 4-43 |

|     | 0x42—APSINT (APS Interrupt Indication Status Register) (WAN Only)   | 4-43   |

|     | 0x40—TXCELLINT (Transmit Cell Interrupt Indication Status Register) | . 4-44 |

|     | 0x41—RXCELLINT (Receive Cell Interrupt Indication Status Register)  | 4-44   |

|     | 0x45—RXSEC (Receive Section Overhead Status Register)               |        |

|     | 0x46—RXLIN (Receive Line Overhead Status Register)                  | . 4-45 |

|     | 0x47—RXPTH (Receive Path Overhead Status Register)                  | . 4-46 |

|     | 0x4A—RXAPS (Receive APS Status Register) (WAN Only)                 | . 4-46 |

|     | 0x48—TXCELL (Transmit Cell Status Register)                         | . 4-47 |

|     | 0x49—RXCELL (Receive Cell Status Register)                          | . 4-47 |

| 4.8 | Counters                                                            | 4-48   |

|     | 0x4C—LOCDCNT (LOCD Event Counter)                                   | . 4-48 |

|     | 0x4D—CORRCNT (Corrected HEC Error Counter)                          | . 4-48 |

|     | 0x4E—UNCCNT (Uncorrected HEC Error Counter)                         | . 4-49 |

|     |                                                                     |        |

| 4703.4 | D1 · 1   | T . C     | D .      | 4703.4 | DIII |

|--------|----------|-----------|----------|--------|------|

| AIM    | Physical | Interface | Devices- | -AIM   | PHY  |

|      | 0x4F—OOFCNT (OOF Event Counter)                      | 4-49   |

|------|------------------------------------------------------|--------|

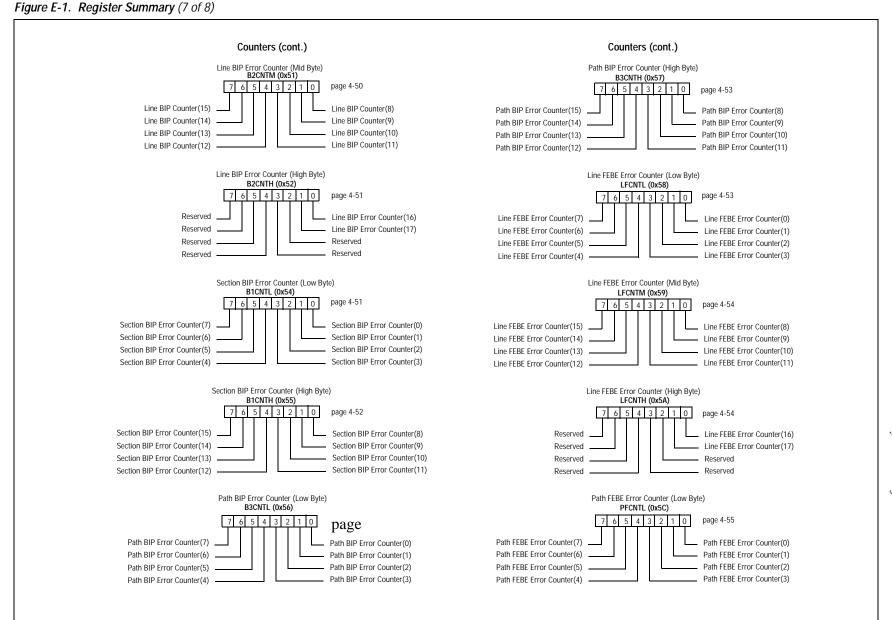

|      | 0x50—B2CNTL (Line BIP Error Counter [Low Byte])      | 4-50   |

|      | 0x51—B2CNTM (Line BIP Error Counter [Mid Byte])      | . 4-50 |

|      | 0x52—B2CNTH (Line BIP Error Counter [High Byte])     | . 4-51 |

|      | 0x54—B1CNTL (Section BIP Error Counter [Low Byte])   | 4-51   |

|      | 0x55—B1CNTH (Section BIP Error Counter [High Byte])  | 4-52   |

|      | 0x56—B3CNTL (Path BIP Error Counter [Low Byte])      | . 4-52 |

|      | 0x57—B3CNTH (Path BIP Error Counter [High Byte])     | 4-53   |

|      | 0x58—LFCNTL (Line FEBE Error Counter [Low Byte])     |        |

|      | 0x59—LFCNTM (Line FEBE Error Counter [Mid Byte])     | . 4-54 |

|      | 0x5A—LFCNTH (Line FEBE Error Counter [High Byte])    |        |

|      | 0x5C—PFCNTL (Path FEBE Error Counter [Low Byte])     |        |

|      | 0x5D—PFCNTH (Path FEBE Error Counter [High Byte])    |        |

|      | 0x5E—NONCNTL (Non-Matching Cell Counter [Low Byte])  |        |

|      | 0x5F—NONCNTH (Non-Matching Cell Counter [High Byte]) |        |

|      | 0x60—TXCNTL (Transmitted Cell Counter [Low Byte])    |        |

|      | 0x61—TXCNTM (Transmitted Cell Counter [Mid Byte])    |        |

|      | 0x62—TXCNTH (Transmitted Cell Counter [High Byte])   |        |

|      | 0x64—RXCNTL (Received Cell Counter [Low Byte])       |        |

|      | 0x65—RXCNTM (Received Cell Counter [Mid Byte])       |        |

|      | 0x66—RXCNTH (Received Cell Counter [High Byte])      | 4-59   |

| 5.0  | Electrical and Mechanical Specifications             | 5-1    |

| 5    | .1 Timing Specifications                             | . 5-1  |

|      | 5.1.1 Microprocessor Interface Timing                | 5-5    |

|      | 5.1.2 Transmit UTOPIA Interface Timing               | . 5-11 |

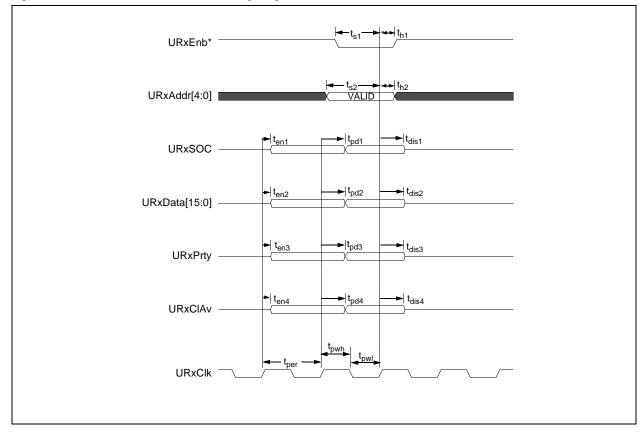

|      | 5.1.3 Receive UTOPIA Interface Timing                | . 5-13 |

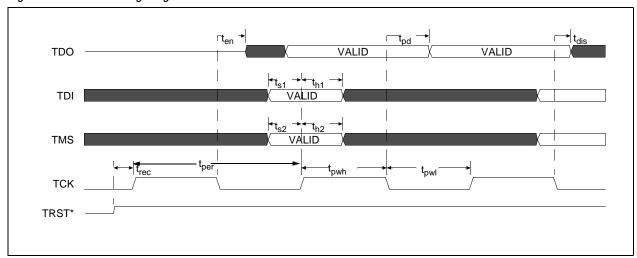

|      | 5.1.4 JTAG Interface Timing                          | 5-15   |

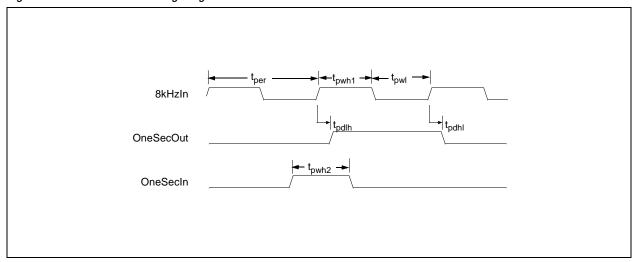

|      | 5.1.5 One-second Interface Timing                    | 5-16   |

| 5    | .2 Absolute Maximum Ratings                          | 5-17   |

| 5    | .3 DC Characteristics                                | 5-18   |

|      | 5.3.1 PECL - Input                                   | 5-19   |

|      | 5.3.2 PECL - Output                                  | . 5-19 |

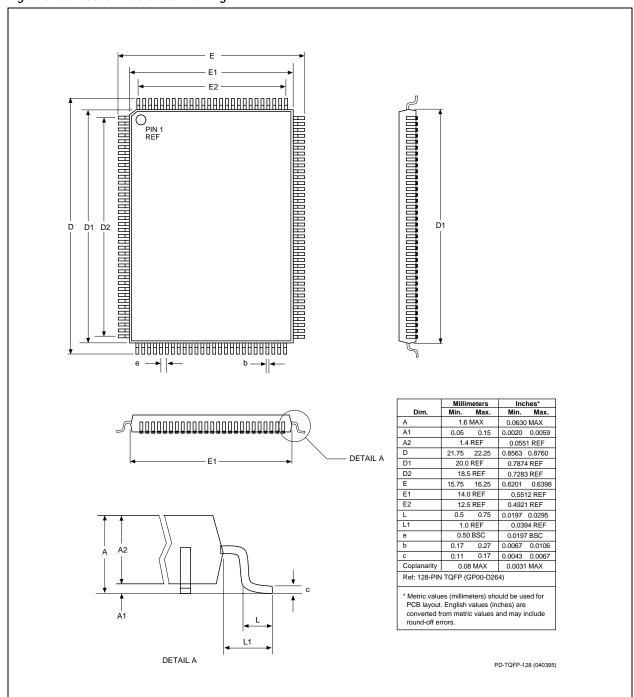

| 5    | .4 Mechanical Drawing                                | 5-20   |

| Appe | ndix A : RS8252/3 Dual PHY Device                    | . A-1  |

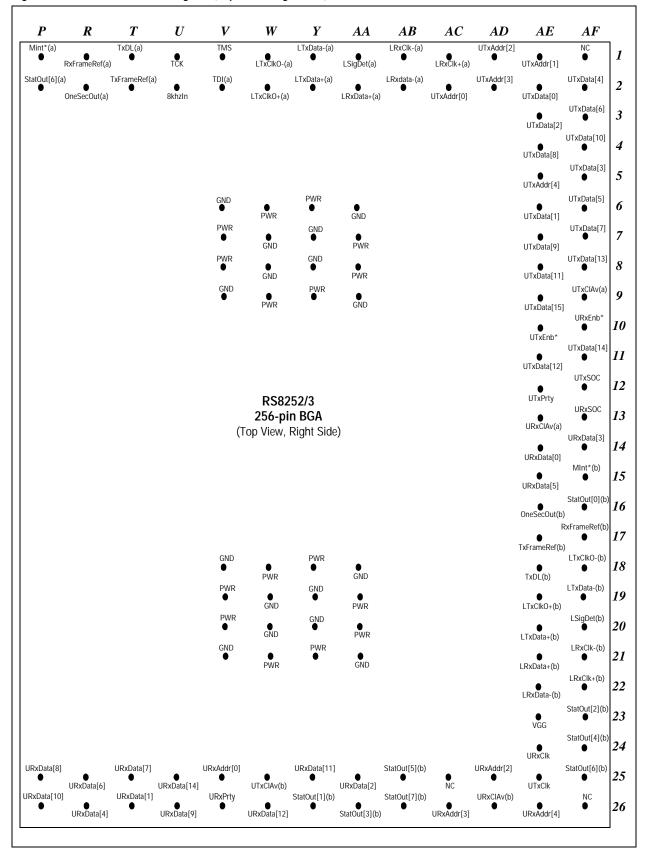

| Α    | .1 RS8252/3 Pinout and Pin Descriptions              | . A-   |

|      |                                                      |        |

|      | .2 RS8252/3 Register Map                             |        |

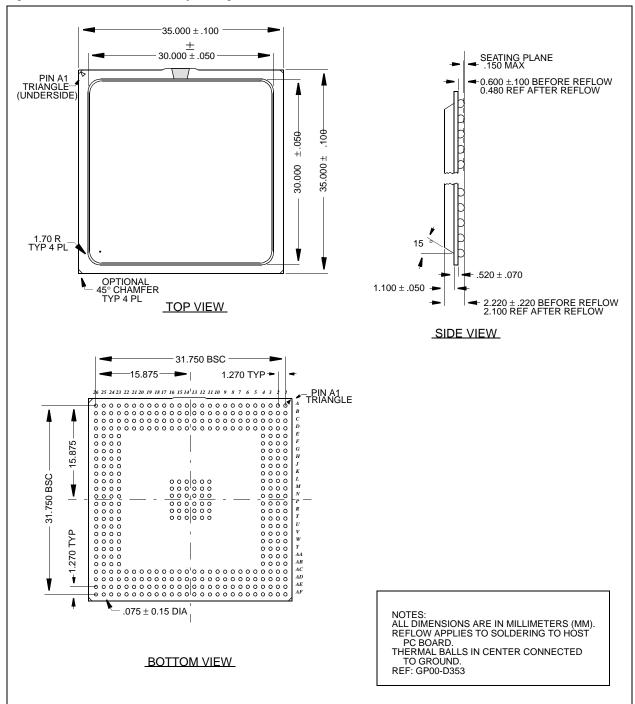

| Α    | .3 RS8252/3 Electrical and Mechanical Description    |        |

|      | A.3.1 RS8252/3 Mechanical Drawing                    | A-17   |

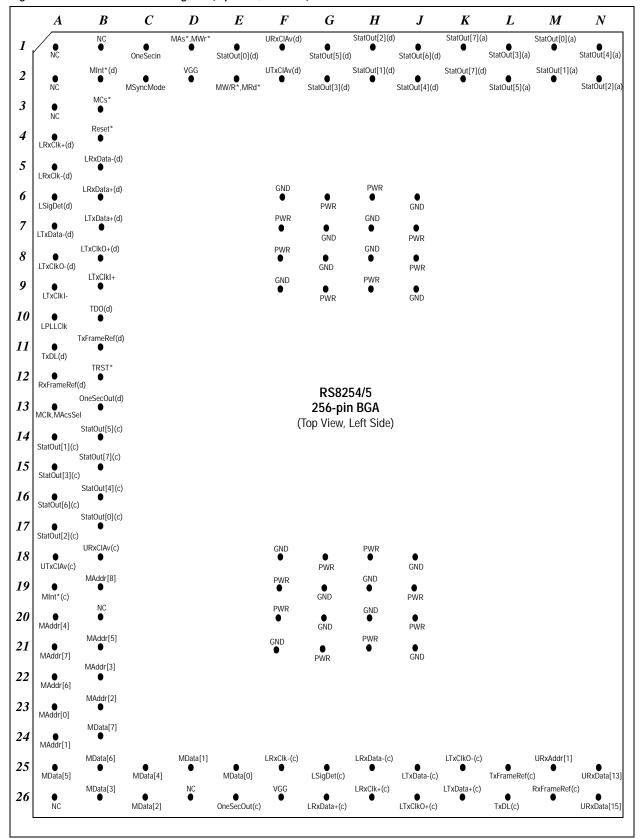

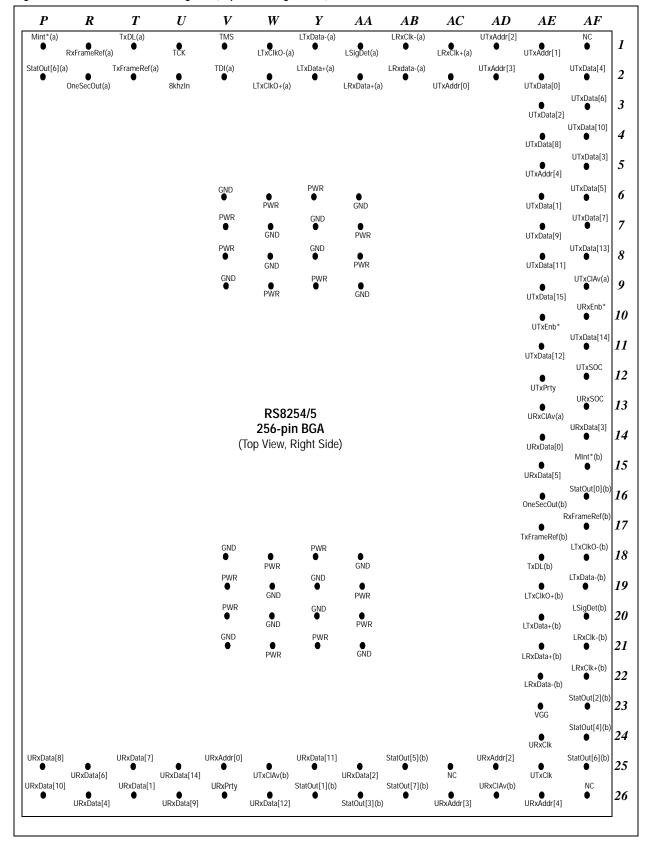

| Appe | endix B: RS8254/5 Quad PHY Device                    | . B-1  |

| В    | .1 RS8254/5 Pinout and Pin Descriptions              | . B-1  |

|      | ·                                                    |        |

| B.3 RS82   | 54/5 Electrical and Mechanical Description | B-16  |

|------------|--------------------------------------------|-------|

| B.3.1      | RS8254/5 Mechanical Drawing                | B-16  |

| Appendix C | : RS8250 PHY Device                        | C-1   |

| C.1 RS82   | 50 Pinout and Pin Descriptions             | C-1   |

| C.2 RS82   | 50 Electrical and Mechanical Description   | C-15  |

| C.2.1      | RS8250 Mechanical Drawing                  | C-16  |

| Appendix D | : Related Standards                        | D-1   |

| Appendix E | : Register Summary                         | . E-1 |

# **List of Figures**

| Figure 1-1.  | RS825x Connected to a SAR (RS8234/5)                            | 1-3  |

|--------------|-----------------------------------------------------------------|------|

| Figure 1-2.  | RS825x Logic Diagram                                            | 1-4  |

| Figure 1-3.  | RS8251 Pinout Diagram                                           | 1-5  |

| Figure 1-4.  | RS825x Detailed Block Diagram                                   | 1-15 |

| Figure 2-1.  | RS825x Transmitter Block Diagram                                | 2-1  |

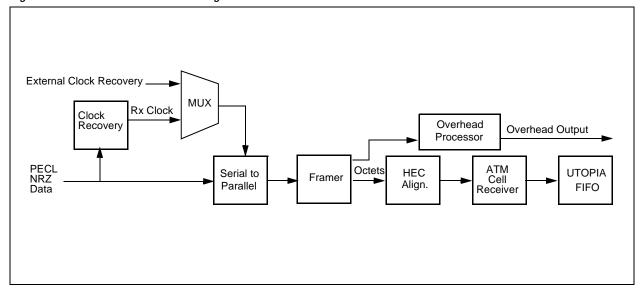

| Figure 2-2.  | RS825x Receiver Block Diagram                                   | 2-2  |

| Figure 2-3.  | Single-ended PECL Diagram                                       | 2-4  |

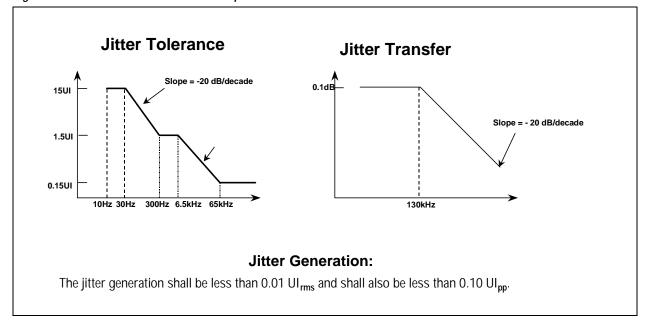

| Figure 2-4.  | Bellcore GR-253-CORE Jitter Specifications                      | 2-6  |

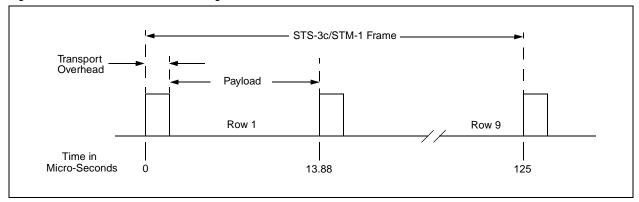

| Figure 2-5.  | STS-3c/STM-1 Basic Frame                                        | 2-8  |

| Figure 2-6.  | STS-3c/STM-1 Frame Timing                                       | 2-9  |

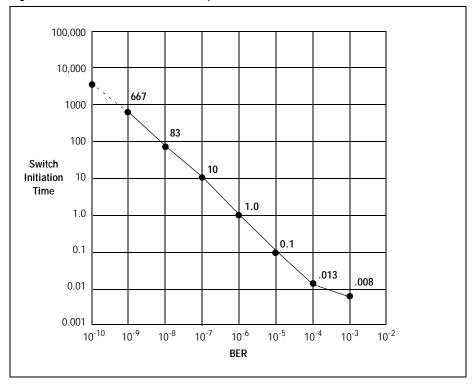

| Figure 2-7.  | Switch Initiation Time Graph                                    | 2-16 |

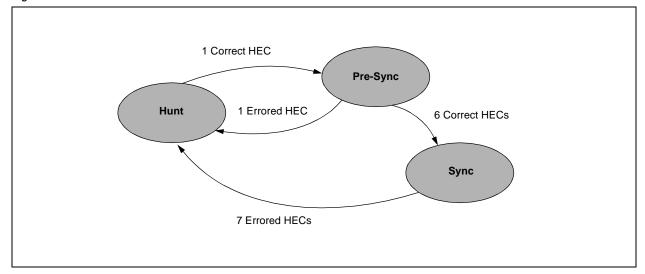

| Figure 2-8.  | Cell Delineation Process                                        | 2-23 |

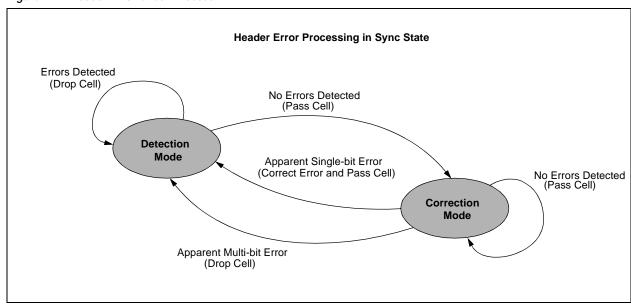

| Figure 2-9.  | Header Error Check Process                                      | 2-24 |

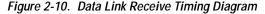

| Figure 2-10. | Data Link Receive Timing Diagram                                | 2-28 |

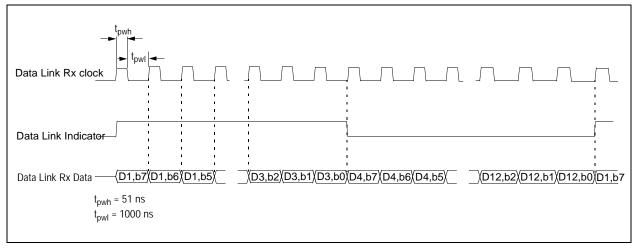

| Figure 2-11. | Interrupt Indication Flow Chart                                 | 2-36 |

| Figure 2-12. | Interrupt Indication Diagram                                    | 2-37 |

| Figure 2-13. | Near-end Line Loopback Diagram                                  | 2-39 |

| Figure 2-14. | UTOPIA Loopback Diagram                                         | 2-40 |

| Figure 2-15. | Source Loopback Diagram                                         | 2-41 |

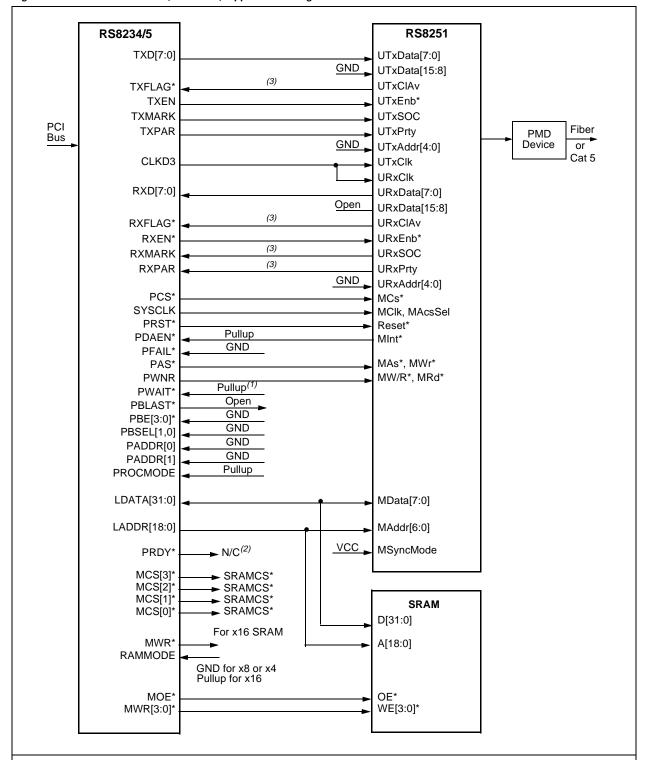

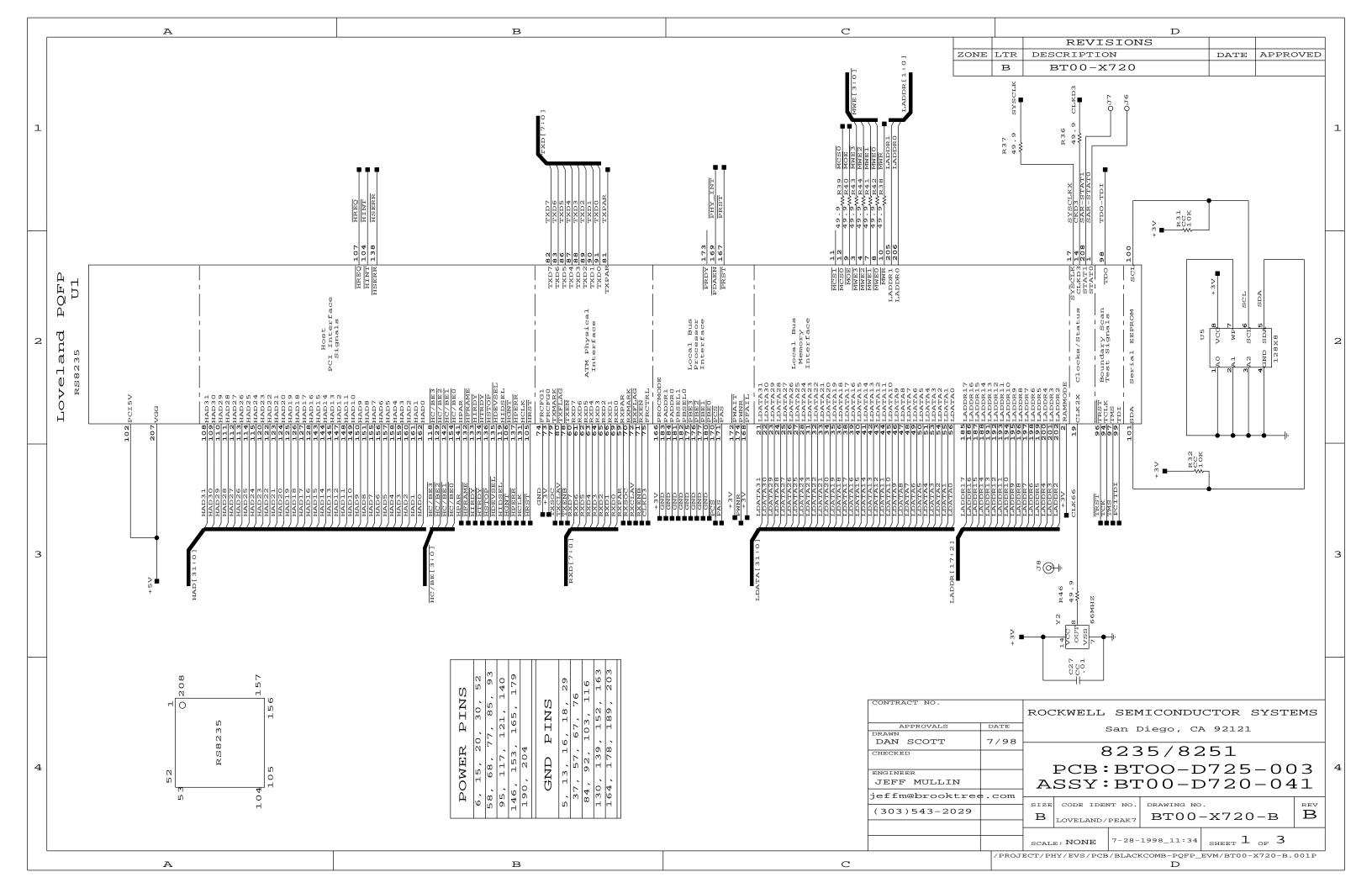

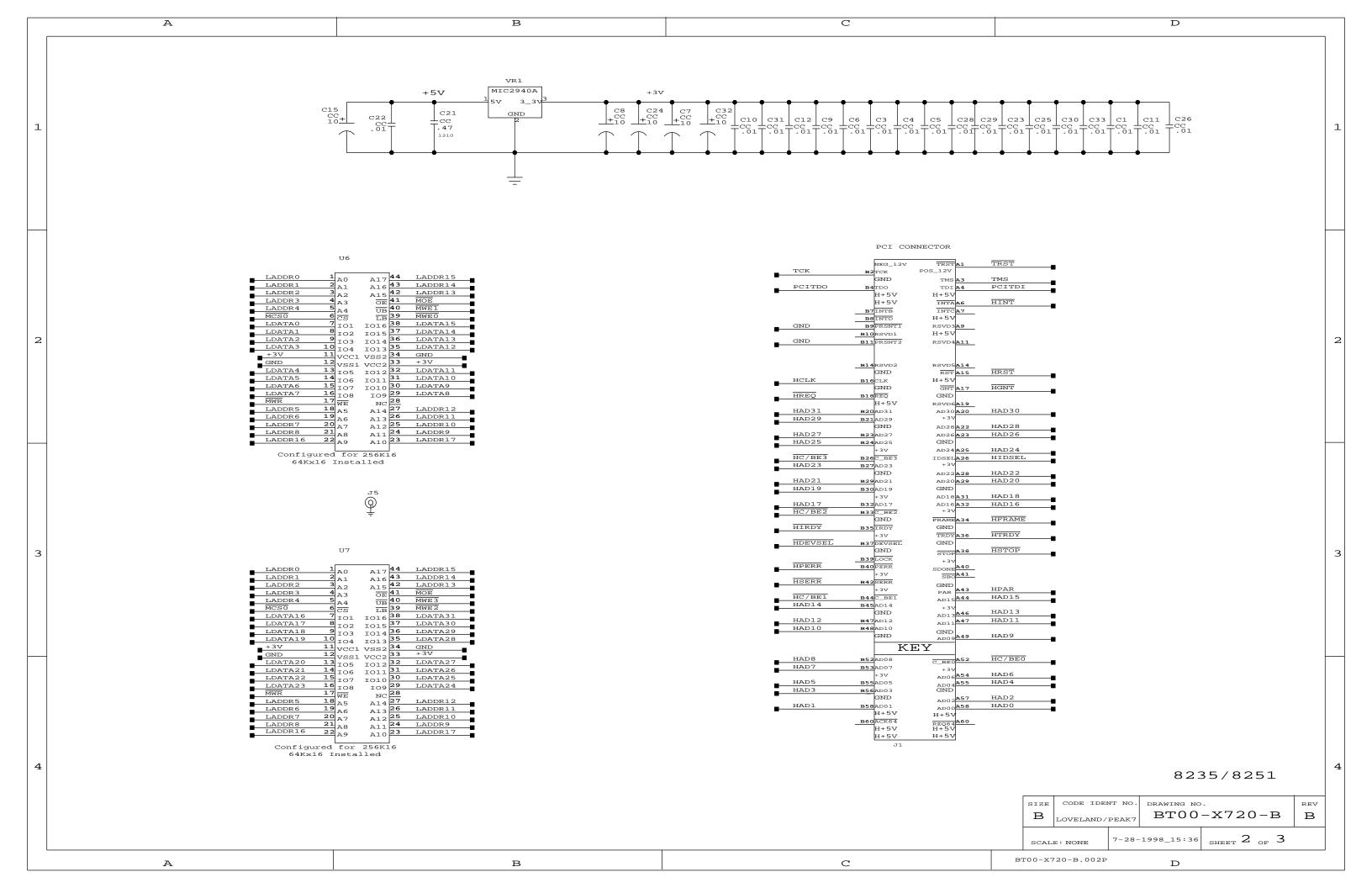

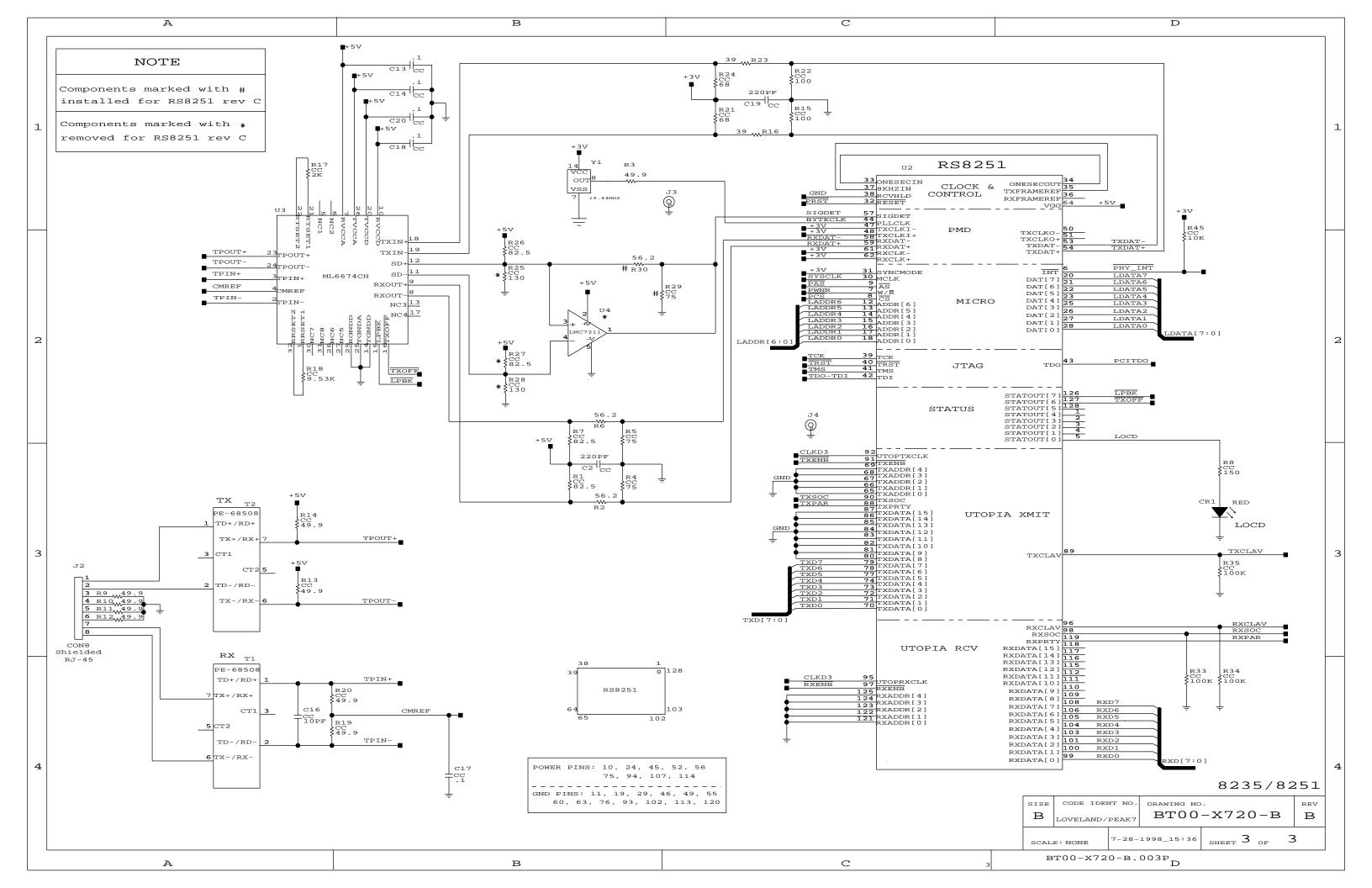

| Figure 3-1.  | RS8251 and SAR (RS8234/5) Application Diagram                   | 3-2  |

| Figure 3-2.  | RS825x to 3.3 V PMD Diagram                                     | 3-3  |

| Figure 3-3.  | RS825x to 5 V PMD Inputs Diagram                                | 3-4  |

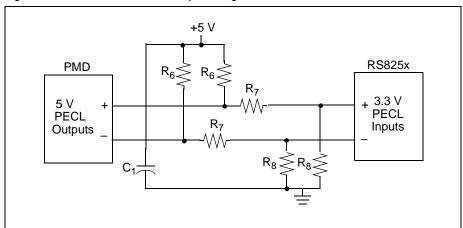

| Figure 3-4.  | RS825x to 5 V PMD Outputs Diagram                               | 3-5  |

| Figure 3-5.  | PECL Layout Diagram (3.3 V Inputs)                              | 3-6  |

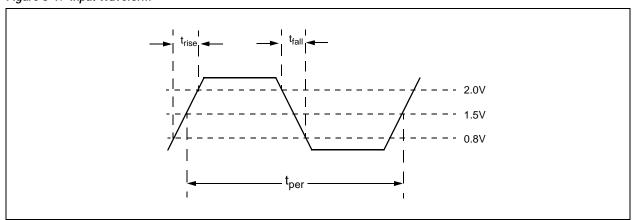

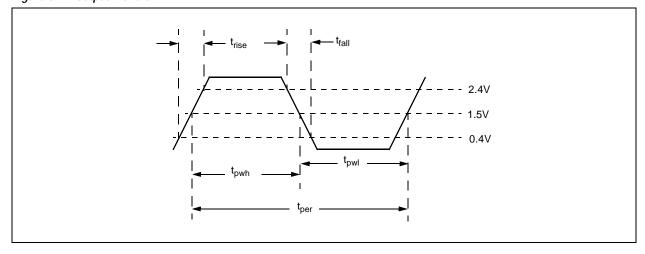

| Figure 5-1.  | Input Waveform                                                  | 5-4  |

| Figure 5-2.  | Output Waveform                                                 | 5-5  |

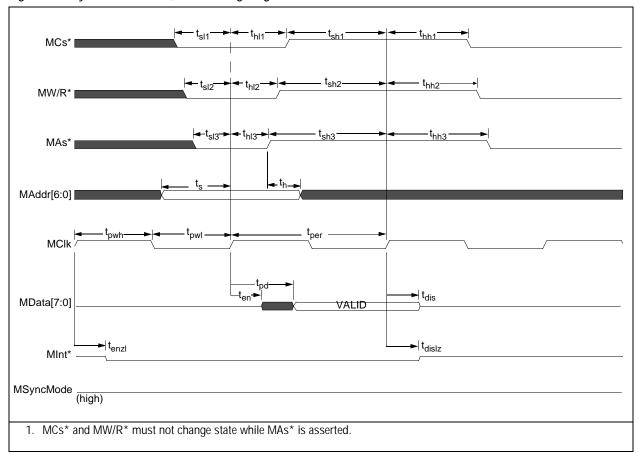

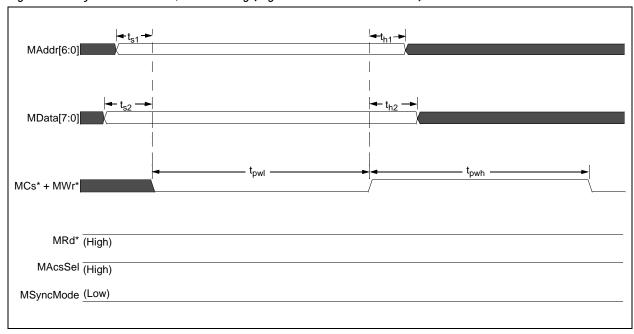

| Figure 5-3.  | Synchronous Mode, Read Timing Diagram                           | 5-5  |

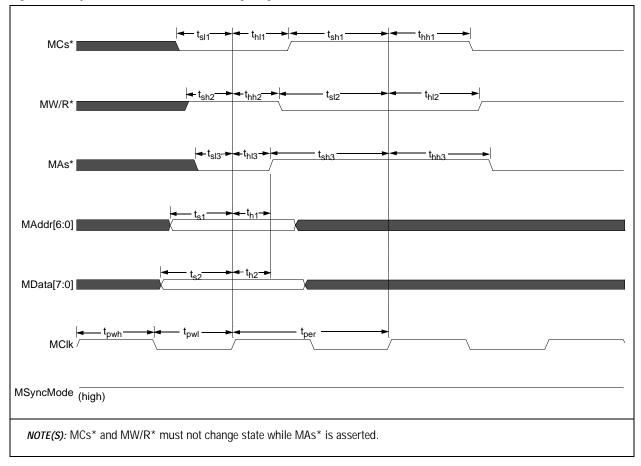

| Figure 5-4.  | Synchronous Mode, Write Timing Diagram                          | 5-7  |

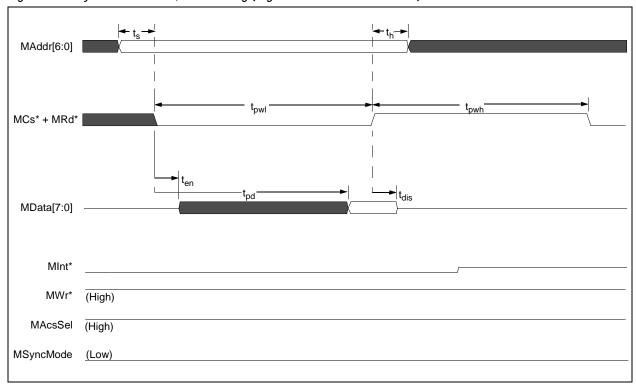

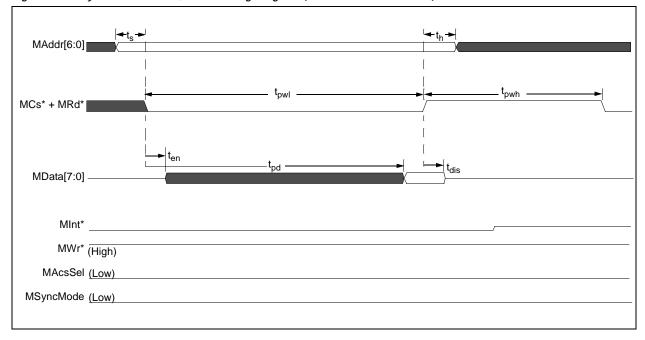

| Figure 5-5.  | Asynchronous Mode, Read Timing (High-performance Access Time)   | 5-8  |

| Figure 5-6.  | Asynchronous Mode, Write Timing (High-performance Access Time)  | 5-9  |

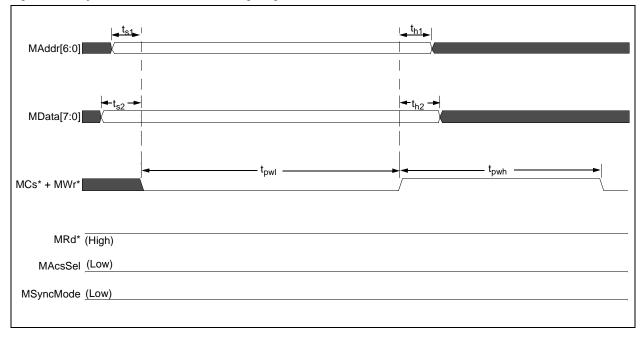

| Figure 5-7.  | Asynchronous Mode, Read Timing Diagram (Low-power Access Time)  | 5-10 |

| Figure 5-8.  | Asynchronous Mode, Write Timing Diagram (Low-power Access Time) | 5-11 |

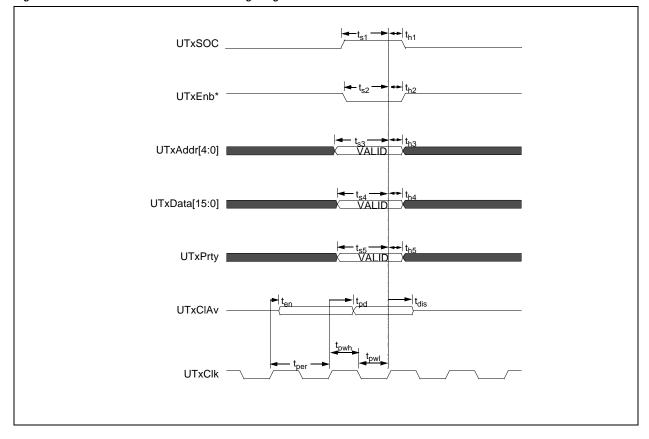

| Figure 5-9.  | Transmit UTOPIA Interface Timing Diagram                        | 5-12 |

| Figure 5-10. | Receive UTOPIA Interface Timing Diagram                    | 5-13 |

|--------------|------------------------------------------------------------|------|

| Figure 5-11. | JTAG Timing Diagram                                        | 5-15 |

| Figure 5-12. | One-second Timing Diagram                                  | 5-16 |

| Figure 5-13. | RS8251 Mechanical Drawing                                  | 5-21 |

| Figure A-1.  | RS8252/3 Pinout Diagram (top view, left side)              | A-2  |

| Figure A-3.  | 256-Pin Ball Gate Array Package (BGA), for RS8252/3        | A-17 |

| Figure B-1.  | RS8254/5 Pinout Diagram (top view, left side)              | B-2  |

| Figure B-2.  | RS8254/5 Pinout Diagram (top view, right side)             | B-3  |

| Figure B-3.  | 256-Pin Ball Gate Array Package (BGA) for the RS8254/5     | B-17 |

| Figure C-1.  | RS8250 Pinout Diagram (top view, left side)                | C-2  |

| Figure C-2.  | 156-Pin Ball Gate Array (BGA) Package – Top and Side Views | C-16 |

| Figure C-3.  | 156-Pin Ball Gate Array (BGA) Package – Bottom View        | C-17 |

| Figure E-1.  | Register Summary                                           | E-2  |

# **List of Tables**

| Table 1-1.  | RS8251 Pin Definitions                                               | 1-6  |

|-------------|----------------------------------------------------------------------|------|

| Table 2-1.  | Single-ended PECL Table                                              | 2-3  |

| Table 2-2.  | PECL Input Logic Table                                               | 2-4  |

| Table 2-3.  | PECL Output Logic Table                                              | 2-5  |

| Table 2-4.  | SONET Overhead Byte Definitions and Values                           | 2-10 |

| Table 2-5.  | Section Overhead Transmit and Receive Functions                      | 2-11 |

| Table 2-6.  | Line Overhead Transmit and Receive Functions                         | 2-13 |

| Table 2-7.  | H1, H2, and H3 Functions                                             | 2-14 |

| Table 2-8.  | SF/SD Threshold Table                                                | 2-15 |

| Table 2-9.  | S1 Byte Description                                                  | 2-18 |

| Table 2-10. | Path Overhead Transmit and Receive Functions                         | 2-18 |

| Table 2-11. | Transmitted RDI-P Values                                             | 2-20 |

| Table 2-12. | Receiver RDI-P Interpretation                                        | 2-20 |

| Table 2-13. | Cell Screening—Matching                                              | 2-25 |

| Table 2-14. | Cell Screening—Accept/Reject Cell                                    | 2-25 |

| Table 2-15. | LStatOut Configuration                                               | 2-26 |

| Table 2-16. | Cell Format for 8-bit Mode                                           | 2-30 |

| Table 2-17. | Cell Format for 16-bit Mode                                          | 2-30 |

| Table 4-1.  | Control and Status Registers                                         | 4-1  |

| Table 5-1.  | Timing Diagram Nomenclature                                          | 5-2  |

| Table 5-2.  | Synchronous Mode, Read Timing Table                                  | 5-6  |

| Table 5-3.  | Synchronous Mode, Write Timing Table                                 | 5-7  |

| Table 5-4.  | Asynchronous Mode, Read Timing Table (High-performance Access Time)  | 5-9  |

| Table 5-5.  | Asynchronous Mode, Write Timing Table (High-performance Access Time) | 5-9  |

| Table 5-6.  | Asynchronous Mode, Read Timing Table (Low-power Access Time)         | 5-10 |

| Table 5-7.  | Asynchronous Mode, Write Timing Table (Low-power Access Time)        | 5-11 |

| Table 5-8.  | Transmit UTOPIA Interface Timing Table                               | 5-12 |

| Table 5-9.  | Receive UTOPIA Interface Timing Table                                | 5-14 |

| Table 5-10. | JTAG Timing Table                                                    | 5-15 |

| Table 5-11. | One-second Timing Table                                              | 5-16 |

| Table 5-12. | Absolute Maximum Ratings                                             | 5-17 |

| Table 5-13. | DC Characteristics                                                   | 5-18 |

| Table 5-14. | PECL-Input DC Characteristics                                        | 5-19 |

xiv

| ATM  | Dhysical | Interface | Davisas  | ATMDHV         |

|------|----------|-----------|----------|----------------|

| AI W | rnysicai | merjace   | Devices- | <i>–ATMPHY</i> |

| Table 5-15. | PECL-Output DC Characteristics | . 5-19 |

|-------------|--------------------------------|--------|

| Table A-2.  | Multi-PHY Addressing           | . A-15 |

| Table B-1.  | RS8254/5 Pin Definitions       | B-4    |

| Table B-2.  | Multi-PHY Addressing           | . B-15 |

| Table C-1.  | RS8250 Pin Definitions         | C-3    |

## 1.0 Product Description

The RS825x ATM Physical Layer Interface (PHY) device is a transmitter/receiver, which performs the Transmission Convergence (TC) sublayer function of converting SONET/SDH frames to ATM cells and vice versa. The RS825x family consists of 6 devices in two categories, WAN and LAN, as

Table 1-1. The RS825x Family

displayed in Table 1-1.

| Number of Ports | WAN Device No. | LAN Device No. |

|-----------------|----------------|----------------|

| One Port        | RS8250         | RS8251         |

| Two Ports       | RS8252         | RS8253         |

| Four Ports      | RS8254         | RS8255         |

The difference between the WAN and LAN versions of the RS825x is that the RS8250/2/4 WAN version includes an enhanced performance feature set as follows:

- The integral PLL/clock and data recovery circuit meets the jitter tolerance, jitter transfer, and jitter generation specification of Bellcore GR.253-CORE

- 2. Automatic Protection Switching (APS) is supported through access of the K1 and K2 overhead octets

- 3. Programmable signal degrade/signal fail BER threshold monitoring with automatic detection and clearing

- 4. Extended SONET overhead processing with access to data link D1-D3 and D4-D12 octets for messaging to an optional serial communication controller

- 5. Access to the S1 overhead status byte for transporting synchronization status messages

The name RS825x in this document refers to the entire family of RS825x devices. Specific device numbers are used when features do not apply to all of the devices in the family. Information concerning the RS8252/3 dual devices can be found in Appendix A, the RS8254/5 quad devices in Appendix B, and the RS8250 single WAN device in Appendix C.

This chapter provides an overview of the RS825x, including its primary features and applications. A logic diagram, package pinouts, and pin descriptions are also presented. A block diagram is included to show the data flow in the device.

### 1.1 RS825x Features

The RS825x, operating at up to 155 Mbps (duplex), provides a single-access ATM service termination for User-to-Network Interfacing (UNI) and Network-to-Network Interfacing (NNI) in conformance with the ATM Forum UNI Specification 94/0317, ITU Recommendation I.432, and other industry standards (see Appendix A for a list). This PHY device consists of several functional blocks: the SONET Framer, the ATM Cell Formatter, the UTOPIA Level 2 interface, and the microprocessor interface. Together these blocks and the clock recovery block provide efficient conversion of SONET frames to ATM cells and vice versa.

The RS825x is implemented in 0.35 micron CMOS technology, which runs on 3.3 Volts. The RS8250 is packaged in a 156-pin Ball Grid Array (BGA); the RS8251, in a 128-pin Thin Quad Flat Pack (TQFP); and the RS8252-5, in a 256-pin BGA. This low-power device processes STS-3c/STM-1 data streams at 155 Mbps (duplex). The device also provides a Pseudo-Emitter Coupled Logic (PECL) interface for serial connection to a Physical Media Dependent (PMD) device. It has a synchronous 16-bit wide, four-cell deep FIFO buffer. An 8-bit microprocessor bus interface is used for configuration, status, and control of the device. Furthermore, the RS825x's output control signals can be set up to drive Light Emitting Diodes (LEDs) for monitoring of data and alarm activity.

The RS825x descrambles received data, then uses the payload pointer (H1, H2) to locate and retrieve the SONET payload envelope. It also processes section, line, and path overhead. ATM cells are extracted from the payload envelope according to the ATM cell delineation standards. The RS825x optionally performs payload descrambling, Header Error Checking (HEC) error detection and correction, and idle cell filtering. Error counts are kept at all levels for performance monitoring.

The RS825x generates a transmit payload pointer (H1, H2) and framing bytes (A1, A2). The device also performs HEC generation and idle cell insertion, as well as ATM cell payload scrambling. The RS825x synthesizes the 155.52 MHz transmit clock from a 19.44 MHz, 8 kHz frequency reference, or can use the clock from the internal clock recovery circuit.

When necessary, the RS825x inserts line and path alarm signals and Remote Defect Indications (RDIs). It also inserts path and line BIP-8 codes and Far End Block Error (FEBE) indications to allow performance monitoring at the far end. Additionally, all-zeros data can be inserted for diagnostic purposes.

### 1.2 Applications Overview

The RS825x can be used in a number of applications including:

- ATM LANs over optical fibers

- Workstations and PC Network Interface Cards (NICs)

- LAN switches and hubs

- SONET or SDH compliant ATM UNIs

The device is typically used in combination with a Segmentation and Reassembly (SAR) device, such as the RS8234 or RS8235 SAR, to provide framing along with segmentation and reassembly of ATM traffic. The device can be used in switch-to-switch links, as well as switch-to-terminal links. The RS825x connects to the SAR via the UTOPIA and microprocessor interfaces (see Figure 1-1). It can be either loop-timed or source-timed. The device can be configured and controlled through a generic microprocessor interface. For more information on applications for the RS825x, see Chapter 3.0.

Figure 1-1. RS825x Connected to a SAR (RS8234/5)

### 1.3 Logic Diagram

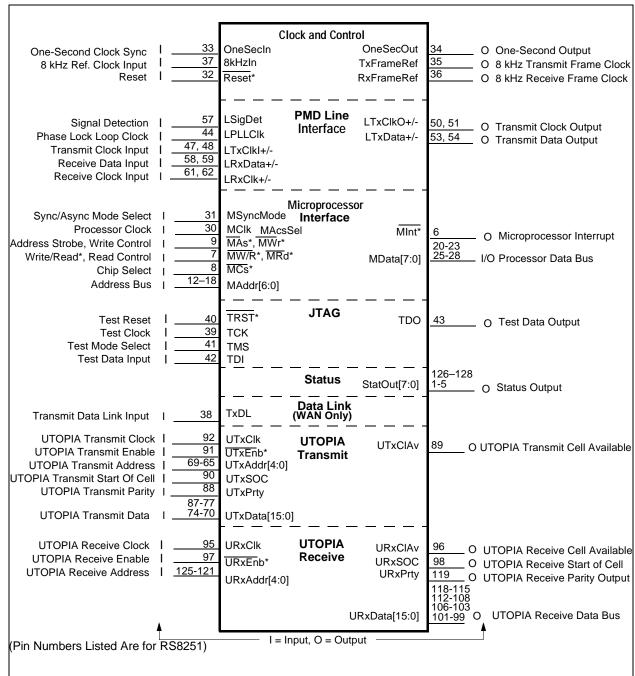

Figure 1-2 is a logic diagram of the RS825x's functional blocks. There are seven general purpose Clock and Control pins. The PMD interface consists of 12 pins. The Microprocessor interface consists of six clock and control inputs, an 8-bit data bus, and a 7-bit address bus. There are five JTAG pins and eight status pins. The UTOPIA interface consists of 26 transmit pins and 26 receive pins. There are 10 power and 13 ground pins. Pin descriptions are given in Table 1-2.

Figure 1-2. RS825x Logic Diagram

1.4 Pin Diagram and Definitions

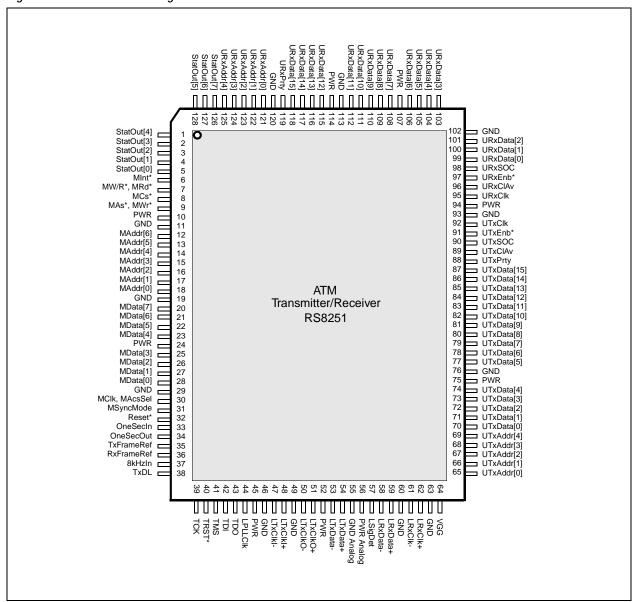

### 1.4 Pin Diagram and Definitions

Figure 1-3 is a pinout diagram for the RS8251 ATM Transmitter/Receiver. It is a single CMOS integrated circuit packaged in a 128-pin TQFP. All unused input pins should be connected to ground. Unused outputs should be left unconnected.

Figure 1-3. RS8251 Pinout Diagram

Pin names and numbers are listed in Table 1-2. An asterisk (\*) following a pin label indicates that the pin logic level is active low.

**Table 1-2. RS8251 Pin Definitions** (1 of 10)

|                    | Pin Label  | Signal Name                                        | No. | Туре                 | I/O | Description                                                                                                                                                                                                                                 |

|--------------------|------------|----------------------------------------------------|-----|----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Reset*     | Device Reset                                       | 32  | TTL-H <sup>(1)</sup> | I   | This pin is used to reset the device when asserted low.                                                                                                                                                                                     |

|                    | OneSecIn   | One-Second<br>Strobe                               | 33  | TTL                  | I   | This input is used to latch device status, typically at 1-second intervals.                                                                                                                                                                 |

| _                  | OneSecOut  | One-Second<br>Output                               | 34  | TTL                  | 0   | This pin is a 1-second count derived from the 8khzln input (pin 37).                                                                                                                                                                        |

| Clock and Control  | TxFrameRef | Transmit Frame<br>Clock                            | 35  | TTL                  | 0   | This pin can be either an 8 kHz output derived from the Transmit SDH frame or a 19.44 MHz output derived from the transmit clock, as selected by bit 1 of the TXSEC (0xOC) register.                                                        |

| Ö                  | RxFrameRef | Receive Frame<br>Clock                             | 36  | TTL                  | 0   | This pin can be either an 8 kHz output derived from the Receive SDH frame or a 19.44 MHz output derived from the recovered (receive) clock as selected by bit 1 of the RXSEC (0x45) register.                                               |

|                    | 8kHzIn     | 8 kHz Reference<br>Clock Input                     | 37  | TTL-H                | I   | This pin is an 8 kHz clock input used to derive OneSecOut (pin 34). The 155.52 MHz transmit clock can be synthesized from this clock.                                                                                                       |

|                    | LTxClkI-   | Line Transmit<br>Clock Input<br>Negative Polarity  | 47  | PECL                 | I   | This pin allows use of an externally generated 155.52 MHz clock as selected by bits 3 and 4 in the CLKREC register (0x01). The external source must be accurate to 20 PPM.                                                                  |

| ace                | LTxClkI+   | Line Transmit<br>Clock Input<br>Positive Polarity  | 48  | PECL                 | I   | This pin allows use of an externally generated 155.52 MHz clock as selected by bits 3 and 4 in the CLKREC register (0x01). The external source must be accurate to 20 PPM.                                                                  |

| PMD Line Interface | LTxClkO-   | Line Transmit<br>Clock Output<br>Negative Polarity | 50  | PECL                 | 0   | This pin is a 155.52 MHz output derived from one of four clock sources: LPLLClk, 8kHzIn, Loop-timed, or LTxClkI+/ The clock source is selected in bits 3 and 4 of the CLKREC register (0x01). It is generally used for diagnostic purposes. |

|                    | LTxClkO+   | Line Transmit<br>Clock Output<br>Positive Polarity | 51  | PECL                 | 0   | This pin is a 155.52 MHz output derived from one of four clock sources: LPLLClk, 8kHzIn, Loop-timed, or LTxClkI+/ The clock source is selected in bits 3 and 4 of the CLKREC register (0x01). It is generally used for diagnostic purposes. |

**Table 1-2. RS8251 Pin Definitions** (2 of 10)

|                            | Pin Label | Signal Name                                  | No. | Туре           | I/O | Description                                                                                                                                                                                                                                                                                                                         |

|----------------------------|-----------|----------------------------------------------|-----|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | LTxData-  | Line Transmit<br>Output Negative<br>Polarity | 53  | PECL           | 0   | This pin transfers SDH-framed data from the RS825x to the PMD in differential serial NRZ format.                                                                                                                                                                                                                                    |

|                            | LTxData+  | Line Transmit<br>Output Positive<br>Polarity | 54  | PECL           | 0   | This pin transfers SDH-framed data from the RS825x to the PMD in differential serial NRZ format.                                                                                                                                                                                                                                    |

|                            | LRxClk-   | Line Receive<br>Clock Negative               | 61  | PECL           | I   | This pin is the receive clock input used if internal clock recovery is bypassed.                                                                                                                                                                                                                                                    |

| ont.)                      | LRxClk+   | Line Receive<br>Clock Positive               | 62  | PECL           | I   | This pin is the receive clock input used if internal clock recovery is bypassed.                                                                                                                                                                                                                                                    |

| PMD Line Interface (cont.) | LRxData-  | Line Receive Input<br>Negative               | 58  | PECL           | I   | This pin receives differential serial NRZ data from the PMD.                                                                                                                                                                                                                                                                        |

| ine Intel                  | LRxData+  | Line Receive Input<br>Positive               | 59  | PECL           | I   | This pin receives differential serial NRZ data from the PMD.                                                                                                                                                                                                                                                                        |

| PMD L                      | LSigDet   | Line Signal<br>Detection                     | 57  | TTL or<br>PECL | I   | This pin is high when the PMD is receiving a valid signal. Rockwell recommends that a comparator be used when interfacing to PMDs with PECL outputs in Rev. 13 or older devices.                                                                                                                                                    |

|                            | LPLLCIk   | Line Phase<br>Locked Loop<br>Clock           | 44  | TTL-H          | I   | This pin is a 19.44 MHz clock input. The transmit synthesizer (PLL) uses this clock to generate 155.52 MHz LTxClkO output when bits 3 and 4 of the CLKREC register (0x01) are set to "0."  Note: The transmit synthesizer PLL and clock recovery PLL use this input as a reference clock regardless of the timing source selection. |

**Table 1-2. RS8251 Pin Definitions** (3 of 10)

|                          | Pin Label        | Signal Name                                                       | No. | Туре  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|------------------|-------------------------------------------------------------------|-----|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | MSyncMode        | Microprocessor<br>Synchronous/Asy<br>nchronous Bus<br>Mode Select | 31  | TTL   | I   | A logic "1" selects the synchronous bus mode compatible with Bt8230 and Bt8233. In this mode, the microprocessor pins are defined as follows: MClk (pin 30), MW/R* (pin 7), MAs* (pin 9), MCs* (pin 8), MInt* (pin 6), MAddr (pins 12-18), and MData (pins 20-28). A logic "0" selects the asynchronous SRAM-type bus mode. In this mode, the pins are defined as follows: MAcsSel (pin 30), MRd* (pin 7), MWr* (pin 9), MCs* (pin 8), MInt* (pin 6), MAddr (pins 12-18), and MData (pins 20-28).                                                                                                                                                                                                                                                                                                                                                                            |

|                          | MCIk,<br>MAcsSel | Microprocessor<br>Clock, Access<br>Time Select                    | 30  | TTL-H |     | When MSyncMode is set to a logic "1," the MClk pin is a clock signal that samples the microprocessor interface pins (MCs*, MW/R*, MAs*, MAddr[6:0], MData[7:0]) on its rising edge. Additionally, the rising edge of MClk may cause the microprocessor interface output pins (MData[7:0], MInt*) to change states.  When MSyncMode is set to a logic "0," the MAcsSel pin selects the asynchronous interface access time. A logic "0" selects a power-saving access mode (130 ns) while a logic "1" selects the high-performance access mode (80 ns).                                                                                                                                                                                                                                                                                                                        |

| Microprocessor Interface | MCs*             | Microprocessor<br>Chip Select                                     | 8   | TTL-H | I   | When MCs* is set to a logic "0," the device is enabled for read and write accesses. When MCs* is set to a logic "1," the device will not respond to input signal transitions on MClk, MAcsSel; MW/R*,MRd*; or MAs*, MWr*. Additionally, when MCs* is set to a logic "1," the MData[7:0] pins are in a high-impedance state but the MInt* pin remains operational.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                          | MW/R*,<br>MRd*   | Microprocessor<br>Write/Read, Read<br>Control                     | 7   | TTL-H |     | When MSyncMode is set to a logic "1," this pin is a read/write control pin. In this mode, when MW/R* is set to a logic "1," a write access is enabled and the MData[7:0] pin values will be written to the memory location indicated by the MAddr[6:0] pins. Also in this mode, when MW/R* is set to a logic "0," a read access is enabled and the memory location indicated by the MAddr[6:0] pins is read and its value placed on the MData[7:0] pins. Both read and write accesses assume the device is chip selected (MCs* = 0), the address is valid (MAs* = 0), and the device is not being reset (Reset* = 1).  When MSyncMode is set to a logic "0," this pin is a read control pin. In this mode, when MRd* is set to a logic "0," a read access is enabled and the memory location indicated by the MAddr[6:0] pins is read and its value placed on the MData[7:0] |

|                          |                  |                                                                   |     |       |     | pins. The read access assumes the device is chip selected (MCs* = 0), a write access is not being requested (MWr* = 1), and the device is not being reset (Reset* = 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**Table 1-2. RS8251 Pin Definitions** (4 of 10)

|                                  | Pin Label  | Signal Name                                        | No. | Туре  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------------------------------|------------|----------------------------------------------------|-----|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                  | MAs*, MWr* | Microprocessor<br>Address Strobe,<br>Write Control | 9   | TTL-H | I   | When MSyncMode is set to a logic "1," this pin is an address strobe pin. When the MAs* pin is set to a logic "0," it indicates a valid address, MAddr[6:0]. This signal is used to qualify read and write accesses.  When MSyncMode is set to a logic "0," this pin is a write control pin. When MWr* is set to a logic "0," a write access is enabled and the MData[7:0] pin values will be written to the memory location indicated by the MAddr[6:0] pins. The write access assumes the device is chip selected (MCs* = 0), a read access is not being requested (MRd* = 1), and the device is not being reset (Reset* = 1). |  |

|                                  | MAddr[6]   | Microprocessor                                     | 12  | TTL   | I   | These seven bits are an address input for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| t.)                              | MAddr[5]   | Address Bus                                        | 13  | TTL   | I   | identifying the register that will be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Microprocessor Interface (cont.) | MAddr[4]   |                                                    | 14  | TTL   | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| erface                           | MAddr[3]   |                                                    |     | 15    | TTL | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| r Inte                           | MAddr[2]   |                                                    |     | 16    | TTL | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| esso                             | MAddr[1]   |                                                    | 17  | TTL   | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| obroc                            | MAddr[0]   |                                                    | 18  | TTL   | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Micr                             | MData[7]   | Microprocessor                                     | 20  | TTL   | I/O | These eight bits are a bidirectional data bus for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                  | MData[6]   | Data Bus                                           | 21  | TTL   | I/O | transferring the read and write data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                  | MData[5]   |                                                    | 22  | TTL   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                  | MData[4]   |                                                    | 23  | TTL   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                  | MData[3]   |                                                    | 25  | TTL   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                  | MData[2]   |                                                    | 26  | TTL   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                  | MData[1]   |                                                    | 27  | TTL   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                  | MData[0]   |                                                    | 28  | TTL   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                  | MInt*      | Microprocessor<br>Interrupt                        | 6   | TTL   | 0   | When a logic "0" is read on this pin, the device<br>needs servicing. It remains asserted until the<br>pending interrupt is acknowledged. This pin is an<br>open drain output for an external wired "OR" logic<br>implementation.                                                                                                                                                                                                                                                                                                                                                                                                |  |

**Table 1-2. RS8251 Pin Definitions** (5 of 10)

|            | Pin Label | Signal Name      | No. | Туре | I/O | Description                                                                                                    |

|------------|-----------|------------------|-----|------|-----|----------------------------------------------------------------------------------------------------------------|

| -1993)     | TRST*     | Test Reset       | 40  | TTL  | I   | When this pin is asserted, the internal boundary-scan logic is reset. This pin has a pull-up resistor.         |

| E 1149.1a- | TCK       | Test Clock       | 39  | TTL  | I   | This pin samples the value of TMS and TDI on its rising edge in order to control the boundary scan operations. |

| (see IEEE  | TMS       | Test Mode Select | 41  | TTL  | I   | This pin controls the boundary-scan Test Access Port (TAP) controller operation.                               |

| JTAG       | TDI       | Test Data Input  | 42  | TTL  | ı   | This pin is the serial test data input.                                                                        |

| '          | TDO       | Test Data Output | 43  | TTL  | 0   | This pin is the serial test data output.                                                                       |

**Table 1-2. RS8251 Pin Definitions** (6 of 10)