# eXtended FAXENGINE™ Device Set

# Introduction

The Rockwell eXtended FAXENGINE<sup>™</sup> Device Set consists of a Rockwell eXtended Facsimile Controller (XFC) device and a Rockwell MONOFAX® Modem device. This family of eXtended FAXENGINE (XFE) devices provides upgradability via its hardware and software compatible controllers.

Starting with the basic eXtended Facsimile Controller (XFC-B), combinations of voice (-V), page memory (-M), plain paper support (-P), and full-duplex speakerphone (-S) support can be added. Voice operation provides 12 minutes (-V12) or 24 minutes (-V24) of digital telephone answering machine (DTAM) recording. Telephone line rates up to 9600 bps (R96) or 14400 bps (R144) are supported. The XFE Device Set models and the supported major functions are listed in Table 1.

Each eXtended FAXENGINE Device Set, including supplied firmware, comprises a complete facsimile machine controller–needing only a power supply, scanner, printer and paper path components to complete the machine.

The FAXENGINE Development System including the FAXENGINE Evaluation System (FEES-X) and the MC24 ROM Emulator (McFERE) provides an effective development environment.

# Features

- Microprocessor and Bus Interface

- Enhanced MC24 central processing unit (CPU)

- 10 MHz CPU clock speed

- Memory efficient input/output bit manipulation

- 24-bit internal address bus

- 8-bit data bus

- External Bus

- Address, data, control, status, interrupt, and decoded chip select signals support connection to external ROM, external RAM, and optional peripheral devices

- 24-bit external address bus (XFE-B: 20-bit)

- Chip selects

- ROMCSn for ROM support

- CS0n for SRAM

- CS1n for external peripherals

- MCSn for modem

- Optional general purpose: CS2n, CS3n, CS4n and CS5n (CS5n is unavailable on the XFC-B)

- DRAM Controller (except XFC-B, XFC-P)

- Supports external page memory

- Battery backed-up refresh with separate battery power

- DMA Controller

- Three to six dedicated internal channels for scanner, printer, and T.4/T.6 access of internal and/or external memory

- External DMA channel (XFC-P, XFC-VP and XFC-MVP only)

- Internal RAM (1K X 8) for shading correction, line buffers and CPU (XFC-MV, XFC-MVP only)

- External RAM up to 1 (XFE-B) or 14 (other) Mbytes

- External ROM up to 1 (XFE-B) or 3 (other) Mbytes

- Interrupt controller

- T.4/T.6 Compression and Decompression in Hardware

- MH/MR (except XFC-B)

- MH/MR/MMR (XFC-MV, XFC-MVP only)

- Alternating compression/decompression (XFC-MV, XFC-MVP)

- Motor Control for Scanner, and Printer

- Four outputs to external current drivers for the scanner motor and four for the printer motor

- Motor outputs can be programmed as general purpose outputs (GPO) for application with a single motor or plain paper machines

- Scanner and Video Control

- CCD and CIS scanners supported

- Six programmable control signals:

- Four programmable scanner control signals

- Two video output control signals support external signal pre-processing

- B4/A4 scanner support

- 5 ms minimum line time

- Line lengths to 4096 pixels

- Scanner flash A/D Interface

- Internal 6-bit flash A/D converter

- A/D reference inputs available for control by external circuits

- Video Processing

- Per single pixel and per eight pixel shading correction

- Edge enhancement and dynamic background and contrast control

- Up to 8x8 programmable dither table

- Image data processing port allows access to scan data prior to video processing

- Multi-level B4 to A4 size reduction (except XFC-B)

- Programmable Resolution Conversion (see Table 1)

- Two-dimensional bi-level resolution conversion provides expansion up to 200% and reduction down to 33%

- Vertical line "OR"ing

- Scanner output bit order reversal

| FAXENGINE<br>Device Set                           | XFC Fax<br>Controller                  | MONOFAX<br>Fax Modem                    | Page<br>Memory | MH/MR/<br>MMR | DRAM<br>Control | External DMA<br>and Resolution<br>Conversion | DTAM<br>Recording Time<br>(Minutes) <sup>4</sup> | Speakerphone |

|---------------------------------------------------|----------------------------------------|-----------------------------------------|----------------|---------------|-----------------|----------------------------------------------|--------------------------------------------------|--------------|

| R96XFE-B                                          | XFC-B                                  | R96DFXL                                 |                | 1             |                 |                                              |                                                  |              |

| R96XFE-M                                          | XFC-MV                                 | R96DFXL                                 | •              | 3             | •               |                                              |                                                  |              |

| R96XFE-P                                          | XFC-P                                  | R96DFXL                                 |                | 2             |                 | •                                            |                                                  |              |

| R96XFE-MP                                         | XFC-MVP                                | R96DFXL                                 | •              | 3             | •               | •                                            |                                                  |              |

| R144XFE-B                                         | XFC-B                                  | R144EFXL                                |                | 1             |                 |                                              |                                                  |              |

| R144XFE-M                                         | XFC-MV                                 | R144EFXL                                | •              | 3             | •               |                                              |                                                  |              |

| R144XFE-P                                         | XFC-P                                  | R144EFXL                                |                | 2             |                 | •                                            |                                                  |              |

| R144XFE-MP                                        | XFC-MVP                                | R144EFXL                                | •              | 3             | •               | •                                            |                                                  |              |

| R96XFE-V24                                        | XFC-V                                  | RFX96V24                                |                | 2             | •               |                                              | 24                                               |              |

| R96XFE-V24S                                       | XFC-V                                  | RFX96V24-S                              |                | 2             | •               |                                              | 24                                               | •            |

| R96XFE-MV24                                       | XFC-MV                                 | RFX96V24                                | •              | 3             | •               |                                              | 24                                               |              |

| R96XFE-MV24S                                      | XFC-MV                                 | RFX96V24-S                              | •              | 3             | •               |                                              | 24                                               | •            |

| R96XFE-V24P                                       | XFC-VP                                 | RFX96V24                                |                | 2             | •               | •                                            | 24                                               |              |

| R96XFE-V24PS                                      | XFC-VP                                 | RFX96V24-S                              |                | 2             | •               | •                                            | 24                                               | •            |

| R96XFE-MV24P                                      | XFC-MVP                                | RFX96V24                                | •              | 3             | •               | •                                            | 24                                               |              |

| R96XFE-MV24PS                                     | XFC-MVP                                | RFX96V24-S                              | •              | 3             | •               | •                                            | 24                                               | •            |

| R144XFE-V24                                       | XFC-V                                  | RFX144V24                               |                | 2             | •               |                                              | 24                                               |              |

| R144XFE-V24S                                      | XFC-V                                  | RFX144V24-S                             |                | 2             | •               |                                              | 24                                               | •            |

| R144XFE-MV24                                      | XFC-MV                                 | RFX144V24                               | •              | 3             | •               |                                              | 24                                               |              |

| R144XFE-MV24S                                     | XFC-MV                                 | RFX144V24-S                             | •              | 3             | •               |                                              | 24                                               | •            |

| R144XFE-V24P                                      | XFC-VP                                 | RFX144V24                               |                | 2             | •               | •                                            | 24                                               |              |

| R144XFE-V24PS                                     | XFC-VP                                 | RFX144V24-S                             |                | 2             | •               | •                                            | 24                                               | •            |

| R144XFE-MV24P                                     | XFC-MVP                                | RFX144V24                               | •              | 3             | •               | •                                            | 24                                               |              |

| R144XFE-MV24PS                                    | XFC-MVP                                | RFX144V24-S                             | •              | 3             | •               | •                                            | 24                                               | •            |

| R96XFE-V                                          | XFC-V                                  | RFX96V12                                |                | 2             | •               |                                              | 12                                               |              |

| R96XFE-VS                                         | XFC-V                                  | RFX96V12-S                              |                | 2             | •               |                                              | 12                                               | •            |

| R96XFE-MV                                         | XFC-MV                                 | RFX96V12                                | •              | 3             | •               |                                              | 12                                               |              |

| R96XFE-MVS                                        | XFC-MV                                 | RFX96V12-S                              | •              | 3             | •               |                                              | 12                                               | •            |

| R96XFE-VP                                         | XFC-VP                                 | RFX96V12                                |                | 2             | •               | •                                            | 12                                               |              |

| R96XFE-VPS                                        | XFC-VP                                 | RFX96V12-S                              |                | 2             | •               | •                                            | 12                                               | •            |

| R96XFE-MVP                                        | XFC-MVP                                | RFX96V12                                | •              | 3             | •               | •                                            | 12                                               |              |

| R96XFE-MVPS                                       | XFC-MVP                                | RFX96V12-S                              | •              | 3             | •               | •                                            | 12                                               | •            |

| R144XFE-V                                         | XFC-V                                  | RFX144V12                               |                | 2             | •               |                                              | 12                                               |              |

| R144XFE-VS                                        | XFC-V                                  | RFX144V12-S                             |                | 2             | •               |                                              | 12                                               | •            |

| R144XFE-MV                                        | XFC-MV                                 | RFX144V12                               | •              | 3             | •               |                                              | 12                                               |              |

| R144XFE-MVS                                       | XFC-MV                                 | RFX144V12-S                             | •              | 3             | •               |                                              | 12                                               | •            |

| R144XFE-VP                                        | XFC-VP                                 | RFX144V12                               |                | 2             | •               | •                                            | 12                                               |              |

| R144XFE-VPS                                       | XFC-VP                                 | RFX144V12-S                             |                | 2             | •               | •                                            | 12                                               | •            |

| R144XFE-MVP                                       | XFC-MVP                                | RFX144V12                               | •              | 3             | •               | •                                            | 12                                               |              |

| R144XFE-MVPS                                      | XFC-MVP                                | RFX144V12-S                             | •              | 3             | •               | •                                            | 12                                               | •            |

| Notes: 1. MH in soft<br>2. MH/MR in<br>3. MH/MR/N | tware.<br>hardware.<br>IMR and alterna | ting compression,<br>hown for voice sto |                |               |                 |                                              |                                                  |              |

MONOFAX is a registered trademark of Rockwell International.

FAXENGINE, MC24, RPICS and DigiTalk are trademarks of Rockwell International.

# Features (Continued)

- Thermal Printer Interface

- 1 to 4 programmable strobe signals

- Traditional printers and latchless "split mode" printers

- Line lengths up to 4096 pixels

- Line times from 5 to 40 ms

- A/D converter monitors printer head temperature

- Programmable Tone Generator

- Operator Interface

- The XFC can directly drive a 32-key keypad (XFC-B: 20)

- A 8x15 keyboard array is supportable with external circuitry (XFC-B: 5x15)

- Up to eight LEDs are driven directly (XFC-B: 5)

- Typical LCD display modules are supported

- Autobaud Interface

- Automatically detects data rate for external UART support

- Synchronous Asynchronous Receiver Transmitter (SART) Interface

- Programmable baud rate generator support to 9600 bps

- Async mode: 1 start bit, 7/8 data bits, 1 stop bit, no parity

- Sync mode: 8 data bits

- Firmware controllable TXD and SCLK

- General Purpose Inputs and/or Outputs

- Provides up to 20 GPIO (XFC-B: 16) and 8 GPOs

- Real Time Clock

- Battery backup

- 32-year range with leap year compensation

- Watchdog Timer

- Compact Packages

- XFC: 144-pin TQFP

- MONOFAX Modem: 100-pin PQFP

- XIA: 28-pin PLCC

- FAXENGINE Development System (FEES-X and MC24 FERE)

- Provides demonstration, prototype development, and evaluation capabilities to facsimile machine developers using the FAXENGINE Device Set

- Connects to a host PC for software development

# Description

### FAXENGINE eXtended Facsimile Controller

The XFC provides design flexibility by virtue of its built-in peripheral functions (e.g., scanner, printer, and operator interfaces) and programmable hardware registers.

The XFC performs the primary facsimile machine control and monitoring functions, interfacing with all major fax machine components. The MC24<sup>™</sup> embedded processor provides an 8-bit data bus, a 24-bit internal address bus and a direct external memory accessing capability of 16 Mbytes (2 Mbytes for the XFC-B).

Scanner, printer, and keyboard interfaces, as well as motor control and the modem interface, are included.

These programmable functions and interfaces support a wide range of peripherals. An integrated flash ADC, combined with Rockwell's Proprietary Image Correction System (RPICS<sup>™</sup>), provides state-of-the-art image processing performance on both bi-level and half-tone images.

#### **MONOFAX Modems**

Different MONOFAX modem models are available with selection depending upon the desired applications. The R144EFXL and R96DFXL support V.29 and V.17 fax machines, while the RFX modems add integrated fax/digital answering machine functionality by providing a voice codec that yields up to 12 (V12) or 24 (V24) minutes of voice storage per 4 Mbits of memory.

The RFX-S modems support the full range of features listed above and add DigiTalk<sup>™</sup> full-duplex speakerphone features for "Natural" hand-free applications. An integrated Analog front-end (IA) is added to support full-duplex speakerphone operation.

#### FAXENGINE Firmware

The FAXENGINE firmware includes a complete software package–core code and application code–for the development of a customized facsimile machine. The following features are supported by the firmware:

- A real-time multitasking environment

- Modular software design

- T.30 protocol

- Call progress support for multiple countries

- T.4 MH compression and decompression (XFE-B)

- T.4 MH/MR & T.6 MMR control routines

- Alternating compression/decompression for MMR

- B4 to A4 reduction

- · Fax transmit, receive and copy capabilities

- Polling, Broadcast and Delayed Transmission functions

- Page memory functions

- Digital Answering Machine functions

- Voice/Fax Discrimination

**Core Code.** The Core Code provides the functions with close functional proximity to the XFE hardware. The Core Code is provided in object code form ready for linking to developer-provided application program object code. The Core Code is highly structured for maximum application flexibility with minimum overhead.

**Application Code.** The Application Code "builds" an example fax machine using the XFE device set in the FEES-X environment. This code is provided in source code form and serves as basis for the developer's application.

#### **FAXENGINE** Development System

The Rockwell FAXENGINE Evaluation System (FEES-X) and MC24 FERE ROM Emulator provides demonstration, prototype development, and evaluation capabilities to facsimile machine developers using the eXtended FAXENGINE Device Set. The FEES-X offers flexibility for visibility and access. It supplies the Modem Evaluation Board with Data Access Arrangement (DAA), sockets for programmable parts, and connectors for an emulator and all fax machine peripherals. The ROM Emulator (MC24 FERE) is a PC-based code development aid with breakpoint and trace capability for debugging firmware.

# **Hardware Description**

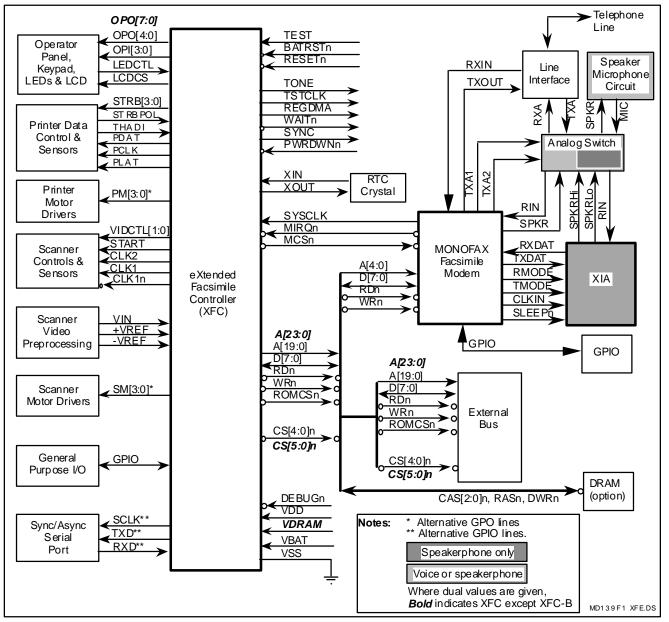

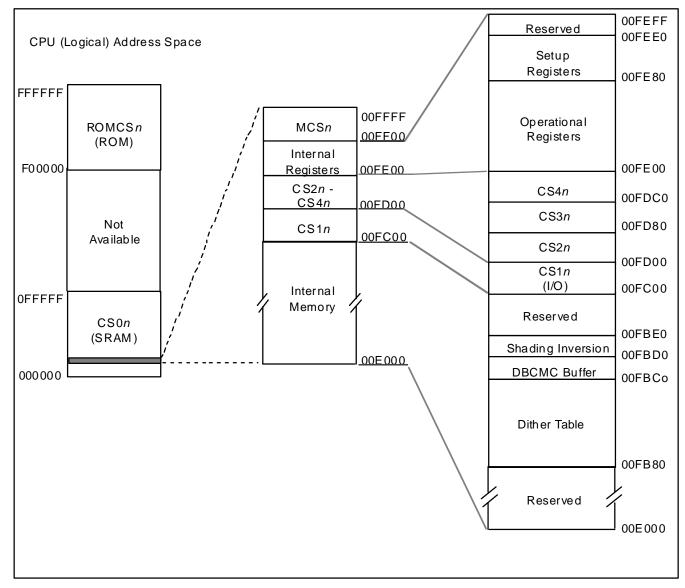

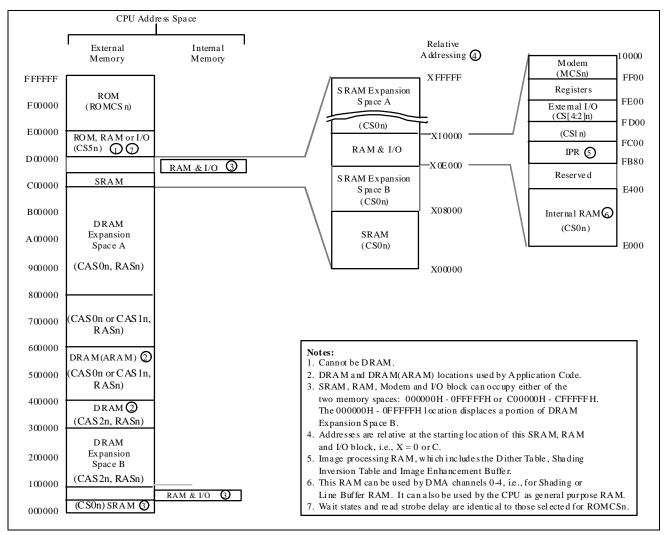

The XFE system-level functional interface is shown in Figure 1. (Note: The suffix n indicates an active low signal.)

#### eXtended Facsimile Controller (XFC)

The XFC contains an internal 8-bit microprocessor with a 16-Mbyte (XFC-B: 2-Mbyte) external address space and dedicated circuitry optimized for facsimile image processing, data compression/decompression and for facsimile machine control and monitoring.

#### Microprocessor

The microprocessor is an enhanced MC24 central processing unit (CPU). This CPU provides fast instruction (10 MHz clock speed) execution and memory efficient input/output bit manipulation. The CPU connects to other

internal XFC functions over a internal 24-bit address bus, 8-bit data bus, and dedicated control lines. The bus is routed outside the XFC for external memory access. The external address bus is 24-bit except for the XFC-B which provides a 20-bit external address bus.

#### **External Bus Control**

Address, data, control, status, interrupt, and decoded chip select signals support connection to external ROM, external RAM, and optional DRAM and peripheral devices. Dedicated internal DMA logic is included for scanner, printer and T.4 access of internal and/or external RAM.

Five (three for XFC-B) internal DMA channels support scanner, printer and T.4 access of the external shading and line buffer RAM. A sixth DMA channel is available to support T.4/T.6 access to external page memory ("External DMA" column, Table 1) or to plain paper printer engines.

Figure 1. XFE Functional Interconnect Diagram

XFE

#### External RAM and ROM

Up to 1 Mbyte of RAM and up to 1 Mbyte of ROM can be connected to the XFC-B as well as external peripherals. Other versions of the XFC can use up to 3 Mbytes of ROM and up to 14 Mbytes of RAM. ROM stores all the FAXENGINE program object code and RAM is used by the FAXENGINE CPU, shading RAM and line buffer RAM.

Independently programmable RAM and ROM wait states from 0 to 3 are supported. RAM sizes may be 8k, 32k, 64k and 1M bytes.

#### **Chip Selects**

Various chip selects (CS) are provided by the XFC such as ROMCSn, CS0n for SRAM, CS1n for external peripherals, MCSn for modem, and optional general purpose chip selects CS[4:2]n and CS5n (except XFC-B).

#### Interrupt Signals

Up to four external interrupts are provided. IRQ8 (GPIO16) is an active high level sensitive interrupt; IRQ5n (GPIO17) and IRQ10n (GPIO18) (except XFC-B) are active low level sensitive interrupts. MIRQn is dedicated to the modem.

#### Scanner and Printer Motor Control

Eight outputs are provided to external current drivers: four for the scanner motor and four for the printer motor. The printer and scanner motor outputs can be programmed as general purpose outputs (GPO) for applications using a single motor or plain paper printers.

#### T.4/T.6 Compressor/Decompressor (See Table 1)

The XFCs (except XFC-B) implement MH and MR data compression and decompression per ITU-T Recommendation T.4 in hardware. The XFC-MV and - MVP also provide MMR data compression and decompression per ITU-T Recommendation T.6 in dedicated hardware. Compression and decompression can be alternated on a line-by-line basis in the XFC-MV and -MVP as well.

#### DRAM Controller (See Table 1)

The DRAM controller supports memory devices of the sizes, number of bits and access speeds tabulated below. DRAM memory space is divided into three blocks thus, if 4M chips are used, a maximum of 12 Mbytes of DRAM is supported. Each block has a programmable size and starting address.

| Addressing Size   | 4M, 1M, 512k, 256k |

|-------------------|--------------------|

| No. of Bits       | 8, 4, 1            |

| Access Speed (ns) | 60 to 150          |

The DRAM controller provides battery backed-up refresh using DRAM battery power (VDRAM).

#### **Bi-Level Resolution Conversion (See Table 1)**

Bi-level expansion (to 200%) and reduction (down to 33%) can be performed on either the scanner bi-level data (described herein), or the bi-level data output by the T4/T6 decompression hardware.

#### **Thermal Printer Control**

The thermal printer interface consists of programmable data, latch, clock, and up to four strobe signals. Programmable timing supports traditional thermal printers, as well as latchless and two-clock split mode printers, and line lengths up to 4096 pixels.

From one to four strobes are generated, with the length of the strobe cycle (line time) and strobe pulse width programmable. Line times from 5 to 40 ms are supported. A strap input to the XFC sets the strobe polarity.

Three signals (PDAT, PCLK, and PLAT) control the transfer of data to the printer.

The XFC includes a 6-bit A/D converter (conversion rate < 80 ms full scale) to monitor the head temperature of the thermal printer. Two external terminating resistors are determined by the specific printhead selected.

#### Scanner and Video Control

Six programmable control and timing signals support common CCD and CIS scanners. The video control function provides signals for controlling the scanner and for processing its video output. Four programmable control signals (START, CLK1, CLK1n, and CLK2) provide timing related to line and pixel timing. These are programmable with regard to start time, relative delay and pulse width.

Two video control output signals (VIDCTL[1:0]) provide digital control for external signal pre-processing circuitry. These signals provide a per pixel period, or per line period, timing with programmable positive-going and negative-going transitions for each signal.

#### Scanner Flash A/D Interface

An internal 6-bit flash A/D converter (FADC) and ADC clock are provided. The A/D reference inputs (Vref+ and Vref–) are available for control by external circuits. A programmable ADC sample position is provided and external video circuits can be tailored by the developer.

#### Video Processing

The XFC supports two modes of correction for scanner data non-uniformities arising from uneven sensor output or uneven illumination. Correction may be provided to an 8-pixel group at a time or, separately to each pixel. Less than 1k bytes of RAM is required to support shading correction. Dynamic background and contrast control is provided for text images. Dithering with edge enhancement is performed for half-tone images. The XFC includes a programmable 8x8 dither table, which is stored in internal RAM (8 bits per table entry). The table is arranged in a matrix of up to 8 rows by up to 8 columns. Multi-level horizontal B4 to A4 reduction is also provided (except XFC-B) for the scanner data.

The XFC includes an optional external image data processing port (multiplexed with GPIO) to allow the OEM developer to access scan data prior to video processing in order to perform proprietary processing.

VID0 - VID7 = parallel output port for multi-level FADC data or shading corrected data (or reduced shading corrected data)

VIDC0 - VIDC1 = control for synchronization with video port data

VIDC2 = bi-level data input for externally processed image data

#### **Operator Interface**

Operator interface functions are supported by the operator output bus OPO[7:0] (OPO[4:0] for the XFC-B), the operator input bus OPI[3:0], and two control outputs (LEDCTL and LCDCS).

The XFC can directly drive a 32-key keypad (20-key for the XFC-B). External blocking diodes are required to isolate the keyboard strobe lines from the LEDs, as the LEDs and keyboard strobe signals use the same lines. An 8x15 keyboard array is supportable with external circuitry (5x15 for the XFC-B).

Up to eight LEDs (five for the XFC-B) can be driven directly by the XFC. The keyboard strobes are shared with the LED drivers. An LED control signal is provided to disable the LEDs during keyboard strobing. The XFC slightly offsets LED turn on/off times thereby preventing power supply overload when all indicators must be activated simultaneously. The LEDCTL signal can supply 12 mA.

Typical LCD display modules are driven by the XFC. The XFC drives the 4-bit bus (OPO[3:0]) and two separate control lines (OPO4 and LCDCS) for LCD support. (For example, the FAXENGINE Development System FEES-X uses a 2-line, 20 character per line, display.)

# Synchronous Asynchronous Receiver Transmitter (SART)

The SART performs serial-to-parallel (S/P) conversion for data received from a peripheral device, and a parallel-to-serial (P/S) conversion of data for transmission to a peripheral device. The interface consists of three lines: TXD, RXD and clock (SCLK). The SART includes a programmable baud rate generator and produces an 8X clock for driving internal logic. Receive data is double-buffered to ease received timing restrictions.

SART status can be read at any time by the CPU. Status includes: IRQ source (TXD or RXD) and operation mode (sync or async). The CPU can also control and monitor TXD and SCLK: RXD can be monitored at any time.

#### Autobaud

The autobaud circuit with supporting firmware is used to analyze a serial data stream in order to determine the baud rate and data structure (parity and character length) to program an external UART.

A precision timer, shift register and edge detector are included to determine the width of the start bit, and to sample the serial data stream. Serial data rates up to 115.2 kbps are supported.

The serial transmitted data is connected to the precision timer and shift register inputs via the SERINP pin. The SEROUT pin is a gated version of the SERINP pin which can be enabled/disabled.

The XFC includes a battery backed-up real time clock. The RTC life is 32 years; its functions include leap year compensation. A 32.768 kHz watch crystal is required by the RTC.

#### General Purpose Inputs and/or Outputs

The XFC provides up to 20 GPIO (16 for XFC-B) and 8 GPO lines.

#### Programmable Tone Generator

A programmable tone generator provides single tone digital output, variable in frequency from 20 to 4000 Hz.

#### System Timing

The XFC can derive its timing from the modem clock or from an external oscillator (max. frequency = 20 MHz). Two internal timer interrupts are provided:

- A 1 ms timer derived from the RTC oscillator timebase (exact period = 1.00708 ms).

- A programmable mechanical subsystem interrupt (MSINT) which serves as a source for motor stepping interrupts and/or scanner and printer interrupts. Independent, programmable, scan and print line times are supported.

#### **Reset and Power Control**

The BATRSTn input initializes the XFC at power-on. An externally generated power-down input, PWRDWNn, controls switching between primary and battery power. The open drain RESETn I/O pin provides a reset output to external circuits, or can accept an externally generated reset. The external reset will not reset the RTC. Separate DRAM and RTC battery power inputs are provided for battery-backed up functions.

#### Documentation

Reference documentation for the XFE family of devices and MONOFAX modems is listed in Table 2.

#### **Environmental and Power Requirements**

Environmental requirements are listed in Table 3 and power requirements are listed in Table 4.

#### **XFC Interface Signals**

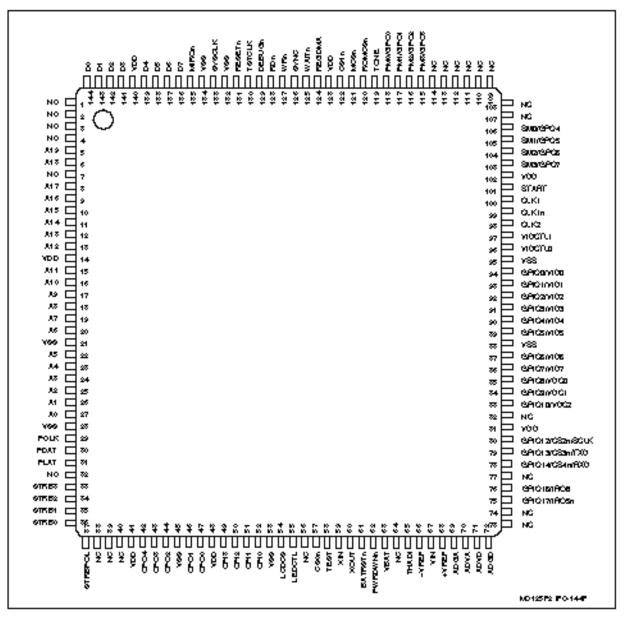

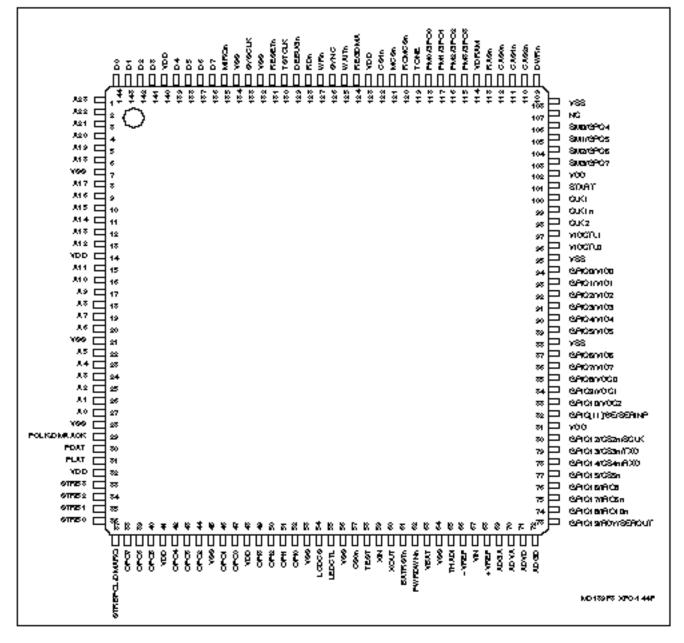

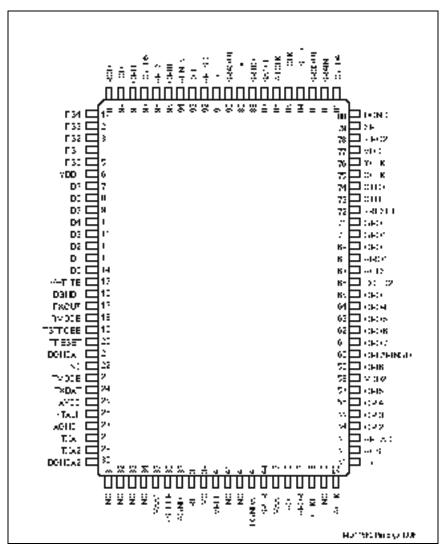

The XFC hardware signal pin assignments are shown in Figures 2 (XFC-B) and 3 (all others), and are described in Tables 5 and 6. Hardware signal characteristics are described in Tables 5 - 7.

#### FACSIMILE MODEM INTERFACE SIGNALS

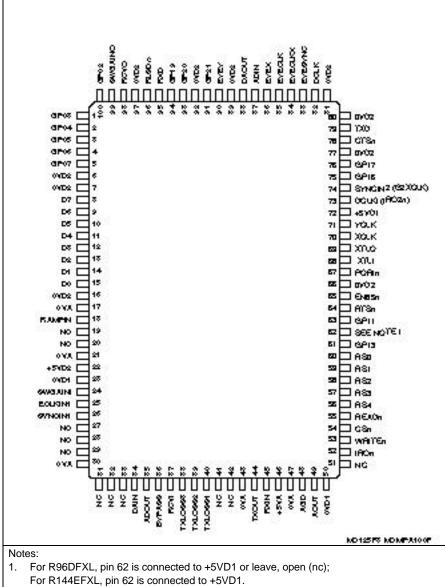

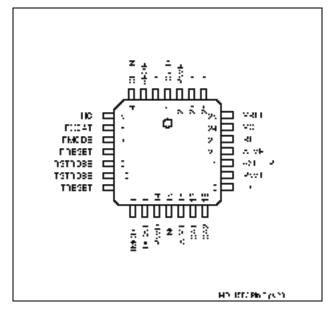

R96DFXL and R144EFXL pin assignments are shown in Figure 4 and described in Table 8. RFX modem hardware interface signals are shown in Figure 5 and described in Table 9. Pin assignments for the 28-pin XIA used with an RFX modem are shown in Figure 6 and are described in Table 10. Modem digital interface signal characteristics are listed in Table 11 and the analog interface characteristics are listed in Table 12. XFE

## **Reference Documentation**

### **Table 2. Reference Documentation**

| Document                                       | Order No. |

|------------------------------------------------|-----------|

| R96DFXL MONOFAX Modem Data Sheet               | MD92      |

| R144EFXL MONOFAX Modem Data Sheet              | MD90      |

| RFX144V12 and RFX96V12 MONOFAX Modems          | MD107     |

| Data Sheet                                     |           |

| RFX144V12-S and RFX96V12-S MONOFAX             | MD115     |

| Modems Data Sheet                              |           |

| RFX144V24-S23 and RFX96V24-S23 MONOFAX         | MD141     |

| Modems Data Sheet                              |           |

| 9600 bps MONOFAX Modem Designer's Guide        | 820       |

| 9600 bps MONOFAX Modem Designer's Guide-       | 820A      |

| Addendum for R96DFXL                           |           |

| R144EFXL MONOFAX Modem Designer's Guide        | 895       |

| RFX144V12 and RFX96V12 MONOFAX Modems          | 1011      |

| Designer's Guide                               |           |

| RFX144V12-S and RFX96V12-S MONOFAX             | 1045      |

| Modems Designer's Guide                        |           |

| RFX144V24-S23 and RFX96V24-S23 MONOFAX         | 1070      |

| Modems Designer's Guide                        |           |

| MC24 Megacell CPU Programmer's Guide           | 415       |

| eXtended Facsimile Controller (XFC-B) Hardware | 1039      |

| Description                                    |           |

| eXtended Facsimile Controller (XFC) Hardware   | 1065      |

| Description (all except -B)                    |           |

| eXtended FAXENGINE (XFE-B) Firmware            | 1040      |

| Description                                    |           |

| FAXENGINE Evaluation System (FEES-X) User's    | 1041      |

| Manual                                         |           |

| MC24 FAXENGINE ROM Emulator System (MC24       | 1016      |

| FERE) User's Manual                            |           |

### **Power Requirements**

#### **Table 4. Power Requirements**

| Device                         | Voltage<br>(Note 1) | Typical<br>Current<br>@25°C<br>(Note 3) | Maximum<br>Current<br>@ 0°C<br>(Note 3) |  |  |  |  |  |  |

|--------------------------------|---------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| XFC-B and XFC                  |                     |                                         |                                         |  |  |  |  |  |  |

| Primary Power                  |                     |                                         |                                         |  |  |  |  |  |  |

| XFC-B                          | +5 VDC +5%/-10%     | 60 mA                                   | 65 mA                                   |  |  |  |  |  |  |

| XFC                            | +5 VDC +5%/-10%     | 65 mA                                   | 70 mA                                   |  |  |  |  |  |  |

| Battery Power and RTC (Note 2) |                     |                                         |                                         |  |  |  |  |  |  |

|                                | +5 VDC              | 18.5 µA                                 | 21.0 µA                                 |  |  |  |  |  |  |

|                                | +3 VDC              | 5.0 µA                                  | 5.5 µA                                  |  |  |  |  |  |  |

|                                | MONOFAX Mo          | odems                                   |                                         |  |  |  |  |  |  |

| R96DFXL                        | +5 VDC ±5%          | 50 mA                                   | 55 mA                                   |  |  |  |  |  |  |

| R144EFXL                       | +5 VDC ±5%          | 54 mA                                   | 60 mA                                   |  |  |  |  |  |  |

| RFX                            | +5 VDC ±5%          | 100/2 mA                                | 119/2.5 mA                              |  |  |  |  |  |  |

| RFX-S                          | +5 VDC ±5% (Note 4) | 124/2.15 mA                             | 149/2.8 mA                              |  |  |  |  |  |  |

| Notes:<br>1. Input vo          | Notes:              |                                         |                                         |  |  |  |  |  |  |

any frequency between 20 and 150 kHz must be less than 500 microvolts peak.

Real Time Clock (RTC) battery power measurements made 2. with a 32.768 kHz crystal oscillator.

Normal/Standby current. Modem and XIA combined. 3.

4.

### **Environmental Requirements**

| Parameter         | Specification                                                                      |

|-------------------|------------------------------------------------------------------------------------|

| Temperature       |                                                                                    |

| Operating         | 0°C to 70°C (32°F to 158°F)                                                        |

| Storage           | -40°C to 80°C (-40°F to 176°F)                                                     |

| Relative Humidity | Up to 90% non-condensing, or a wet bulb temperature up to 35°C, whichever is less. |

# Hardware Interface Signals

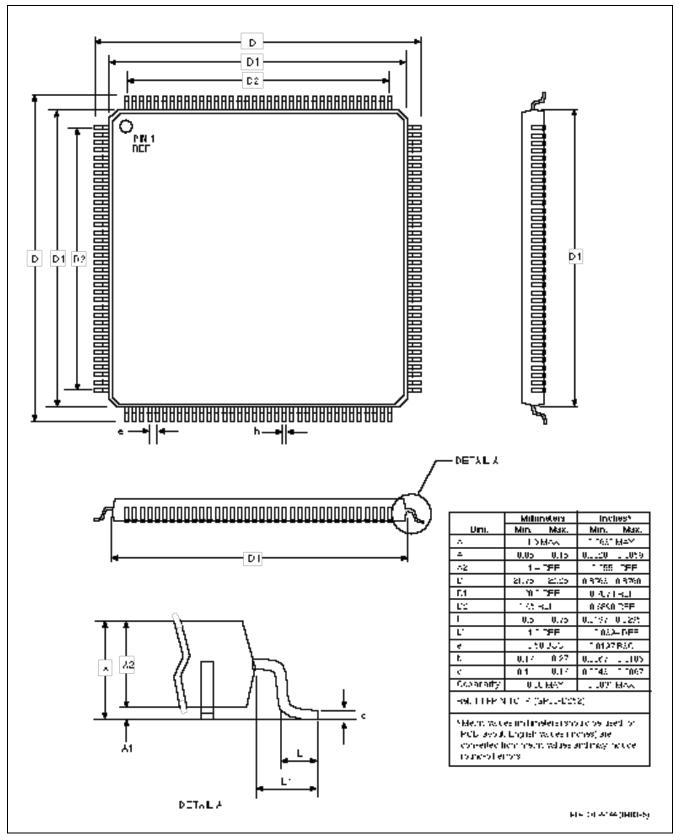

The XFC hardware pin assignments are shown in Figures 2 (XFC-B) and 3 (all others); the signals are described by type in Tables 5 and 6.

Figure 2. XFC-B Pin Signals - 144-Pin TQFP

Figure 3. XFC (Except -B) Pin Signals 144-Pin TQFP.

XFE

|             | Table 5. AFC-B Fin Assignments |     |               |                |                                                                            |  |  |  |  |  |

|-------------|--------------------------------|-----|---------------|----------------|----------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name    | Pin No.                        | I/O | Input<br>Type | Output<br>Type | Pin Description<br>(Note: Active low signals have an "n" pin name ending.) |  |  |  |  |  |

|             |                                |     |               |                | ol Interface                                                               |  |  |  |  |  |

| MIRQn       | 135                            | 1   | HU            |                | Modem interrupt, active low. (Hysteresis In, Internal Pullup.)             |  |  |  |  |  |

| SYSCLK      | 133                            | I   | Н             |                | System clock. (Hysteresis In.)                                             |  |  |  |  |  |

| TSTCLK      | 130                            | 0   |               | 3XC            | Test clock.                                                                |  |  |  |  |  |

|             |                                |     |               | Bus Contr      | ol Interface                                                               |  |  |  |  |  |

| A[19:0]     | [5:6][8:13]<br>[15:20][22:27]  | 0   | Т             | 3XT            | Address bus (20-bit).                                                      |  |  |  |  |  |

| D[7:0]      | [136:139]<br>[141:144]         | I/O | Т             | 3XT            | Data bus (8-bit).                                                          |  |  |  |  |  |

| RDn         | 128                            | 0   |               | 3XTT           | Read strobe.                                                               |  |  |  |  |  |

| WRn         | 127                            | 0   |               | 3XTT           | Write strobe.                                                              |  |  |  |  |  |

| ROMCSn      | 120                            | 0   |               | 2XT            | ROM chip select.                                                           |  |  |  |  |  |

| CS1n        | 122                            | 0   |               | 2XT            | I/O chip select.                                                           |  |  |  |  |  |

| CS0n        | 57                             | 0   |               | 2XTT           | SRAM chip select. (Battery powered.)                                       |  |  |  |  |  |

| MCSn        | 121                            | 0   |               | 2XC            | Modem chip select.                                                         |  |  |  |  |  |

| SYNC        | 126                            | 0   |               | 2XC            | Indicates CPU op code fetch cycle (active high).                           |  |  |  |  |  |

| REGDMA      | 124                            | 0   |               | 3XC            | Indicates REGSEL cycle and DMA cycle.                                      |  |  |  |  |  |

| WAITn       | 125                            | 0   |               | 3XC            | Indicates current TSTCLK cycle is a wait state or a halt state.            |  |  |  |  |  |

|             |                                |     | Prime         | Power Res      | et Logic and Test                                                          |  |  |  |  |  |

| DEBUGn      | 129                            |     | HU            |                | External non-maskable input (NMI).                                         |  |  |  |  |  |

| RESETn      | 131                            | I/O | HU            | 2XO            | XFC Reset.                                                                 |  |  |  |  |  |

| TEST        | 58                             |     | С             |                | Sets Test mode (battery powered).                                          |  |  |  |  |  |

|             |                                | E   | Battery F     | ower Cont      | trol and Reset Logic                                                       |  |  |  |  |  |

| XIN         | 59                             |     | OSC           |                | Crystal oscillator input pin.                                              |  |  |  |  |  |

| XOUT        | 60                             | 0   |               | OSC            | Crystal oscillator output pin.                                             |  |  |  |  |  |

| PWRDWNn     | 62                             | I   | Н             |                | Indicates loss of prime power (results in NMI).                            |  |  |  |  |  |

| BATRSTn     | 61                             |     | Н             |                | Battery power reset input.                                                 |  |  |  |  |  |

|             |                                |     |               | Scanner        | Interface                                                                  |  |  |  |  |  |

| START       | 101                            | 0   |               | 2XS            | Scanner shift gate control.                                                |  |  |  |  |  |

| CLK1        | 100                            | 0   |               | 2XS            | Scanner clock.                                                             |  |  |  |  |  |

| CLK1n       | 99                             | 0   |               | 2XS            | Scanner clock-inverted.                                                    |  |  |  |  |  |

| CLK2        | 98                             | 0   |               | 2XS            | Scanner reset gate control (or clock for CIS scanner).                     |  |  |  |  |  |

| VIDCTL[1:0] | [97:96]                        | 0   |               | 2XC            | Control for video preprocessing circuits.                                  |  |  |  |  |  |

|             |                                |     |               | Printer        | Interface                                                                  |  |  |  |  |  |

| PCLK        | 29                             | 0   |               | 3XC            | Thermal Print Head (TPH) clock.                                            |  |  |  |  |  |

| PDAT        | 30                             | 0   |               | 2XP            | Serial printing data (to TPH).                                             |  |  |  |  |  |

| PLAT        | 31                             | 0   |               | 3XP            | TPH data latch.                                                            |  |  |  |  |  |

| STRB[3:0]   | [33:36]                        | 0   |               | 1XP            | Strobe signals for the TPH.                                                |  |  |  |  |  |

| STRBPOL     | 37                             | I   | С             |                | Sets strobe polarity, active high/low.                                     |  |  |  |  |  |

#### Table 5. XFC-B Pin Assignments

continued

| Table 5. XFC-B Pin Assignments (Continued) |                                    |     |               |                |                                                             |  |  |  |  |

|--------------------------------------------|------------------------------------|-----|---------------|----------------|-------------------------------------------------------------|--|--|--|--|

| Pin Name                                   | Pin No.                            | I/O | Input<br>Type | Output<br>Type | Pin Description                                             |  |  |  |  |

|                                            |                                    |     | 0             | perator Pa     | inel Interface                                              |  |  |  |  |

| OPO[4:0]                                   | [42:44][46:47]                     | 0   |               | 2XL            | Keyboard / LED strobe [4:0].                                |  |  |  |  |

| OPI[3:0]                                   | [49:52]                            | I   | HU            |                | Keyboard return [3:0]. (Pullup, Hysteresis In.)             |  |  |  |  |

| LEDCTL                                     | 55                                 | 0   |               | 4XC            | Indicates outputs OPO[4:0] are for LEDs.                    |  |  |  |  |

| LCDCS                                      | 54                                 | 0   |               | 1XC            | LCD chip select.                                            |  |  |  |  |

| General Purpose I/O                        |                                    |     |               |                |                                                             |  |  |  |  |

| GPIO[7:0]/<br>VID[7:0]                     | [86:87][89:94]                     | I/O | Н             | 2XC            | Programmable: GPIO (8 lines) or video data bus.             |  |  |  |  |

| GPIO[10:8]/<br>VDC[2:0]                    | [83:85]                            | I/O | н             | 2XC            | Programmable: GPIO (3 lines) or video data control signals. |  |  |  |  |

| GPIO12/<br>CS2n/SCLK                       | 80                                 | I/O | н             | 2XC            | Programmable: GPIO line, I/O chip select or SCLK (SART).    |  |  |  |  |

| GPIO13/<br>CS3n/TXD                        | 79                                 | I/O | н             | 2XC            | Programmable: GPIO line, I/O chip select or TXD (SART).     |  |  |  |  |

| GPIO14/<br>CS4n/RXD                        | 78                                 | I/O | Н             | 2XC            | Programmable: GPIO line, I/O chip select or RXD (SART).     |  |  |  |  |

| GPIO16/IRQ8                                | 76                                 | I/O | Н             | 1XC            | Programmable: GPIO line or active high interrupt.           |  |  |  |  |

| GPIO17/<br>IRQ5n                           | 75                                 | I/O | н             | 1XC            | Programmable: GPIO line or active low interrupt.            |  |  |  |  |

|                                            |                                    |     |               | Miscel         | laneous                                                     |  |  |  |  |

| SM[3:0] / GPO[7:4]                         | [103:106]                          | 0   |               | 1XC            | Programmable: scan motor control pins or GPO pins.          |  |  |  |  |

| PM[3:0] / GPO[3:0]                         |                                    | 0   |               | 1XC            | Programmable: print motor control pins or GPO pins.         |  |  |  |  |

| TONE                                       | 119                                | 0   |               | 1XC            | Tone output signal.                                         |  |  |  |  |

|                                            |                                    |     | Power,        | Reference      | Voltages, Ground                                            |  |  |  |  |

| -Vref                                      | 66                                 | I   | -VR           |                | Negative Reference Voltage for Video A/D.                   |  |  |  |  |

| +Vref                                      | 68                                 | I   | +VR           |                | Positive Reference Voltage for Video A/D.                   |  |  |  |  |

| ADGA                                       | 69                                 |     | VADG          |                | A/D Analog Ground.                                          |  |  |  |  |

| ADVA                                       | 70                                 |     | VADV          |                | A/D Analog Power.                                           |  |  |  |  |

| ADGD                                       | 72                                 |     | VADG          |                | A/D Digital Ground.                                         |  |  |  |  |

| ADVD                                       | 71                                 |     | VADV          |                | A/D Digital Power.                                          |  |  |  |  |

| VIN                                        | 67                                 | I   | VA            |                | Analog Video A/D input.                                     |  |  |  |  |

| THADI                                      | 65                                 | 1   | TA            |                | Analog Thermal A/D input.                                   |  |  |  |  |

| VSS(8)                                     | 134, 132, 95, 88,<br>53, 45 28, 21 |     |               |                | Digital Ground.                                             |  |  |  |  |

| VDD (7)                                    | 140, 123, 102,<br>81, 48, 41, 14   |     |               |                | Digital Power.                                              |  |  |  |  |

| VBAT                                       | 63                                 |     |               |                | Battery Power.                                              |  |  |  |  |

|                                            |                                    |     |               | No Cor         | inection                                                    |  |  |  |  |

| NC                                         |                                    |     |               |                |                                                             |  |  |  |  |

#### Table 5. XFC-B Pin Assignments (Continued)

|                   | <b>-</b>                      |     |           |                | B) Pin Assignments                                                         |

|-------------------|-------------------------------|-----|-----------|----------------|----------------------------------------------------------------------------|

| Pin Name          | Pin No.                       | I/O | Input     | Output<br>Type | Pin Description<br>(Note: Active low signals have an "n" pin name ending.) |

|                   |                               |     | Туре      |                | ol Interface                                                               |

| VIRQn             | 135                           | 1   | HU        |                | Modem interrupt, active low. (Hysteresis In, Internal Pullup.)             |

| SYSCLK            | 133                           |     | H         |                | System clock. (Hysteresis In.)                                             |

| TSTCLK            | 130                           | 0   |           | 3XC            | Test clock.                                                                |

| ISICLK            | 130                           | 0   |           |                |                                                                            |

| A [00 0]          | 14 01/0 401                   |     |           |                | ol Interface                                                               |

| A[23:0]           | [1:6][8:13]<br>[15:20][22:27] | 0   | Т         | 3XT            | Address bus (24-bit).                                                      |

| D[7:0]            | [136:139]<br>[141:144]        | I/O | Т         | 3XT            | Data bus (8-bit).                                                          |

| RDn               | 128                           | 0   |           | 3XTT           | Read strobe.                                                               |

| WRn               | 127                           | 0   |           | 3XTT           | Write strobe.                                                              |

| ROMCSn            | 120                           | 0   |           | 2XT            | ROM chip select.                                                           |

| CS1n              | 122                           | 0   |           | 2XT            | I/O chip select.                                                           |

| CS0n              | 57                            | 0   |           | 2XTT           | SRAM chip select. (Battery powered.)                                       |

| MCSn              | 121                           | 0   |           | 2XC            | Modem chip select.                                                         |

| SYNC              | 126                           | 0   |           | 2XC            | Indicates CPU op code fetch cycle (active high).                           |

| REGDMA            | 124                           | 0   |           | 3XC            | Indicates REGSEL cycle and DMA cycle.                                      |

| WAITn             | 125                           | 0   |           | 3XC            | Indicates current TSTCLK cycle is a wait state or a halt state.            |

| RASn              | 113                           | 0   | -         | 3XTT           | DRAM row address select.                                                   |

| CAS[2:0]n         | [110:112]                     | 0   | -         | 2XTT           | DRAM column address select.                                                |

| DWRn              | 109                           | 0   | -         | 3XTT           | DRAM write.                                                                |

|                   |                               |     | Prime     | Power Res      | et Logic and Test                                                          |

| DEBUGn            | 129                           | I   | HU        |                | External non-maskable input (NMI).                                         |

| RESETn            | 131                           | I/O | HU        | 2XO            | XFC Reset.                                                                 |

| TEST              | 58                            | 1   | С         |                | Sets Test mode (battery powered).                                          |

| -                 | 1                             | E   | Battery P | ower Con       | trol and Reset Logic                                                       |

| XIN               | 59                            |     | OSC       |                | Crystal oscillator input pin.                                              |

| XOUT              | 60                            | 0   |           | OSC            | Crystal oscillator output pin.                                             |

| PWRDWNn           | 62                            | 1   | Н         |                | Indicates loss of prime power (results in NMI).                            |

| BATRSTn           | 61                            | - · | Н         |                | Battery power reset input.                                                 |

| b, (into int      | 01                            |     | ••        | Scanner        | Interface                                                                  |

| START             | 101                           | 0   |           | 2XS            | Scanner shift gate control.                                                |

| CLK1              | 100                           | 0   |           | 2XS            | Scanner clock.                                                             |

| CLK1n             | 99                            | 0   |           | 2XS            | Scanner clock.                                                             |

| CLK2              | 98                            | 0   |           | 2XS            | Scanner reset gate control (or clock for CIS scanner).                     |

| VIDCTL[1:0]       | [97:96]                       | 0   |           | 2XC            | Control for video preprocessing circuits.                                  |

|                   |                               | Ŭ   |           |                | Interface                                                                  |

| PCLK/DMAACK       | 29                            | 0   |           | 3XC            | Thermal Print Head (TPH) clock or external DMAACK.                         |

| PDAT              | 30                            | 0   |           | 2XP            | Serial printing data (to TPH).                                             |

| PLAT              | 31                            | 0   |           | 3XP            | TPH data latch.                                                            |

| STRB[3:0]         | [33:36]                       | 0   |           | 1XP            | Strobe signals for the TPH.                                                |

| STRBPOL/<br>DMARQ | 37                            | 1   | C         |                | Sets strobe polarity, active high/low., or external DMAREQ.                |

#### Table 6. XFC (Except -B) Pin Assignments

continued

|                         | Table 6. XFC (Except -B) Pin Assignments              |       |               |                |                                                                    |  |  |  |  |

|-------------------------|-------------------------------------------------------|-------|---------------|----------------|--------------------------------------------------------------------|--|--|--|--|

| Pin Name                | Pin No.                                               | I/O   | Input<br>Type | Output<br>Type | Pin Description                                                    |  |  |  |  |

|                         |                                                       |       | C             | perator Pa     | nel Interface                                                      |  |  |  |  |

| OPO[7:0]                | [38:40][42:44]<br>[46:47]                             | 0     |               | 2XL            | Keyboard / LED strobe [7:0].                                       |  |  |  |  |

| OPI[3:0]                | [49:52]                                               | Ι     | HU            |                | Keyboard return [3:0]. (Pullup, Hysteresis In.)                    |  |  |  |  |

| LEDCTL                  | 55                                                    | 0     |               | 4XC            | Indicates outputs OPO[7:0] are for LEDs.                           |  |  |  |  |

| LCDCS                   | 54                                                    | 0     |               | 1XC            | LCD chip select.                                                   |  |  |  |  |

|                         | •<br>•                                                |       |               | General P      | urpose I/O                                                         |  |  |  |  |

| GPIO[7:0]/<br>VID[7:0]  | [86:87][89:94]                                        | I/O   | Н             | 2XC            | Programmable: GPIO (8 lines) or video data bus.                    |  |  |  |  |

| GPIO[10:8]/<br>VDC[2:0] | [83:85]                                               | I/O   | Н             | 2XC            | Programmable: GPIO (3 lines) or video data control signals.        |  |  |  |  |

| GPIO11/BE/<br>SERINP    | 82                                                    | I/O   | н             | 1XC            | Programmable: GPIO line, Bus Enable, serial data input (Autobaud). |  |  |  |  |

| GPIO12/<br>CS2n/SCLK    | 80                                                    | I/O   | н             | 2XC            | Programmable: GPIO line, I/O chip select or SCLK (SART).           |  |  |  |  |

| GPIO13/<br>CS3n/TXD     | 79                                                    | I/O   | Н             | 2XC            | Programmable: GPIO line, I/O chip select or TXD (SART).            |  |  |  |  |

| GPIO14/<br>CS4n/RXD     | 78                                                    | I/O   | Н             | 2XC            | Programmable: GPIO line, I/O chip select or RXD (SART).            |  |  |  |  |

| GPIO15/CS5n             | 77                                                    | I/O   | Н             | 2XC            | Programmable: GPIO line or I/O chip select.                        |  |  |  |  |

| GPIO16/IRQ8             | 76                                                    | I/O   | Н             | 1XC            | Programmable: GPIO line or active high interrupt.                  |  |  |  |  |

| GPIO17/<br>IRQ5n        | 75                                                    | I/O   | Н             | 1XC            | Programmable: GPIO line or active low interrupt.                   |  |  |  |  |

| GPIO18/IRQ10n           | 74                                                    | I/O   | Н             | 1XC            | Programmable: GPIO line or active low interrupt.                   |  |  |  |  |

| GPIO[19]/RDY/<br>SEROUT | 73                                                    | I/O   | н             | 1XC            | Programmable: GPIO line, Ready or Serial out (Autobaud).           |  |  |  |  |

|                         |                                                       |       |               | Miscell        | aneous                                                             |  |  |  |  |

| SM[3:0] / GPO[7:4]      | [103:106]                                             | 0     |               | 1XC            | Programmable: scan motor control pins or GPO pins.                 |  |  |  |  |

| PM[3:0] / GPO[3:0]      |                                                       | 0     |               | 1XC            | Programmable: print motor control pins or GPO pins.                |  |  |  |  |

| TONE                    | 119                                                   | 0     |               | 1XC            | Tone output signal.                                                |  |  |  |  |

| TONE                    | 110                                                   | U     | Power         | -              | Voltages, Ground                                                   |  |  |  |  |

| -Vref                   | 66                                                    | 1     | -VR           |                | Negative Reference Voltage for Video A/D.                          |  |  |  |  |

| +Vref                   | 68                                                    | 1     | +VR           |                | Positive Reference Voltage for Video A/D.                          |  |  |  |  |

| ADGA                    | 69                                                    | 1     | VADG          |                | A/D Analog Ground.                                                 |  |  |  |  |

| ADVA                    | 70                                                    |       | VADV          |                | A/D Analog Power.                                                  |  |  |  |  |

| ADGD                    | 72                                                    |       | VADG          |                | A/D Digital Ground.                                                |  |  |  |  |

| ADVD                    | 71                                                    |       | VADV          |                | A/D Digital Power.                                                 |  |  |  |  |

| VIN                     | 67                                                    | 1     | VA            |                | Analog Video A/D input.                                            |  |  |  |  |

| THADI                   | 65                                                    | li li | TA            |                | Analog Thermal A/D input.                                          |  |  |  |  |

| VSS(12)                 | 134, 132, 108, 95,<br>88, 64, 56, 53, 45<br>28, 21, 7 |       |               |                | Digital Ground.                                                    |  |  |  |  |

| VDD (8)                 | 140, 123, 102,<br>81, 48, 41, 32, 14                  |       |               |                | Digital Power.                                                     |  |  |  |  |

| VDRAM                   | 114                                                   |       |               |                | Battery power for DRAM refresh.                                    |  |  |  |  |

| VBAT                    | 63                                                    |       |               |                | Battery Power for RTC and SRAM.                                    |  |  |  |  |

|                         |                                                       |       |               | No Con         | nection                                                            |  |  |  |  |

| NC                      | 107                                                   |       |               |                | No connection                                                      |  |  |  |  |

| NC                      | 107,                                                  |       | 1             |                | No connection.                                                     |  |  |  |  |

#### Table 6. XFC (Except -B) Pin Assignments

|               |                               | Input Signal Cha  | acteristics     |                       |                                 |          |

|---------------|-------------------------------|-------------------|-----------------|-----------------------|---------------------------------|----------|

| Input<br>Type | Description                   | VIL<br>(V max)    | VIH<br>(V min)  | Hysteresis<br>(V min) | Pullup<br>Resistance<br>(K ohm) |          |

| С             | CMOS Input                    | 0.3*VDD           | 0.7*VDD         |                       |                                 |          |

| Н             | Hysteresis                    | 0.3*VDD           | 0.6*VDD         | 1.0                   |                                 |          |

| HU            | Hysteresis/Pullup             | 0.3*VDD           | 0.6*VDD         | 1.0                   | 35–150                          |          |

| Т             | TTL Input                     | 0.8               | 2.0             |                       |                                 |          |

| TU            | TTL/Pullup                    | 0.8               | 2.0             |                       | 35-150                          |          |

| OSC           | CMOS Input                    | 0.3*VDD           | 0.7*VDD         |                       |                                 |          |

|               | Abs                           | olute Input Range | = 0.5 to VDD+0. | .5                    |                                 |          |

| Input         | Description                   | Operating         | Operating       | Abs. Max.             | Abs. Max.                       |          |

| Туре          |                               | (V min)           | (V max)         | (V min)               | (V max)                         |          |

| TA            | Thermal Head Analog Input     | 0.2*VDD           | 0.8*VDD         | -0.5                  | VDD+0.5                         |          |

| VA            | Video Analog In               | -VR               | +VR             | -0.5                  | VADV + 0.5                      |          |

| +VR           | Video A/D +Vref               | 0.8               | 3.3             | -0.5                  | VADV + 0.5                      |          |

| -VR           | Video A/D -Vref               | -0.2              | 2.0             | -0.5                  | VADV + 0.5                      |          |

| VADV          | Video A/D Power               | VDD-0.1           | VDD + 0.1       | -0.5                  | 7.0                             |          |

| VADG          | Video A/D GND                 | -0.1              | 0.1             | -0.5                  | 0.5                             |          |

| VDD           | Digital Power                 | 4.5               | 5.25            | -0.5                  | 7.0                             |          |

| GND           | Digital Ground                | 0                 | 0               | 0                     | 0                               |          |

| VDRAM         | Battery Power for DRAM        | 2.25              | 5.25            | -0.5                  | 7.0                             |          |

| VBAT          | Battery Power for<br>RTC/SRAM | 2.25              | 5.25            | -0.5                  | 7.0                             |          |

|               |                               | Output Signal Ch  | aracteristics   |                       |                                 |          |

| Output        | Description                   | VOL               | IOL             | VOH                   | ЮН                              | CL       |

| Туре          |                               | (V max)           | (mA max)        | (V min)               | (mA max)                        | (pF max) |

| 1XC           | CMOS Output (1X)              | 0.4               | 1.6             | VDD-1.5               | 1.6                             | 50       |

| 1XP, 2XP      | High Capacitance Driver       | 0.4               | 1.6             | VDD-1.5               | 1.6                             | 200      |

| 2XC           | CMOS Output (2X)              | 0.4               | 3.5             | VDD-1.5               | 3.5                             | 50       |

| 2XT           | TTL Output (2X)               | 0.4               | 4               | 2.4                   | 4                               | 50       |

| 2XS           | CMOS Output (2X)              | 0.4               | 3.5             | VDD-1.5               | 3.5                             | 50       |

|               | ,                             |                   |                 | 1.5                   | 15                              | 50       |

| 2XL           | LED Driver                    | 0.7               | 10              | VDD-1.5               | 3.5                             | 100      |

| 2XO           | CMOS Output, Open Drain       | 0.4               | 3.5             | N/A                   | N/A                             | 50       |

| 3XC           | CMOS Output (3X)              | 0.4               | 6               | VDD-1.5               | 6                               | 50       |

| 3XP           | High Capacitance Driver (3X)  | 0.4               | 6               | VDD-1.5               | 6                               | 700      |

| 3XT           | TTL Output (3X)               | 0.4               | 6               | 2.4                   | 6                               | 50       |

| 4XC           | CMOS Output (4X)              | 0.4               | 12              | VDD-1.0               | 12                              | 50       |

| 2XTT          | 2X Tristate TTL Output        | 0.4               | 4               | 2.4                   | 4                               | 50       |

| 3XTT          | 3X Tristate TTL Output        | 0.4               | 6               | 2.4                   | 6                               | 50       |

### Table 7. XFC Input and Output Signal Characteristics

2. Names in parentheses apply to R144EFXL only.

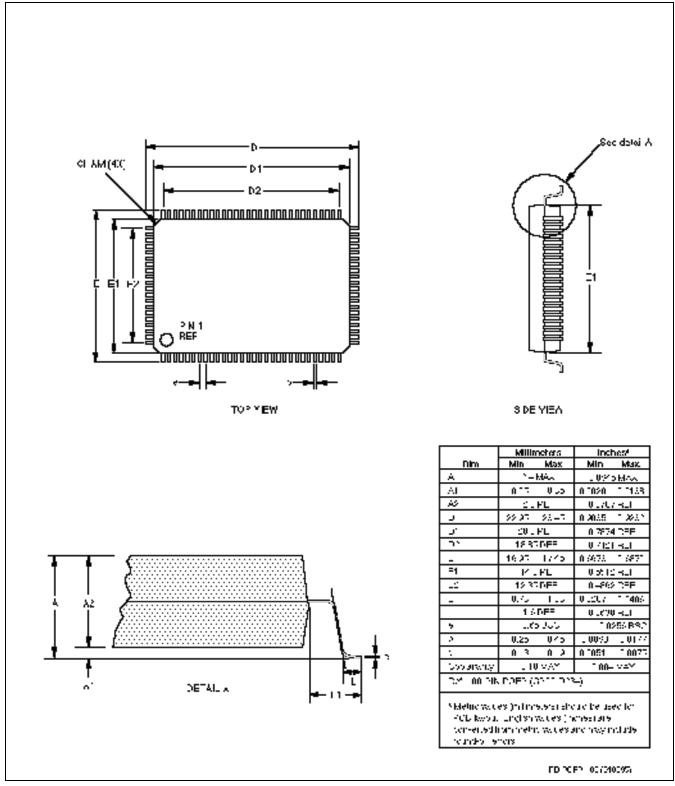

Figure 4. R96DFXL and R144EFXL Facsimile Modem Pin Assignments.

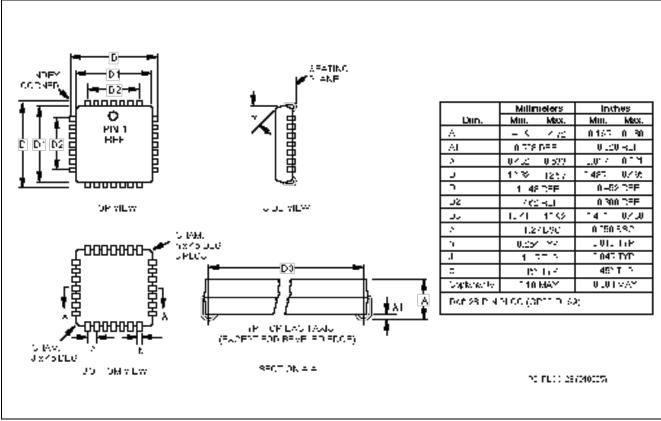

Figure 5. RFX(-S) Facsimile Modem Pin Assignments.

Figure 6. 28-Pin XIA Pin Signals.

| Pin No. | Signal Name | I/O Type | Pin No. | Signal Name      | I/O Type    |

|---------|-------------|----------|---------|------------------|-------------|

| 1       | GP03        | IA/OB    | 51      | NC               |             |

| 2       | GP04        | IA/OB    | 52      | IRQn, (IRQ1n)    | OC (Note 4) |

| 3       | GP05        | IA/OB    | 53      | WRITEn, R/Wn     | IA          |

| 4       | GP06        | IA/OB    | 54      | CSn              | IA          |

| 5       | GP07        | IA/OB    | 55      | READn-f2         | IA          |

| 6       | 0VD2        | GND      | 56      | RS4              | IA          |

| 7       | 0VD2        | GND      | 57      | RS3              | IA          |

| 8       | D7          | IA/OB    | 58      | RS2              | IA          |

| 9       | D6          | IA/OB    | 59      | RS1              | IA          |

| 10      | D5          | IA/OB    | 60      | RS0              | IA          |

| 11      | D4          | IA/OB    | 61      | GP13             | IA/OB       |

| 12      | D3          | IA/OB    | 62      | NC (+5VD1)       | (Note 4)    |

| 13      | D3<br>D2    | IA/OB    | 63      | GP11             | IA/OB       |

| 14      | D1          | IA/OB    | 64      | RTSn             | IA          |

| 15      | D0          | IA/OB    | 65      | EN85n            | R           |

| 15      | 0VD2        | GND      | 66      | 0VD2             | GND         |

| 10      | 0VD2<br>0VA |          |         |                  | ID          |

|         |             | GND      | 67      | PORIn            |             |

| 18      | RAMPIN      | R        | 68      | XTLI             | R           |

| 19      | NC          |          | 69      | XTLO             | R           |