# **RM7000**

# RM7000™ Microprocessor with On-Chip Secondary Cache

# **Datasheet**

**Proprietary and Confidential**

Issue 1, January 2001

## **Legal Information**

## Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-2002175 (R1)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

RM7000 and Fast Packet Cache are trademarks of PMC-Sierra, Inc.

## **Contacting PMC-Sierra**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000 Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: http://www.pmc-sierra.com

# **Revision History**

| Issue<br>No. | Issue Date   | ECN<br>Number | Originator | Details of Change                                                      |

|--------------|--------------|---------------|------------|------------------------------------------------------------------------|

| 1            | January 2001 | 3618          | T. Chapman | Applied PMC-Sierra template to existing MPD (QED) FrameMaker document. |

|              |              |               |            | Changed IP register bits to INT.                                       |

|              |              |               |            | Updated Notes 1 and 5 of the System Interface Parameters table.        |

## **Document Conventions**

The following conventions are used in this datasheet:

- All signal, pin, and bus names described in the text, such as **ExtRqst\***, are in boldface typeface.

- All bit and field names described in the text, such as *Interrupt Mask*, are in an italic-bold typeface.

- All instruction names, such as MFHI, are in san serif typeface.

## **Table of Contents**

| Le  | gal Info | ormation                             | 2   |

|-----|----------|--------------------------------------|-----|

| Re  | vision   | History                              | 3   |

| Do  | cumer    | nt Conventions                       | 4   |

| Tal | ole of   | Contents                             | 5   |

| Lis | of Fig   | gures                                | 7   |

| Lis | of Ta    | bles                                 | 8   |

| 1   | Feat     | Jres                                 | 9   |

| 2   | Block    | CDiagram                             | .10 |

| 3   | Desc     | ription                              | .11 |

| 4   | Hard     | ware Overview                        | .12 |

|     | 4.1      | CPU Registers                        | .12 |

|     | 4.2      | Superscalar Dispatch                 | .12 |

|     | 4.3      | Pipeline                             | .13 |

|     | 4.4      | Integer Unit                         | .14 |

|     | 4.5      | ALU                                  | .15 |

|     | 4.6      | Integer Multiply/Divide              | .15 |

|     | 4.7      | Floating-Point Coprocessor           | 16  |

|     | 4.8      | Floating-Point Unit                  | .16 |

|     | 4.9      | Floating-Point General Register File | .16 |

|     | 4.10     | System Control Coprocessor (CP0)     | .17 |

|     | 4.11     | System Control Coprocessor Registers | 18  |

|     | 4.12     | Virtual to Physical Address Mapping  | 19  |

|     | 4.13     | Joint TLB                            | 20  |

|     | 4.14     | Instruction TLB                      | 20  |

|     | 4.15     | Data TLB                             | 20  |

|     | 4.16     | Cache Memory                         | .21 |

|     | 4.17     | Instruction Cache                    | .21 |

|     | 4.18     | Data Cache                           | .21 |

|     | 4.19     | Secondary Cache                      | .23 |

|     | 4.20     | Secondary Caching Protocols          | 24  |

|     | 4.21     | Tertiary Cache                       | 24  |

|     | 4.22     | Cache Locking                        | .26 |

|     | 4.23     | Cache Management                     | .26 |

|     | 4.24     | Primary Write Buffer                 | .27 |

|     | 4.25     | System Interface                     | .27 |

|     | 4.26     | System Address/Data Bus              | 28  |

|     |          | System Command Bus                   |     |

|     | 4.28     | Handshake Signals                    | 28  |

|     | 4.29     | System Interface Operation           | 29  |

|    | 4.30 Data Prefetch                  | 31 |

|----|-------------------------------------|----|

|    | 4.31 Enhanced Write Modes           | 32 |

|    | 4.32 External Requests              | 32 |

|    | 4.33 Test/Breakpoint Registers      | 32 |

|    | 4.34 Performance Counters           | 33 |

|    | 4.35 Interrupt Handling             | 35 |

|    | 4.36 Standby Mode                   | 37 |

|    | 4.37 JTAG Interface                 | 37 |

|    | 4.38 Boot-Time Options              | 37 |

|    | 4.39 Boot-Time Modes                | 37 |

| 5  | Pin Descriptions                    | 39 |

| 6  | Absolute Maximum Ratings1           | 43 |

| 7  | Recommended Operating Conditions    | 44 |

| 8  | DC Electrical Characteristics       | 45 |

| 9  | Power Consumption                   | 46 |

| 10 | AC Electrical Characteristics       | 47 |

|    | 10.1 Capacitive Load Deration       | 47 |

|    | 10.2 Clock Parameters               | 47 |

|    | 10.3 System Interface Parameters    | 48 |

|    | 10.4 Boot-Time Interface Parameters | 48 |

| 11 | Timing Diagrams                     | 49 |

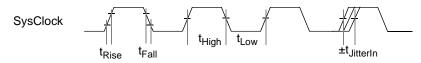

|    | 11.1 Clock Timing                   | 49 |

| 12 | Packaging Information               | 50 |

| 13 | RM7000 Pinout                       | 51 |

| 14 | Ordering Information                | 53 |

# **List of Figures**

| Figure 1  | Block Diagram                                | 10 |

|-----------|----------------------------------------------|----|

| Figure 2  | CP0 Registers                                | 12 |

| Figure 3  | Instruction Issue Paradigm                   | 13 |

| Figure 4  | Pipeline 1                                   | 4  |

| Figure 5  | CP0 Registers                                | 18 |

| Figure 6  | Kernel Mode Virtual Addressing (32-bit mode) | 19 |

| Figure 7  | Tertiary Cache Hit and Miss                  | 25 |

| Figure 8  | Typical Embedded System Block Diagram        | 28 |

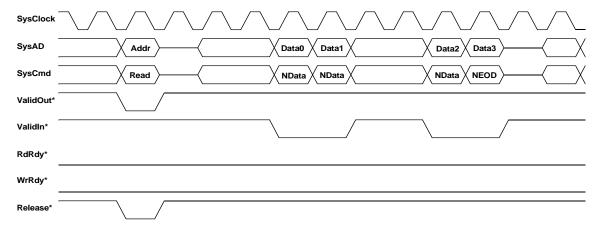

| Figure 9  | Processor Block Read                         | 30 |

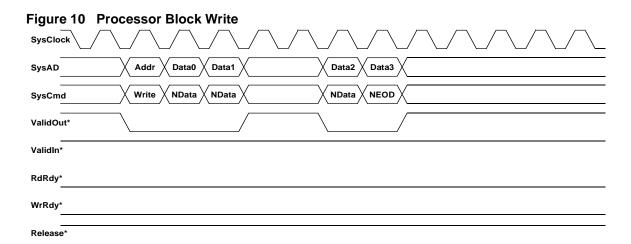

| Figure 10 | Processor Block Write                        | 31 |

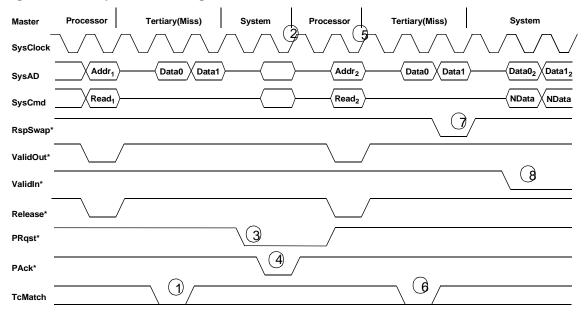

| Figure 11 | Multiple Outstanding Reads                   | 31 |

| Figure 12 | Clock Timing                                 | 49 |

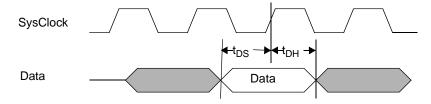

| Figure 13 | Input Timing                                 | 49 |

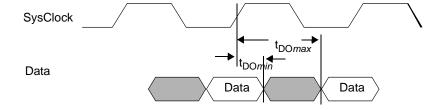

| Figure 14 | Output Timing                                | 49 |

## **List of Tables**

| Table 1  | Instruction Issue Rules                   | 12 |

|----------|-------------------------------------------|----|

| Table 2  | Dual Issue Instruction Classes            | 13 |

| Table 3  | ALU Operations                            | 15 |

| Table 4  | Integer Multiply/Divide Operations        | 15 |

| Table 5  | Floating Point Latencies and Repeat Rates | 17 |

| Table 6  | Cache Attributes                          | 26 |

| Table 7  | Cache Locking Control                     | 26 |

| Table 8  | Penalty Cycles                            | 27 |

| Table 9  | Watch Control Register                    | 33 |

| Table 10 | Performance Counter Control               | 34 |

| Table 11 | Cause Register                            | 36 |

| Table 12 | Interrupt Control Register                | 36 |

| Table 13 | IPLLO Register                            | 36 |

| Table 14 | IPLHI Register                            | 36 |

| Table 15 | Interrupt Vector Spacing                  | 37 |

| Table 16 | Boot Time Mode Stream                     | 38 |

| Table 17 | System interface Pins                     | 39 |

| Table 18 | Clock/control interface Pins              | 40 |

| Table 19 | Tertiary cache interfacePins              | 41 |

| Table 20 | Interrupt Interface Pins                  | 42 |

| Table 21 | JTAG Interface Pins                       | 42 |

| Table 22 | Initialization Interface Pins             | 42 |

#### 1 Features

- Dual Issue symmetric superscalar microprocessor with instruction prefetch optimized for system level price/performance

- 200, 250, 266, 300 MHz operating frequency

- >500 Dhrystone 2.1 MIPS @ 300 MHz

- High-performance system interface

- 1000 MB per second peak throughput

- 125 MHz max. freq., multiplexed address/data

- Supports two outstanding reads with out-of-order return

- Processor clock multipliers 2, 2.5, 3, 3.5, 4, 4.5, 5, 6, 7, 8, 9

- Integrated primary and secondary caches all are 4-way set associative with 32 byte line size

- 16 KB instruction, 16 KB data, 256 KB on-chip secondary

- Per line cache locking in primaries and secondary

- Fast Packet Cache<sup>TM</sup> increases system efficiency in networking applications

- Integrated external cache controller (up to 8 MB)

- High-performance floating-point unit 600 MFLOPS maximum

- Single cycle repeat rate for common single-precision operations and some double-precision operations

- Single cycle repeat rate for single-precision combined multiply-add operations

- Two cycle repeat rate for double-precision multiply and double-precision combined multiply-add operations

- MIPS IV Superset Instruction Set Architecture

- Data PREFETCH instruction allows the processor to overlap cache miss latency and instruction execution

- Single-cycle floating-point multiply-add

- · Integrated memory management unit

- Fully associative joint TLB (shared by I and D translations)

- 64/48 dual entries map 128/96 pages

- Variable page size

- Embedded application enhancements

- Specialized DSP integer Multiply-Accumulate instructions, (MAD/MADU) and threeoperand multiply instruction (MUL)

- I&D Test/Break-point (Watch) registers for emulation & debug

- Performance counter for system and software tuning & debug

- Fourteen fully prioritized vectored interrupts 10 external, 2 internal, 2 software

- Fully static CMOS design with dynamic power down logic

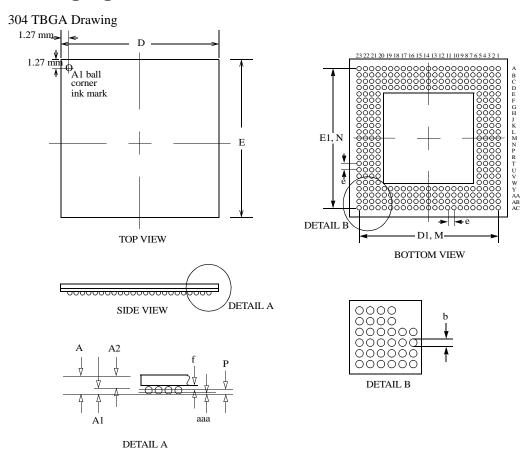

- RM5271 pin compatible, 304 pin TBGA package, 31x31 mm

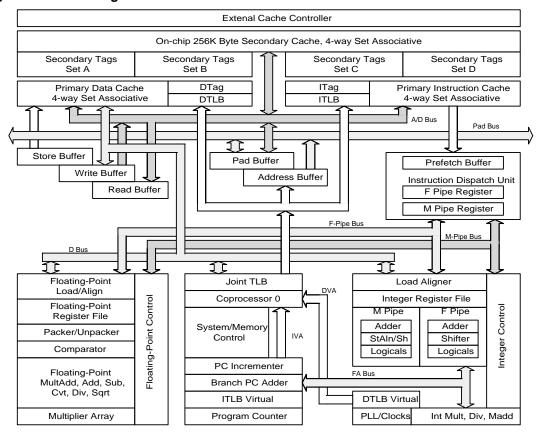

## 2 Block Diagram

Figure 1 Block Diagram

## 3 Description

PMC-Sierra's RM7000 is a highly integrated symmetric superscalar microprocessor capable of issuing two instructions each processor cycle. It has two high-performance 64-bit integer units as well as a high-throughput, fully pipelined 64-bit floating point unit. To keep its multiple execution units running efficiently, the RM7000 integrates not only 16 KB 4-way set associative instruction and data caches but backs them up with an integrated 256 KB 4-way set associative secondary as well. For maximum efficiency, the data and secondary caches are write-back and non-blocking. An optional external tertiary cache provides high-performance capability even in applications having very large data sets.

A RM5200 Family compatible, operating system friendlymemory management unit with a 64/48-entry fully associative TLB and a high-performance 64-bit system interface supporting multiple outstanding reads with out-of-order return and hardware prioritized and vectored interrupts round out the main features of the processor.

The RM7000 is ideally suited for high-end embedded control applications such as internetworking, high-performance image manipulation, high-speed printing, and 3-D visualization. The RM7000 is also applicable to the low end workstation market where its balanced integer and floating-point performance and direct support for a large tertiary cache (up to 8 MB) provide outstanding price/performance.

## 4 Hardware Overview

The RM7000 offers a high-level of integration targeted at high-performance embedded applications. The key elements of the RM7000 are briefly described below.

#### 4.1 CPU Registers

Like all MIPS ISA processors, the RM7000 CPU has a simple, clean user visible state consisting of 32 general purpose registers (GPR), two special purpose registers for integer multiplication and division, and a program counter; there are no condition code bits. Figure 2 shows the user visible state.

Figure 2 CP0 Registers

| Multiply/Divide Registers |

|---------------------------|

| 63 0                      |

| HI                        |

| 63 0                      |

| LO                        |

|                           |

| Program Counter           |

| 63 0                      |

| PC                        |

|                           |

|                           |

|                           |

## 4.2 Superscalar Dispatch

The RM7000 has an efficient symmetric superscalar dispatch unit which allows it to issue up to two instructions per cycle. For purposes of instruction issue, the RM7000 defines four classes of instructions: integer, load/store, branches, and floating-point. There are two logical pipelines, the *function*, or F, pipeline and the *memory*, or M, pipeline. Note however that the M pipe can execute integer as well as memory type instructions.

**Table 1 Instruction Issue Rules**

| F Pipe                                            | M Pipe              |

|---------------------------------------------------|---------------------|

| one of:                                           | one of:             |

| integer, branch, floating-point, integer mul, div | integer, load/store |

Figure 3 is a simplification of the pipeline section and illustrates the basics of the instruction issue mechanism.

Dispatch Unit

F Pipe IBus

M Pipe IBus

FP F Pipe

FP M Pipe

Integer F Pipe

M Pipe

Figure 3 Instruction Issue Paradigm

The figure illustrates that one F pipe instruction and one M pipe instruction can be issued concurrently but that two M pipe or two F pipe instructions cannot be issued. Table 2 specifies more completely the instructions within each class.

Table 2 Dual Issue Instruction Classes

| integer                        | load/store                                              | floating-point                                          | branch                           |

|--------------------------------|---------------------------------------------------------|---------------------------------------------------------|----------------------------------|

| add, sub, or, xor, shift, etc. | lw, sw, ld, sd, ldc1,<br>sdc1, mov, movc,<br>fmov, etc. | fadd, fsub, fmult,<br>fmadd, fdiv, fcmp,<br>fsqrt, etc. | beq, bne, bCzT,<br>bCzF, j, etc. |

The symmetric superscalar capability of the RM7000, in combination with its low latency integer execution units and high-throughput fully pipelined floating-point execution unit, provides unparalleled price/performance in computational intensive embedded applications.

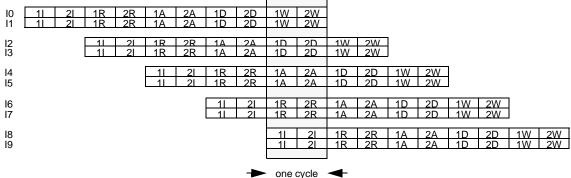

## 4.3 Pipeline

The logical length of both the F and M pipelines is five stages with state committing in the register write, or W, pipe stage. The physical length of the floating-point execution pipeline is actually seven stages but this is completely transparent to the user.

Figure 4 shows instruction execution within the RM7000 when instructions are issuing simultaneously down both pipelines. As illustrated in the figure, up to ten instructions can be executing simultaneously. This figure presents a somewhat simplistic view of the processors operation however since the out-of-order completion of loads, stores, and long latency floating-point operations can result in there being even more instructions in process than what is shown.

#### Figure 4 Pipeline

- 1I-1R: Instruction cache access

- 21: Instruction virtual to physical address translation

- 2R: Register file read, Bypass calculation, Instruction decode, Branch address calculation

1A: Issue or slip decision, Branch decision

1A: Data virtual address calculation

- 1A-2A: Integer add, logical, shift

- 2A: Store Align

- -2D: Data cache access and load align

- 1D: Data virtual to physical address translation

- 2W: Register file write

Note that instruction dependencies, resource conflicts, and branches result in some of the instruction slots being occupied by NOPs.

#### 4.4 Integer Unit

Like the RM5200 Fcamily, the RM7000 implements the MIPS IV Instruction Set Architecture, and is therefore fully upward compatible with applications that run on processors such as the R4650 and R4700 that implement the earlier generation MIPS III Instruction Set Architecture. Additionally, the RM7000 includes two implementation specific instructions not found in the baseline MIPS IV ISA, but that are useful in the embedded market place. Described in detail in a later section, these instructions are integer multiply-accumulate and three-operand integer multiply.

The RM7000 integer unit includes thirty-two general purpose 64-bit registers, the HI/LO result registers for the two-operand integer multiply/divide operations, and the program counter, or PC. There are two separate execution units, one of which can execute function, or F, type instructions and one which can execute memory, or M, type instructions. See above for a description of the instruction types and the issue rules. As a special case, integer multiply/divide instructions as well as their corresponding MFHI and MFLO instructions can only be executed in the F type execution unit. Within each execution unit the operational characteristics are the same as on previous MIPS designs with single cycle ALU operations (add, sub, logical, shift), one cycle load delay, and an autonomous multiply/divide unit.

#### Register File

The RM7000 has thirty-two general purpose registers with register location 0 (r0) hard wired to a zero value. These registers are used for scalar integer operations and address calculation. In order to service the two integer execution units, the register file has four read ports and two write ports and is fully bypassed both within and between the two execution units to minimize operation latency in the pipeline.

#### 4.5 ALU

The RM7000 has two complete integer ALUs each consisting of an integer adder/subtractor, a logic unit, and a shifter. Table 3 shows the functions performed by the ALUs for each execution unit. Each of these units is optimized to perform all operations in a single processor cycle.

Table 3 ALU Operations

| Unit    | F Pipe                          | M Pipe                          |

|---------|---------------------------------|---------------------------------|

| Adder   | add, sub                        | add, sub, data address add      |

| Logic   | logic, moves, zero shifts (nop) | logic, moves, zero shifts (nop) |

| Shifter | non zero shift                  | non zero shift, store align     |

## 4.6 Integer Multiply/Divide

The RM7000 has a single dedicated integer multiply/divide unit optimized for high-speed multiply and multiply-accumulate operations. The multiply/divide unit resides in the F type execution unit. Table 4 shows the performance of the multiply/divide unit on each operation.

Table 4 Integer Multiply/Divide Operations

| Opcode           | Operand<br>Size | Latency | Repeat<br>Rate | Stall<br>Cycles |

|------------------|-----------------|---------|----------------|-----------------|

| MULT/U,          | 16 bit          | 4       | 3              | 0               |

| MAD/U            | 32 bit          | 5       | 4              | 0               |

| MUL              | 16 bit          | 4       | 3              | 2               |

|                  | 32 bit          | 5       | 4              | 3               |

| DMULT,<br>DMULTU | any             | 9       | 8              | 0               |

| DIV, DIVD        | any             | 36      | 36             | 0               |

| DDIV,<br>DDIVU   | any             | 68      | 68             | 0               |

The baseline MIPS IV ISA specifies that the results of a multiply or divide operation be placed in the Hi and Lo registers. These values can then be transferred to the general purpose register file using the Move-from-Hi and Move-from-Lo (MFHI/MFLO) instructions.

In addition to the baseline MIPS IV integer multiply instructions, the RM7000 also implements the 3-operand multiply instruction, MUL. This instruction specifies that the multiply result go directly to the integer register file rather than the Lo register. The portion of the multiply that would have normally gone into the Hi register is discarded. For applications where it is known that the upper half of the multiply result is not required, using the MUL instruction eliminates the necessity of executing an explicit MFLO instruction.

Also included in the RM7000 are the multiply-add instructions MAD/MADU. This instruction multiplies two operands and adds the resulting product to the current contents of the Hi and Lo registers. The multiply-accumulate operation is the core primitive of almost all signal processing

algorithms allowing the RM7000 to eliminate the need for a separate DSP engine in many embedded applications.

By pipelining the multiply-accumulate function and dynamically determining the size of the input operands, the RM7000 is able to maximize throughput while still using an area efficient implementation.

## 4.7 Floating-Point Coprocessor

The RM7000 incorporates a high-performance fully pipelined floating-point coprocessor which includes a floating-point register file and autonomous execution units for multiply/add/convert and divide/square root. The floating-point coprocessor is a tightly coupled co-execution unit, decoding and executing instructions in parallel with, and in the case of floating-point loads and stores, in cooperation with the M pipe of the integer unit. As described earlier, the superscalar capabilities of the RM7000 allow floating-point computation instructions to issue concurrently with integer instructions.

#### 4.8 Floating-Point Unit

The RM7000 floating-point execution unit supports single and double precision arithmetic, as specified in the IEEE Standard 754. The execution unit is broken into a separate divide/square root unit and a pipelined multiply/add unit. Overlap of divide/square root and multiply/add is supported.

The RM7000 maintains fully precise floating-point exceptions while allowing both overlapped and pipelined operations. Precise exceptions are extremely important in object-oriented programming environments and highly desirable for debugging in any environment.

The floating-point unit's operation set includes floating-point add, subtract, multiply, multiply-add, divide, square root, reciprocal, reciprocal square root, conditional moves, conversion between fixed-point and floating-point format, conversion between floating-point formats, and floating-point compare. Table 5 gives the latencies of the floating-point instructions in internal processor cycles.

## 4.9 Floating-Point General Register File

The floating-point general register file, FGR, is made up of thirty-two 64-bit registers. With the floating-point load and store double instructions, LDC1 and SDC1, the floating-point unit can take advantage of the 64-bit wide data cache and issue a floating-point coprocessor load or store doubleword instruction in every cycle.

The floating-point control register file contains two registers; one for determining configuration and revision information for the coprocessor and one for control and status information. These registers are primarily used for diagnostic software, exception handling, state saving and restoring, and control of rounding modes.

Table 5 Floating Point Latencies and Repeat Rates

| Operation   | Latency<br>Single/double | Repeat Rate<br>Single/double |

|-------------|--------------------------|------------------------------|

|             | _                        | _                            |

| fadd        | 4                        | 1                            |

| fsub        | 4                        | 1                            |

| fmult       | 4/5                      | 1/2                          |

| fmadd       | 4/5                      | 1/2                          |

| fmsub       | 4/5                      | 1/2                          |

| fdiv        | 21/36                    | 19/34                        |

| fsqrt       | 21/36                    | 19/34                        |

| frecip      | 21/36                    | 19/34                        |

| frsqrt      | 38/68                    | 36/66                        |

| fcvt.s.d    | 4                        | 1                            |

| fcvt.s.w    | 6                        | 3                            |

| fcvt.s.l    | 6                        | 3                            |

| fcvt.d.s    | 4                        | 1                            |

| fcvt.d.w    | 4                        | 1                            |

| fcvt.d.l    | 4                        | 1                            |

| fcvt.w.s    | 4                        | 1                            |

| fcvt.w.d    | 4                        | 1                            |

| fcvt.l.s    | 4                        | 1                            |

| fcvt.l.d    | 4                        | 1                            |

| fcmp        | 1                        | 1                            |

| fmov, fmovc | 1                        | 1                            |

| fabs, fneg  | 1                        | 1                            |

To support superscalar operations, the FGR has four read ports and two write ports, and is fully bypassed to minimize operation latency in the pipeline. Three of the read ports and one write port are used to support the combined multiply-add instruction while the fourth read and second write port allows a concurrent floating-point load or store and conditional moves.

## 4.10 System Control Coprocessor (CP0)

The system control coprocessor (CP0) in the MIPS architecture is responsible for the virtual memory sub-system, the exception control system, and the diagnostics capability of the processor. In the MIPS architecture, the system control coprocessor (and thus the kernel software) is implementation dependent. For memory management, the RM7000 CP0 is logically identical to that of the RM5200 Family and R5000. For interrupt exceptions and diagnostics, the RM7000 is a superset of the RM5200 Family and R5000 implementing additional features described later in the sections on Interrupts, the Test/Breakpoint facility, and the Performance Counter facility.

The memory management unit controls the virtual memory system page mapping. It consists of an instruction address translation buffer (ITLB), a data address translation buffer (DTLB), a Joint TLB (JTLB), and coprocessor registers used by the virtual memory mapping sub-system.

#### 4.11 System Control Coprocessor Registers

The RM7000 incorporates all system control coprocessor (CP0) registers internally. These registers provide the path through which the virtual memory system's page mapping is examined and modified, exceptions are handled, and operating modes are controlled (kernel vs. user mode, interrupts enabled or disabled, cache features). In addition, the RM7000 includes registers to implement a real-time cycle counting facility, to aid in cache and system diagnostics, and to assist in data error detection.

To support the non-blocking caches and enhanced interrupt handling capabilities of the RM7000, both the data and control register spaces of CP0 are supported by the RM7000. In the data register space, that is the space accessed using the MFC0 and MTC0 instructions, the RM7000 supports the same registers as found in the RM5200, R4000 and R5000 families. In the control space, that is the space accessed by the previously unused CTC0 and CFC0 instructions, the RM7000 supports five new registers. The first three of these new 32-bit registers support the enhanced interrupt handling capabilities and are the Interrupt Control, Interrupt Priority Level Lo (IPLLO), and Interrupt Priority Level Hi (IPLHI) registers. These registers are described further in the section on interrupt handling. The other two registers, Imprecise Error 1 and Imprecise Error 2, have been added to help diagnose bus errors which occur on non-blocking memory references.

Figure 5 shows the CP0 registers.

47 Info Status Cause 12 13\* Index **EPC** Watch1 Watch Mask 14' 18 24\* TLB Random Watch2 **XContext** Wired **ECC** CacheErr (entries protected from TLBWR) **PRId ErrorEPC** LLAddr TagHi 29\* Config 16\* Used for memory Used for exception management \* Register number processing

Figure 5 CP0 Registers

## 4.12 Virtual to Physical Address Mapping

The RM7000 provides three modes of virtual addressing:

- user mode

- supervisor mode

- kernel mode

This mechanism is available to system software to provide a secure environment for user processes. Bits in the CPO Status register determine which virtual addressing mode is used. In the user mode, the RM7000 provides a single, uniform virtual address space of 256 GB (2 GB in 32-bit mode).

When operating in the kernel mode, four distinct virtual address spaces, totalling 1024 GB (4 GB in 32-bit mode), are simultaneously available and are differentiated by the high-order bits of the virtual address.

The RM7000 processor also supports a supervisor mode in which the virtual address space is 256.5 GB (2.5 GB in 32-bit mode), divided into three regions based on the high-order bits of the virtual address. Figure 6 shows the address space layout for 32-bit operation.

Figure 6 Kernel Mode Virtual Addressing (32-bit mode)

| 0xfffffff  | Kernel virtual address space           |

|------------|----------------------------------------|

|            | (kseg3)                                |

| 0xE0000000 | Mapped, 0.5GB                          |

|            |                                        |

| 0xDFFFFFFF | Supervisor virtual address space       |

|            | (ksseg)                                |

| 0xC0000000 | Mapped, 0.5GB                          |

|            |                                        |

| 0xBFFFFFFF | Uncached kernel physical address space |

|            | (kseg1)                                |

| 0xA0000000 | Unmapped, 0.5GB                        |

|            |                                        |

| 0x9FFFFFFF | Cached kernel physical address space   |

|            | (kseg0)                                |

| 0x80000000 | Unmapped, 0.5GB                        |

|            |                                        |

| 0x7FFFFFFF | User virtual address space             |

|            | (kuseg)                                |

|            | Mapped, 2.0GB                          |

|            | ]                                      |

When the RM7000 is configured for 64-bit addressing, the virtual address space layout is an upward compatible extension of the 32-bit virtual address space layout.

#### 4.13 Joint TLB

For fast virtual-to-physical address translation, the RM7000 uses a large, fully associative TLB that maps virtual pages to their corresponding physical addresses. As indicated by its name, the joint TLB (JTLB) is used for both instruction and data translations. The JTLB is organized as pairs of even/odd entries, and maps a virtual address and address space identifier into the large, 64 GB physical address space. By default, the JTLB is configured as 48 pairs of even/odd entries. The 64 even/odd entry optional configuration is set at boot time.

Two mechanisms are provided to assist in controlling the amount of mapped space, and the replacement characteristics of various memory regions. First, the page size can be configured, on a per-entry basis, to use page sizes in the range of 4 KB to 16 MB (in 4X multiples). A CP0 register, PageMask, is loaded with the desired page size of a mapping, and that size is stored into the TLB along with the virtual address when a new entry is written. Thus, operating systems can create special purpose maps; for example, a typical frame buffer can be memory mapped using only one TLB entry.

The second mechanism controls the replacement algorithm when a TLB miss occurs. The RM7000 provides a random replacement algorithm to select a TLB entry to be written with a new mapping; however, the processor also provides a mechanism whereby a system specific number of mappings can be locked into the TLB, thereby avoiding random replacement. This mechanism allows the operating system to guarantee that certain pages are always mapped for performance reasons and for deadlock avoidance. This mechanism also facilitates the design of real-time systems by allowing deterministic access to critical software.

The JTLB also contains information that controls the cache coherency protocol for each page. Specifically, each page has attribute bits to determine whether the coherency algorithm is: uncached, write-back, write-through with write-allocate, write-through without write-allocate, write-back with secondary and tertiary bypass. Note that both of the write-through protocols bypass both the secondary and the tertiary caches since neither of these caches support writes of less than a complete cache line.

These protocols are used for both code and data on the RM7000 with data using write-back or write-through depending on the application. The write-through modes support the same efficient frame buffer handling as the RM5200 Family, R4700, and R5000.

#### 4.14 Instruction TLB

The RM7000 uses a 4-entry instruction TLB (ITLB) to minimize contention for the JTLB, to eliminate the critical path of translating through a large associative array, and to save power. Each ITLB entry maps a 4 KB page. The ITLB improves performance by allowing instruction address translation to occur in parallel with data address translation. When a miss occurs on an instruction address translation by the ITLB, the least-recently used ITLB entry is filled from the JTLB. The operation of the ITLB is completely transparent to the user.

#### 4.15 Data TLB

The RM7000 uses a 4-entry data TLB (DTLB) for the same reasons cited above for the ITLB. Each DTLB entry maps a 4 KB page. The DTLB improves performance by allowing data address translation to occur in parallel with instruction address translation. When a miss occurs on a data

address translation by the DTLB, the DTLB is filled from the JTLB. The DTLB refill is pseudo-LRU: the least recently used entry of the least recently used pair of entries is filled. The operation of the DTLB is completely transparent to the user.

#### 4.16 Cache Memory

In order to keep the RM7000's superscalar pipeline full and operating efficiently, the RM7000 has integrated primary instruction and data caches with single cycle access as well as a large unified secondary cache with a three cycle miss penalty from the primaries. Each primary cache has a 64-bit read path, a 128-bit write path, and both caches can be accessed simultaneously. The primary caches provide the integer and floating-point units with an aggregate bandwidth of 4.8 GB per second at an internal clock frequency of 300 MHz. During an instruction or data primary cache refill, the secondary cache can provide a 64-bit datum every cycle following the initial three cycle latency for a peak bandwidth of 2.4 GB per second. For applications requiring even higher performance, the RM7000 also has a direct interface to a large external tertiary cache.

#### 4.17 Instruction Cache

The RM7000 has an integrated 16 KB, four-way set associative instruction cache and, even though instruction address translation is done in parallel with the cache access, the combination of 4-way set associativity and 16 KB size results in a cache which is virtually indexed and physically tagged. Since the effective physical index eliminates the potential for virtual aliases in the cache, it is possible that some operating system code can be simplified vis-a-vis the RM5200 Family, R5000 and R4000 class processors.

The data array portion of the instruction cache is 64 bits wide and protected by word parity while the tag array holds a 24-bit physical address, 14 housekeeping bits, a valid bit, and a single bit of parity protection.

By accessing 64 bits per cycle, the instruction cache is able to supply two instructions per cycle to the superscalar dispatch unit. For signal processing, graphics, and other numerical code sequences where a floating-point load or store and a floating-point computation instruction are being issued together in a loop, the entire bandwidth available from the instruction cache will be consumed by instruction issue. For typical integer code mixes, where instruction dependencies and other resource constraints restrict the achievable parallelism, the extra instruction cache bandwidth is used to fetch both the taken and non-taken branch paths to minimize the overall penalty for branches.

A 32-byte (eight instruction) line size is used to maximize the communication efficiency between the instruction cache and the secondary cache, tertiary cache, or memory system.

The RM7000 is the first MIPS RISC microprocessor to support cache locking on a per line basis. The contents of each line of the cache can be *locked* by setting a bit in the Tag. Locking the line prevents its contents from being overwritten by a subsequent cache miss. Refill will occur only into unlocked cache lines. This mechanism allows the programmer to lock critical code into the cache thereby guaranteeing deterministic behavior for the locked code sequence.

#### 4.18 Data Cache

The RM7000 has an integrated 16 KB, four-way set associative data cache, and even though data address translation is done in parallel with the cache access, the combination of 4-way set

associativity and 16 KB size results in a cache which is physically indexed and physically tagged. Since the effective physical index eliminates the potential for virtual aliases in the cache, it is possible that some operating system code can be simplified vis-a-vis the RM5200 Family, R5000 and R4000 class processors.

The data cache is non-blocking; that is, a miss in the data cache will not necessarily stall the processor pipeline. As long as no instruction is encountered which is dependent on the data reference which caused the miss, the pipeline will continue to advance. Once there are two cache misses outstanding, the processor will stall if it encounters another load or store instruction.

A 32-byte (eight word) line size is used to maximize the communication efficiency between the data cache and the secondary cache, tertiary cache, or memory system.

The data array portion of the data cache is 64 bits wide and protected by byte parity while the tag array holds a 24-bit physical address, three housekeeping bits, a two bit cache state field, and has two bits of parity protection.

The normal write policy is write-back, which means that a store to a cache line does not immediately cause memory to be updated. This increases system performance by reducing bus traffic and eliminating the bottleneck of waiting for each store operation to finish before issuing a subsequent memory operation. Software can, however, select write-through on a per-page basis when appropriate, such as for frame buffers. Cache protocols supported for the data cache are:

#### 1. Uncached

Reads to addresses in a memory area identified as uncached will not access the cache. Writes to such addresses will be written directly to main memory without updating the cache.

#### 2. Write-back

Loads and instruction fetches will first search the cache, reading the next memory hierarchy level only if the desired data is not cache resident. On data store operations, the cache is first searched to determine if the target address is cache resident. If it is resident, the cache contents will be updated, and the cache line marked for later write-back. If the cache lookup misses, the target line is first brought into the cache and then the write is performed as above.

#### 3. Write-through with write allocate

Loads and instruction fetches will first search the cache, reading from memory only if the desired data is not cache resident; write-through data is never cached in the secondary or tertiary caches. On data store operations, the cache is first searched to determine if the target address is cache resident. If it is resident, the primary cache contents will be updated and main memory will also be written leaving the *write-back* bit of the cache line unchanged; no writes will occur into the secondary or tertiary. If the cache lookup misses, the target line is first brought into the cache and then the write is performed as above.

#### 4. Write-through without write allocate

Loads and instruction fetches will first search the cache, reading from memory only if the desired data is not cache resident; write-through data is never cached in the secondary or tertiary caches. On data store operations, the cache is first searched to determine if the target address is cache resident. If it is resident, the cache contents will be updated and main memory will also be written leaving the *write-back* bit of the cache line unchanged; no writes will

occur into the secondary or tertiary. If the cache lookup misses, then only main memory is written.

5. Fast Packet Cache<sup>TM</sup> (Write-back with secondary and tertiary bypass)

Loads and instruction fetches first search the primary cache, reading from memory only if the desired data is not resident; the secondary and tertiary are not searched. On data store operations, the primary cache is first searched to determine if the target address is resident. If it is resident, the cache contents are updated, and the cache line marked for later write-back. If the cache lookup misses, the target line is first brought into the cache and then the write is performed as above.

Associated with the Data Cache is the *store buffer*. When the RM7000 executes a STORE instruction, this single-entry buffer gets written with the store data while the tag comparison is performed. If the tag matches, then the data is written into the Data Cache in the next cycle that the Data Cache is not accessed (the next non-load cycle). The store buffer allows the RM7000 to execute a store every processor cycle and to perform back-to-back stores without penalty. In the event of a store immediately followed by a load to the same address, a combined merge and cache write will occur such that no penalty is incurred.

#### 4.19 Secondary Cache

The RM7000 has an integrated 256 KB, four-way set associative, block write-back secondary cache. The secondary has the same line size as the primaries, 32 bytes, is logically 64-bits wide matching the system interface and primary widths, and is protected with doubleword parity. The secondary tag array holds a 20-bit physical address, two housekeeping bits, a three bit cache state field, and two parity bits.

By integrating a secondary cache, the RM7000 is able to dramatically decrease the latency of a primary cache miss without dramatically increasing the number of pins and the amount of power required by the processor. From a technology point of view, integrating a secondary cache maximally leverages CMOS semiconductor technology by using silicon to build the structures that are most amenable to silicon technology; silicon is being used to build very dense, low power memory arrays rather than large power hungry I/O buffers.

Further benefits of an integrated secondary are flexibility in the cache organization and management policies that are not practical with an external cache. Two previously mentioned examples are the 4-way associativity and write-back cache protocol.

A third management policy for which integration affords flexibility is cache hierarchy management. With multiple levels of cache, it is necessary to specify a policy for dealing with cases where two cache lines at level n of the hierarchy would, if possible, be sharing an entry in level n+1 of the hierarchy. The policy followed by the RM7000 is motivated by the desire to get maximum cache utility and results in the RM7000 allowing entries in the primaries which do not necessarily have a corresponding entry in the secondary; the RM7000 does not force the primaries to be a subset of the secondary. For example, if primary cache line A is being filled and a cache line already exists in the secondary for primary cache line B at the location where primary A's line would reside then that secondary entry will be replaced by an entry corresponding to primary cache line A and no action will occur in the primary for cache line B. This operation will create the aforementioned scenario where the primary cache line which initially had a corresponding

secondary entry will no longer have such an entry. Such a primary line is called an *orphan*. In general, cache lines at level n+1 of the hierarchy are called *parents* of level n's *children*.

Another RM7000 cache management optimization occurs for the case of a secondary cache line replacement where the secondary line is dirty and has a corresponding dirty line in the primary. In this case, since it is permissible to leave the dirty line in the primary, it is not necessary to write the secondary line back to main memory. Taking this scenario one step further, a final optimization occurs when the aforementioned dirty primary line is replaced by another line and must be written back, in this case, it will be written directly to memory bypassing the secondary cache.

#### 4.20 Secondary Caching Protocols

Unlike the primary data cache, the secondary cache supports only uncached and block write-back. As noted earlier, cache lines managed with either of the write-through protocols will not be placed in the secondary cache. A new caching attribute, write-back with secondary and tertiary bypass, allows the secondary, and the tertiary if present, to be bypassed entirely. When this attribute is selected, the secondary and tertiary will not be filled on load misses and will not be written on dirty write-backs from the primary.

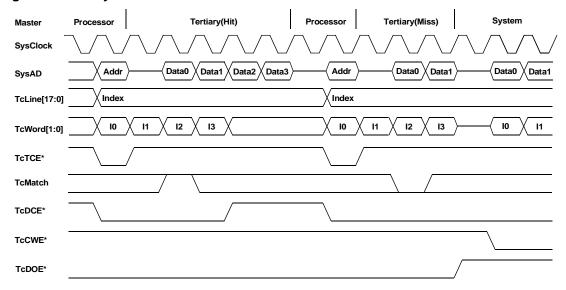

## 4.21 Tertiary Cache

Like the RM5270, RM5271 and R5000, the RM7000 has direct support for an external cache. In the case of the RM527x chips this is a secondary cache whereas for the RM7000 this cache becomes a level-3, or tertiary cache. The tertiary cache is direct mapped and block write-through with byte parity protection for data. The RM7000 tertiary operates identical to the secondary of the RM527x and R5000 while supporting additional size increments to 4M and 8M byte caches.

The tertiary interface uses the **SysAD** bus for data and tags while providing a separate bus, **TcLine**, for addresses, and a handful of tertiary specific control signals (for the complete set, see Pin Listing).

A tertiary read looks nearly identical to a standard processor read except that the tag chip enable signal, **TcTCE\***, is asserted concurrently with **ValidOut\*** and **Release\***, initiating a tag probe and indicating to the external controller that a tertiary cache access is being performed. As a result, the external controller monitors the tertiary hit signal, **TcMatch**, and if a hit is indicated the controller will abort the memory read and will refrain from acquiring control of the system interface. Along with **TcTCE\***, the processor also asserts the tag data enable signal, **TcTDE\***, which causes the tag RAMs to latch the **SysAD** address internally for use as the replacement tag if a cache miss occurs.

On a tertiary miss, a refill is accomplished with a two signal handshake between the data output enable signal, **TcDOE**\*, which is deasserted by the controller and the tag and data write enable signal, **TcCWE**\*, which is asserted by the processor. Figure 7 illustrates a tertiary cache hit followed by a miss.

Other capabilities of the tertiary interface include block write, tag invalidate, and tag probe. For details of these transactions as well as detailed timing waveforms for all the tertiary transactions, see the R5000 or RM7000 Bus Interface Specifications. The tertiary cache tag can easily be implemented with standard components such as the Motorola MCM69T618.

The RM7000 cache attributes for the instruction, data, internal secondary, and optional external tertiary caches are summarized in Table 6.

**Table 6 Cache Attributes**

| Attribute               | Instruction           | Data                                                                 | Secondary                   | Tertiary                                |

|-------------------------|-----------------------|----------------------------------------------------------------------|-----------------------------|-----------------------------------------|

| Size                    | 16KB                  | 16KB                                                                 | SKB 256KB                   |                                         |

| Associativity           | 4-way                 | 4-way                                                                | 4-way                       | direct mapped                           |

| Replacement Algorithm.  | cyclic                | cyclic                                                               | cyclic                      | direct replacement                      |

| Line size               | 32 byte               | 32 byte                                                              | 32 byte                     | 32 byte                                 |

| Index                   | vAddr <sub>110</sub>  | vAddr <sub>110</sub> pAddr <sub>150</sub>                            |                             | pAddr <sub>220</sub>                    |

| Tag                     | pAddr <sub>3512</sub> | pAddr <sub>3512</sub>                                                | pAddr <sub>3516</sub>       | pAddr <sub>3519</sub>                   |

| Write policy            | n.a.                  | write-back, write-<br>through                                        | block write-back,<br>bypass | block write-through, bypass             |

| read policy             | n.a.                  | non-blocking (2 non-blocking (data outstanding) only, 2 outstanding) |                             | non-blocking (data only, 2 outstanding) |

| read order              | critical word first   | critical word first                                                  | critical word first         | critical word first                     |

| write order             | NA                    | sequential                                                           | sequential sequential       |                                         |

| miss restart following: | complete line         | first double (if n.a. n.a waiting for data)                          |                             | n.a.                                    |

| Parity                  | per word              | per byte                                                             | per doubleword              | per byte                                |

## 4.22 Cache Locking

The RM7000 allows critical code or data fragments to be locked into the primary and secondary caches. The user has complete control over what locking is performed with cache line granularity. For instruction and data fragments in the primaries, locking is accomplished by setting either or both of the cache lock enable bits in the CP0 ECC register, specifying the set via a field in the CP0 ECC register, and then executing either a load instruction or a Fill\_I cache operation for data or instructions respectively. Only two sets are lockable within each cache: set A and set B. Locking within the secondary works identically to the primaries using a separate secondary lock enable bit and the same set selection field. As with the primaries, only two sets are lockable: sets A and B. Table 7 summarizes the cache locking capabilities.

Table 7 Cache Locking Control

| Cache     | Lock Enable | Set Select  | Activate   |

|-----------|-------------|-------------|------------|

| Primary I | ECC[27]     | ECC[28]=0→A | Fill_l     |

|           |             | ECC[28]=1→B |            |

| Primary D | ECC[26]     | ECC[28]=0→A | Load/Store |

|           |             | ECC[28]=1→B |            |

| Secondary | ECC[25]     | ECC[28]=0→A | Fill_I or  |

|           |             | ECC[28]=1→B | Load/Store |

## 4.23 Cache Management

To improve the performance of critical data movement operations in the embedded environment, the RM7000 significantly improves the speed of operation of certain critical cache management

operations vis-a-vis the R5000 and R4000 families. In particular, the speed of the Hit-Writeback-Invalidate and Hit-Invalidate cache operations has been improved in some cases by an order of magnitude over that of the earlier families. Table 8 compares the RM7000 with the R4000 and R5000 processors.

Table 8 Penalty Cycles

|                              |           | Penalty |             |  |

|------------------------------|-----------|---------|-------------|--|

| Operation                    | Condition | RM7000  | R4000/R5000 |  |

| Hit-Writeback-<br>Invalidate | Miss      | 0       | 7           |  |

|                              | Hit-Clean | 3       | 12          |  |

|                              | Hit-Dirty | 3+n     | 14+n        |  |

| Hit-Invalidate               | Miss      | 0       | 7           |  |

|                              | Hit       | 2       | 9           |  |

For the Hit-Dirty case of Hit-Writeback-Invalidate, if the writeback buffer is full from some previous cache eviction then n is the number of cycles required to empty the writeback buffer. If the buffer is empty then n is zero.

The penalty value is the number of processor cycles beyond the one cycle required to issue the instruction that is required to implement the operation.

#### 4.24 Primary Write Buffer

Writes to secondary cache or external memory, whether cache miss write-backs or stores to uncached or write-through addresses, use the integrated primary write buffer. The write buffer holds up to four 64-bit address and data pairs. The entire buffer is used for a data cache write-back and allows the processor to proceed in parallel with memory update. For uncached and write-through stores, the write buffer significantly increases performance by decoupling the **SysAD** bus transfers from the instruction execution stream.

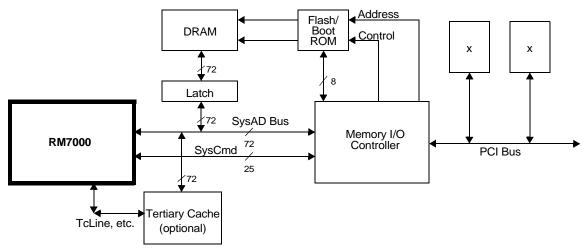

## 4.25 System Interface

The RM7000 provides a high-performance 64-bit system interface which is compatible with the RM5200 Family and R5000. Unlike the R4000 and R5000 family processors which provide only an integral multiplication factor between SysClock and the pipeline clock, the RM7000 also allows half-integral multipliers, thereby providing greater granularity in the designers choice of pipeline and system interface frequencies.

The interface consists of a 64-bit Address/Data bus with 8 check bits and a 9-bit command bus. In addition, there are ten handshake signals and ten interrupt inputs. The interface has a simple timing specification and is capable of transferring data between the processor and memory at a peak rate of 1000 MB/sec with a 125 MHz SysClock.

Figure 8 shows a typical embedded system using the RM7000. This example shows a system with a bank of DRAMs, an optional tertiary cache, and an interface ASIC which provides DRAM control as well as an I/O port.

Figure 8 Typical Embedded System Block Diagram

#### 4.26 System Address/Data Bus

The 64-bit System Address Data (**SysAD**) bus is used to transfer addresses and data between the RM7000 and the rest of the system. It is protected with an 8-bit parity check bus, **SysADC**.

The system interface is configurable to allow easy interfacing to memory and I/O systems of varying frequencies. The data rate and the bus frequency at which the RM7000 transmits data to the system interface are programmable via boot time mode control bits. Also, the rate at which the processor receives data is fully controlled by the external device. Therefore, either a low cost interface requiring no read or write buffering or a faster, high-performance interface can be designed to communicate with the RM7000. Again, the system designer has the flexibility to make these price/performance trade-offs.

## 4.27 System Command Bus

The RM7000 interface has a 9-bit System Command (SysCmd) bus. The command bus indicates whether the SysAD bus carries an address or data. If the SysAD bus carries an address, then the SysCmd bus also indicates what type of transaction is to take place (for example, a read or write). If the SysAD bus carries data, then the SysCmd bus also gives information about the data (for example, this is the last data word transmitted, or the data contains an error). The SysCmd bus is bidirectional to support both processor requests and external requests to the RM7000. Processor requests are initiated by the RM7000 and responded to by an external device. External requests are issued by an external device and require the RM7000 to respond.

The RM7000 supports one to eight byte and 32-byte block transfers on the **SysAD** bus. In the case of a sub-doubleword transfer, the 3 low-order address bits give the byte address of the transfer, and the **SysCmd** bus indicates the number of bytes being transferred.

## 4.28 Handshake Signals

There are ten handshake signals on the system interface. Two of these, **RdRdy\*** and **WrRdy\***, are used by an external device to indicate to the RM7000 whether it can accept a new read or write

transaction. The RM7000 samples these signals before deasserting the address on read and write requests.

**ExtRqst\*** and **Release\*** are used to transfer control of the **SysAD** and **SysCmd** buses from the processor to an external device. When an external device needs to control the interface, it asserts **ExtRqst\***. The RM7000 responds by asserting **Release\*** to release the system interface to slave state.

**PRqst\*** and **PAck\*** are used to transfer control of the **SysAD** and **SysCmd** buses from the external agent to the processor. These two pins are new to the interface relative to the RM52x, R4000 and R5000 families and have been added to support multiple outstanding reads and ultimately the non-blocking caches. When the processor needs to reacquire control of the interface, it asserts PRqst\*. The external device responds by asserting PAck\* to return control of the interface to the processor.

**RspSwap\*** is also a new pin and is used by the external agent to tell the processor when it is returning data out of order; i.e., when there are two outstanding reads, the external agent asserts **RspSwap\*** when it is going to return the data for the second read before it returns the data for the first read. **RspSwap\*** must be asserted by the external agent two cycles ahead of when it presents data so that the processor has time to switch to the correct address for writes into the tertiary cache.

**RdType** is the last new pin on the interface. **RdType** indicates whether a read is an instruction read or a data read. When asserted the reference is an instruction read, when deasserted it is a data read. **RdType** is only valid during valid address cycles.

**ValidOut\*** and **ValidIn\*** are used by the RM7000 and the external device respectively to indicate that there is a valid command or data on the **SysAD** and **SysCmd** buses. The RM7000 asserts **ValidOut\*** when it is driving these buses with a valid command or data, and the external device drives **ValidIn\*** when it has control of the buses and is driving a valid command or data.

## 4.29 System Interface Operation

Unlike the R4000 and R5000 processor families, to support the non-blocking caches and data Prefetch instructions, the RM7000 allows two outstanding reads. An external device may respond to read requests in whatever order it chooses by using the response order indicator pin **RspSwap\***. No more than two read requests will be submitted to the external device. Other than support for two outstanding reads, operation of the system interface is identical to that of the RM5270, RM5271 and R5000. Support for multiple outstanding reads can be enabled or disabled via a boottime mode bit.

The RM7000 can issue read and write requests to an external device, while an external device can issue null and write requests to the RM7000.

For processor reads, the RM7000 asserts **ValidOut\*** and simultaneously drives the address and read command on the **SysAD** and **SysCmd** buses. If the system interface has **RdRdy\*** asserted, then the processor tristates its drivers and releases the system interface to slave state by asserting **Release\***. The external device can then begin sending data to the RM7000.

Figure 9 shows a processor block read request and the external agent read response for a system with either no tertiary cache or a transaction where the tertiary is being bypassed.

Figure 9 Processor Block Read

The read latency is four cycles (**ValidOut\*** to **ValidIn\***), and the response data pattern is DDxxDD. Figure 10 shows a processor block write where the processor was programmed with write-back data rate boot code 2, or DDxxDDxx.

Finally, Figure 11 shows a typical sequence resulting in two outstanding reads both with initial tertiary cache accesses, as explained in the following sequence.

- 1. The processor issues a read which misses in the tertiary cache.

- 2. The external agent takes control of the bus in preparation for returning data to the processor.

- 3. The processor encounters another internal cache miss and therefore asserts **PRqst\*** in order to regain control of the bus.

- 4. The external agent pulses **PAck\***, returning control of the bus to the processor.

- 5. The processor issues a read for the second miss.

- 6. The second cycle also misses in the tertiary.

- 7. The **RspSwap\*** pin is asserted to denote the out of order response. Not shown in the figure is the completion of the data transfer for the second miss, or any of the data transfer for the first miss.

- 8. The external agent retakes control of the bus and begins returning data (out of order) for the second miss to the processor.

#### 4.30 Data Prefetch

The RM7000 is the first PMC-Sierra design to support the MIPS IV integer data prefetch (PREF) and floating-point data prefetch (PREFX) instructions. These instructions are used by the compiler or by an assembly language programmer when it is known or suspected that an upcoming data reference is going to miss in the cache. By appropriately placing a prefetch instruction, the memory latency can be hidden under the execution of other instructions. If the execution of a prefetch instruction would cause a memory management or address error exception the prefetch is treated as a NOP.

The "Hint" field of the data prefetch instruction is used to specify the action taken by the instruction. The instruction can operate normally (that is, fetching data as if for a load operation) or it can allocate and fill a cache line with zeroes on a primary data cache miss.

#### 4.31 Enhanced Write Modes

Like previous MIPS processor designs, the RM7000 implements two enhancements to the original R4000 write mechanism: Write Reissue and Pipeline Writes. In write reissue mode, a write rate of one write every two bus cycles can be achieved. A write issues if **WrRdy\*** is asserted two cycles earlier and is still asserted during the issue cycle. If it is not still asserted then the last write will reissue. Pipelined writes have the same two bus cycle write repeat rate, but can issue one additional write following the deassertion of **WrRdy\***.

#### 4.32 External Requests

The RM7000 can respond to certain requests issued by an external device. These requests take one of two forms: *Write* requests and *Null* requests. An external device executes a write request when it wishes to update one of the processors writable resources such as the internal interrupt register. A null request is executed when the external device wishes the processor to reassert ownership of the processor external interface. Typically a null request will be executed after an external device, that has acquired control of the processor interface via **ExtRqst\***, has completed an independent transaction between itself and system memory in a system where memory is connected directly to the **SysAD** bus. Normally this transaction would be a DMA read or write from the I/O system.

#### 4.33 Test/Breakpoint Registers

To increase both observability and controllability of the processor thereby easing hardware and software debugging, a pair of Test/Break-point, or Watch, registers, Watch1 and Watch2, have been added to the RM7000. Each Watch register can be separately enabled to watch for a load address, a store address, or an instruction address. All address comparisons are done on physical addresses. An associated register, Watch Mask, has also been added so that either or both of the Watch registers can compare against an address range rather than a specific address. The range granularity is limited to a power of two.

When enabled, a match of either Watch register results in an exception. If the Watch is enabled for a load or store address then the exception is the Watch exception as defined for the R4000 with Cause exception code twenty-three. If the Watch is enabled for instruction addresses then a newly defined Instruction Watch exception is taken and the Cause code is sixteen. The Watch register which caused the exception is indicated by Cause bits 25..24. Table 9 summarizes a Watch operation.

Table 9 Watch Control Register

| Register   | Bit Field/Function |      |       |       |                    |                    |  |  |

|------------|--------------------|------|-------|-------|--------------------|--------------------|--|--|

|            | 63                 | 62   | 61    | 60:36 | 35:2               | 1:0                |  |  |

| Watch1, 2  | Store              | Load | Instr | 0     | Addr               | 0                  |  |  |

|            | 31:2               |      | 1     | 0     |                    |                    |  |  |

| Watch Mask | Mask               |      |       |       | Mask<br>Watch<br>2 | Mask<br>Watch<br>1 |  |  |

#### 4.34 Performance Counters

Like the Test/Break-point capability described above, the Performance Counter feature has been added to improve the observability and controllability of the processor thereby easing system debug and, especially in the case of the performance counters, easing system tuning.

The Performance Counter feature is implemented using two new CP0 registers, PerfCount and PerfControl. The PerfCount register is a 32-bit writable counter which causes an interrupt when bit 31 is set. The PerfControl register is a 32-bit register containing a five bit field which selects one of twenty-two event types as well as a handful of bits which control the overall counting function. Note that only one event type can be counted at a time and that counting can occur for user code, kernel code, or both. The event types and control bits are listed in Table 10.

**Table 10 Performance Counter Control**

| PerfControl |                                                                                     |

|-------------|-------------------------------------------------------------------------------------|

| Field       | Description                                                                         |

| 40          | Event Type                                                                          |

|             | 00: Clock cycles                                                                    |

|             | 01: Total instructions issued                                                       |

|             | 02: Floating-point instructions issued                                              |

|             | 03: Integer instructions issued                                                     |

|             | 04: Load instructions issued                                                        |

|             | 05: Store instructions issued                                                       |

|             | 06: Dual issued pairs                                                               |

|             | 07: Branch prefetches                                                               |

|             | 08: External Cache Misses                                                           |

|             | 09: Stall cycles                                                                    |

|             | 0A: Secondary cache misses                                                          |

|             | 0B: Instruction cache misses                                                        |

|             | 0C: Data cache misses                                                               |

|             | 0D: Data TLB misses                                                                 |

|             | 0E: Instruction TLB misses                                                          |

|             | 0F: Joint TLB instruction misses                                                    |

|             | 10: Joint TLB data misses                                                           |

|             | 11: Branches taken                                                                  |

|             | 12: Branches issued                                                                 |

|             | 13: Secondary cache writebacks                                                      |

|             | 14: Primary cache writebacks                                                        |

|             | 15: Dcache miss stall cycles (cycles where both cache miss tokens taken and a third |

|             | address is requested)                                                               |

|             | 16: Cache misses                                                                    |

|             | 17: FP possible exception cycles                                                    |

|             | 18: Slip Cycles due to multiplier busy                                              |

|             | 19: Coprocessor 0 slip cycles                                                       |

|             | 1A: Slip cycles doe to pending non-blocking loads                                   |

|             | 1B: Write buffer full stall cycles                                                  |

|             | 1C: Cache instruction stall cycles                                                  |

|             | 1D: Multiplier stall cycles                                                         |

|             | 1E: Stall cycles due to pending non-blocking loads - stall start of exception       |

| 75          | Reserved (must be zero)                                                             |

| 8           | Count in Kernel Mode                                                                |

|             | 0: Disable                                                                          |

|             | 1: Enable                                                                           |

| 9           | Count in User Mode                                                                  |

|             | 0: Disable                                                                          |

|             | 1: Enable                                                                           |

| 10          | Count Enable                                                                        |

|             | 0: Disable                                                                          |

|             | 1: Enable                                                                           |

| 24 44       | ****                                                                                |

| 3111        | Reserved (must be zero)                                                             |

The performance counter interrupt will only occur when interrupts are enabled in the *Status* register, IE=1, and *Interrupt Mask* bit 13 (*IM[13]*) of the coprocessor 0 interrupt control register is not set.

Since the performance counter can be set up to count clock cycles, it can be used as either a) a second timer or b) a watchdog interrupt. A watchdog interrupt can be used as an aid in debugging system or software "hangs." Typically the software is setup to periodically update the count so that no interrupt will occur. When a hang occurs the interrupt ultimately triggers thereby breaking free from the hang-up.

#### 4.35 Interrupt Handling

In order to provide better real time interrupt handling, the RM7000 provides an extended set of hardware interrupts each of which can be separately prioritized and separately vectored.

In addition to the six external interrupt pins available on the R4000 and R5000 family processors, the RM7000 provides four more interrupt pins for a total of ten external interrupts.

As described above, the performance counter is also a hardware interrupt source, **INT[13]**. Also, whereas the R4000 and R5000 family processors map the timer interrupt onto **INT[7]**, the RM7000 provides a separate interrupt, **INT[12]**, for this purpose freeing **INT[7]** for use as a pure external interrupt.

All of these interrupts, **INT[13..0]**, the Performance Counter, and the Timer, have corresponding interrupt mask bits, *IM[13..0]*, and interrupt pending bits, *IP[13..0]*, in the Status, Interrupt Control, and Cause registers. The bit assignments for the Interrupt Control and Cause registers are shown in Table 11 and Table 12. The Status register has not changed from the RM5200 Family and R5000, and is not shown.

The *IV* bit in the Cause register is the global enable bit for the enhanced interrupt features. If this bit is clear then interrupt operation is compatible with the RM5200 Family and R5000. Although not related to the interrupt mechanism, note that the *W1* and *W2* bits indicate which Watch register caused a particular Watch exception.

In the Interrupt Control register, the interrupt vector spacing is controlled by the Spacing field as described below. The *Interrupt Mask* field (*IM[15..8]*) contains the interrupt mask for interrupts eight through thirteen. *IM[15..14]* are reserved for future use. The *Timer Exclusive* (*TE*) bit if set moves the Timer interrupt to *INT[12]*. If clear, the Timer interrupt will be or'ed into *INT[7]* as on the R5000.

The Interrupt Control register uses *IM13* to enable the Performance Counter Control.

Priority of the interrupts is set via two new coprocessor 0 registers called Interrupt Priority Level Lo (IPLLO) and Interrupt Priority Level Hi (IPLHI).

#### Table 11 Cause Register

| 31 | 30 | 29,28 | 27 | 26 | 25 | 24 | 238     | 7 | 62  | 0,1 |

|----|----|-------|----|----|----|----|---------|---|-----|-----|

| BD | 0  | CE    | 0  | W2 | W1 | IV | IP[150] | 0 | EXC | 0   |

#### **Table 12 Interrupt Control Register**

| 3116 | 158     | 7  | 65 | 40      |

|------|---------|----|----|---------|

| 0    | IM[158] | TE | 0  | Spacing |

#### Table 13 IPLLO Register

| 3128 | 2724 | 2320 | 1916 | 1512 | 118  | 74   | 30   |

|------|------|------|------|------|------|------|------|

| IPL7 | IPL6 | IPL5 | IPL4 | IPL3 | IPL2 | IPL1 | IPL0 |

#### Table 14 IPLHI Register

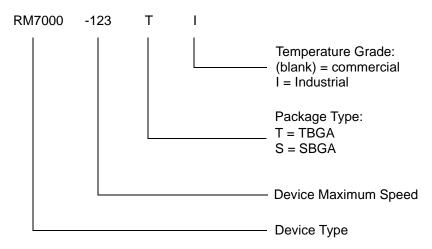

| 3128 | 2724 | 2320  | 1916  | 1512  | 118   | 74   | 30   |