# **PO-005**

## FIBRE OPTIC RECEIVER TO 10 BIT VIDEO

The PO-005 is a stand alone solution for single channel fibre optic to 10 bit parallel video. Using the Gennum chipset the module provides EDH insertion for SMPTE 259M compliant signals. The module can successfully receive a serial digital signal over a range of up to 7km. The PO-005 compliments the PI-005 10 bit parallel video to optic fibre transmitter.

#### **INPUT**

**Optical wavelength** 1270nm to 1380nm

Optical input sensitivity -29dBm for BER <1x10E-12 Optical input overload -14dBm for BER <1x10E-12

#### **OUTPUTS**

Output signal CCIR Rec. 656 10 bit parallel video

#### **SUPPLY**

Power: 5V

**Current:** 300mA max

#### **EDH OPTION**

| <b>Indications:</b> | EDH - Error detected Here    | (Note 1) |

|---------------------|------------------------------|----------|

|                     | EDA - Error detected already | (Note 1) |

|                     | UES - Unknown Error status   | (Note 1) |

| <b>Controls:</b>    | TRS - Insert:                | (Note 2) |

|                     | Bypass Mode:                 | (Note 2) |

- **Note 1.** These are accessible only through the serial interface SCL and SDA.

- Note 2. These are available only through the I/O interface see connector for details.

#### **CONNECTORS**

**Input** ST multimode

Output 48 PIN Z-PAC 4 row x 12 on 2mm pitch

**INDICATORS** Carrier Detected (Green) LED

#### **Connector Pinout**

| 1   | 2   | 3    | 4    | 5    | 6   | 7     | 8      | 9      | 10  | 11  | 12  |

|-----|-----|------|------|------|-----|-------|--------|--------|-----|-----|-----|

| +5V | CLK | D0   | D1   | D2   | D3  | D4    | D5     | D6     | D7  | D8  | D9  |

| 13  | 14  | 15   | 16   | 17   | 18  | 19    | 20     | 21     | 22  | 23  | 24  |

| +5V | +5V | A0   | A1   | SDA  | SCL | RESET | TRS    | BYPASS | GND | GND | GND |

|     |     |      |      |      |     |       | INSERT | EDH    |     |     |     |

| 25  | 26  | 27   | 28   | 29   | 30  | 31    | 32     | 33     | 34  | 35  | 36  |

| NC  | NC  | NC   | NC   | NC   | NC  | NC    | NC     | NC     | NC  | NC  | ID3 |

| 37  | 38  | 39   | 40   | 41   | 42  | 43    | 44     | 45     | 46  | 47  | 48  |

| IO8 | IO9 | IO10 | IO11 | IO12 | NC  | NC    | NC     | NC     | ID0 | ID1 | ID2 |

RESET When taken low resets the internal circuitry of the serial digital input processor.

BYPASS EDH Internally pulled high:

When high EDH packet is passed through unaltered.

TRS INSERT Internally pulled high:

Pull low to disable TRS Blanking, ITU-601Clipping & TRS Insertion.

D0 to D9 Parallel Data Bus D0 LSB, D9 MSB

CLK Parallel Data clock

A0,A1 Address lines to modify I<sup>2</sup>c bus address.

SCL,SDA I<sup>2</sup>c data and clock lines

ID0,ID1,ID2,ID3 Card type identification code.

IO8-IO12 Do not connect.

### Card Type Identification code.

| CARD TYPE | ID3 | ID2 | ID1 | ID0 |

|-----------|-----|-----|-----|-----|

| PI-005    | 0V  | +5V | 0V  | 0V  |

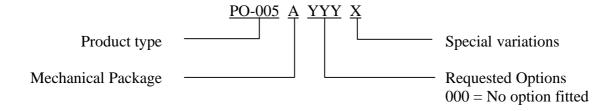

### **Ordering codes**

Note: This item is **NOT** aqueous washable.

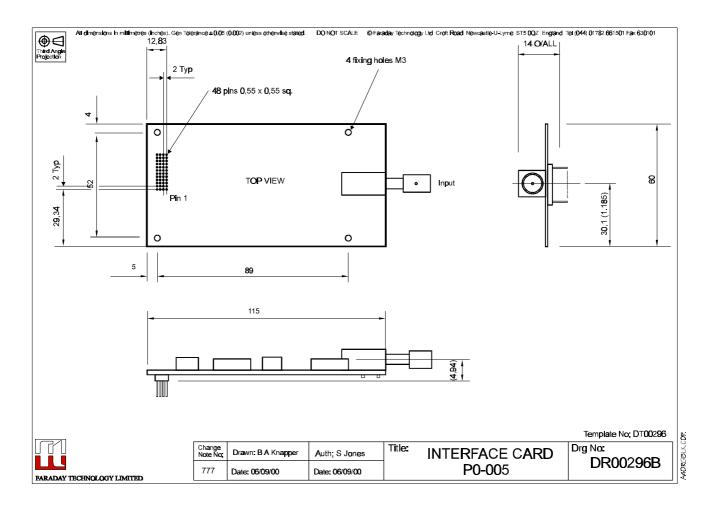

## PACKAGE DETAIL