# High Performance GTL Termination Network for Socket 370 Processors

#### **Features**

- 24 terminations in a single package

- 5 chip solution for all 119 GTL terminations

- High speed termination network

- · Center ground pin placement reduces ground bounce and eases board layout

- Very low cross-talk

- Saves board space and reduces assembly cost

### **Applications**

- · High Performance Servers

- High Performance Desk Top Systems

- Intel Celeron<sup>™</sup> and Pentium<sup>™</sup> CPUs

### **Application Information**

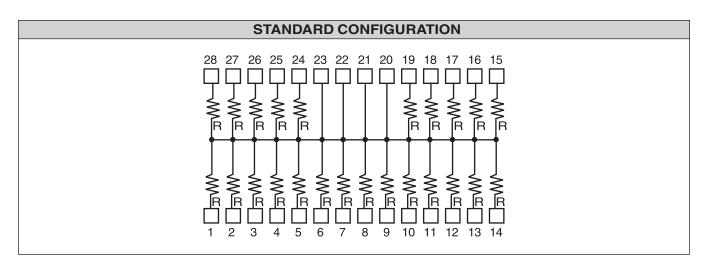

High speed microprocessors demand unique, high speed bus termination. The PACGTL Termination Network provides 24 terminations per package and meets the requirements for high speed terminations. The termination resistor values are 56 or 120 ohms each. Five devices provide the necessary terminations for the 32-bit address bus, 64-bit data bus, and the control of status signals. Potential board layout solutions are included in this datasheet.

This termination network provides high performance. high reliability, and low cost through manufacturing

efficiency. The termination resistor elements are fabricated using state-of-the-art thin film manufacturing. This integrated solution is silicon-based and has the same reliability characteristics of today's microprocessor products. The thin film resistors have very high stability over temperature, over applied voltage, and over life. In addition, the QSOP (SSOP) industry standard packaging is easy to handle in manufacturing and yields high reliability similar to other semiconductor components.

| STANDARD PART ORDERING INFORMATION |       |                      |  |  |

|------------------------------------|-------|----------------------|--|--|

| Package                            |       | Ordering Part Number |  |  |

| Pins                               | Style | Part Marking         |  |  |

| 28                                 | QSOP  | PAC560GTL            |  |  |

| 28                                 | QSOP  | PAC121GTL            |  |  |

When placing an order please specify desired shipping: Tubes or Tage & Reel.

All trademarks are the property of their respective holders. P/Active® is a registered trademark and PACTM is a trademark of California Micro Devices.

C0970500

## **CALIFORNIA MICRO DEVICES**

| STANDARD VALUES                 |                           |  |  |  |

|---------------------------------|---------------------------|--|--|--|

| Resistor (R)                    | $56\Omega$ or $120\Omega$ |  |  |  |

| Absolute Tolerance (R)          | ±5%                       |  |  |  |

| TCR                             | ±150ppM                   |  |  |  |

| Operating Temperature Range     | 0°C to 70°C               |  |  |  |

| Max Package Power Rating (70°C) | 1W                        |  |  |  |

| Minimum Insulation Resistance   | 10,000MΩ                  |  |  |  |

| Cross-talk*                     | 4%                        |  |  |  |

| <b>R</b> (Ω) | Code | Power Rating/<br>Resistor |

|--------------|------|---------------------------|

| 56           | 560  | 100mW                     |

| 120          | 121  | 40mW                      |

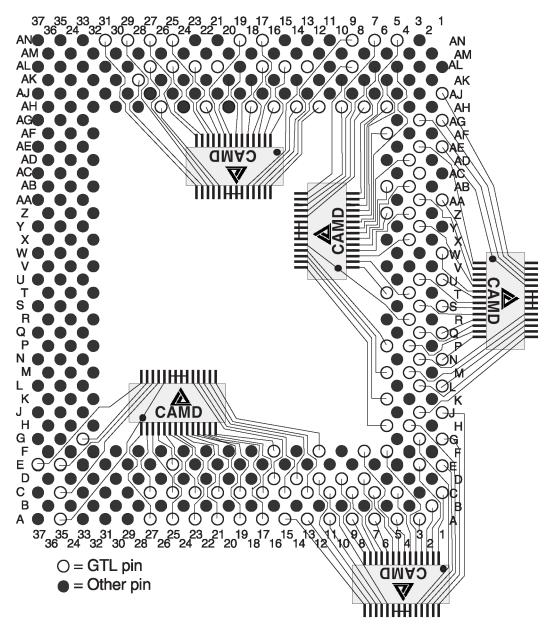

### RECOMMENDED LAYOUT FOR SOCKET 370 (OPTION A) FOR CELERON™ AND MENDOCINO™ CPUs

### 11-mil track pitch, single layer

Note: This option requires 1 metal layer in board routing for all 119 GTL termination lines.

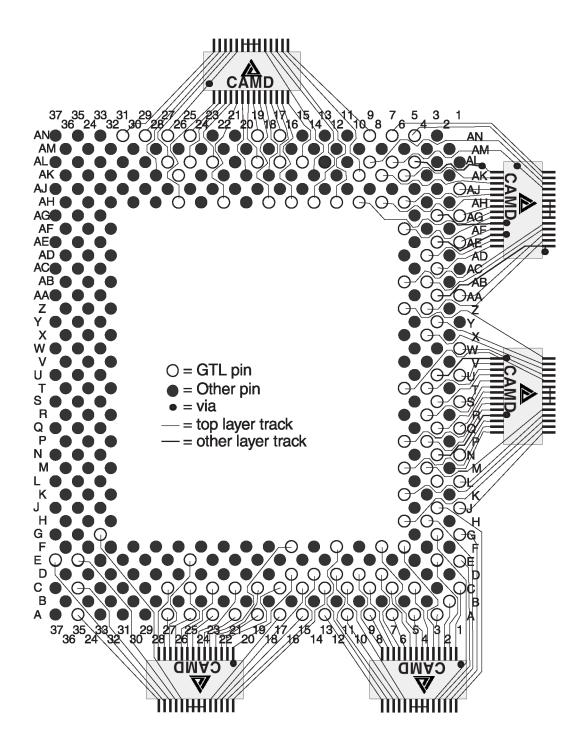

### RECOMMENDED LAYOUT FOR SOCKET 370 (OPTION B) FOR CELERON™ AND MENDOCINO™ CPUs

Note: This option requires 2 metal layers in board routing for all 119 GTL termination lines. Please note that the second layer only uses 6 short traces, minimizing potencial interference with other traces, and also minimizing the number of vias.