# 18-Bit Universal Bus Driver with 3-State Outputs

## **Product Features**

- Very high-speed, low-noise universal bus driver with embedded resistor outputs

- Meets PC133 SDRAM Registered DIMM specification

- Implements output impedance control for low-noise and heavy-load applications

- Fast Propagation Delay: 2.5ns max. for 50pF test load

- $V_{CC} = 3.3 \text{V} \text{ or } 2.5 \text{V} \text{ or } 1.8 \text{V}$

- Packages available:

- -56-pin 240 mil wide plastic TSSOP (A)

- -56-pin 173 mil wide plastic TVSOP (K)

## **Product Pin Configuration**

| 56 GND 55 NC 54 A1 53 GND 52 A2 51 A3 50 VCC 49 A4 48 A5 47 A6 46 GND 45 A7 7in 44 A8 6 43 A9 6 42 A10 41 A11 40 A12 39 GND 38 A13 37 A14 36 A15 35 VCC 34 A16 33 A17 32 GND 31 A18 30 CLK |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 A18                                                                                                                                                                                     |

|                                                                                                                                                                                            |

## **Product Description**

Pericom Semiconductor's PI74AVC series of logic circuits are produced using the Company's advanced 0.35 micron CMOS technology, achieving industry leading speed.

The 18-bit PI74AVC16834 universal bus driver is designed for 1.8V to 3.6V V<sub>CC</sub> operation.

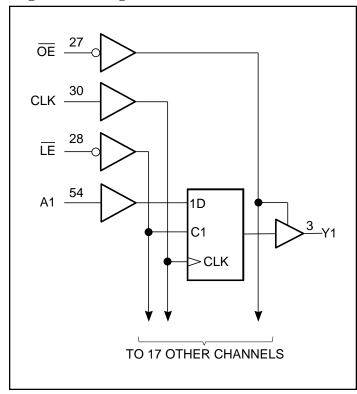

Data flow from A to Y is controlled by Output Enable ( $\overline{OE}$ ). The device operates in the transparent mode when  $\overline{LE}$  is LOW. The A data is latched if CLK is held at a high or low logic level. If  $\overline{\text{LE}}$  is HIGH, the A-bus is stored in the latch/flip-flop on the low-to-high transition of CLK. When  $\overline{OE}$  is HIGH, the outputs are in the highimpedance state.

The PI74AVC16834 bus driver is designed to drive an array of 133 MHz synchronous memory chips, with minimal undershoot/ overshoot noise, and to meet the input signal rise/fall time requirement of memory chips.

The output drivers of this part have an embedded series-resistor. For DIMM module design, no external series termination resistors near the buffer drivers or any other termination resistors are required. This feature simplifies DIMM module layout design, and results in cost savings.

> PS8378B 08/09/99

1

## **Logic Block Diagram**

# **Product Pin Description**

| Pin Name        | Description                      |

|-----------------|----------------------------------|

| ŌĒ              | Output Enable Input (Active LOW) |

| LE              | Latch Enable (Active LOW)        |

| CLK             | Clock Input                      |

| A               | Data Input                       |

| Y               | Data Output                      |

| GND             | Ground                           |

| V <sub>CC</sub> | Power                            |

## Truth Table(1)

|    | Inp | outs |   |                   |

|----|-----|------|---|-------------------|

| ŌE | LE  | CLK  | A | Outputs Y         |

| Н  | X   | X    | X | Z                 |

| L  | L   | X    | L | L                 |

| L  | L   | X    | Н | Н                 |

| L  | Н   | 1    | L | L                 |

| L  | Н   | 1    | Н | Н                 |

| L  | Н   | Н    | X | Yo <sup>(2)</sup> |

| L  | Н   | L    | X | Yo <sup>(3)</sup> |

## Note:

- 1 H = High Signal Level

- L = Low Signal Level

- Z = High Impedance

- ↑ = Transition LOW-to-HIGH

- X = Irrelevant

- 2. Output level before the indicated steady-state input conditions were established, provided that CLK is HIGH before  $\overline{\text{LE}}$  goes HIGH.

- 3. Output level before the indicated steady-state input conditions were established.

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature—65°C to +150°C                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature with Power Applied                                                                                                                                                                                |

| Supply Voltage Range, V <sub>CC</sub> —0.5V to +4.6V                                                                                                                                                                  |

| Input Voltage Range, $V_I^{(1)}$ —0.5V to +4.6V                                                                                                                                                                       |

| Voltage range applied to any output in the high-impedance or power-off state, $V_0^{(1)}$ $-0.5V$ to $+4.6V$                                                                                                          |

| Voltage range applied to any output in the high or low state, $V_0^{(1,2)}$                                                                                                                                           |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ )                                                                                                                                                                           |

| Output clamp current, $I_{OK}$ ( $V_0 < 0$ )                                                                                                                                                                          |

| Continuous output current, I <sub>0</sub> ±50mA                                                                                                                                                                       |

| Continuous current through each $V_{CC}$ or GND $\pm 100$ mA                                                                                                                                                          |

| $\begin{array}{c} \text{Package thermal impedance, } \theta_{JA}{}^{(3)}\text{: A (TSSOP) package} & \qquad \qquad & 81^{\circ}\text{C/W} \\ \text{K (TVSOP) package} & \qquad & 86^{\circ}\text{C/W} \\ \end{array}$ |

#### Note:

- 1. Input and output negative voltage ratings may be exceeded if the input and output current ratings are observed.

- 2. Output positive voltage rating may be exceeded up to 4.6V maximum if the output current rating is observed.

- 3. Package thermal impedance is calculated in accordance with JESD 51.

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Recommended Operating Conditions**(1)

| Parameters        | Description                        | Test Conditions                           | Min.                   | Max.                   | Units |

|-------------------|------------------------------------|-------------------------------------------|------------------------|------------------------|-------|

| **                | C 1 37 4                           | Operating                                 | 1.65                   | 3.6                    |       |

| $V_{CC}$          | Supply Voltage                     | Data Retention Only                       | 1.2                    |                        |       |

|                   |                                    | $V_{CC} = 1.2V$                           | V <sub>CC</sub>        |                        |       |

| **                | ****                               | $V_{CC} = 1.65 V \text{ to } 1.95 V$      | 0.65 x V <sub>CC</sub> |                        |       |

| $V_{\mathrm{IH}}$ | High-level Input Voltage           | $V_{CC} = 2.3 V \text{ to } 2.7 V$        | 1.7                    |                        |       |

|                   |                                    | $V_{CC} = 3V$ to 3.6V                     | 2                      |                        |       |

|                   |                                    | $V_{CC} = 1.2V$                           |                        | GND                    | V     |

| * 7               | Low-level Input Voltage            | $V_{CC} = 1.65 V \text{ to } 1.95 V$      |                        | 0.35 x V <sub>CC</sub> | _     |

| $V_{IL}$          |                                    | $V_{CC} = 2.3 V \text{ to } 2.7 V$        |                        | 0.7                    |       |

|                   |                                    | $V_{CC} = 3V$ to 3.6V                     |                        | 0.8                    |       |

| V <sub>IN</sub>   | Input Voltage                      | 0                                         | 3.6                    |                        |       |

| $V_{ m OUT}$      | Output Voltage                     | Active State                              | 0                      | Vcc                    |       |

|                   |                                    | 3-State                                   | 0                      | 3.6                    |       |

|                   | High-level Output Current (2)      | $V_{CC} = 1.65 V$ to 1.95 V               |                        | -4                     |       |

| $I_{OHS}$         |                                    | $V_{CC} = 2.3 V \text{ to } 2.7 V$        |                        | -8                     |       |

|                   |                                    | $V_{CC} = 3V \text{ to } 3.6V$            |                        | -12                    | 4     |

|                   |                                    | $V_{CC} = 1.65 V \text{ to } 1.95 V$      |                        | 4                      | mA    |

| $I_{OLS}$         | Low-level Output Current (2)       | $V_{CC} = 2.3 V \text{ to } 2.7 V$        |                        | 8                      |       |

|                   |                                    | $V_{\rm CC} = 3V$ to 3.6V                 |                        | 12                     |       |

| Δt/Δv             | Input transition rise or fall rate | $V_{CC} = 1.65 \text{V to } 3.6 \text{V}$ |                        | 5                      | ns/V  |

| $T_{A}$           | Operating Free-Air Temperature     |                                           | -40                    | 85                     | °C    |

## Note:

- 1. Unused control inputs must be held HIGH or LOW to prevent them from floating.

- 2. Dynamic drive is greater than standard output drive of  $I_{OH} = -24 \text{mA}$  and  $I_{OL} = 24 \text{mA}$

## **DC Electrical Characteristics** (Over the Operating Range, $TA = -40^{\circ}C$ to $+85^{\circ}C$ , $VCC = 3.3V \pm 10\%$ )

| Pa               | arameters             |                                          | Test Conditions                            | V <sub>CC</sub> <sup>(1)</sup> | Min.                 | Typ.(2) | Max. | Units |

|------------------|-----------------------|------------------------------------------|--------------------------------------------|--------------------------------|----------------------|---------|------|-------|

|                  |                       | $I_{OHS} = -100\mu A$                    | V <sub>IH</sub> or V <sub>IL</sub>         | 1.65 to 3.6                    | V <sub>CC</sub> -0.2 |         |      |       |

| Voy              |                       | $I_{OHS} = -4mA$                         | $V_{IH} = 1.07V$                           | 1.65                           | 1.2                  |         |      |       |

| V <sub>OH</sub>  |                       | $I_{OHS} = -8mA$                         | $V_{IH} = 1.7V$                            | 2.3                            | 1.75                 |         |      |       |

|                  |                       | $I_{OHS} = -12mA$                        | $V_{IH} = 2V$                              | 3.0                            | 2.3                  |         |      | v     |

|                  |                       | $I_{OLS} = 100 \mu A$                    | V <sub>IH</sub> or V <sub>IL</sub>         | 1.65 to 3.6                    |                      |         | 0.2  | ·     |

| Vor              |                       | $I_{OLS} = 4mA$                          | $V_{\rm IL} = 0.57 V$                      | 1.65                           |                      |         | 0.45 |       |

| VOL              | Vol                   | $I_{OLS} = 8mA$                          | $V_{\rm IL} = 0.7 V$                       | 2.3                            |                      |         | 0.55 | 5     |

|                  |                       | $I_{OLS} = 12mA$                         | $V_{\rm IL} = 0.8 V$                       | 3.0                            |                      |         | 0.7  |       |

| $I_{\mathrm{I}}$ | Control Inputs        | $V_{I} = V_{CC}$ or GND                  |                                            | 3.6                            |                      |         | 2.5  |       |

| I <sub>OFF</sub> |                       | $V_{\rm I} = 0 \text{ or } 3.6 \text{V}$ |                                            | 0                              |                      |         | ±10  |       |

| $I_{OZ}^{(3)}$   |                       | $V_{O} = V_{CC}$ or GND                  | $\overline{\mathrm{OE}} = \mathrm{V_{CC}}$ | 3.6                            |                      |         | ±10  | μΑ    |

| I <sub>CC</sub>  |                       | $V_{I} = V_{CC}$ or GND                  | $I_{O} = 0$                                | 3.6                            |                      |         | 40   |       |

|                  | Control Inputs        |                                          |                                            | 2.5                            |                      | 4.5     |      |       |

| $C_{\mathrm{I}}$ | Control inputs        | V = V = a CND                            |                                            | 3.3                            |                      | 4.5     |      |       |

|                  | Data Input            | $V_{I} = V_{CC} \text{ or GND}$          |                                            | 2.5                            |                      | 4.0     |      | pF    |

|                  | Data Input            |                                          |                                            | 3.3                            |                      | 4.0     |      | pr    |

| Co               | Outputs V. = V or CND |                                          |                                            | 2.5                            |                      | 6.5     |      |       |

| Co               | Outputs               | $V_{O} = V_{CC}$ or GND                  |                                            | 3.3                            |                      | 6.5     |      |       |

#### **Notes:**

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are measured at +25°C.

- 3. For I/O ports, the I<sub>OZ</sub> includes the input leakage current.

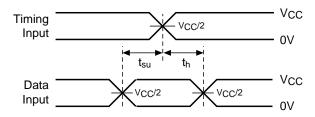

# **Timing Requirements over Operating Range**

| Parameters                       | Description                                 | $V_{CC} = 1.8 \text{ V}$ $\pm 0.15 \text{V}$ |      | V <sub>CC</sub> = 2.5V<br>± 0.2V |      | V <sub>CC</sub> =3.3V<br>± 0.3V |      | Units |

|----------------------------------|---------------------------------------------|----------------------------------------------|------|----------------------------------|------|---------------------------------|------|-------|

|                                  |                                             | Min.                                         | Max. | Min.                             | Max. | Min.                            | Max. |       |

| fclock                           | Clock Frequency                             |                                              | 150  |                                  | 150  |                                 | 150  | MHz   |

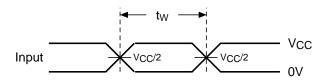

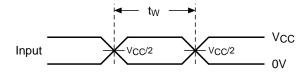

| t <sub>W</sub> Pulse<br>Duration | LE Low                                      | 2.0                                          |      | 1.2                              |      | 1.0                             |      |       |

|                                  | CLK High or Low                             | 2.0                                          |      | 1.2                              |      | 1.0                             |      |       |

| t Catam times                    | Data before CLK↑                            | 1.4                                          |      | 1.2                              |      | 1.0                             |      | ns    |

| t <sub>SU</sub> Setup time       | Data before LE↑, CLK High or Low            | 1.4                                          |      | 1.2                              |      | 1.0                             |      | 1115  |

| t <sub>H</sub> Hold time         | Data after CLK↑                             | 1.0                                          |      | 0.8                              |      | 0.6                             |      |       |

|                                  | Data after <del>LE</del> ↑, CLK High or Low | 1.0                                          |      | 0.8                              |      | 0.6                             |      |       |

5

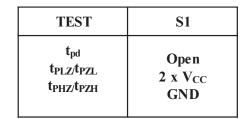

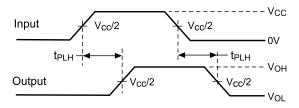

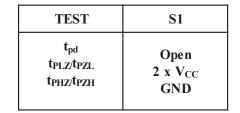

# **Switching Characteristics Over Recommended Operating Free-Air Temperature Range** Unless otherwise noted, see Figures 1 through 3.

| Parameter        | From    | To (Output) | V <sub>CC</sub> = ±0.1 |      | V <sub>CC</sub> = ±0. |      | $V_{CC} = 3.3V^{(1)} \pm 0.3V$ |      | Units |

|------------------|---------|-------------|------------------------|------|-----------------------|------|--------------------------------|------|-------|

|                  | (Input) | (Output)    | Min.                   | Max. | Min.                  | Max. | Min.                           | Max. |       |

| f <sub>max</sub> |         |             | 150                    |      | 150                   |      | 150                            |      | MHz   |

|                  | A       |             | 1.0                    | 4.5  | 0.8                   | 3.0  | 0.7                            | 2.4  |       |

| $t_{pd}$         | ĪĒ      |             | 1.0                    | 5.0  | 0.8                   | 3.3  | 0.7                            | 2.5  |       |

|                  | CLK     | Y           | 1.0                    | 4.5  | 0.8                   | 3.0  | 0.7                            | 2.5  | ns    |

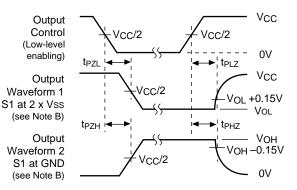

| t <sub>en</sub>  | ŌĒ      |             | 1.5                    | 5.5  | 1.0                   | 4.5  | 1.0                            | 4.0  |       |

| t <sub>DIS</sub> | ŌĒ      |             | 1.5                    | 5.0  | 1.0                   | 4.5  | 1.0                            | 4.0  |       |

**Note 1.** Load at 50pF and 500 $\Omega$ .

# Operating Characteristics, $T_A = 25^{\circ}C$

| Parameters                        | Test<br>Conditions | $V_{\rm CC} = 1.8 V$ Typ. | $V_{\rm CC} = 2.5 V$ Typ. | $V_{\rm CC} = 3.3V$ Typ. | Units |    |

|-----------------------------------|--------------------|---------------------------|---------------------------|--------------------------|-------|----|

|                                   |                    |                           | -J P                      | -J P*                    | -J P  |    |

| C <sub>pd</sub> Power dissipation | Outputs Enabled    | $C_L = 0$ ,               | 45                        | 48                       | 52    | рF |

| capacitance                       | Outputs Disabled   | f= 10 MHz                 | 23                        | 25                       | 28    | pr |

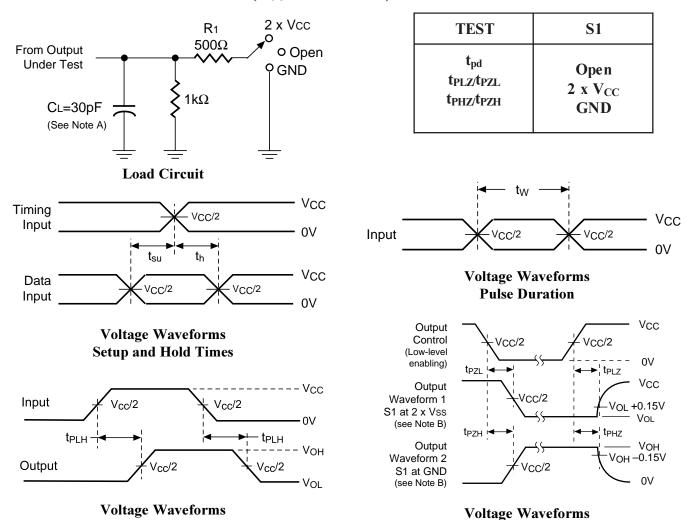

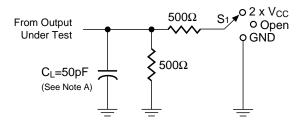

## Parameter Measurement Information ( $V_{CC} = 1.8V \pm 0.15V$ )

#### **Notes:**

A. C<sub>L</sub> includes probe and jig capacitance.

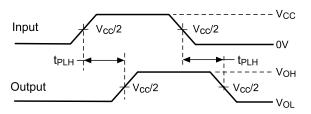

**Propagation Delay Times**

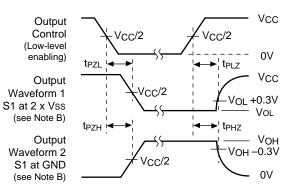

- B. Waveform 1 is for an output with internal conditions such that the output is LOW except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is HIGH except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0$  = 50 $\Omega$ ,  $t_r \leq$ 2ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E.  $t_{\text{PLZ}}$  and  $t_{\text{PHZ}}$  are the same as  $t_{\text{dis}}.$

- F. tpzL and tpzH are the same as tdis.

- G.  $t_{\text{PLH}}$  and  $t_{\text{PHL}}$  are the same as  $t_{\text{dis}}.$

Figure 1. Load Circuit and Voltage Waveforms

7

PS8378B 08/09/99

**Enable and Disable Times**

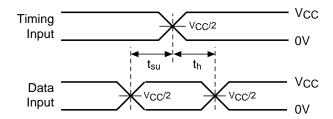

## Parameter Measurement Information ( $V_{CC} = 2.5V \pm 0.2V$ )

#### **Load Circuit**

Voltage Waveforms Setup and Hold Times

Voltage Waveforms Propagation Delay Times

Voltage Waveforms Pulse Duration

Voltage Waveforms Enable and Disable Times

#### **Notes:**

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is LOW except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is HIGH except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50\Omega$ ,  $t_r \leq 2$ ns,  $t_r \leq 2$ ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E. tplz and tpHz are the same as tdis.

- F. t<sub>PZL</sub> and t<sub>PZH</sub> are the same as t<sub>dis</sub>.

- G. tplh and tphl are the same as tdis.

Figure 2. Load Circuit and Voltage Waveforms

8

PS8378B 08/09/99

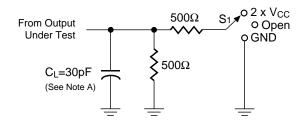

## Parameter Measurement Information ( $V_{CC} = 3.3V \pm 0.3V$ )

**Load Circuit**

Voltage Waveforms Setup and Hold Times

Voltage Waveforms Propagation Delay Times

Voltage Waveforms Pulse Duration

Voltage Waveforms Enable and Disable Times

## **Notes:**

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is LOW except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is HIGH except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O$  =  $50\Omega$ ,  $t_r \leq 2$ ns,  $t_r \leq 2$ ns.

- D. The outputs are measured one at a time with one transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{dis}$ .

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{dis}$ .

Figure 3. Load Circuit and Voltage Waveforms

#### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com

PS8378B 08/09/99