## 3.3V 8-Bit Buffers/Line Drivers with 3-State Outputs

#### **Product Features**

- Advanced low power CMOS design for 2.7V to 3.6V V<sub>CC</sub> operation

- Supports 5V input/output tolerance in mixed signal mode operation

- Function compatible with LVT family of products

- Balanced ±24mA output drive

- Typical V<sub>OLP</sub> (Output Ground Bounce) < 0.8V at V<sub>CC</sub>=3.3V,  $T_A=25$ °C

- I<sub>off</sub> and Power Up/Down 3-State support live insertion

- Latch-up performance exceeds 200mA Per JESD78

- ESD protection exceeds JESD 22

- -2000V Human-Body Model (A114-B)

- 200V Machine Model (A115-A)

- Packages (Pb-free available):

- -20-pin 209-mil wide plastic SSOP (H20)

- -20-pin 173-mil wide plastic TSSOP (L20)

- -20-pin 300-mil wide plastic SOIC (S20)

#### **Product Description**

Pericom Semiconductor's PI74LVTC series of logic circuits are produced using the Company's advanced CMOS technology, achieving industry leading speed.

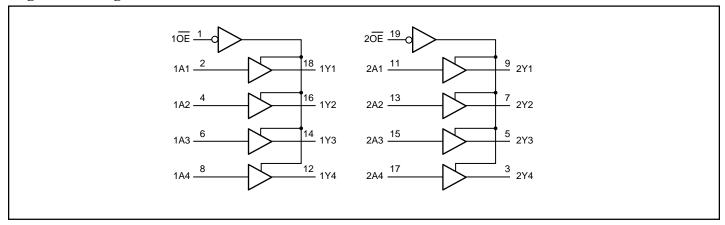

The PI74LVTC244 is a non-inverting 8-bit buffer and line driver designed for low-voltage 2.7V to 3.6V V<sub>CC</sub> operation, with the capability of interfacing to the 5V system environment. With its balanced drive characteristics, this high-speed, low power device provides low ground bounce and transmission line impedance matching. This makes it ideal for driving on board buses and transmission lines. The device can be used as two 4-bit buffers with separate output enable (OE) inputs.

When V<sub>CC</sub> is between 0 to 1.5V during power up or power down, the outputs of the device are in the high-impedance state. To ensure the high-impedance state above 1.5V, OE should be tied to Vcc through a pullup resistor; the minimum value of the resistor is determined by the current sinking capability of the driver.

The device fully supports live-insertion with its I<sub>off</sub> and power-up/ down 3-state. The Ioff circuitry disables the outputs when the power is off, preventing the backflow of damaging current through the device. Power-up/down 3-state places the outputs in the high-impedance state during power up or power down, preventing driver conflict.

### Logic Block Diagram

1

07/01/03 PS8691

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Supply voltage range, V <sub>CC</sub> –0.5V to+6.5V                          |

|------------------------------------------------------------------------------|

| Input voltage range, $V_1^{(1)}$                                             |

| Voltage range applied to any output in the                                   |

| high-impedance or power-off state, $V_0^{(1)}$ $-0.5V$ to $+6.5V$            |

| Voltage range applied to any output in the                                   |

| active state, $V_0^{(1), (2)}$ 0.5V to $V_{CC}$ +0.5V                        |

| Input clamp current, $I_{IK}(V_I < 0)$                                       |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> <0) –50mA              |

| Continous Output Current I <sub>O</sub> ±50mA                                |

| Continous Current through each V <sub>CC</sub> or GND pin ±100mA             |

| Package thermal impedance, θ <sub>JA</sub> <sup>(3)</sup> : package H 81°C/W |

| package L 84°C/W                                                             |

| package S 84°C/W                                                             |

| Storage Temperature range, T <sub>stg</sub> 65°C to 150°C                    |

#### **Notes:**

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 1. Input negative-voltage and output voltage ratings may be exceeded if the input and output clamp current ratings are observed.

- 2. This value is limited to 6.5V maximum.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

#### Truth Table<sup>(4)</sup>

| Inp             | Outputs |     |

|-----------------|---------|-----|

| x <del>OE</del> | xAx     | xYx |

| L               | Н       | Н   |

| L               | L       | L   |

| Н               | X       | Z   |

#### Notes:

- 4. H = High Signal Level

- L = Low Signal Level

- X = Don't Care or Irrelevant

- Z = High Impedance

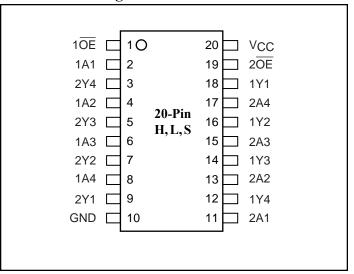

## **Product Pin Description**

| Pin Name         | Description                               |  |  |  |  |

|------------------|-------------------------------------------|--|--|--|--|

| x <del>O</del> E | 3-State Output Enable Inputs (Active LOW) |  |  |  |  |

| xAx              | Inputs                                    |  |  |  |  |

| xYx              | 3-State Outputs                           |  |  |  |  |

| GND              | Ground                                    |  |  |  |  |

| V <sub>CC</sub>  | Power                                     |  |  |  |  |

## **Product Pin Configuration**

## $\textbf{Recommended Operating Conditions}^{(5)}$

|                                                        |                                          | Min. | Max.            | Units |  |

|--------------------------------------------------------|------------------------------------------|------|-----------------|-------|--|

| V <sub>CC</sub> Supply Voltage                         | Operating                                | 2.7  | 3.6             |       |  |

| V <sub>IH</sub> High-level Input Voltage               | $V_{CC} = 2.7V \text{ to } 3.6V$         | 2.0  |                 |       |  |

| V <sub>IL</sub> Low-level Input Voltage                | $V_{CC} = 2.7V \text{ to } 3.6V$         |      | 0.8             | ]     |  |

| V <sub>I</sub> Input Voltage                           |                                          | 0    | 5.5             | V     |  |

| V <sub>O</sub> Output Voltage                          | High or Low State                        | 0    | V <sub>CC</sub> |       |  |

|                                                        | 3-State                                  | 0    | 5.5             |       |  |

| I <sub>OH</sub> High-level output current              | $V_{CC} = 2.7V$                          |      | -12             |       |  |

|                                                        | $V_{CC} = 3.0 V \text{ to } 3.6 V$       |      | - 24            |       |  |

|                                                        | $V_{CC} = 2.7V$                          |      | 12              | mA    |  |

| I <sub>O</sub> L Low-level output current              | $V_{CC} = 3.0 \text{V to } 3.6 \text{V}$ |      | 24              | 1     |  |

| $\Delta t/\Delta V$ Input transition rise or fall rate |                                          |      | 10              | ns/V  |  |

| $\Delta t/\Delta V_{CC}$ Power-up ramp rate            |                                          | 150  |                 | μs/V  |  |

| T <sub>A</sub> Operating free-air temperature          | - 40                                     | 85   | °C              |       |  |

#### **Notes:**

5. All unused inputs must be held at  $V_{CC}$  or GND to ensure proper device operation.

07/01/03

## **DC Electrical Characteristics** (Over the Operating Range, $T_A = -40$ °C +85°C)

| Paramete-<br>rs   | Description                       | Test Conditions                  |                                                                           | Min.                  | Max.  | Units |

|-------------------|-----------------------------------|----------------------------------|---------------------------------------------------------------------------|-----------------------|-------|-------|

| V <sub>IK</sub>   | Clamp Diode Voltage               | $V_{CC} = 2.7V$                  | $I_{I} = -18\text{mA}$                                                    |                       | -1.2V |       |

|                   |                                   | $V_{CC} = 2.7V \text{ to } 3.6V$ | $I_{OH} = -100 \mu A$                                                     | V <sub>CC</sub> -0.2V |       |       |

|                   | Outout High Voltage               | $V_{CC} = 2.7V$                  | $I_{OH} = -12 \text{mA}$                                                  | 2.2                   |       |       |

| V <sub>OH</sub>   | Outout riigii voitage             | V - 2V                           | $I_{OH} = -12 \text{mA}$                                                  | 2.4                   |       |       |

|                   |                                   | $V_{CC} = 3V$                    | $I_{OH} = -24 \text{mA}$                                                  | 2.2                   |       | V     |

|                   |                                   | $V_{CC} = 2.7V \text{ to } 3.6V$ | $I_{OL} = 100 \mu A$                                                      |                       | 0.2   |       |

| V                 | Outout Low Voltage                | $V_{CC} = 2.7V$                  | $I_{OL} = 12 \text{mA}$                                                   |                       | 0.4   |       |

| V <sub>OL</sub>   | Outout Low Voltage                | $V_{CC} = 3V$                    | $I_{OL} = 12 \text{mA}$                                                   |                       | 0.4   |       |

|                   |                                   |                                  | $I_{OL} = 24 \text{mA}$                                                   |                       | 0.55  |       |

| I <sub>I</sub>    | Input leakage Current             | $V_{CC} = 0 \text{ to } 3.6V$    | $0 \le V_I \le 5.5V$                                                      |                       | ±5    |       |

| I <sub>OFF</sub>  | Power Off Disable                 | $V_{CC} = 0V$                    | $V_{\rm I}$ or $V_{\rm O} = 0$ to 5.5V                                    |                       | ±5    |       |

| I <sub>OZ</sub>   | 3-State Output Leakage<br>Current | $V_{CC} = 2.7V \text{ to } 3.6V$ | $0 \le V_O \le 5.5V$                                                      |                       | ±5    |       |

| I <sub>OZPU</sub> | Power-Up 3-State Current          | $V_{CC} = 0V \text{ to } 1.5V$   | $V_O = 0.5V$ to 5.5V,<br>$\overline{OE} = \text{don't care}$              |                       | ±5    |       |

| I <sub>OZPD</sub> | Power-Down 3-State Current        | $V_{CC} = 1.5V \text{ to } 0V$   | $ \underline{V}_{O} = 0.5V \text{ to } 5.5V, $ $OE = \text{don't care}$   |                       | ±5    | μΑ    |

| I <sub>CC</sub>   | Quiescent Power Supply<br>Current | $V_{CC} = 2.7V \text{ to } 3.6V$ | $\frac{V_{I} = V_{CC} \text{ or GND}}{3.6V \le V_{I} \le 5.5V} I_{O} = 0$ |                       | 100   |       |

| $\Delta I_{CC}$   | Increase in I <sub>CC</sub>       | $V_{\rm CC} = 3V$ to 3.6V        | One input at $V_{CC}$ - 0.6 $V^{(6)}$<br>Other inputs at $V_{CC}$ or GND  |                       | 100   |       |

#### **Notes:**

6. This is the increase in supply current for each input that is at the specified TTL voltage level rather than  $V_{CC}$  or GND

4

## Capacitance

| Parameters        | Description                       | Test Conditions                                         | <b>Typ.</b> <sup>(7)</sup> | Units |

|-------------------|-----------------------------------|---------------------------------------------------------|----------------------------|-------|

| $C_{\mathrm{IN}}$ | Input Capacitance                 | $V_{CC} = 3.3V$ , $V_I = V_{CC}$ or GND                 | 3.0                        |       |

| C <sub>OUT</sub>  | Output Capacitance                | $V_{CC} = 3.3V$ , $V_O = V_{CC}$ or GND                 | 6.2                        | pF    |

| $C_{PD}$          | Power Dissipation Capacitance (8) | $V_{CC} = 3.3V$ , $V_{I} = 0V$ or $V_{CC}$ , $f=10$ MHz | 28                         |       |

#### **Notes:**

- 7. All typical values are measured at  $V_{CC}$  = 3.3V,  $T_A$  = 25°C.

- 8.  $C_{PD}$  is defined as the value of the internal equivalent capacitance withic is derived from dynamic operating current consumption ( $I_{CCD}$ ) at no output loading and operating at 50% duty cycle,  $C_{PD}$  is related to  $I_{CCD}$  dynamic operating current by the expression:  $I_{CCD} = (C_{PD})(V_{CC})(f_{IN})+(I_{CCS}tatic)$ .

## Switching Characteristics Over Operating Range

|                    | E                                       |                | Tr.   | $V_{CC} = 3.3V \pm 0.3V$ |                       | $V_{CC} = 2.7V$                                |      |       |     |     |    |

|--------------------|-----------------------------------------|----------------|-------|--------------------------|-----------------------|------------------------------------------------|------|-------|-----|-----|----|

| Parameters         | Description                             | From (Input) ( |       | C 50 E D 50001           |                       | $C_{L} = 50 \text{pF}, R_{L} = 500 \text{Ohm}$ |      | Units |     |     |    |

|                    |                                         |                |       | Min.                     | Max.                  | Min.                                           | Max. |       |     |     |    |

| t <sub>PLH</sub>   | Propagation                             | A              | A     | A                        | Y                     | 1.0                                            | 5.2  | 1.0   | 5.8 |     |    |

| t <sub>PHL</sub>   | Delay                                   |                |       |                          | A                     | I                                              | 1.0  | 5.2   | 1.0 | 5.8 |    |

| t <sub>PZH</sub>   | Output Enable                           | ŌE             | ŌE    | OE OE                    | Output Enable Time OE | Y                                              | 1.0  | 5.8   | 1.0 | 6.8 |    |

| t <sub>PZL</sub>   | Time                                    |                |       |                          |                       | I                                              | 1.0  | 5.8   | 1.0 | 6.8 | ns |

| t <sub>PHZ</sub>   | Output Disable Time                     | ŌE             | OE OE | OE                       |                       | Y                                              | 1.0  | 4.6   | 1.0 | 4.8 |    |

| $t_{\mathrm{PL}Z}$ |                                         |                |       |                          | I                     | 1.0                                            | 4.6  | 1.0   | 4.8 |     |    |

| t <sub>SK(O)</sub> | Output to<br>Output Skew <sup>(9)</sup> |                |       |                          | 0.5                   |                                                |      |       |     |     |    |

5

#### **Notes:**

9. Skew between any two outputs, switching in the same direction.

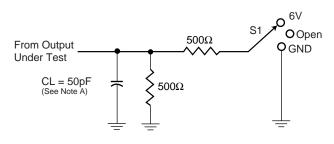

# PARAMETER MEASUREMENT INFORMATION $V_{CC} = 2.7V$ and $3.3V \pm 0.3V$

| Test      | S1   |

|-----------|------|

| tplh/tphl | Open |

| tplz/tpzl | 6V   |

| tphz/tpzh | GND  |

**Load Circuit**

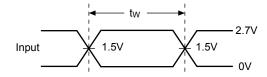

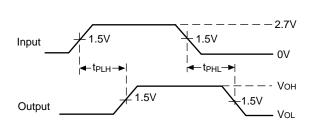

Voltage Waveforms Pulse Duration

Voltage Waveforms Propagation Delay Times

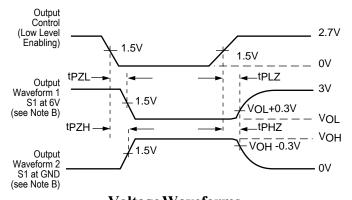

Voltage Waveforms Enable and Disable Times

Figure 1. Load Circuit and Voltage Waveforms

#### Notes:

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input impulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O$  = 5000hm,  $t_R \leq$  2.5ns,  $t_F \leq$  2.5ns.

6

D. The outputs are measured one at a time with one transition per measurement.

PS8691 07/01/03

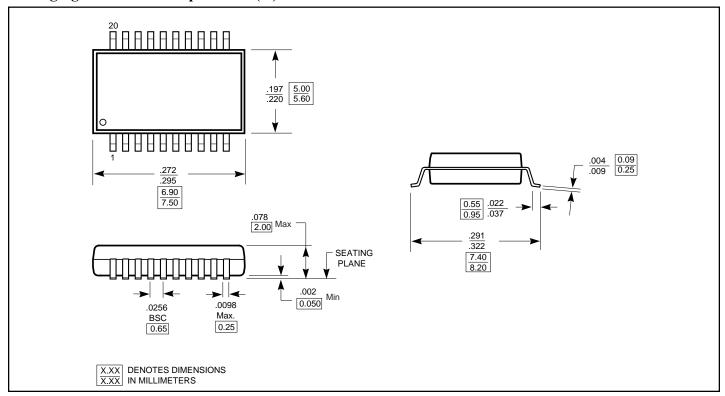

## Packaging Mechanical: 20-pin SSOP (H)

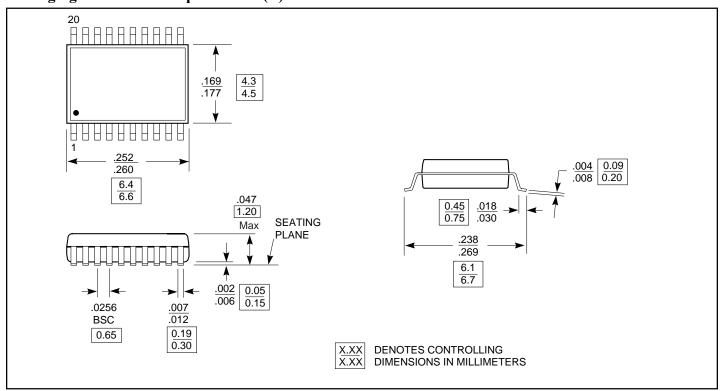

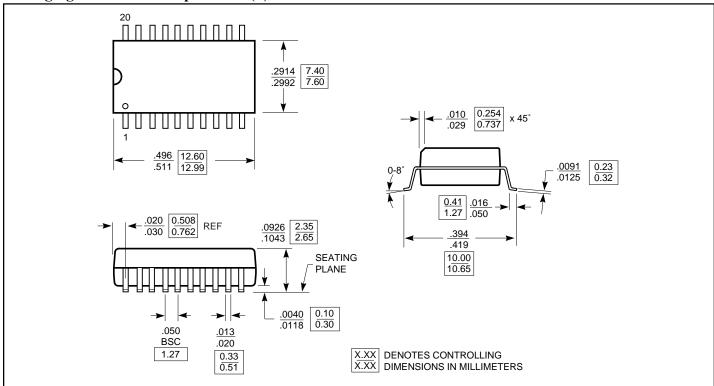

## Packaging Mechanical: 20-pin TSSOP(L)

## Packaging Mechanical: 20-pin SOIC (S)

## **Ordering Information**

| Ordering Code | Packaging Code | Description                        |

|---------------|----------------|------------------------------------|

| PI74LVTC244H  | Н              | 20-pin, 209-mil wide plastic SSOP  |

| PI74LVTC244L  | L              | 20-pin, 173-mil wide plastic TSSOP |

| PI74LVTC244S  | S              | 20-pin, 300-mil wide plastic SOIC  |

#### **Notes:**

1. Thermal characteristics can be found on the company web site at http://www.pericom.com/packaging/mechanicals.php

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com 8

07/01/03 PS8691