## PI90LV211/PI90LVT211

#### **Product Features**

- Meets or Exceeds Requirements of ANSI TIA/EIA-644-1995

- Designed for Clocking Rates up to 320MHz

- Operates from a single 3.3-V Supply

- Low-Voltage Differential Signaling (LVDS) with Output Voltages of ±350mV into a 100-ohm load

- Choice between LVDS or TTL clock input

- · Synchronous Enable/Disable

- Multiplexed clock input

- Internal 300 kohm pullup resistor on all control pins

- -CLK and CLK have 110-ohm termination (PI90LVT211)

- · Common and individual Enable/Disable control

- 50ps Output-to-Output Skew

- ±24ps Period Jitter

- Bus Pins are High Impedance when disabled or with  $V_{CC} \le 1.5 V$

- TTL Inputs are 5V Tolerant

- Power Dissipation at 300 MHz (TBD)

- P190LV211 is functionally compatible with Motorola's (PECL)MC10E211/MC100E211

- >12kV ESD Protection

- 28-pin TSSOP (L) and QSOP (Q) packages

# 1:6 Differential Clock Distribution Chip

### **Product Description**

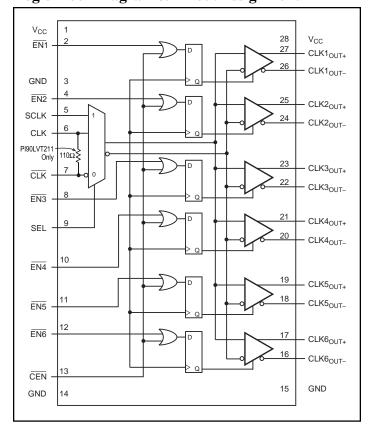

The PI90LV211 implements low voltage differential signaling (LVDS) to achieve clocking rates as high as 320 MHz with low skew. The PI90LV211 is a low skew 1:6 fanout device designed explicitly for low skew clock distribution applications. The device features a multiplexed clock input to allow for the distribution of a lower speed scan or test clock with the high-speed system clock. When LOW the SEL pin will select the differential clock input.

Both a common enable and individual output enables are provided. When asserted the positive output will go LOW on the next negative transition of the CLK (or SCLK) input. The enable function is synchronous so that the outputs will only be enabled/disabled when they are already in the LOW state. This avoids any chance of generating a runt clock pulse when the device is enabled/disabled as can happen with an asynchronous control. The internal flip flop is clocked on the falling edge of the input clock, therefore all associated specification limits are referenced to the negative edge of the clock input.

Individual synchronous enable controls and multiplexed clock inputs make this device ideal as the first level distribution unit in a distribution tree. The individual enables could be used to allow for the disabling of individual cards on a backplane in fault tolerant designs.

## Logic Block Diagram & Pinout Assignment

#### **Function Table**

| CLK/CLK  | SCLK         | SEL    | <del>EN</del> x | CEN    | CLK OUT (±) |

|----------|--------------|--------|-----------------|--------|-------------|

| H/L<br>X | X<br>H/L     | L<br>H | L<br>L          | L<br>L | CLK<br>SCLK |

| <b>\</b> | $\downarrow$ | X<br>H | H<br>L          | L<br>H | Z*<br>Z**   |

- ENx disables individual banks

- CEN disables all six banks

- = Negative transition of CLK or SCLK

- Z = High Impedance

1

PS8535A 09/11/01

## **Electrical Characteristics over Recommended Operating Conditions** (unless otherwise noted).

| Symbol                     | Parameter                                                              | Test Conditions                                     | Min.  | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |

|----------------------------|------------------------------------------------------------------------|-----------------------------------------------------|-------|----------------------------|------|-------|

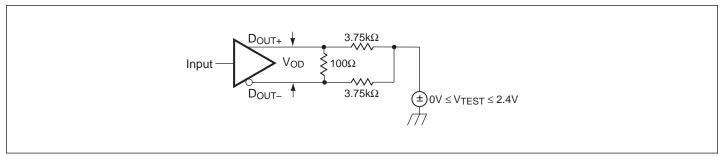

| V <sub>OD</sub>            | Differential output voltage magnitude                                  | $R_{\rm L} = 100\Omega$                             | 247   | 340                        | 454  | mV    |

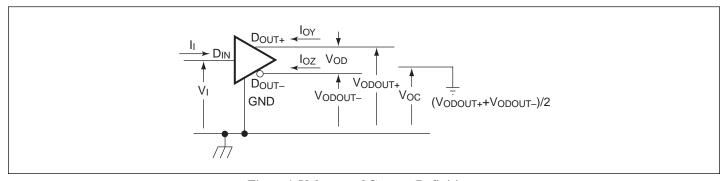

| $\Delta  V_{\mathrm{OD}} $ | Change in differential output voltage magnitude between logic states   | See Figures 1 and 2                                 | -50   |                            | 50   |       |

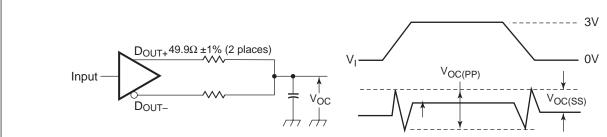

| V <sub>OC(SS)</sub>        | Steady-state common-mode output voltage                                |                                                     | 1.125 | 1.30                       | 1.60 | V     |

| $\Delta V_{OC(SS)}$        | Change in steady-state common-mode output voltage between logic states | See Figure 3                                        | -50   |                            | 50   | - mV  |

| V <sub>OC(PP)</sub>        | Peak-to-peak common-mode output voltage                                |                                                     |       | 40                         | 150  |       |

| Inn                        | Supply Current                                                         | Enabled, $R_L = 100\Omega \ V_{IN} = V_{CC}$ or GND |       | 27                         | 35   | A     |

| $I_{CC}$                   |                                                                        | Disabled, $V_{IN} = V_{CC}$ or GND                  |       | 3.0                        | 3.9  | .9 mA |

| $I_{\mathrm{IH}}$          | High-level input current                                               | $V_{IH} = 2V$                                       |       | 4.8                        | 20   | Α.    |

| $I_{\mathrm{IL}}$          | Low-level input current                                                | $V_{IL} = 0.8V$                                     |       | 9                          | 20   | μA    |

| I <sub>OS</sub>            | Chart aircuit auteut aureant                                           | V <sub>ODOUT+</sub> or V <sub>ODOUT-</sub> = 0V     |       |                            | ±7   | mA    |

|                            | Short-circuit output current                                           | $V_{OD} = 0V$                                       |       |                            | ±4.5 |       |

| I <sub>OZ</sub>            | High-impedance output current                                          | $V_{O} = 0V$ or $V_{CC}$                            |       |                            | ±1   | μА    |

| I <sub>O(OFF)</sub>        | Power-off output current                                               | $V_{CC} = 1.5V,  V_{O} = 2.4V$                      |       |                            | ±1   |       |

| C <sub>IN</sub>            | Input capacitance,                                                     | $V_{\rm I} = 0.4 \sin(4E6\pi t) + 0.5 V$            |       | 9                          |      | Г     |

| Co                         | Output capacitance                                                     | $V_{I} = 0.4 \sin (4E6\pi t) + 0.5 V$ , Disabled    |       | 10                         |      | pF    |

| R <sub>TERM</sub>          | Termination Resistor                                                   | PI90LVT211                                          | 90    | 110                        | 132  | Ω     |

### Switching Characteristics over Recommended Operating Conditions (unless otherwise noted)<sup>(8,9)</sup>.

| Characteristic                                           | Symbol                | Min.  | Тур. | Max.                  | Units | Condition |

|----------------------------------------------------------|-----------------------|-------|------|-----------------------|-------|-----------|

| Propagation Delay to Output                              |                       |       |      |                       |       |           |

| CLK to CLKOUT ±                                          | $t_{\rm PLH}$         | 1.5   | 2.7  | 3.4                   |       |           |

| SCLK to CLKOUT ±                                         | $t_{ m PHL}$          | 1.5   | 2.7  | 3.24                  |       |           |

| SEL to CLKOUT ±                                          |                       | 1.5   | 2.7  | 3.6                   |       |           |

| Disable Time                                             |                       |       |      |                       | ns    |           |

| CLK or SCLK to CLKOUT ±                                  | $t_{\mathrm{PHZ}}$    |       | 2.2  | 2.8                   |       |           |

|                                                          | $t_{\rm PLZ}$         |       | 2.1  | 2.8                   |       | 2         |

|                                                          | $t_{\mathrm{PZH}}$    |       | 3.6  | 4.8                   |       | 2         |

|                                                          | t <sub>PZL</sub>      |       | 2.8  | 4.8                   |       |           |

| Part-to-Part Skew                                        |                       |       |      |                       |       |           |

| CLK (Diff) to Q                                          | t <sub>skew</sub>     |       |      | TBD                   |       |           |

| CLK (SE), SCLK to Q                                      | SKCW                  |       |      | TBD                   |       | 1         |

| With Device Skew                                         |                       |       |      | TBD                   |       |           |

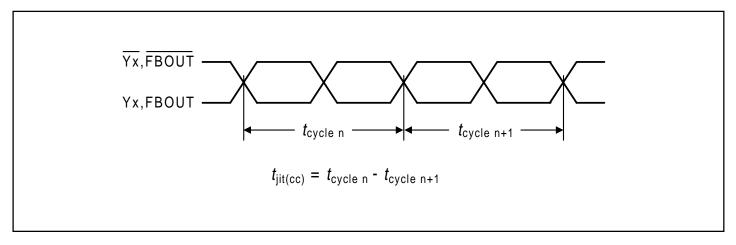

| Cycle-to-Cycle Jitter                                    | t <sub>jit(cc)</sub>  | -48   |      | +48                   |       | Figure 6  |

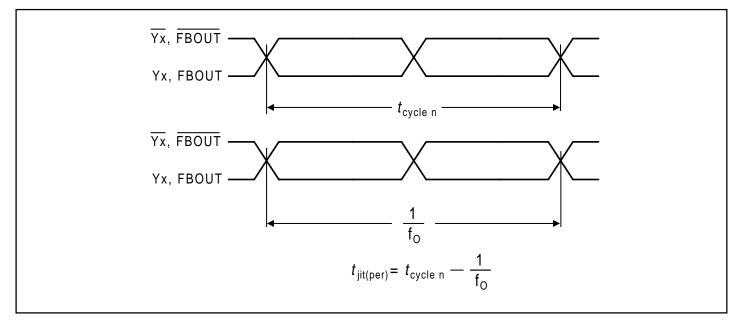

| Period Jitter                                            | t <sub>jit(per)</sub> | -24   |      | +24                   | ps    | Figure 7  |

| Setup Time                                               |                       |       |      |                       |       |           |

| $\overline{\mathrm{EN}}\mathrm{x}$ to CLK                | $t_{\rm s}$           | 200   | -100 |                       |       | 2         |

| CEN to CLK                                               |                       | 200   | 0    |                       |       |           |

| Hold Time                                                |                       |       |      |                       |       | _         |

| CLK to $\overline{\text{EN}}$ x, $\overline{\text{CEN}}$ | $t_{\rm h}$           |       | 600  | 760                   |       | 2         |

| Minimum Input Swing (CLK)                                | $V_{PP}$              | 0.20  |      | 0.800                 | V     | 3         |

| Com. Mode Range (CLK)                                    | V <sub>CMR</sub>      | 0.125 | 1.5  | V <sub>CC</sub> - 0.2 | v     | 4         |

| Rise/Fall Times                                          |                       |       |      |                       |       |           |

| 20 - 80%                                                 | $t_r, t_f$            | 150   | 400  | 1200                  |       |           |

| Duty Cycle Distortion Pulse Skew (tplh - tphl)           |                       |       |      |                       | 1     |           |

| SCLK to CLKOUT±                                          | t <sub>SK1R</sub>     |       | 140  | 180                   | ps    | 5         |

| CLK to CLKOUT±                                           | t <sub>SK1R</sub>     |       | 25   | 60                    |       |           |

| Channel-to-Channel Skew, same edge                       | t <sub>SK2R</sub>     |       | 30   | 100                   |       | 6         |

| Maximum Operating Frequency                              |                       |       | 250  |                       | MHz   | 7         |

#### Notes:

- 1. Within-Device skew is defined for identical transitions on similar paths through a device.

- 2. Setup, Hold, and Disable times are all relative to a falling edge on CLK or SCLK.

- 3. Minimum input swing for which AC parameters are guaranteed. Full DC LVDS output swings will be generated with only 50mV input swings.

- 4. The range in which the high level of the input swing must fall while meeting the  $V_{PP}\,\text{spec}.$

- 5.  $t_{SKIR}$  is the difference in receiver propagation delay ( $t_{PLH}$ - $t_{PHL}$ ) of one device, and is the duty cycle distortion of the output at any given temperature and  $V_{CC}$ . The propagation delay specification is a device-to-device worst case over process, voltage, and temperature.

- 6. t<sub>SK2R</sub> is the difference in receiver propagation delay between channels in the same device of any outputs switching in the same direction. This parameter is guaranteed by design and characterization.

- 7. Generator input conditions:  $t_r t_f < 1$ ns, 50% duty cycle, differential (1.10V to 1.35V peak-peak). Output Criteria: 60%/40% duty cycle,  $V_{OL}(max)0-4V$ ,  $V_{OH}(min)2.7V$ , Load 7pF (stray plus probes).

- 8. C<sub>L</sub> includes probe and fixture capacitance.

- 9. Generator waveform for all tests unless otherwise specified: f = 25 MHz,  $Z_0 = 50$  ohms,  $t_r = 1$ ns,  $t_f = 1$ ns (35%-65%). To ensure fastest propagation delay and minimum skew, clock input edge rates should not be slower than 1ns/V; control signals not slower than 3ns/V.

#### **Parameter Measurement Information**

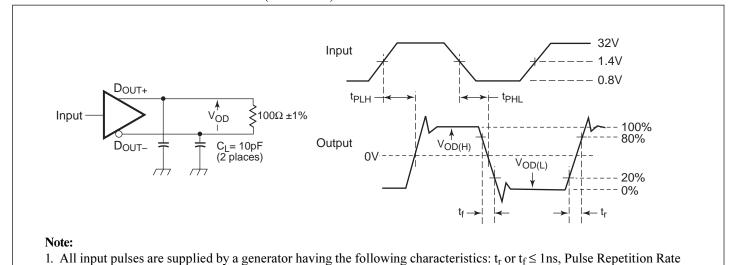

Figure 1. Voltage and Current Definitions

Figure 2. Vop Test Circuit

#### Note:

1. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$ ns, Pulse Repetition Rate (PRR) = 50 Mpps, Pulse width =  $10 \pm 0.2$ ns.  $C_L$  includes instrumentation and fixture capacitance within 0.06m of the D.U.T. The measurement of VOC(PP) is made on test equipment with a -3dB bandwidth of at least 300MHz.

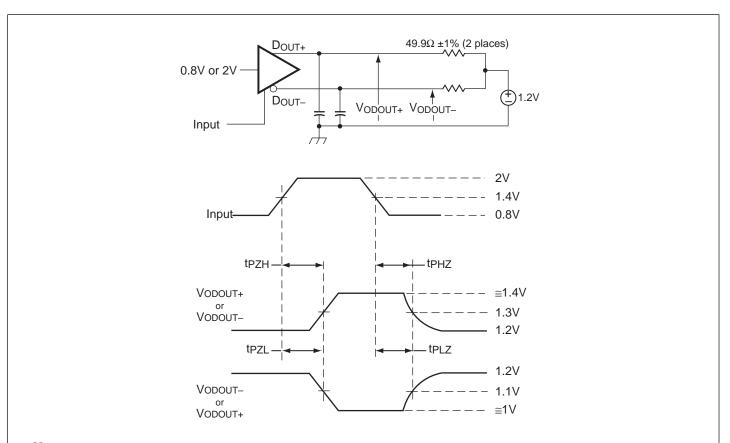

$Figure 3. \, Test \, Circuit \, \& \, Definitions \, for \, the \, Driver \, Common-Mode \, Output \, Voltage \,$

4

PS8535A 09/11/01

### Parameter Measurement Information (continued)

### Figure 4. Test Circuit, Timing, & Voltage Definitions for the Differential Output Signal

(PRR) = 15 Mpps, Pulse width  $= 10 \pm 0.2 \text{ns}$ .  $C_L$  includes instrumentation and fixture capacitance within 0.06m of the D.U.T.

#### Note:

1. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$ ns, Pulse Repetition Rate (PRR) = 0.5 Mpps, Pulse width  $= 500 \pm 10$ ns.  $C_L$  includes instrumentation and fixture capacitance within 0.06m of the D.U.T.

Figure 5. Enable & Disable Time Circuit & Definitions

5

Figure 6. Cycle-to-Cycle Jitter

Figure 7. Period Jitter

6

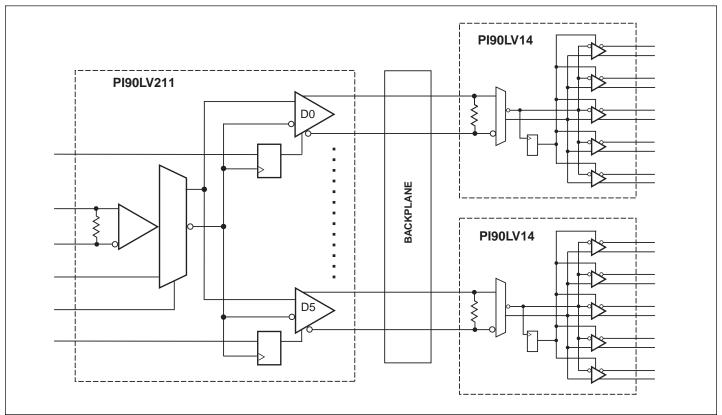

### **General Description**

The PI90LV211 is a 1:6 fanout tree designed explicitly for low-skew, high-speed clock distribution. The device was targeted to work in conjunction with the PI90LV14 device to provide another level of flexibility in the design and implementation of clock distribution trees. The individual synchronous enable controls and multiplexed clock inputs make the device ideal as the first level distribution unit in a distribution tree. The device provides the ability to distribute a lower speed scan or test clock along with the high-speed system clock to ease the design of system diagnostics and self test procedures. The individual enables could be used to allow for the disabling of individual cards on a backplane in fault tolerant designs.

#### Handling Open Inputs and Outputs

With the simultaneous switching characteristics and the tight skew specifications of the P90LV211, the handling of the unused outputs becomes critical. To minimize the noise generated on the die all outputs should be terminated in pairs, i.e. both the true and compliment outputs should be terminated even if only one of the outputs will be used in the system. With both complimentary pairs terminated, the current in the  $V_{CC}$  pins will remain essentially constant and thus inductance induced voltage glitches on  $V_{CC}$  will not occur.  $V_{CC}$  glitches will result in distorted output waveforms and degradations in the skew performance of the device.

The package parasitics of the 28-lead package cause the signals on a given pin to be influenced by signals on adjacent pins. PI90LV211

is characterized and tested with all of the outputs switching, therefore the numbers in the data book are guaranteed only for this situation. If all of the outputs of the PI90LV211 are not needed and there is a desire to save power, the unused output pairs can be left unterminated. Unterminated outputs can influence the propagation delay on adjacent pins by 15ps–20ps. Therefore, under these conditions, this 15ps–20ps needs to be added to the overall skew of the device. Pins which are separated by a package corner are not considered adjacent pins in the context of propagation delay influence. Therefore if all of the outputs on a single side of the package are terminated, the specification limits in the data sheet will apply.

#### Using the Enable Pins

Both the common enable  $(\overline{\text{CEN}})$  and the individual enables (ENx) are synchronous to the CLK or SCLK input depending on which is selected. The active low signals are clocked into the enable flip flops on the negative edges of the PI90LV211 clock inputs. In this way, the devices will only be disabled when the outputs are already in the LOW state. The internal propagation delays are such that the delay to the output through the distribution buffers is less than that through the enable flip flops. This will ensure that the disabling of the device will not slice any time off the clock pulse. On initial power up, the enable flip flops will randomly attain a stable state; therefore precautions should be taken on initial power up to ensure the PI90LV211 is in the desired state.

Figure 8. Standard PI90LV211 LVDS Application

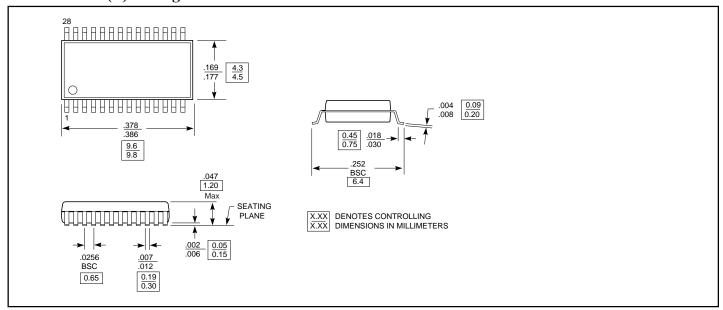

### 28-Pin TSSOP (L) Package

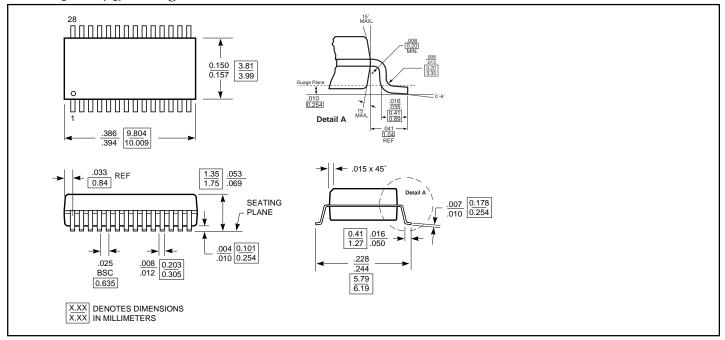

### 28-Pin QSOP (Q) Package

### **Ordering Information**

| Ordering Code | Package Type         | Operating Range |  |  |

|---------------|----------------------|-----------------|--|--|

| PI90LV211L    | 28-pin 173-mil TSSOP | -40°C to 85°C   |  |  |

| PI90LV211Q    | 28-pin 150-mil TSSOP | -40 C to 83 C   |  |  |

#### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com