### Precision 1-13 Clock Buffer

### **Product Features**

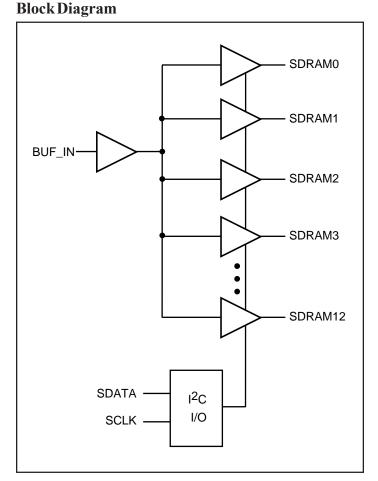

- High speed, low noise non-inverting 1-13 buffer

- Supports up to four SDRAM DIMMs

- Low skew (< 250ps) between any two output clocks

- I<sup>2</sup>C Serial Configuration interface

- Multiple V<sub>DD</sub>, V<sub>SS</sub> pins for noise reduction

- 3.3V power supply voltage

- Separate Hi-Z pin for testing

- 28-pin SSOP and SOIC packages (H, S)

### **Description**

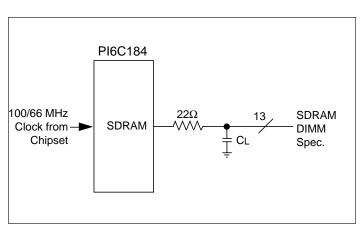

The PI6C184 is a high-speed low-noise 1-13 non-inverting buffer designed for SDRAM clock buffer applications.

This buffer is intended to be used with the PI6C104 clock generator for Intel Architecture for both desktop and mobile systems.

At power up all SDRAM output are enabled and active. The I<sup>2</sup>C Serial control may be used to individually activate/deactivate any of the 13 output drivers.

### Note:

Purchase of I<sup>2</sup>C components from Pericom conveys a license to use them in an I<sup>2</sup>C system as defined by Philips.

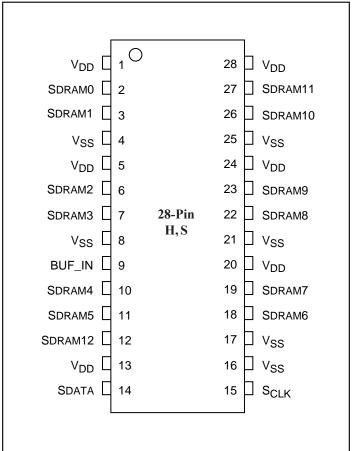

### **Pin Configuration**

# **Pin Description**

| Pin                 | Symbol          | Type   | Quantit- | Description                                                                    |

|---------------------|-----------------|--------|----------|--------------------------------------------------------------------------------|

| 2,3,6,7,10,11,18,19 | SDRAM [0.7]     | 0      | 8        | SDRAM Byte 0 clock output                                                      |

| 26,27,12            | SDRAM [10.12]   | 0      | 3        | SDRAM Byte 1 clock output                                                      |

| 22,23               | SDRAM [8.9]     | 0      | 2        | SDRAM Byte 2 clock output                                                      |

| 9                   | BUF_IN          | 1      | 1        | Input for 1-13-buffer                                                          |

| 14                  | SDATA           | I/O    | 1        | Data pin for I <sup>2</sup> C circuitry. Has a 100k Internal pull-up resistor  |

| 15                  | SCLK            | I/O    | 1        | Clock pin for I <sup>2</sup> C circuitry. Has a 100k Internal pull-up resistor |

| 1,5,13,20,24,28     | V <sub>DD</sub> | Power  | 6        | 3.3V power supply for SDRAM buffer                                             |

| 4,8,16,17,21,25     | V <sub>SS</sub> | Ground | 6        | Ground for SDRAM Buffers                                                       |

# PI6C184 Serial Configuration Map

Byte0: SDRAM Active/Inactive Register (1 = enable, 0 = disable)

| Bit   | Pin # | Description              |

|-------|-------|--------------------------|

| Bit 7 | 19    | SDRAM7 (Active/Inactive) |

| Bit 6 | 18    | SDRAM6 (Active/Inactive) |

| Bit 5 | 11    | SDRAM5 (Active/Inactive) |

| Bit 4 | 10    | SDRAM4 (Active/Inactive) |

| Bit 3 | 7     | SDRAM3 (Active/Inactive) |

| Bit 2 | 6     | SDRAM2 (Active/Inactive) |

| Bit 1 | 3     | SDRAM1 (Active/Inactive) |

| Bit 0 | 2     | SDRAM0 (Active/Inactive) |

### Note:

Inactive means outputs are held LOW and are disabled from switching

# PI6C184 I<sup>2</sup>C Address Assignment

|   | <b>A6</b> | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

|---|-----------|----|----|----|----|----|----|-----|

| I | 1         | 1  | 0  | 1  | 0  | 0  | 1  | 0   |

# 2-Wire I<sup>2</sup>C Control

The I<sup>2</sup>C interface permits individual enable/disable of each clock output and test mode enable.

The PI6C184 is a slave receiver device. It can not be read back. Sub addressing is not supported. All preceding bytes must be sent in order to change one of the control bytes.

Every bite put on the SDATA line must be 8-bits long (MSB first), followed by an acknowledge bit generated by the receiving device. During normal data transfers SDATA changes only when SCLK is LOW. Exceptions: A HIGH to LOW transition on SDATA while SCLK is HIGH indicates a "start" condition. A LOW to HIGH transition on SDATA while SCLK is HIGH is a "stop" condition and indicates the end of a data transfer cycle.

Each data transfer is initiated with a start condition and ended with

Byte1: SDRAM Active/Inactive Register (1 = enable, 0 = disable)

| Bit   | Pin # | Description               |

|-------|-------|---------------------------|

| Bit 7 |       | NC (Initialize to 0)      |

| Bit 6 |       | NC (Initialize to 0)      |

| Bit 5 |       | NC (Initialize to 0)      |

| Bit 4 |       | NC (Initialize to 0)      |

| Bit 3 |       | NC (Initialize to 0)      |

| Bit 2 | 12    | SDRAM12 (Active/Inactive) |

| Bit 1 | 27    | SDRAM11(Active/Inactive)  |

| Bit 0 | 26    | SDRAM10 (Active/Inactive) |

a stop condition. The first byte after a start condition is always a 7-bit address byte followed by a read/write bit. (HIGH=read from addressed device, LOW=write to addressed device). If the device's own address is detected, PI6C184 generates an acknowledge by pulling SDATA line LOW during ninth clock pulse, then accepts the following data bytes until another start or stop condition is detected.

Following acknowledgement of the address byte (D2), two more bytes must be sent:

- 1. "Command Code" byte, and

- 2. "Byte Count" byte.

Although the data bits on these two bytes are "don't care," they must be sent and acknowledged.

Byte2: Optional Register for Possible Future Requirements (1 = enable, 0 = disable)

| Bit   | Pin # | Description              |

|-------|-------|--------------------------|

| Bit 7 | 23    | SDRAM9 (Active/Inactive) |

| Bit 6 | 22    | SDRAM8 (Active/Inactive) |

| Bit 5 | -     | (Reserved)               |

| Bit 4 | -     | (Reserved)               |

| Bit 3 | -     | (Reserved)               |

| Bit 2 | -     | (Reserved)               |

| Bit 1 | -     | (Reserved)               |

| Bit 0 | -     | (Reserved)               |

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                    |  |

|------------------------------------------------------|--|

| Ambient Temperature with Power Applied0°C to +70°C   |  |

| 3.3V Supply Voltage to Ground Potential0.5V to +4.6V |  |

| DC Input Voltage0.5V to +4.6V                        |  |

| - r                                                  |  |

### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Supply Current** ( $V_{DD}$ =+3.465V, $C_{LOAD}$ =Max.)

| Symbol      | Parameter      | Test Condition     | Min. | Тур. | Max. | Units |

|-------------|----------------|--------------------|------|------|------|-------|

| $I_{ m DD}$ | Supply Current | BUF_IN = 0 MHz     |      |      | 3    |       |

| $I_{ m DD}$ | Supply Current | BUF_IN = 66.66 MHz |      |      | 230  | mA    |

| $I_{DD}$    | Supply Current | BUF_IN = 100.0 MHz |      |      | 360  |       |

3

# $\textbf{DC Operating Specifications} \, (V_{DD} = +3.3 \, \mathrm{V} \pm 5\%, T_A = 0 ^{\circ}\mathrm{C} - 70 ^{\circ}\mathrm{C})$

| Symbol                   | Parameter                    | Test Condition                      | Min.                 | Max.                 | Units |  |

|--------------------------|------------------------------|-------------------------------------|----------------------|----------------------|-------|--|

| Input Voltage            |                              |                                     |                      |                      |       |  |

| V <sub>IH</sub>          | Input high voltage           | V <sub>DD</sub>                     | 2.0                  | V <sub>DD</sub> +0.3 | V     |  |

| V <sub>IL</sub>          | Input low voltage            |                                     | V <sub>SS</sub> -0.3 | 0.8                  | v     |  |

| $I_{\mathrm{IL}}$        | Input leakage current        | $0 < V_{IN} < V_{DD}$               | -5                   | +5                   | mA    |  |

| $V_{DD}[0-9] = 3.3V \pm$ | $V_{DD}[0-9] = 3.3V \pm 5\%$ |                                     |                      |                      |       |  |

| V <sub>OH</sub>          | Output high voltage          | oltage $I_{OH} = -1 \text{ mA}$ 2.4 |                      |                      | V     |  |

| V <sub>OL</sub>          | Output low voltage           | $I_{OL} = 1 \text{mA}$              |                      | 0.4                  | V     |  |

| C <sub>OUT</sub>         | Output pin capacitance       |                                     |                      | 6                    | n E   |  |

| $C_{ m IN}$              | Input pin capacitance        |                                     |                      | 5                    | pF    |  |

| L <sub>PIN</sub>         | Pin Inductance               |                                     |                      | 7                    | nН    |  |

| $T_{A}$                  | Ambient Temperature          | No Airflow                          | 0                    | 70                   | °C    |  |

# SDRAM Clock Buffer Operating Specification

| Symbol                | Parameter                        | Test Conditions      | Min. | Тур. | Max. | Units |

|-----------------------|----------------------------------|----------------------|------|------|------|-------|

| I <sub>OHMIN</sub>    | Pull-up current                  | $V_{OUT} = 2.0V$     | -54  |      |      |       |

| I <sub>OHMAX</sub>    | Pull-up current                  | $V_{OUT} = 3.135V$   |      |      | -46  | A     |

| I <sub>OLMIN</sub>    | Pull-down current                | $V_{OUT} = 1.0V$     | 54   |      |      | mA    |

| I <sub>OLMAX</sub>    | Pull-down current                | $V_{OUT} = 0.4V$     |      |      | 53   |       |

| t <sub>RH</sub> SDRAM | Output rise edge rate SDRAM only | 3.3V ±5% @ 04V-2.4V  | 1.5  |      | 4    | Mag   |

| t <sub>TH</sub> SDRAM | Output fall edge rate SDRAM only | 3.3V ±5% @ 2.4V-0.4V | 1.5  |      | 4    | V/ns  |

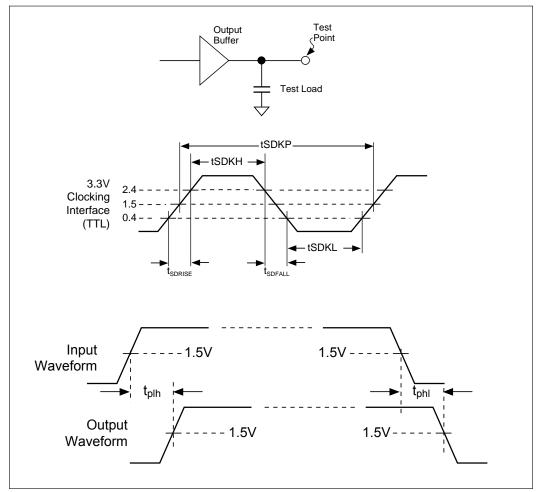

# **ACTiming**

| Carrello I                         | Downwooder                        | 66 MHz |      | 100  | II   |        |

|------------------------------------|-----------------------------------|--------|------|------|------|--------|

| Symbol                             | Parameter                         | Min.   | Max. | Min. | Max. | Units  |

| t <sub>SDKP</sub>                  | SDRAM CLK period                  | 15.0   | 15.5 | 10.0 | 10.5 |        |

| t <sub>SDKH</sub>                  | SDRAM CLK high time               | 5.6    |      | 3.3  |      | ns     |

| t <sub>SDKL</sub>                  | SDRAM CLK low time                | 5.3    |      | 3.1  |      |        |

| t <sub>SDRISE</sub>                | SDRAM CLK rise time               | 1.5    | 4.0  | 1.5  | 4.0  | - V/ns |

| t <sub>SDFALL</sub>                | SDRAM CLK fall time               | 1.5    | 4.0  | 1.5  | 4.0  | V/IIS  |

| t <sub>PLH</sub>                   | SDRAM Buffer LH propagation delay | 1.0    | 5.0  | 1.0  | 5.0  |        |

| t <sub>PHL</sub>                   | SDRAM Buffer HL propagation delay | 1.0    | 5.0  | 1.0  | 5.0  |        |

| t <sub>PZL</sub> ,t <sub>PZH</sub> | SDRAM Buffer Enable delay         | 1.0    | 8.0  | 1.0  | 8.0  | ns     |

| t <sub>PLZ</sub> ,t <sub>PHZ</sub> | SDRAM Buffer Disable delay        | 1.0    | 8.0  | 1.0  | 8.0  |        |

| Duty Cycle                         | Measured at 1.5V                  | 45     | 55   | 45   | 55   | %      |

| t <sub>SDSKW</sub>                 | SDRAM Output to Output Skew       |        | 250  |      | 250  | ps     |

Figure 1. Clock Waveforms

### Minimum and Maximum Expected Capacitive Loads

| Clock | Min. Load | Max. Load | Units | Notes                    |

|-------|-----------|-----------|-------|--------------------------|

| SDRAM | 20        | 30        | pF    | SDRAM DIMM Specification |

#### Notes:

- 1. Maximum rise/fall times are guaranteed at maximum specified load.

- 2. Minimum rise/fall times are guaranteed at minimum specified load.

- 3. Rise/fall times are specified with pure capacitive load as shown. Testing is done with an additional  $500\Omega$  resistor in parallel.

### **Design Guidelines to Reduce EMI**

- 1. Place series resistors and CI capacitors as close as possible to the respective clock pins. Typical value for CI is 10pF. Series resistor value can be increased to reduce EMI provided that the rise and fall time are still within the specified values.

- 2. Minimize the number of "vias" of the clock traces.

- 3. Route clock traces over a continuous ground plane or over a continuous power plane. Avoid routing clock traces from plane to plane (refer to rule #2).

5

4. Position clock signals away from signals that go to any cables or any external connectors.

PS8320A 10/14/02

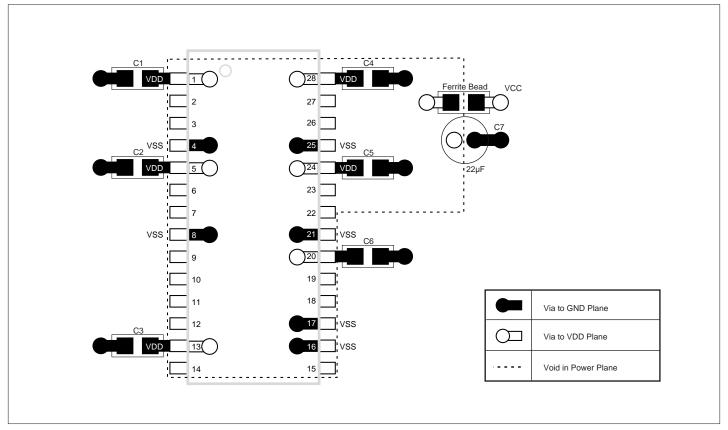

# **PCB Layout Suggestion**

6

### Note:

This is only a suggested layout. There may be alternate solutions depending on actual PCB design and layout.

As a general rule, C1-C7 should be placed as close as possible to their respective  $V_{DD}$ .

Recommended capacitor values: C1-C7 ........... 0.1µF, ceramic

C8 ......  $22\mu F$

Figure 2. Design Guidelines

PS8320A 10/14/02

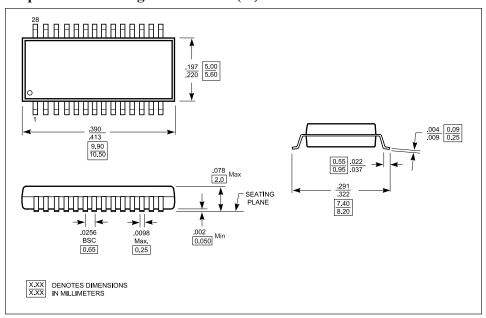

### 28-pin SSOP Package Mechanical (H)

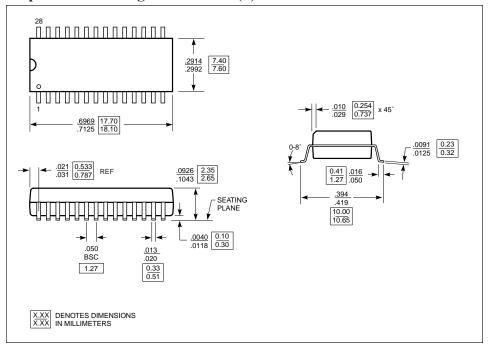

### 28-pin SOIC Package Mechanical (S)

# **Ordering Information**

| P/N      | Description         |

|----------|---------------------|

| PI6C184H | 28-pin SSOP Package |

| PI6C184S | 28-pin SOIC Package |

### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com