# PC7410 PowerPC<sup>™</sup> Microprocessor Fact Sheet

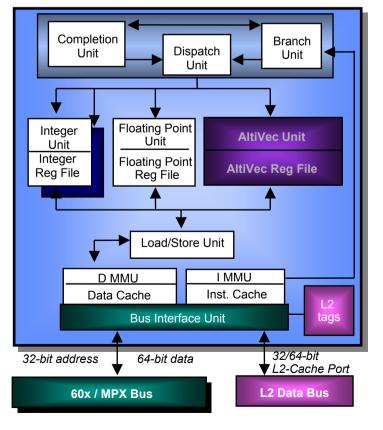

The MPC7410 PowerPC<sup>TM</sup> microprocessor is a high-performance, low-power, 32-bit implementation of the PowerPC RISC architecture combined with a full 128-bit implementation of Motorola's AltiVec<sup>TM</sup> technology. This creates a microprocessor ideal for leading-edge computing, embedded network control, and signal processing applications. The MPC7410 offers the high-bandwidth MPX bus with minimized signal setup times and reduced idle cycles to increase maximum operating frequency to over 100 MHz, in addition to increased address and data bus bandwidth. To maintain compatibility for existing designs, the MPC7410 also supports the 60x bus protocol. MPC7410 microprocessors offer single-cycle double precision floating-point performance, full symmetric multi-processing, (SMP) capabilities, and support for up to 2MB of backside L2 cache. While the MPC7410 is software-compatible with existing PowerPC 603e, 740, and 750 microprocessors, to utilize the full potential of the AltiVec technology changes to existing source code is required.

# AltiVec Technology

AltiVec Technology expands the capabilities of PowerPC microprocessors by providing leading-edge, general-purpose processing performance while concurrently addressing high-bandwidth data processing and algorithmic-intensive computations in a single-chip solution. AltiVec technology:

- Meets the computational demands of networking infrastructure such as multichannel modems, echo cancellation equipment, and basestation processing.

- Enables faster, more secure encryption methods optimized for the SIMD processing model

- Provides compelling performance for multimedia-oriented desktop computers, desktop publishing, and digital video processing.

- Enables real-time processing of the most demanding data streams (MPEG-2 encode, continuous speech recognition, real-time thigh-resolution 3D graphics, etc...)

## **PC7410 Main Features**

## • Eight independent execution units :

- Two integer units

- Double precision floating-point unit

- Vector permit unit

- Vector arithmetic logic unit

- Load/store unit

- System unit

- Branch processing unit

## • Cache and MMU support :

- 32-Kbytes physically -addressed instruction and data caches

- 8 way set-associative

- Dedicated L2 cache interface with on-chip L2 tags

- Separate MMUs for instructions and data

- Virtual memory support up to 4 Petabytes (2)<sup>52</sup>

- Real memory support up to 4 Gigabytes  $(2)^{32}$

- 128 entry instructions and data TLBs

## Bus Interface

- Compatible with 60x interface

- Support the MPX bus architecture

- 32-bit address bus

- 64- bit data bus

- 12 Bus-to-Core frequency multiplier

- Selectable interface voltages of 1.8 V or 2.5 V

### Power Management

- Selectable 1.8 V interface voltage to reduce power in output buffers

- 3 static power saving modes : doze, nap and sleep

- Dynamic power management on decode

- Full symmetric multiprocessing (MERSI) capability

- Integrated thermal management unit (with software interrupt)

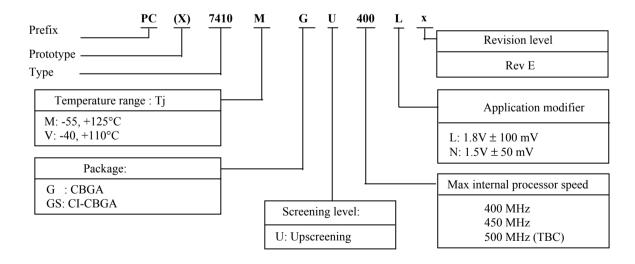

#### Packaging

- 360 pin CBGA & CI-CGA

### Screening

- CBGA upscreening base upon Atmel -Grenoble standards

- Full military temperature range ( $Tj = -55^{\circ}C + 125^{\circ}C$ )

- Industrial temperature range (Tj =  $-40^{\circ}C + 110^{\circ}C$ )

| CPU Summary                    | PC7410                                                      |

|--------------------------------|-------------------------------------------------------------|

|                                | 400 – 450 MHz                                               |

| Die Revision                   | 1.4 = E                                                     |

| CPU Speeds - Internal          | 400 MHz                                                     |

|                                | 450 MHz                                                     |

| CPU Bus Dividers               | 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x,<br>7.5x, 8x, 9x |

| Bus Interface                  | 32-bit address, 64-bit data                                 |

| Instructions per Clock         | 3 (2+Branch)                                                |

| L1 Cache                       | 32-KB Instruction and Data                                  |

| L2 Cache                       | 512KB, 1MB, 2MB                                             |

| Core-to-L2 Frequency Divisions | 1:1, 1.5:1, 2:1, 2.5:1, 3:1, 3.5:1, 4:1                     |

| Typ/Max Power Dissipation      | est. 6.0W @ 500 MHz                                         |

| Die Size                       | 52 mm²                                                      |

| Package                        | 360-pin Flip-Chip PBGA                                      |

|                                | Ceramic Package if Identifications                          |

| Process                        | 0.15 µ CMOS, 5LM                                            |

| Voltage                        | 1.8/2.5/3.3V I/O                                            |

|                                | 1.8V internal                                               |

| SPECint95 (estimated)          | 22.8 @ 500 MHz                                              |

| SPECfp95 (estimated)           | 17.0 @ 500 MHz                                              |

| Other Performance              | 917 MIPS @ 500 MHz                                          |

| atus                           | Preview                                                     |

| Samples                        | 3Q/2001                                                     |

| Production                     | 4Q/2001                                                     |

|                                | Integer (2)                                                 |

|                                | Floating Point Unit                                         |

|                                | Vector Unit                                                 |

| Execution Units                | Branch Unit                                                 |

|                                | Load/Store Unit                                             |

|                                | System Register                                             |

For additional information and product availability: contact your local ATMEL-Grenoble representative or visit our web site at http://www.atmel.com

You may also contact the PowerPC technical hotline at std.hotline@gfo.atmel.com

The PowerPC and PowerPC603e names and the PowerPC logotype are trademarks of International Business Machines Corporation, used under licence therefrom.