# dsPIC30F

# dsPIC<sup>™</sup> High Performance 16-bit Digital Signal Controller Family Overview

# High Performance Modified RISC CPU:

- Modified Harvard architecture

- C compiler optimized instruction set architecture

- 89 base instructions

- 24-bit wide instructions, 16-bit wide data path

- Linear program memory addressing up to 4M Instruction Words

- · Linear data memory addressing up to 64 Kbytes

- Up to 144 Kbytes on-chip FLASH program space

- Up to 48K Instruction Words

- Up to 8 Kbytes of on-chip data RAM

- Up to 4 Kbytes of non-volatile data EEPROM

- 16 x 16-bit working register array

- Three Address Generation Units that enable:

- Dual data fetch

- Accumulator writeback for DSP operations

- Flexible addressing modes supporting:

- Indirect, Modulo and Bit-Reversed modes

- Two, 40-bit wide accumulators with optional saturation logic

- 16-bit x 16-bit single cycle hardware fractional/ integer multiplier

- Single cycle Multiply-Accumulate (MAC) operation

- 40-stage Barrel Shifter

- Up to 30 MIPs operation:

- DC to 40 MHz External Clock Input mode

- 4 MHz 10 MHz Crystal mode with PLL active (4X, 8X, 16X)

- Up to 45 interrupt sources

- 7 user selectable priority levels

- 8 processor exceptions and software traps

- Vector table with up to 62 vectors

# Peripheral Features (see Note 1):

- High current sink/source I/O pins: 25 mA/25 mA

- Up to 5 external interrupt sources

- Timer module with programmable prescaler:

- Up to five 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- Dual Compare mode available

#### **Peripheral Features (Continued):**

- Data Converter Interface (DCI), supports common audio CODEC protocols, including I<sup>2</sup>S and AC'97

- 3-wire SPI<sup>™</sup> modules (supports 4 SPI modes and Frame Sync mode)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Addressable UART modules supporting:

- Interrupt-on-address bit

- Wake-up-on-START bit

- 4 characters deep TX and RX FIFO buffers

- CAN bus modules

- As many as 54 programmable digital I/O pins

- Some with interrupt-on-change (up to 24)

**Note 1:** Refer to Table 1-1, Table 1-2 and Table 2-1 for exact peripheral features per device.

#### **Advanced Analog Features:**

- 10-bit Analog-to-Digital Converters (A/D) with:

- 16 input channels, typically

- 500 ksps conversion rate

- Automated input scanning

- 2 or 4 simultaneous samples

- Conversion available during SLEEP

- 12-bit Analog-to-Digital Converters (A/D) with:

- 16 input channels, typically

- 100 ksps conversion rate

- Automated input scanning

- Conversion available during SLEEP

- Programmable Low Voltage Detection (LVD)

- Supports interrupt on low voltage detection

- Programmable Brown-out Reset generation

#### Motor Control PWM Module Features:

- · Up to 8 PWM output channels

- Complementary or Independent Output modes

- Edge and Center Aligned modes

- 4 duty cycle generators

- Dedicated time-base with 4 modes

- Programmable output polarity

- · Dead-time control for Complementary mode

- Manual output control

- Trigger for A/D conversions

# Quadrature Encoder Interface Module Features:

- Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- · Count direction status

- Position measurement (x2 and x4) mode

- Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

#### **Special Microcontroller Features:**

- Enhanced FLASH program memory

- 100,000 write/erase cycle (typical) for industrial temperature range

- Data EEPROM memory

- 1,000,000 write/erase cycle (typical) industrial temperature range

- Data EEPROM Retention > 20 years

- Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low power RC oscillator for reliable operation

# Special Microcontroller Features (Continued):

- · Fail safe clock monitor operation

- Detects clock failure and switches to on-chip 8 MHz RC oscillator

- Programmable code protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via 3 pins and power/ground

- Selectable Power Management modes

- SLEEP, IDLE and Alternate Clock modes

# **CMOS Technology:**

- · Low power, high speed FLASH technology

- Fully static design

- Wide operating voltage range (2.5V to 5.5V)

- · Industrial and extended temperature ranges

- Low power consumption

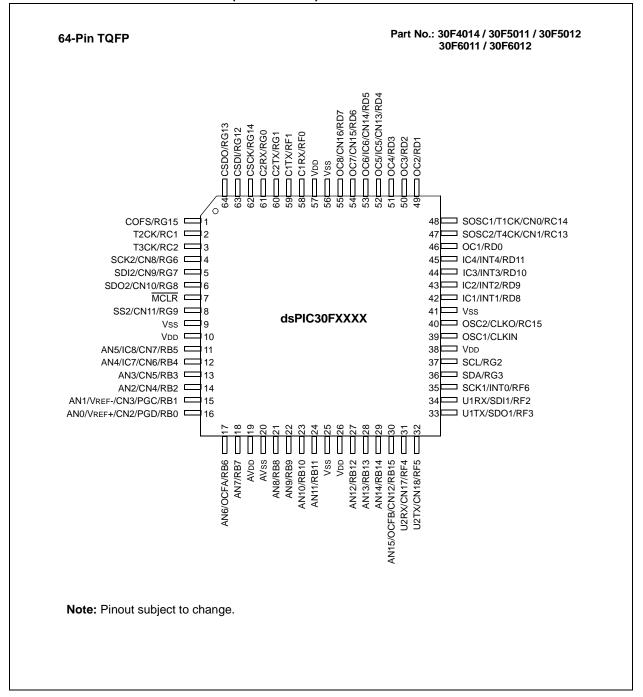

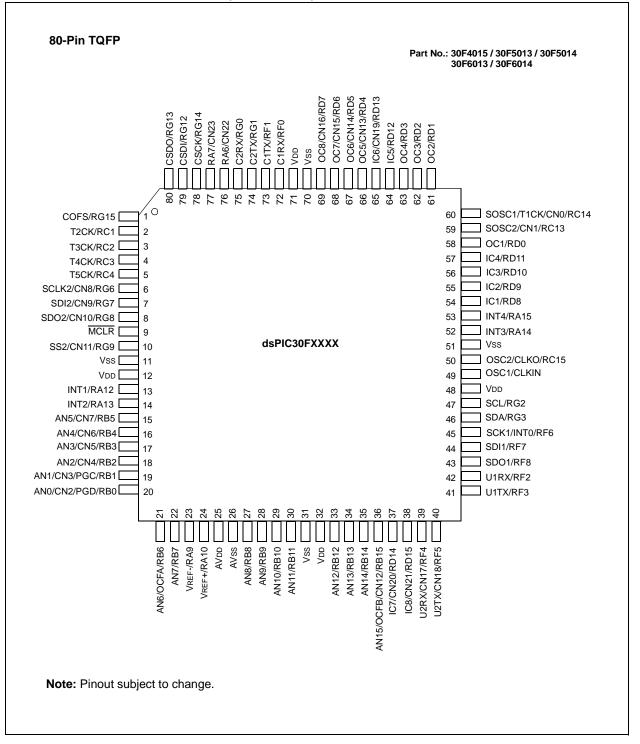

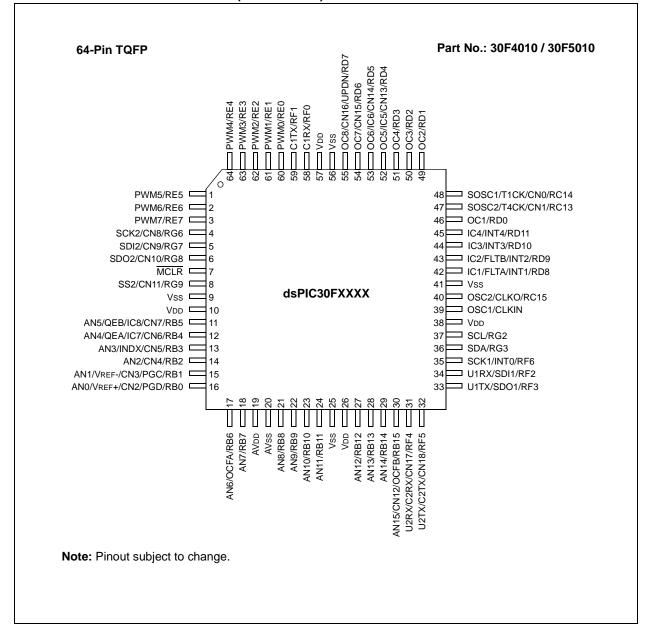

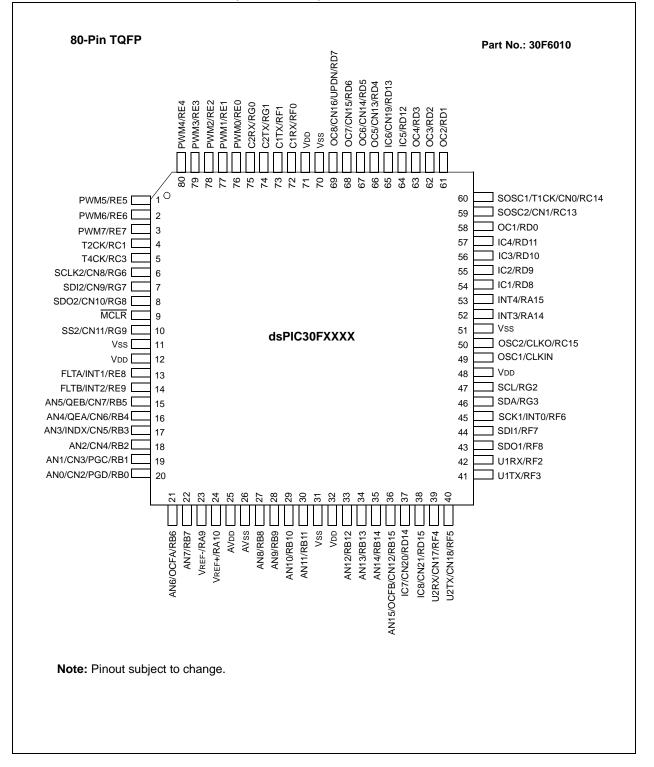

#### Packaging:

- 80-pin TQFP

- 64-pin TQFP

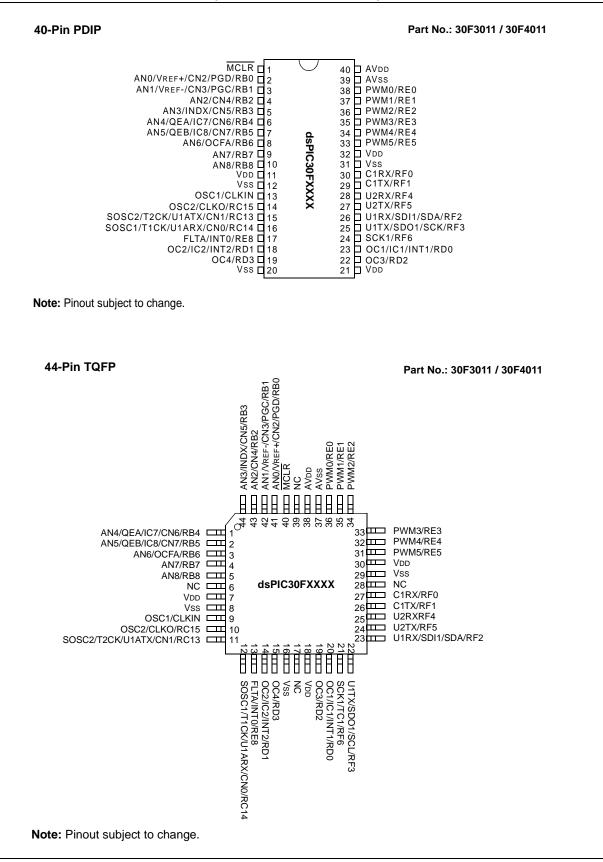

- 40-pin DIP, 44-pin TQFP

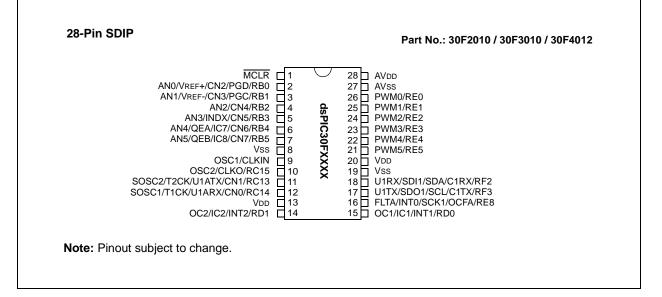

- 28-pin DIP (300 mil), 28-pin SOIC

- 18-pin DIP (300 mil), 18-pin SOIC

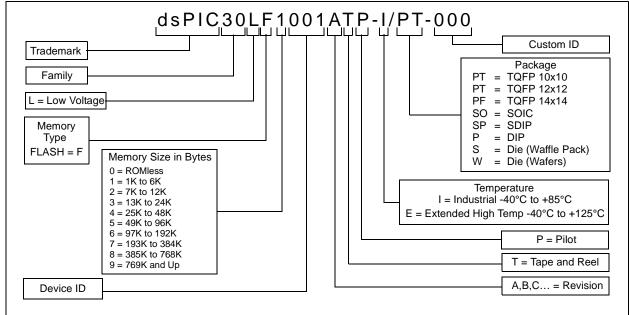

The following figure defines the part number structure.

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

# 1.0 GENERAL PURPOSE AND SENSOR FAMILY PRODUCT INFORMATION

| Device       | Pins | Progra | am Memory    | SRAM  | EEPROM |        | Input | Output Comp/ | A/D 12-bit | UART | SPI™ | I²C™             |

|--------------|------|--------|--------------|-------|--------|--------|-------|--------------|------------|------|------|------------------|

| 201100       |      | Bytes  | Instructions | Bytes | Bytes  | 16-bit | Сар   | Std PWM      | 100 Ksps   | ٩U   | SF   | l <sup>2</sup> ( |

| dsPIC30F2011 | 18   | 12K    | 4K           | 1024  | 0      | 3      | 2     | 2            | 8 ch       | 1    | 1    | 1                |

| dsPIC30F3012 | 18   | 24K    | 8K           | 2048  | 1024   | 3      | 2     | 2            | 8 ch       | 1    | 1    | 1                |

| dsPIC30F2012 | 28   | 12K    | 4K           | 1024  | 0      | 3      | 2     | 2            | 10 ch      | 1    | 1    | 1                |

| dsPIC30F3013 | 28   | 24K    | 8K           | 2048  | 1024   | 3      | 2     | 2            | 10 ch      | 2    | 1    | 1                |

#### TABLE 1-1: dsPIC30F SENSOR PROCESSOR FAMILY VARIANTS

### TABLE 1-2: dsPIC30F GENERAL PURPOSE CONTROLLER FAMILY

| Dovice         | Device Pins - |       | SRAM EEPROM Tim | Timer Input Output Comp/ |       | Codec A/D<br>12-bit |     | UART    | SPI™                      | l²C™               | CAN |    |                  |   |

|----------------|---------------|-------|-----------------|--------------------------|-------|---------------------|-----|---------|---------------------------|--------------------|-----|----|------------------|---|

| Device         | PINS          | Bytes | Instructions    | Bytes                    | Bytes | 16-bit              | Сар | Std PWM | Interface                 | 12-bit<br>100 Ksps | NA  | SP | l <sup>2</sup> C | C |

| dsPIC30F3014** | 40/44         | 24K   | 8K              | 2048                     | 1024  | 3                   | 2   | 2       | -                         | 13 ch              | 2   | 1  | 1                | - |

| dsPIC30F4013** | 40/44         | 48K   | 16K             | 2048                     | 1024  | 5                   | 4   | 4       | AC97,<br>I <sup>2</sup> S | 13 ch              | 2   | 1  | 1                | 1 |

| dsPIC30F4014** | 64            | 36K   | 12K             | 2048                     | 1024  | 5                   | 8   | 8       | AC97,<br>I <sup>2</sup> S | 16 ch              | 2   | 2  | 1                | 1 |

| dsPIC30F5011   | 64            | 66K   | 22K             | 4096                     | 1024  | 5                   | 8   | 8       | -                         | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F5012   | 64            | 96K   | 32K             | 4096                     | 2048  | 5                   | 8   | 8       | AC97,<br>I <sup>2</sup> S | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F6011   | 64            | 132K  | 44K             | 6144                     | 2048  | 5                   | 8   | 8       | -                         | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F6012   | 64            | 144K  | 48K             | 8192                     | 4096  | 5                   | 8   | 8       | AC97,<br>I <sup>2</sup> S | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F4015** | 80            | 36K   | 12K             | 2048                     | 1024  | 5                   | 8   | 8       | AC97,<br>I <sup>2</sup> S | 16 ch              | 2   | 2  | 1                | 1 |

| dsPIC30F5013   | 80            | 66K   | 22K             | 4096                     | 1024  | 5                   | 8   | 8       | -                         | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F5014   | 80            | 96K   | 32K             | 4096                     | 2048  | 5                   | 8   | 8       | AC97,<br>I <sup>2</sup> S | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F6013   | 80            | 132K  | 44K             | 6144                     | 2048  | 5                   | 8   | 8       | -                         | 16 ch              | 2   | 2  | 1                | 2 |

| dsPIC30F6014   | 80            | 144K  | 48K             | 8192                     | 4096  | 5                   | 8   | 8       | AC97,<br>I <sup>2</sup> S | 16 ch              | 2   | 2  | 1                | 2 |

\*\* Proposed Products (others are committed)

# dsPIC30F

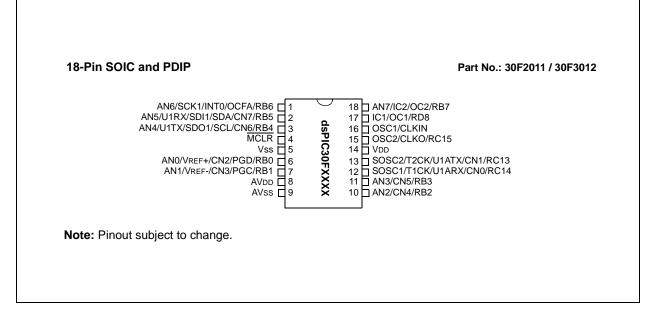

#### FIGURE 1-1: PIN DIAGRAMS (18-Pin SOIC, 18-Pin PDIP)

# 2.0 MOTOR CONTROL FAMILY PRODUCT INFORMATION

#### TABLE 2-1:dsPIC30F POWER CONVERSION AND MOTION CONTROL FAMILY VARIANTS

| Device       | Pins  | -    | m Mem.<br>tes/<br>ctions | SRAM<br>Bytes | EEPROM<br>Bytes | Timer<br>16-bit | Input<br>Cap | Output<br>Comp/<br>Std PWM | Motor<br>Cntrl<br>PWM | A/D10-bit<br>500 Ksps | Quad<br>Enc | UART | SPITM | I²C™ | CAN |

|--------------|-------|------|--------------------------|---------------|-----------------|-----------------|--------------|----------------------------|-----------------------|-----------------------|-------------|------|-------|------|-----|

| dsPIC30F2010 | 28    | 12K  | 4K                       | 512           | 1024            | 3               | 4            | 2                          | 6 ch                  | 6 ch                  | 1           | 1    | 1     | 1    | -   |

| dsPIC30F3010 | 28    | 24K  | 8K                       | 1024          | 1024            | 5               | 4            | 2                          | 6 ch                  | 6 ch                  | 1           | 1    | 1     | 1    | -   |

| dsPIC30F4012 | 28    | 48K  | 16K                      | 2048          | 1024            | 5               | 4            | 2                          | 6 ch                  | 6 ch                  | 1           | 1    | 1     | 1    | 1   |

| dsPIC30F3011 | 40/44 | 24K  | 8K                       | 1024          | 1024            | 5               | 4            | 4                          | 6 ch                  | 9 ch                  | 1           | 2    | 1     | 1    | -   |

| dsPIC30F4011 | 40/44 | 48K  | 16K                      | 2048          | 1024            | 5               | 4            | 4                          | 6 ch                  | 9 ch                  | 1           | 2    | 1     | 1    | 1   |

| dsPIC30F4010 | 64    | 36K  | 12K                      | 2048          | 1024            | 5               | 8            | 8                          | 8 ch                  | 16 ch                 | 1           | 2    | 2     | 1    | 1   |

| dsPIC30F5010 | 64    | 96K  | 32K                      | 4096          | 2048            | 5               | 8            | 8                          | 8 ch                  | 16 ch                 | 1           | 2    | 2     | 1    | 2   |

| dsPIC30F6010 | 80    | 144K | 48K                      | 8192          | 4096            | 5               | 8            | 8                          | 8 ch                  | 16 ch                 | 1           | 2    | 2     | 1    | 2   |

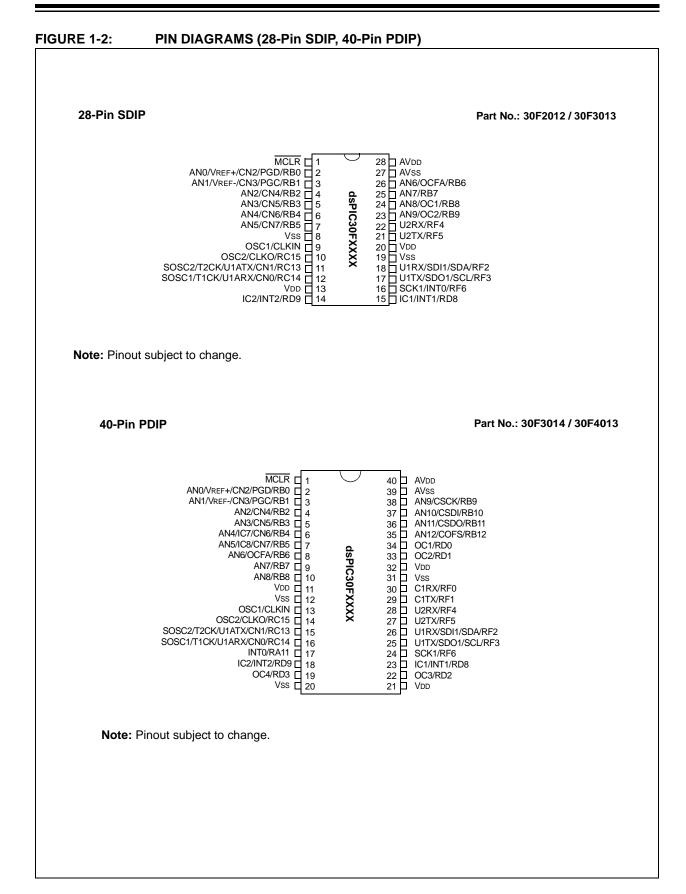

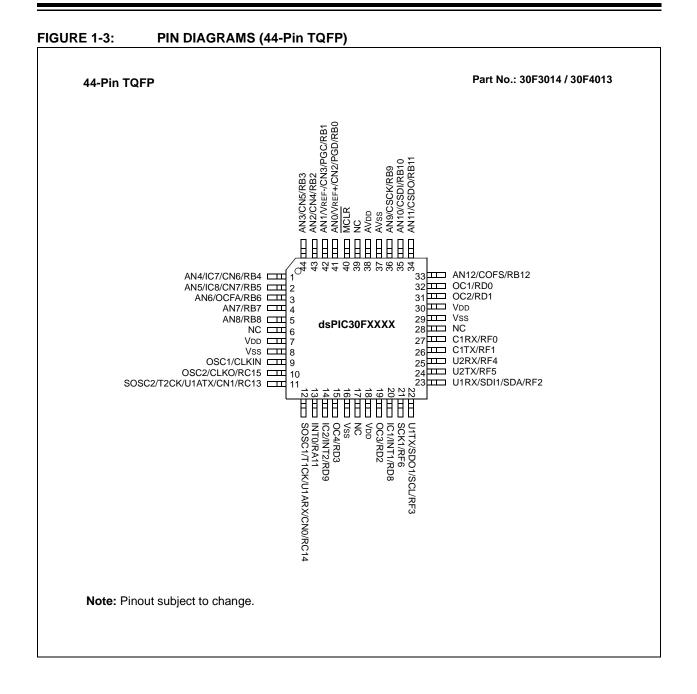

#### FIGURE 2-1: PIN DIAGRAMS (28-Pin SDIP)

#### FIGURE 2-2: PIN DIAGRAMS (40-Pin PDIP, 44-Pin TQFP)

# 3.0 CORE ARCHITECTURE OVERVIEW

### 3.1 Core Overview

The dsPIC30FXXX core is a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The core has a 24-bit instruction word. The Program Counter (PC) is 24-bits wide, with the Least Significant (LS) bit always clear and the Most Significant (MS) bit is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction pre-fetch mechanism is used to help maintain throughput. Unconditional overhead free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The working register array consists of 16 x 16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a software stack pointer for interrupts and calls.

The data space is 64 Kbytes (32K words), and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory, AGU, which combines the X and Y memory into a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts. The X and Y data space boundary is device specific and cannot be altered by the user. Each data word consists of 2 bytes, and most instructions can address data either as words or bytes.

There are two methods of accessing data stored in program memory:

- The upper 32 Kbytes of data space memory can optionally be mapped into the lower half (user space) of program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with the sole limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.

- Linear indirect access of 32K word pages within program space is also possible, using any working register via table read and write instructions. Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (modulo addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms. The X AGU also supports bit-reversed addressing on destination effective addresses, to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect and Register Offset Addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3-operand instructions are supported, allowing C=A+B operations to be executed in a single cycle.

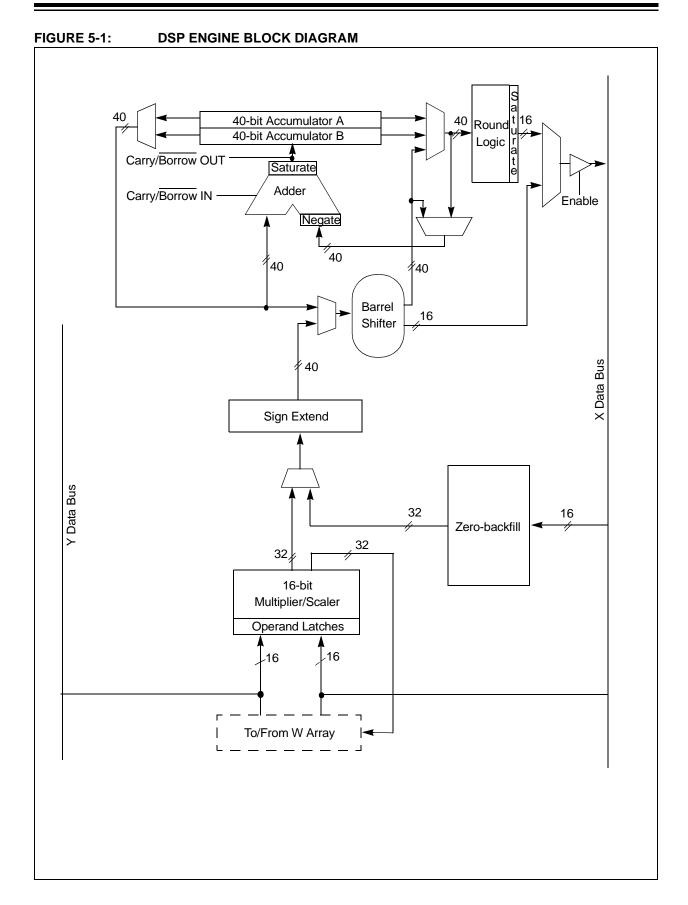

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high speed 16-bit by 16-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bi-directional barrel shifter. Data in the accumulator, or any working register, can be shifted up to 15 bits right or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory while multiplying two W registers in one instruction cycle. To enable this concurrent fetching of data operands, the data space is split for these instructions and linear for all others. This is achieved in a transparent and flexible manner through dedicating certain working registers to each address space for the MAC class of instructions.

The core does not support a multi-stage instruction pipeline. However, a single-stage instruction pre-fetch mechanism is used, which accesses and partially pre-decodes instructions a cycle ahead to maximize available execution time. Most instructions execute in a single cycle, with certain exceptions, as outlined in Section 3.1.2.

The core features a vectored exception processing structure for traps and interrupts, with 62 independent vectors. The exceptions consist of up to 8 traps (of which 3 are reserved) and 54 interrupts. Each interrupt is prioritized, based on a user assigned priority between 1 and 7 (1 being the lowest priority and 7 being the highest) in conjunction with a predetermined 'natural order'.

#### 3.1.1 COMPILER DRIVEN ENHANCEMENTS

In addition to DSP performance requirements, the core architecture was strongly influenced by recommendations which would lead to a more efficient (code size and speed) C compiler.

- For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3 operand instructions can be supported, allowing C= A+B operations to be executed in a single cycle.

- 2. Instruction addressing modes are extremely flexible to meet compiler needs.

- The working register array is comprised of 16 x 16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as the software stack pointer for interrupts and calls.

- 4. Linear indirect access of all data space is possible, plus the memory direct address range has been extended to 8 Kbytes. This, together with the addition of 16-bit direct address MOV based instructions, has provided a contiguous linear addressing space.

- 5. Linear indirect access of 32K word (64 Kbyte) pages within program space is possible, using any working register via new table read and write instructions.

- 6. Part of data space can be mapped into program space, allowing constant data to be accessed as if it were in data space.

#### 3.1.2 INSTRUCTION FETCH MECHANISM

A one-stage pre-fetching mechanism accesses each instruction a cycle ahead to maximize available execution time. Most instructions execute in a single cycle. Exceptions are:

- 1. Flow control instructions (such as program Branches, Calls, Returns) take 2 cycles, since the IR (instruction register) and pre-fetch buffer must be flushed and refilled.

- 2. Instructions where one operand is to be fetched from program space (using any method). These operations consume 2 cycles (with the notable exception of instructions executed within a REPEAT loop, which executes in 1 cycle).

- 3. Double-word move based instructions.

Most instructions access data as required during instruction execution. Instructions which utilize the multiplier array must have data available at the beginning of the instruction cycle. Consequently, this data must be pre-fetched, usually by the preceding instruction, resulting in a simple out of order data processing model.

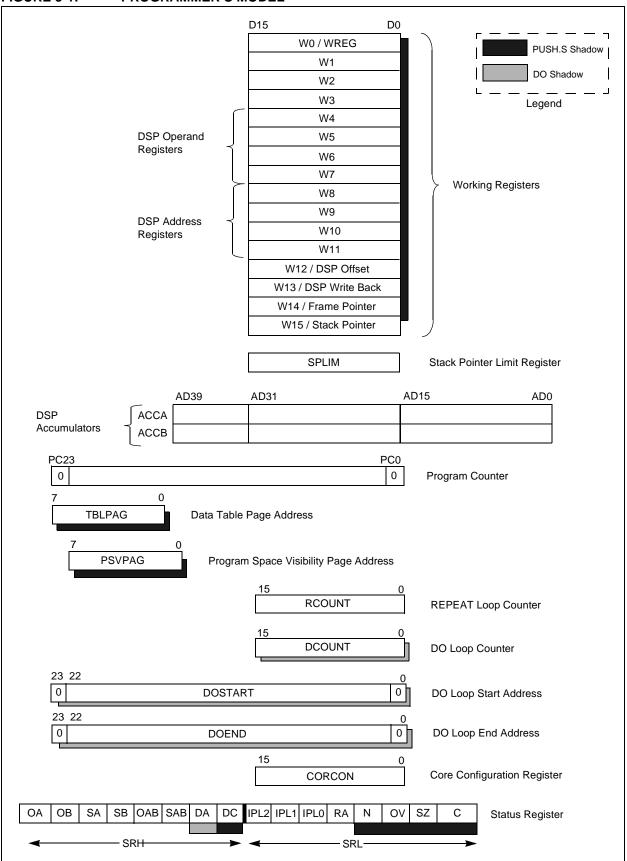

# 3.2 Programmer's Model

The programmer's model is shown in Figure 3-1 and consists of 16 x 16-bit working registers (W0 through W15), 2 x 40-bit accumulators (ACCA and ACCB), Status register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), DO and REPEAT registers (DOSTART, DOEND, DCOUNT and RCOUNT), and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 is the W register for all instructions that perform file register addressing.

Most of these registers have a shadow register associated with them, as shown in Figure 3-1. The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon some event occurring. None of the shadow registers are accessible directly. The following rules apply for transfer of registers into and out of shadows.

- PUSH.s and POP.s W0...W14, TBLPAG, PSVPAG, SR (DC, N, OV, SZ and C bits only) transferred

- DO instruction

DA bit, DOSTART, DOEND, DCOUNT shadows

pushed on loop start, popped on loop end

When a byte operation is performed on a working register, only the Least Significant Byte of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes can be manipulated through byte wide data memory space accesses.

#### 3.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

W15 is the dedicated software stack pointer (SP), and will be automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the stack pointer (e.g., creating stack frames).

In order to protect against misaligned stack accesses, W15<0> is always clear.

W15 is initialized to 0x0800 during a RESET. The user may reprogram the SP during initialization to any location within data space greater than 0x0800.

W14 has been dedicated as a stack frame pointer, as defined by the LNK and ULNK instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

The stack pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops (reads) and post increments for stack pushes (writes).

# 4.0 DATA ADDRESS SPACE

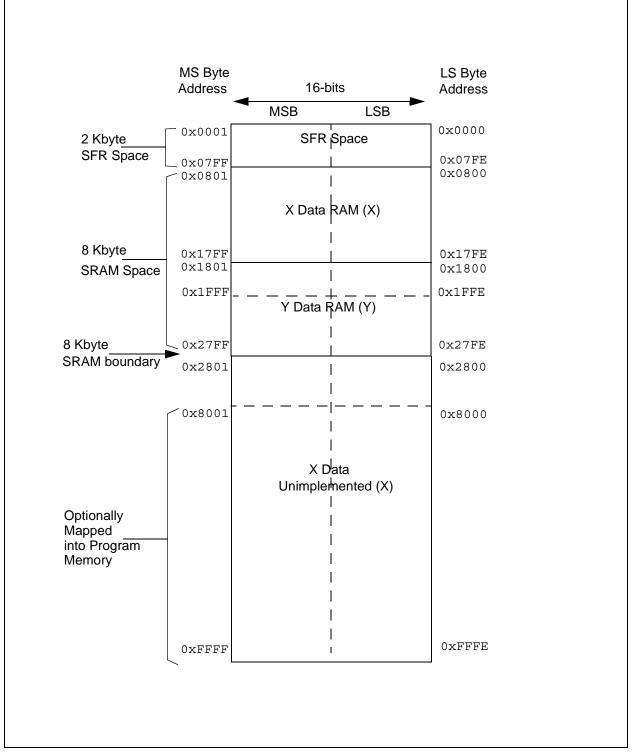

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

#### 4.1 Data Spaces

The X AGU is used by all instructions and supports all addressing modes. It consists of a read AGU (X RAGU) and a write AGU (X WAGU), which operate independently during different phases of the instruction cycle. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X RAGU and X WAGU also support modulo addressing for any instructions subject to addressing mode restrictions. Bit-reversed addressing is only supported by X WAGU.

The Y AGU and data path are used in concert with the X AGU by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y-bus. This class of instructions dedicates two W register pointers, W10 and W11, to always operate through the Y AGU and address Y data space independent of X data space, whereas W8 and W9 operate through the X RAGU and address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y, so the write occurs across the X-bus. Consequently, it can be to any address in the entire data space.

The Y AGU only supports the post-modification addressing modes associated with the MAC class of instructions. It also supports modulo addressing for automated circular buffers. Of course, all other instructions can access the Y data address space through the X AGU, when it is regarded as part of the composite linear space.

The boundary between the X and Y data spaces is not user programmable. Should an EA point to data outside its own assigned address space, or to a location outside physical memory, an all zero word/byte will be returned. For example, although Y address space is visible by all non-MAC instructions using any addressing mode, an attempt by a MAC instruction to fetch data from that space using W8 or W9 (X space pointers) will return  $0 \ge 0000$ .

# TABLE 4-1:EFFECT OF INVALID<br/>MEMORY ACCESSES

| Attempted Operation                                         | Data Returned |

|-------------------------------------------------------------|---------------|

| EA=an unimplemented address                                 | 0x0000        |

| W8 or W9 used to access Y data space in a MAC instruction   | 0x0000        |

| W10 or W11 used to access X data space in a MAC instruction | 0x0000        |

All effective addresses are 16-bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes or 32K words.

#### 4.2 Data Space Width

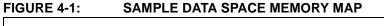

The core data width is 16-bits. All internal registers are organized as 16-bit wide words. Data space memory is organized in byte addressable, 16-bit wide blocks. Figure 4-1 depicts a sample data space memory map for the dsPIC30F.

#### 4.3 Data Alignment

To help maintain backward compatibility with PICmicro<sup>®</sup> devices and improve data space memory usage efficiency, the dsPIC30F instruction set supports both word and byte operations. Data is aligned in data memory and registers as words, but all data space EAs resolve to bytes. Data byte reads will read the complete word which contains the byte, using the LS bit of any EA to determine which byte to select. The selected byte is placed onto the LS Byte of the X data path (no byte accesses are possible from the Y data path as the MAC class of instruction can only fetch words). That is, data memory and registers are organized as two parallel byte wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

As a consequence of this byte accessibility, all effective address calculations (including those generated by the DSP operations, which are restricted to word-sized data) are internally scaled to step through word aligned memory. For example, the core would recognize that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws+1 for byte operations and Ws+2 for word operations. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be forced. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be inhibited and the PC will not be incremented. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

# 5.0 DSP ENGINE

Concurrent operation of the DSP engine with MCU instruction flow is not possible, though both the MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED and EDAC instructions).

The DSP engine consists of a high speed 16-bit x 16-bit multiplier, a barrel shifter and a 40-bit adder/subtractor with two target accumulators, round and saturation logic. The 16-bit x 16-bit multiplier is also utilized for MCU based multiply instructions.

Data input to the DSP engine is derived from one of the following:

- Directly from the W array (registers W4, W5, W6 or W7) via the X and Y data buses for the MAC class of instructions (MAC, MSC, MPY, MPY.N, ED, EDAC, CLR and MOVSAC)

- 2. From the X-bus for all other DSP instructions

- 3. From the X-bus for all MCU instructions which use the barrel shifter

Data output from the DSP engine is written to one of the following:

- 1. The target accumulator, as defined by the DSP instruction being executed

- The X-bus for MAC, MSC, CLR and MOVSAC accumulator writes, where the EA is derived from W13 only (MPY, MPY.N, ED and EDAC do not offer an accumulator write option)

- 3. The X-bus for all MCU instructions which use the barrel shifter

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations, which require no additional data. These instructions are ADD, SUB and NEG.

A block diagram of the DSP engine is shown in Figure 5-1.

#### 5.1 Multiplier

The 16 x 16-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31), or 32-bit integer results. Integer data is inherently represented as a signed two's-complement value, where the MSB is defined as a sign bit. Generally speaking, the range of an N-bit two's-complement integer is  $-2^{N-1}$  to  $2^{N-1}$ -1. For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,645 (0x7FFF FFFF).

### 5.2 Data Accumulators and Adder/ Subtractor

The data accumulator consists of a 40-bit adder/ subractor with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter prior to accumulation.

# 5.2.1 ADDER/SUBTRACTOR, OVERFLOW AND SATURATION

The adder/subtractor is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input. In the case of addition, the carry/borrow input is active-high and the other input is true data (not complemented), whereas in the case of subtraction, the carry/borrow input is active-low and the other input is complemented. The adder/subtractor generates overflow status bits SA/SB and OA/OB, which are latched and reflected in the Status Register:

- Overflow from bit 39. This is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39. This is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the overflow status bits described above, and the SATA/B and ACCSAT mode control bits to determine when to saturate and to what value to saturate

#### 5.2.2 ROUND LOGIC

The round logic is a combinational block, which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16bit 1.15 data value, which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the LS word is simply discarded.

# 5.2.3 DATA SPACE WRITE SATURATION

In addition to adder/subtractor saturation, writes to data space may also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

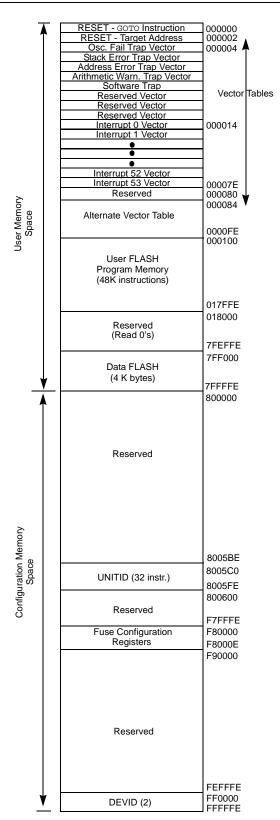

# 6.0 EXCEPTION PROCESSING

The dsPIC30F has 45 interrupt sources and 8 processor exceptions (traps), which must be arbitrated based on a priority scheme.

The processor core is responsible for reading the Interrupt Vector Table (IVT) and transferring the address contained in the interrupt vector to the program counter. The interrupt vector is transferred from the program data bus into the program counter, via a 24-bit wide multiplexer on the input of the program counter.

The Interrupt Vector Table (IVT) and Alternate Interrupt Vector Table (AIVT) are placed near the beginning of program memory (0x000004).

The interrupt controller and processor exceptions are responsible for pre-processing the interrupts prior to them being presented to the processor core. The interrupts and traps are enabled, prioritized, and controlled using centralized special function registers:

- IFS0<15:0>, IFS1<15:0>, IFS2<15:0> All interrupt request flags are maintained in these three registers. The flags are set by their respective peripherals or external signals, and they are cleared via software.

- IEC0<15:0>, IEC1<15:0>, IEC2<15:0>

All interrupt enable control bits are maintained in these three registers. These control bits are used to individually enable interrupts from the peripherals or external signals.

- IPC0<15:0>... IPC11<7:0> The user assignable priority level associated with each of these 45 interrupts is held centrally in these twelve registers.

- IPL<2:0> The current CPU priority level is explicitly stored in the 16-bit Status register that resides in the processor core.

- INTCON1<15:0>, INTCON2<15:0> Global interrupt control functions are derived from these two registers. INTCON1 contains the control and status flags for the processor exceptions. The INTCON2 register controls the external interrupt request signal behavior and the use of the alternate vector table.

- Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

All interrupt sources can be user assigned to one of 8 priority levels, 0 through 7 via the IPCx registers. Each interrupt source is associated with an interrupt vector. Levels 7 and 0 represent the highest and lowest maskable priorities, respectively.

# FIGURE 6-1: PROGRAM SPACE MEMORY MAP

Certain interrupts have specialized control bits for features like edge or level triggered interrupts, interrupt-on-change, etc. Control of these features remains within the peripheral module, which generates the interrupt.

The DISI instruction can be used to disable the processing of interrupts of priorities 6 and lower for a certain number of instructions, during which the DISI bit remains set.

When an interrupt is serviced, the PC is loaded with the address stored in the vector location in Program memory that corresponds to the interrupt. There are 63 different vectors within the IVT. These vectors are contained in locations 0x000004 through 0x0000FE of program memory. These locations contain 24-bit addresses, and in order to preserve robustness, an address error trap will take place should the PC attempt to fetch any of these words during normal execution. This prevents execution of random data through accidentally decrementing a PC into vector space, accidentally mapping a data space address into vector space, or the PC rolling over to 0x000000 after reaching the end of implemented program memory space. Execution of a GOTO instruction to this vector space will also generate an address error trap.

# 6.1 Interrupt Priority

The user assignable Interrupt Priority Control (IPC<2:0>) bits for each individual interrupt source are located in the three LS bits of each nibble within the IPCx register(s). Bit 3 of each nibble is not used and is read as a 0. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user selectable priority levels start at 0 |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|

|       | as the lowest priority and level 7 as the      |  |  |  |  |  |

|       | highest priority.                              |  |  |  |  |  |

Since more than one interrupt request source may be assigned to a specific user specified priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority"

The Natural Order Priority of an interrupt is numerically identical to its Vector Number.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The natural order priority number is the same as the vector number.

The ability for the user to assign every interrupt to one of eight priority levels implies that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example: the PLVD (Low Voltage Detect) can be given a priority of 7, and the INT0 (external interrupt 0) may be assigned to priority level 1, thus giving it a very low effective priority.

# 7.0 LOW VOLTAGE DETECT

In many applications, the ability to determine if the device voltage (VDD) is below a specified voltage level is a desirable feature. A window of operation for the application can be created, where the application software can do "housekeeping tasks" before the device voltage exits the valid operating range. This can be done using the Low Voltage Detect (LVD) module.

This module contains software programmable circuitry, where a device voltage trip point can be specified (internal reference voltage). When the voltage of the device becomes lower than the specified point, an interrupt flag is set. If the LVD interrupt is enabled, the program execution will take a level 7 (can be any user assigned priority interrupt level) exception and take appropriate action.

The Low Voltage Detect circuitry is completely under software control. This allows the circuitry to be "turned off" by the software, which minimizes the current consumption for the device.

# 8.0 dsPIC30F PERIPHERALS

The Digital Signal Controller (DSC) family of 16-bit MCU devices will provide the integrated functionality of many peripheral functions. The functions that are utilized (one or more) on the DSC devices are as follows:

- System Integration Block

- 10-bit high speed A/D Converter

- 12-bit high resolution A/D Converter

- General Purpose 16-bit timers

- Watchdog Timer module

- Motor Control PWM module

- Quadrature Encoder module

- Input Capture module

- Output Compare/PWM module

- Data Converter Interface

- Serial Peripheral Interface (SPI™) module

- UART module

- I<sup>2</sup>C<sup>™</sup> module

- Controller Area Network (CAN) module

- I/O pins

#### 8.0.1 SYSTEM INTEGRATION BLOCK

The System Integration Block contains many of the smaller functions and peripherals that provide essential services to the dsPIC30F device. The SIB contains:

- Primary Clock Oscillators (XTL, XT, HS)

- 32 kHz Clock Oscillator (LP)

- PLL Clock Multiplier

- High Speed Internal RC Oscillator (FRC)

- Watchdog Timer with low power RC Oscillator (LPRC)

- External RC Oscillator (EXTRC)

- Power-on Reset Circuit (POR)

- Programmable Brown-out Detector (BOR)

- Programmable Low Voltage Detector (LVD)

There are three primary clock oscillators: XTL, XT, HS. The XTL oscillator is designed for crystals or ceramic resonators in the range of 200 kHz to 4 MHz. The XT oscillator is designed for crystals and ceramic resonators in the range of 4 to 10 MHz. The HS (high Speed) oscillator is for crystals in the 10 to 25 MHz range. These oscillators use the OSC1 and OSC2 pins.

The secondary (LP) oscillator is designed for low power and uses a 32 kHz crystal or ceramic resonator. The LP oscillator uses the SOSC1 and SOSC2 pins.

The FRC (Fast RC) internal oscillator runs at a nominal 8 MHz.

The LPRC (Low Power RC) internal oscIllator is connected to the Watchdog Timer, and it runs at a nom-inal 512 kHz.

The External RC (EXTRC) oscillator uses an external resistor and capacitor connected to the OSC1 pin. Frequency of operation is up to 4 MHz.

The OSC1 pin may also be used as an input from an external clock source, this mode is called "EC".

#### 8.1 A/D Module Overview

There will be 2 versions of A/D converters available for the dsPIC30F family of devices. There is a 10-bit high speed A/D module and a 12-bit high resolution A/D module. Some of the key features for the 10 and 12-bit ADC are presented below.

#### 8.1.1 10-BIT A/D FEATURES

- 10-bit resolution

- Uni-polar differential Inputs

- Up to 16 input channels

- Selectable reference inputs

- ±1 LSB max DNL

- ±2 LSB max INL

- Four on-chip sample and hold amplifiers

- Single supply operation: 2.7V 5.5V

- 500 ksps sampling rate at 5V

- 100 ksps sampling rate at 2.7V

- · Ability to convert while the device SLEEPS

- Low power CMOS technology

- 5 nA typical standby current, 2 μA max

- 2.5 mA typical active current at 5V

#### 8.1.2 12-BIT A/D FEATURES

- 12-bit resolution

- Uni-polar differential Inputs

- Up to 16 input channels

- Selectable reference inputs

- ±1 LSB max DNL

- ±2 LSB max INL

- One on-chip sample and hold amplifier

- · Automated input scanning

- Single supply operation: 2.7V 5.5V

- 100 ksps sampling rate at 5V

- 50 ksps sampling rate at 2.7V

- · Ability to convert while the device SLEEPS

- Low power CMOS technology

- 5 nA typical standby current, 2 μA max

- 2.5 mA max active current at 5V

#### 8.1.3 A/D DESCRIPTION

The A/D modules provide up to 16 analog inputs with both single ended and differential inputs. These modules offer on-board sample and hold circuitry.

To minimize control loop errors due to finite update times (conversion plus computations), a high speed low latency ADC is required.

In addition, several hardware features have been added to the peripheral interface to improve real-time performance in a typical DSP based application.

- 1. Result alignment options

- 2. Automated sampling

- 3. Automated input scanning

- 4. Dual Port data buffer

- 5. External conversion start control

# 8.2 General Purpose Timer Overview

The General Purpose (GP) Timer module provides the time-base elements for Input Capture, Output Compare/PWM and can be configured for a real-time clock operation, as well as various timer/counter modes.

The dsPIC30F device will support up to five 16-bit timers. Four of the 16-bit timers can be configured as two 32-bit timers. Each timer has several selectable operating modes.

# 8.3 Watchdog Timer Module Overview

The primary function of the Watchdog Timer (WDT) is to reset the processor in the event of a software malfunction. The WDT is a free running timer which runs off an on-chip RC oscillator, requiring no external component. Therefore, the WDT timer will continue to operate, even if the main processor clock (e.g., the crystal oscillator) fails.

The Watchdog timer can be "Enabled" or "Disabled" only through a configuration bit (WDTEN) in the Configuration Register.

WDTEN = 1 enables the Watchdog Timer. The enabling is done when programming the device. By default, after chip-erase, the Watchdog Timer is enabled. Any device programmer capable of programming dsPIC devices (such as Microchip's PRO MATE<sup>®</sup> II and PICSTART<sup>®</sup> Plus programmers) allows programming of this and other configuration bits to the desired state. If enabled, the WDT will increment until it overflows or "times out". A WDT time-out will force a device RESET (except during SLEEP). To prevent a WDT time-out, the user must clear the Watchdog Timer using a CLRWDT instruction.

If a WDT times out during SLEEP, the device will wakeup. The STATUS bit will be cleared ("0") to indicate a wake-up resulting from WDT time-out.

### 8.4 Motor Control PWM Module Overview

This module simplifies the task of generating multiple, synchronized Pulse Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- Three-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptable Power Supply (UPS)

- The PWM module has the following features:

- 8 PWM I/O pins with 4 duty cycle generators

- Up to 16-bit resolution

- 'On-the-Fly' PWM frequency changes

- Edge and Center Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center Aligned mode

- Output override control for electrically commutated motor (ECM) operation

- Dead-time control for Complementary mode

- 'Special Event' comparator for scheduling other peripheral events, such as A/D conversions

This module contains 4 duty cycle generators, numbered 1 through 4. The module has 8 PWM output pins, numbered 0 through 7. The eight I/O pins are grouped into odd numbered/even numbered pairs. For complementary loads, the even PWM pins must always be the complement of the corresponding odd I/O pins to prevent damage to the power transistor devices. Consequently, the signals on the even numbered I/O pins have certain limitations when the module is in the Complementary Operating mode.

#### 8.4.1 PWM TIME-BASE

The PWM time-base is provided by a 15-bit timer with a prescaler and postscaler. Bit 15 of the PTMR SFR contains a read only status bit, PTDIR, that indicates the present count direction of the PWM time-base. If the PTDIR status bit is cleared, PTMR is counting upwards. If PTDIR is set, PTMR is counting downwards. The PWM time-base is configured via a special function register (SFR).

The PWM time-base can be configured for four different modes of operation:

- Free Running mode

- Single-Shot mode

- Continuous Up/Down Count mode

- Continuous Up/Down Count mode with interrupts for double-updates

These four modes are selected by the PTMOD<1:0> bits in the PTCON SFR. The Up/Down Counting modes support center aligned PWM generation. The Single-Shot mode allows the PWM module to support pulse control of certain electronically commutated motors (ECMs).

#### 8.5 QEI Module Overview

The Quadrature Encoder Interface (QEI) module provides the interface to incremental encoders for obtaining motor positioning data. Incremental encoders are very useful and specific to motor control applications.

The Quadrature Encoder Interface (QEI) is a key feature requirement for several motor control applications, such as Switched Reluctance (SR) motor and AC Induction Motor (ACIM). The operational features of the QEI are, but not limited to:

- Three input channels for two phase signals and index pulse

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- Quadrature Encoder Interface interrupts

### 8.6 Input Capture Module Overview

The Input Capture module is useful in applications requiring Frequency (Period) and Pulse measurement. The dsPIC30F device will support up to eight input capture channels. The key operational features are:

- · Capture every falling edge

- Capture every rising edge

- Capture every 4th rising edge

- Capture every 16th rising edge

- · Capture every rising and falling edge

- Capture timer values based on internal or external clocks

- Timer2 or Timer3 time-base selection

- Device wake-up from capture pin during CPU SLEEP and IDLE modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values

These operating modes are determined by setting the appropriate control and configuration bits.

Input capture is useful for such modes as:

- Frequency/Period/Pulse Measurements

- · Additional sources of external interrupts

#### 8.7 Output Compare/PWM Module Overview

The Output Compare module features are quite useful in applications requiring operational modes such as:

- Generation of variable width output pulses

- Simple PWM Operation

The dsPIC30F device will support up to eight Output Compare channels with the following key operational features:

- Timer2 and Timer3 Selection mode

- Simple Output Compare Match mode

- Dual Output Compare Match mode

- · Simple Glitchless PWM mode

- Output Compare during CPU SLEEP and IDLE mode

- Interrupt on output compare/PWM event

- Interrupt on PWM fault detect condition

#### 8.8 Data Converter Interface

The dsPIC Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/decoders (CODECs), A/D converters, and D/A converters. The following interfaces are supported:

- Framed Synchronous Serial Transfer (Single or Multi-Channel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- AC-link Compliant mode

The DCI module has the following hardware features:

- Programmable word size up to 16-bits.

- Support for up to 16 time slots, for a maximum frame size of 256 bits.

- Data buffering for up to 4 samples without CPU overhead

#### 8.9 SPI<sup>™</sup> Module Overview

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. It is compatible with Motorola's SPI and SIOP interfaces.

This SPI module includes all SPI modes. A Frame Synchronization mode is also included for support of voice band CODECs.

The serial port consists of a 16-bit shift register, SPISR, used for shifting data in and out and a buffer register, SPIBUF. A control register, SPICON, configures the module. Additionally, a status register, SPISTAT, indicates various status conditions.

Four pins make up the serial interface: SDI, serial data input; SDO, serial data output; SCK, shift clock input or output; SS, active low slave select, which also serves as the FSYNC, frame synchronization pulse.

In Master mode operation, SCK is clock output, but in Slave mode, it is clock input.

A series of eight or sixteen clock pulses (depending on mode) shift out the 8- or 16-bits from the SPISR to SDO pin and simultaneously shift in 8- or 16-bits data from SDI pin. An interrupt is generated when the transfer is complete (interrupt flag bit SPIIF). This interrupt can be disabled through the interrupt enable bit SPIIE.

The receive operation is double buffered. When a complete byte is received, it is transferred from SPISR to SPIBUF.

If the receive buffer is full when the protocol needs to transfer data from SPISR to SPIBUF, the module will set the SPIROV bit, indicating an overflow condition. The module will not complete the transfer of the data from SPISR to SPIBUF. The module will not respond to SCL transitions while SPIROV is '1', effectively disabling the module until software reads SPIBUF. Transmit writes are double buffered. The user writes to the SPIBUF. When the master or slave transfer finishes, the SPISR is swapped with the SPIBUF. This places the receive data in the SPIBUF and the transmit data in the SPISR, ready for the next transfer.

In Master mode, data is transmitted as soon as SPIBUF is written. The interrupt is raised at the middle of the last bit duration (i.e., after the last bit in is latched).

In Slave mode, data is transmitted and received as external clock pulses appear on SCK. Again, the interrupt is set as the last bit is latched in. If  $\overline{SS}$  control bit is enabled, then transmission and reception are enabled only when  $\overline{SS} =$  low. SDO output will be disabled in  $\overline{SS}$  mode, with  $\overline{SS} =$  high.

# 8.10 UART Module Overview

The dsPIC products will have one or more UART's.

The key features of the UART module are:

- Full-duplex operation with 8- or 9-bit data

- Even, Odd or No Parity options (for 8-bit data)

- · One or two STOP bits

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates range from up to 2.5 Mbps and down to 38 Hz at 30 MIPs

- 4-character deep transmit data buffer

- 4-character deep receive data buffer

- Parity, Framing and Buffer Overrun error detection

- 16X Baud Clock output for IrDA support

- Support for Interrupt only on Address Detect (9th bit = 1)

- Separate Transmit and Receive interrupts

- Loopback mode for diagnostics

- Alternate TX/RX pins

# 8.11 I<sup>2</sup>C<sup>™</sup> Module Overview

The I<sup>2</sup>C module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc.

The Inter-Integrated Circuit (I<sup>2</sup>C) module offers full hardware support for both Slave and Multi-Master operations.

The key features of the I<sup>2</sup>C module are:

- I<sup>2</sup>C interface supports both Master and Slave operation.

- I<sup>2</sup>C Slave operation supports 7- and 10-bit address.

- I<sup>2</sup>C Master operation supports 7- and 10-bit address.

- I<sup>2</sup>C port allows bi-directional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports Multi-Master operation. Detects bus collision and will arbitrate accordingly.

- Slew Rate Control for 100 kHz and 400 kHz bus speeds.

In  $I^2C$  mode, pin SCL is clock and pin SDA is data. The module will override the data direction bits for these pins. The pins that are used for  $I^2C$  modes are configured as open drain.

# 8.12 Controller Area Network (CAN) Module Overview

The Controller Area Network (CAN) is a serial communications protocol, which efficiently supports distributed real-time control.

The dsPIC30F CAN module satisfies the Version 2.0B specification, which allows message identifier lengths of 11 and/or 29 bits to be used (an identifier length of 29 bits allows over 536 million message identifiers). Version 2.0B CAN is also referred to as "Extended CAN".

The module will support CAN 1.2, CAN 2.0A, CAN2.0B Passive, and CAN 2.0B Active versions of the protocol. The module features are:

- Standard and extended data frames

- 0 8 bytes data length

- Programmable bit rate up to 1 Mb/sec

- · Support for remote frames

- Double buffered receiver with two prioritized received message storage buffers

- 6 full (standard/extended identifier) acceptance filters, 2 associated with the high priority receive buffer, and 4 associated with the low priority receive buffer

- 2 full acceptance filter masks, one each associated with the high and low priority receive buffers

- Three transmit buffers with application specified prioritization and abort capability

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode and programmable state clocking supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

# 8.13 I/O Pins

Some pins for the I/O pin functions are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

All I/O port pins have three registers directly associated with the operation of the port pin. The Data Direction Register determines whether the pin is an input or an output. The port Data Latch Register provides latched output data for the I/O pins. The Port Register provides visibility of the logic state of the I/O pins. Reading the Port Register provides the I/O pin logic state, while writes to the Port Register write the data to the port Data Latch Register.

#### 8.13.1 I/O PIN FEATURES

- Schmitt Trigger input

- Open drain output

- TTL input levels

- CMOS output drivers

- Weak internal pull-up

- Interrupt-on-change feature (inputs only)

#### 8.13.2 I/O Port Latch

I/O port pins have latch bits (LAT register). The LAT register, when read, will yield the contents of the I/O latch, and when written, will modify the contents of the I/O latch, thus modifying the value driven out on a pin if the corresponding Data Direction Register bit is configured for output. This can be used in read-modify-write instructions that allow the user to modify the contents of the latch register, regardless of the status of the corresponding pins.

# 9.0 dsPIC30F INSTRUCTION SET

#### 9.1 Introduction

The dsPIC30F instruction set provides a broad suite of instructions, which supports traditional microcontroller applications and a class of instructions, which supports math intensive applications. Since almost all of the functionality of the PICmicro instruction set has been maintained, this hybrid instruction set allows a friendly DSP migration path for users already familiar with the PICmicro microcontroller.

#### 9.2 Instruction Set Overview

The dsPIC30F instruction set contains 89 instructions, which can be grouped into the ten functional categories shown in Table 9-1. Table 9-1 defines the symbols used in the instruction summary tables, Table 9-3 through Table 9-12. These tables define the syntax, description, storage and execution requirements for each instruction. Storage requirements are represented in 24-bit instruction words, and execution requirements are represented in instruction cycles. Most instructions have several different Addressing modes and execution flows, which require different instruction variants. For instance, there are six unique ADD instructions and each instruction variant has its own instruction encoding.

#### TABLE 9-1: dsPIC30F INSTRUCTION GROUPS

| Functional Group          | Summary Table |

|---------------------------|---------------|

| Move Instructions         | Table 9-3     |

| Logic Instructions        | Table 9-4     |

| Rotate/Shift Instructions | Table 9-5     |

| Bit Instructions          | Table 9-6     |

| Compare/Skip Instructions | Table 9-7     |

| Flow Instructions         | Table 9-8     |

| Shadow/Stack Instructions | Table 9-9     |

| Control Instructions      | Table 9-10    |

| Control Instructions      | Table 9-11    |

| DSP Instructions          | Table 9-12    |

#### 9.2.1 MULTI-CYCLE INSTRUCTIONS

As the instruction summary tables show, most instructions execute in a single cycle, with the following exceptions:

- Instructions DO, MOV.D, POP.D, PUSH.D, TBLRDH, TBLRDL, TBLWTH, and TBLWTL require 2 cycles to execute.

- Instructions DIVF, DIV.S, DIV.U are single cycle instructions, which should be executed 18 consecutive times as the target REPEAT instruction.

- Instructions that change the program counter also require 2 cycles to execute, with the extra cycle executed as a NOP. Skip instructions, which skip over a 2-word instruction, require 3 instruction cycles to execute, with 2 cycles executed as a NOP.

- The RETFIE, RETLW, and RETURN are a special case of an instruction that changes the program counter. These execute in 3 cycles, unless an exception is pending and then they execute in 2 cycles.

- The TRAP instruction is a special case of an instruction that changes the program counter. It executes in **5** cycles, which includes the pre-fetch of the first instruction of the exception handler.

| Note: | Instructions which access program           |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | memory as data, using Program Space         |  |  |  |  |  |  |

|       | Visibility, will incur a one cycle delay.   |  |  |  |  |  |  |

|       | However, when the target instruction of a   |  |  |  |  |  |  |

|       | REPEAT loop accesses program memory         |  |  |  |  |  |  |

|       | as data, only the first execution of the    |  |  |  |  |  |  |

|       | target instruction is subject to the delay. |  |  |  |  |  |  |

|       | See the dsPIC30F Data Sheet for details.    |  |  |  |  |  |  |

#### 9.2.2 MULTI-WORD INSTRUCTIONS

As the instruction summary tables show, almost all instructions consume one instruction word (24 bits), with the exception of the CALL, DO and GOTO instructions, which are Flow Instructions listed in Table 9-9. These instructions require two words of memory, because their opcodes embed large literal operands.

| TABLE 9-2: STIVIDULS USED IN SUIVINIART TABLES | TABLE 9-2: | SYMBOLS USED IN SUMMARY TABLES |

|------------------------------------------------|------------|--------------------------------|

|------------------------------------------------|------------|--------------------------------|

| Symbol | Description                                                                    |

|--------|--------------------------------------------------------------------------------|

| #      | Literal operand designation                                                    |

| Acc    | Accumulator A or Accumulator B                                                 |

| AWB    | Accumulator Write Back                                                         |

| bit3   | 3-bit wide bit position (0:7)                                                  |

| bit4   | 4-bit wide bit position (0:15)                                                 |

| Expr   | Absolute address, label or expression (resolved by the linker)                 |

| f      | File register address                                                          |

| lit1   | 1-bit literal (0:1)                                                            |

| lit4   | 4-bit literal (0:15)                                                           |

| lit5   | 5-bit literal (0:31)                                                           |

| lit8   | 8-bit literal (0:255)                                                          |

| lit10  | 10-bit literal (0:255 for Byte mode, 0:1023 for Word mode)                     |

| lit14  | 14-bit literal (0:16383)                                                       |

| lit16  | 16-bit literal (0:65535)                                                       |

| lit23  | 23-bit literal (0:8388607)                                                     |

| Slit4  | Signed 4-bit literal (-8:7)                                                    |

| Slit5  | Signed 5-bit literal (-16:15)                                                  |

| Slit10 | Signed 10-bit literal (-512:511)                                               |

| Slit16 | Signed 16-bit literal (-32768:32767)                                           |

| TOS    | Top-of-Stack                                                                   |

| Wb     | Base working register                                                          |

| Wd     | Destination working register (direct and indirect addressing)                  |

| Wdo    | Destination working register (direct and indirect addressing with Offset mode) |

| Wm, Wn | Working register divide pair (dividend, divisor)                               |

| Wm*Wm  | Working register multiplier pair (same source register)                        |

| Wm*Wn  | Working register multiplier pair (different source registers)                  |

| Wn     | Both source and destination working register (direct addressing)               |

| Wnd    | Destination working register (direct addressing)                               |

| Wns    | Source working register (direct addressing)                                    |

| WREG   | Default working register                                                       |

| Ws     | Source working register (direct and indirect addressing)                       |

| Wso    | Source working register (direct and indirect addressing with Offset mode)      |

| Wx     | Source Addressing mode and working register for X data bus pre-fetch           |

| Wxd    | Destination working register for X data bus pre-fetch                          |

| Wy     | Source Addressing mode and working register for Y data bus pre-fetch           |

| Wyd    | Destination working register for Y data bus pre-fetch                          |

| Assembly | / Syntax        | Description                                                                                                        | Words     | Cycles  |

|----------|-----------------|--------------------------------------------------------------------------------------------------------------------|-----------|---------|

| EXCH     | Wns,Wnd         | Swap Wns and Wnd                                                                                                   | 1         | 1       |

| MOV      | f {,WREG}       | Move f to destination                                                                                              | 1         | 1       |

| MOV      | WREG,f          | Move WREG to f                                                                                                     | 1         | 1       |

| MOV      | f,Wnd           | Move f to Wnd                                                                                                      | 1         | 1       |

| MOV      | Wns,f           | Move Wns to f                                                                                                      | 1         | 1       |

| MOV.b    | #lit8,Wnd       | Move 8-bit literal to Wnd                                                                                          | 1         | 1       |

| MOV      | #lit16,Wnd      | Move 16-bit literal to Wnd                                                                                         | 1         | 1       |

| MOV      | [Ws+Slit10],Wnd | Move [Ws + signed 10-bit offset] to Wnd                                                                            | 1         | 1       |

| MOV      | Wns,[Wd+Slit10] | Move Wns to [Wd + signed 10-bit offset]                                                                            | 1         | 1       |

| MOV      | Wso,Wdo         | Move Wso to Wdo                                                                                                    | 1         | 1       |

| MOV.D    | Ws,Wnd          | Move double Ws to Wnd:Wnd+1                                                                                        | 1         | 2       |

| MOV.D    | Wns,Wd          | Move double Wns:Wns+1 to Wd                                                                                        | 1         | 2       |

| SWAP     | Wn              | Wn = byte or nibble swap Wn                                                                                        | 1         | 1       |

| TBLRDH   | Ws,Wd           | Read high program word to Wd                                                                                       | 1         | 2       |

| TBLRDL   | Ws,Wd           | Read low program word to Wd                                                                                        | 1         | 2       |

| TBLWTH   | Ws,Wd           | Write Ws to high program word                                                                                      | 1         | 2       |

| TBLWTL   | Ws,Wd           | Write Ws to low program word                                                                                       | 1         | 2       |

| Note:    | • •             | G} operand is specified, the destination of the instructine destination of the instruction is the file register f. | on is WRE | G. When |

#### TABLE 9-3: MOVE INSTRUCTIONS

#### TABLE 9-4: MATH INSTRUCTIONS

| Assembly | v Syntax     | Description                                 | Words | Cycles |

|----------|--------------|---------------------------------------------|-------|--------|

| ADD      | f {,WREG}    | Destination = f + WREG                      | 1     | 1      |

| ADD      | #lit10,Wn    | Wn = lit10 + Wn                             | 1     | 1      |

| ADD      | Wb,#lit5,Wd  | Wd = Wb + lit5                              | 1     | 1      |

| ADD      | Wb,Ws,Wd     | Wd = Wb + Ws                                | 1     | 1      |

| ADDC     | f {,WREG}    | Destination = $f + WREG + (C)$              | 1     | 1      |

| ADDC     | #lit10,Wn    | Wn = lit10 + Wn + (C)                       | 1     | 1      |

| ADDC     | Wb,#lit5,Wd  | Wd = Wb + lit5 + (C)                        | 1     | 1      |

| ADDC     | Wb,Ws,Wd     | Wd = Wb + Ws + (C)                          | 1     | 1      |

| DAW.B    | Wn           | Wn = decimal adjust Wn                      | 1     | 1      |

| DEC      | f {,WREG}    | Destination = f -1                          | 1     | 1      |

| DEC      | Ws,Wd        | Wd = Ws - 1                                 | 1     | 1      |

| DEC2     | f {,WREG}    | Destination = f -2                          | 1     | 1      |

| DEC2     | Ws,Wd        | Wd = Ws - 2                                 | 1     | 1      |

| DIV.S    | Wm,Wn        | Signed 16/16-bit integer divide             | 1     | 18     |

| DIV.SD   | Wm,Wn        | Signed 32/16-bit integer divide             | 1     | 18     |

| DIV.U    | Wm,Wn        | Unsigned 16/16-bit integer divide           | 1     | 18     |

| DIV.UD   | Wm,Wn        | Unsigned 32/16-bit integer divide           | 1     | 18     |

| DIVF     | Wm,Wn        | Signed 16/16-bit fractional divide          | 1     | 18     |

| INC      | f {,WREG}    | Destination = $f + 1$                       | 1     | 1      |

| INC      | Ws,Wd        | Wd = Ws + 1                                 | 1     | 1      |

| INC2     | f {,WREG}    | Destination = $f + 2$                       | 1     | 1      |

| INC2     | Ws,Wd        | Wd = Ws + 2                                 | 1     | 1      |

| MUL      | f            | W3:W2 = f * WREG                            | 1     | 1      |

| MUL.SS   | Wb,Ws,Wnd    | {Wnd+1,Wnd} = sign(Wb) * sign(Ws)           | 1     | 1      |

| MUL.SU   | Wb,#lit5,Wnd | $\{Wnd+1,Wnd\} = sign(Wb) * unsign(lit5)$   | 1     | 1      |

| MUL.SU   | Wb,Ws,Wnd    | {Wnd+1,Wnd} = sign(Wb) * unsign(Ws)         | 1     | 1      |

| MUL.US   | Wb,Ws,Wnd    | $\{Wnd+1,Wnd\} = unsign(Wb) * sign(Ws)$     | 1     | 1      |

| MUL.UU   | Wb,#lit5,Wnd | $\{Wnd+1,Wnd\} = unsign(Wb) * unsign(lit5)$ | 1     | 1      |

| MUL.UU   | Wb,Ws,Wnd    | {Wnd+1,Wnd} = unsign(Wb) * unsign(Ws)       | 1     | 1      |

| SE       | Ws,Wnd       | Wnd = sign-extended Ws                      | 1     | 1      |

| SUB      | f {,WREG}    | Destination = f - WREG                      | 1     | 1      |

| SUB      | Wn,#lit10    | Wn = Wn - lit10                             | 1     | 1      |

| SUB      | Wb,#lit5,Wd  | Wd = Wb - lit5                              | 1     | 1      |

| SUB      | Wb,Ws,Wd     | Wd = Wb - Ws                                | 1     | 1      |

| SUBB     | f {,WREG}    | Destination = f - WREG - (C)                | 1     | 1      |

| SUBB     | Wn,#lit10    | Wn = Wn - lit10 - (C)                       | 1     | 1      |

| SUBB     | Wb,#lit5,Wd  | $Wd = Wb - lit5 - (\overline{C})$           | 1     | 1      |

| SUBB     | Wb,Ws,Wd     | $Wd = Wb - Ws - (\overline{C})$             | 1     | 1      |

| SUBBR    | f {,WREG}    | Destination = WREG - f - $(\overline{C})$   | 1     | 1      |

| SUBBR    | Wb,#lit5,Wd  | $Wd = lit5 - Wb - (\overline{C})$           | 1     | 1      |

| SUBBR    | Wb,Ws,Wd     | $Wd = Ws - Wb - (\overline{C})$             | 1     | 1      |

| SUBR     | f {,WREG}    | Destination = WREG - f                      | 1     | 1      |

| SUBR     | Wb,#lit5,Wd  | Wd = lit5 - Wb                              | 1     | 1      |

| SUBR     | Wb,Ws,Wd     | Wd = Ws - Wb                                | 1     | 1      |

| ZE       | Ws,Wnd       | Wnd = zero-extended Ws                      | 1     | 1      |

| Assembl | y Syntax    | Description                                                                                                | Words | Cycles   |

|---------|-------------|------------------------------------------------------------------------------------------------------------|-------|----------|

| AND     | f {,WREG}   | Destination = f .AND. WREG                                                                                 | 1     | 1        |

| AND     | #lit10,Wn   | Wn = lit10 .AND. Wn                                                                                        | 1     | 1        |

| AND     | Wb,#lit5,Wd | Wd = Wb .AND. lit5                                                                                         | 1     | 1        |

| AND     | Wb,Ws,Wd    | Wd = Wb .AND. Ws                                                                                           | 1     | 1        |

| CLR     | f           | f = 0x0000                                                                                                 | 1     | 1        |

| CLR     | WREG        | WREG = 0x0000                                                                                              | 1     | 1        |

| CLR     | Wd          | Wd = 0x0000                                                                                                | 1     | 1        |

| COM     | f {,WREG}   | Destination = $\overline{f}$                                                                               | 1     | 1        |

| COM     | Ws,Wd       | $Wd = \overline{Ws}$                                                                                       | 1     | 1        |

| IOR     | f {,WREG}   | Destination = f .IOR. WREG                                                                                 | 1     | 1        |

| IOR     | #lit10,Wn   | Wn = lit10 .IOR. Wn                                                                                        | 1     | 1        |

| IOR     | Wb,#lit5,Wd | Wd = Wb .IOR. lit5                                                                                         | 1     | 1        |

| IOR     | Wb,Ws,Wd    | Wd = Wb .IOR. Ws                                                                                           | 1     | 1        |

| NEG     | f {,WREG}   | Destination = $\overline{f}$ + 1                                                                           | 1     | 1        |

| NEG     | Ws,Wd       | $Wd = \overline{Ws} + 1$                                                                                   | 1     | 1        |

| SETM    | f           | f = 0xFFFF                                                                                                 | 1     | 1        |

| SETM    | WREG        | WREG = 0xFFFF                                                                                              | 1     | 1        |

| SETM    | Wd          | Wd = 0xFFFF                                                                                                | 1     | 1        |

| XOR     | f {,WREG}   | Destination = f .XOR. WREG                                                                                 | 1     | 1        |

| XOR     | #lit10,Wn   | Wn = lit10 .XOR. Wn                                                                                        | 1     | 1        |

| XOR     | Wb,#lit5,Wd | Wd = Wb .XOR. lit5                                                                                         | 1     | 1        |

| XOR     | Wb,Ws,Wd    | Wd = Wb .XOR. Ws                                                                                           | 1     | 1        |

| Note:   | •           | ,WREG} operand is specified, the destination of ified, the destination of the instruction is the file regi |       | EG. Wher |

#### TABLE 9-5: LOGIC INSTRUCTIONS

| Assemb | ly Syntax    | Description                                                                                                                | Words            | Cycles   |

|--------|--------------|----------------------------------------------------------------------------------------------------------------------------|------------------|----------|

| ASR    | f {,WREG}    | Destination = arithmetic right shift f                                                                                     | 1                | 1        |

| ASR    | Ws,Wd        | Wd = arithmetic right shift Ws                                                                                             | 1                | 1        |

| ASR    | Wb,#lit4,Wnd | Wnd = arithmetic right shift Wb by lit4                                                                                    | 1                | 1        |