# **Application Note** 2798

## Current Regulation and DC Sequencing Circuits for Dual Supply GaAs Power Amplifiers

#### Introduction

The purpose of this application note is to address the issue of DC operation for Pacific Monolithics' dual supply GaAs power amplifiers. The PM2107 is used in this application note as the example. A critical issue in the operation of GaAs amplifiers is the control of the DC biasing point. GaAs MESFET devices inherently have variation in gate pinch off voltage and saturated drain current due to gate recessing and channel implant techniques. Additionally, temperature variations can cause shifts in drain current. Due to these variations the drain current of the PM2107, under fixed negative gate voltage bias, can vary up to +/- 90mA under quiescent operation (no RF applied) or backed off linear modes of operation. The variation is larger in linear applications as compared to saturated applications because of the large signal self-biasing effect in the amplifier. Current variation leads to difficulty in current budgeting and thermal management, especially in battery applications, thereby making current regulation often necessary.

Most dual supply amplifiers require that the negative bias be turned on before applying the positive drain voltage to the amplifier to avoid the surge in drain current and the associated thermal or metal migration degradation. Typically the negative bias is generated by a charge pump plus filtering thereby possibly causing a momentary delay in the negative supply which in turn may create a momentary surge in the drain current. Experiments at 5V Vds have shown that Pacific Monolithics' dual supply GaAs amplifiers can withstand a power up (Vds=5V, Vgs=0V) current surge of 500Ms or less before the maximum allowable junction temperature is reached. Any longer delay in the ramping of the negative supply or continuous repetition of such incidents may damage the amplifiers and cause long term reliability issues. A DC sequencing circuit can be used to prevent the problem.

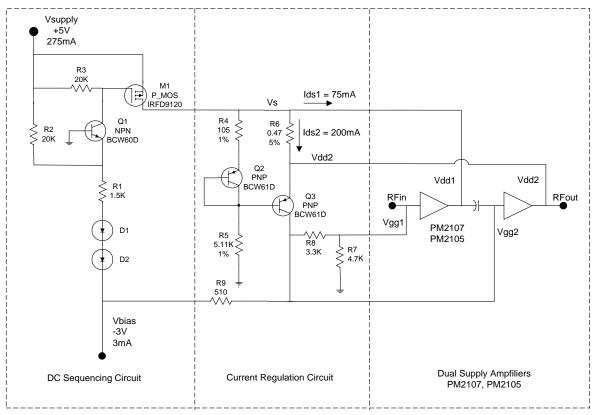

The DC sequencing and current regulation circuits on page 3 were developed to operate with Pacific Monolithics' dual supply power amplifiers. They are presented here to operate together as one circuit but they may be used independently of each other if only one of the functions is desired.

## **Principles of Operation**

#### **DC** Sequencing Circuit

The purpose of the DC sequencing circuit is to ensure that a negative bias voltage is present before switching power to the amplifier. When a negative voltage of more than -0.7V is present on the emitter terminal of Q1, the transistor turns on and sinks current through R3. The collector voltage of Q1 will drop relative to the supply voltage and turns on M1, switching power to the amplifier. D1 and D2 are used for offsetting the trigger level of the negative bias voltage. R2 feeds the emitter of Q1 to guarantee the transistor is off in the event that the bias supply is floating.

Page 2 AP2798

#### **Current Regulation Circuit**

The purpose of the current regulation circuit is to automatically set the bias level of the amplifier and maintain constant quiescent current over temperature. A reference voltage at the emitter terminal of Q3 is set by a resistive voltage divider network, R4 and R5, and the Vbe drop of Q2. The voltage drop across R6 sets a limited current flow to supply the drain of the second stage of the amplifier, which with the recommended configuration is about 200mA quiescent current. This resistor can be changed to set the desired current level for regulation. Vgg1 is tapped off the regulated Vgg2 by the resistive voltage divider network, R7 and R8. Thus it can be adjusted from 0V to Vgg2, offering the flexibility of biasing the 1st stage independently yet still regulated proportionally to Vgg2. The recommended resistor values bias the 1st stage of the amplifier at about 75mA quiescent drain current. Q2 and Q3 are configured as a current mirror, so the circuit tracks over temperature as well. Under large signal operation, the AC voltage self biases the 2nd stage and overcomes the current regulator.

Design Equations:

$$V_{dd2} = \frac{V_s - 0.7^*}{R_4 + R_5} R_5 + 0.7^*$$

$I_{ds2} \cong \frac{V_s - V_{dd2}}{R_6}$

## **Design Considerations**

The 1% tolerance of the resistors used in critical areas of the current regulation circuit must be observed for minimum current variation. A power MOS switch with least "on" channel resistance for the same current handling capability is recommended. See the parts list on page 3 for suggested manufacturers. This design condition is for 5V supply. Operation at other supply voltages may require adjustments to R6 to obtain the desired current. A negative 3V supply of 3mA is required to set the bias condition. Page 4 presents some performance curves of the PM2107 using both the sequencing and current regulation circuit.

#### PM2104 and PM2105 Application

The above discussions can be equally well applied to other Pacific Monolithics' dual supply amplifiers, the PM2104 and PM2105.

For further information, please call Pacific Monolithics, Inc. RF Products 408-745-2700

<sup>\*</sup>Assuming Vbe of Q2 is 0.7V.

<sup>\*\*</sup>Ids2 is slightly less then the expression due to some current flowing into Q3.

DC Sequencing and Current Regulation Circuit Parts List

| DC Sequencing Circuit: |             |           |                                                                                               |  |

|------------------------|-------------|-----------|-----------------------------------------------------------------------------------------------|--|

| Part#                  | Value       | Type/Size | Descriptions/Suggested Manufacturers                                                          |  |

| R1                     | 1.5K        | SM 0603   | Surface Mount Resistor                                                                        |  |

| R2, R3                 | 20K         | SM 0603   | Surface Mount Resistor                                                                        |  |

| D1, D2                 | Diode       | SOT23     | PN Diode, Zetex: (Digi-key PN: BAV99ZXCT-ND)                                                  |  |

| Q1                     | High β NPN  | SOT23     | NPN Bipolar Transistor, High Beta<br>Zetex: BCW60D, BCX70K; Diodes Inc.: BC847C               |  |

| M1                     | PMOS Switch | SOT6      | Power MOS Switch<br>Fairchild Semi. (Digi-key PN: NDC652PCT-ND)<br>National Semi. PN: NDS332P |  |

| Current Regulation Circuit: |            |           |                                        |  |

|-----------------------------|------------|-----------|----------------------------------------|--|

| Part#                       | Value      | Type/Size | Descriptions/Suggested Manufacturers   |  |

| R4                          | 105 1%     | SM 0603   | 1% Surface Mount Resistor              |  |

| R5                          | 5.11K 1%   | SM 0603   | 1% Surface Mount Resistor              |  |

| R6                          | 0.47       | SM 2512   | Surface Mount Resistor                 |  |

| R7                          | 4.7K       | SM 0603   | Surface Mount Resistor                 |  |

| R8                          | 3.3K       | SM 0603   | Surface Mount Resistor                 |  |

| R9                          | 510        | SM 0603   | Surface Mount Resistor                 |  |

| Q2, Q3                      | High β PNP | SOT23     | PNP Bipolar Transistor, High Beta      |  |

|                             |            |           | Zetex: BCW61D, BCX71K; Philips: BC857C |  |

\*Note: All resistor value tolerances are 5% unless specified.

**AP2798** Page 4

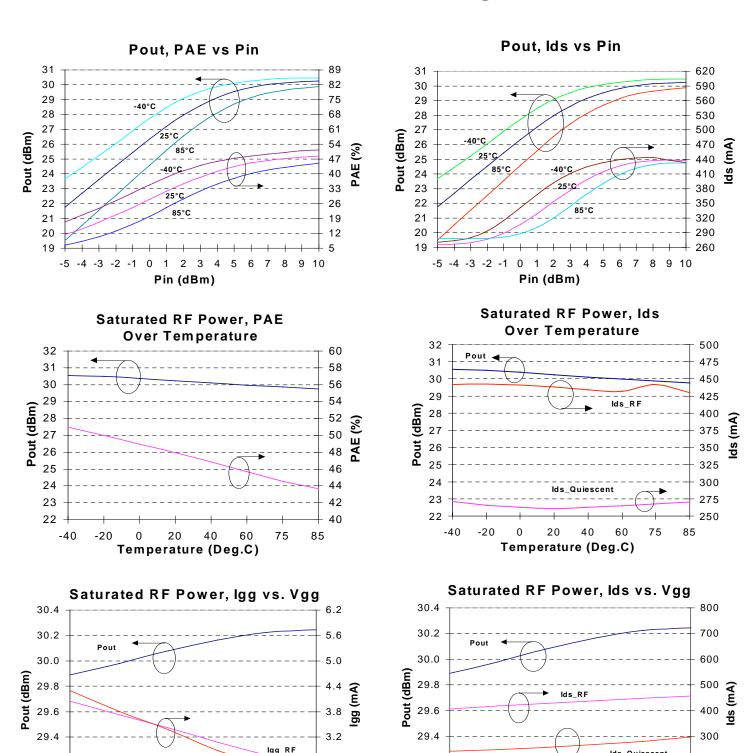

### **RF** Performances with Current Regulation Bias

2.6

2.0

-2.6

lgg\_Quiescent

-2.8

-3.0

29.2

29.0

-3.6

-3.4

29.2

29.0

-3.6

-3.4

-3.2

Vgg (V)

Vgg (V)

-3.2

-3.0

lds\_Quiescen

-2.8

200

100

-2.6