# PLL Clock Driver For 2.5V DDR-SDRAM Memory

### **Product Features**

- PLL clock distribution optimized for Double Data Rate SDRAM applications.

- Distributes one differential clock input pair to ten differential clock output pairs.

- Inputs (CLK, \overline{CLK}) and (FBIN, \overline{FBIN}): SSTL\_2

- Input PWRDWN: LVCMOS

- Outputs  $(Yx, \overline{Yx})$ ,  $(FBOUT, \overline{FBOUT})$ : SSTL\_2

- External feedback pins (FBIN, FBIN) are used to synchronize the outputs to the clock input.

- Operates at AV<sub>CC</sub> = 2.5V for core circuit and internal PLL, and V<sub>DDO</sub> = 2.5V for differential output drivers

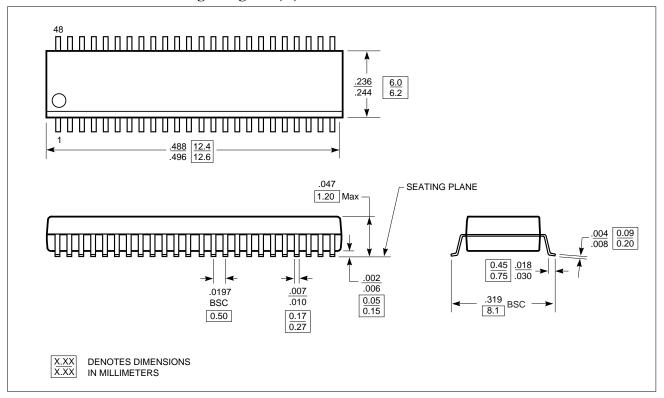

- Available Packages: Plastic 48-pin TSSOP (A)

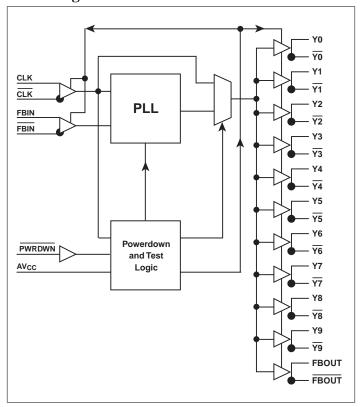

### **Block Diagram**

### **Product Description**

1

PI6CV857 PLL clock device for registered DDR DIMM applications This PLL Clock Buffer is designed for 2.5  $V_{DDQ}$  and 2.5V  $AV_{CC}$  operation and differential data input and output levels. Package options include plastic Thin Shrink Small-Outline Package (TSSOP). The device is a zero delay buffer that distributes a differential clock input pair (CLK,  $\overline{CLK}$ ) to ten differential pairs of clock outputs (Y[0:9], Y/[0:9]) and one differential pair feedback clock outputs (FBOUT,  $\overline{FBOUT}$ ). The clock outputs are controlled by the input clocks (CLK,  $\overline{CLK}$ ), the feedback clocks (FBIN,  $\overline{FBIN}$ ), the 2.5- VLVCMOS input ( $\overline{PWRDWN}$ ) and the Analog Power input (AV $_{CC}$ ). When input  $\overline{PWRDWN}$  is low while power is applied, the input receivers are disabled, the PLL is turned off and the differential clock outputs are 3-stated. When the AV $_{CC}$  is strapped low, the PLL is turned off and bypassed for test purposes.

When the input frequency falls below a suggested detection frequency that is below the operating frequency of the PLL, the device will enter a low power mode. An input frequency detection circuit will detect the low frequency condition and perform the same low power features as when the PWRDWN input is low.

The PLL in the PI6CV857 clock driver uses the input clocks (CLK,  $\overline{\text{CLK}}$ ) and the feedback clocks (FBIN, FBIN) to provide high-performance, low-skew, low-jitter output differential clocks (Y[0:9],  $\overline{\text{Y}}$ [0:9]). The PI6CV857 is also able to track Spread Spectrum Clocking for reduced EMI.

PS8464A 03/17/00

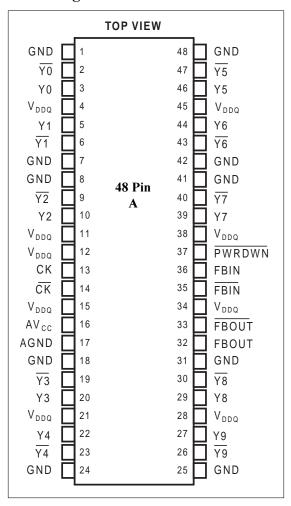

### **Pin Configuration**

### **Function Table**

| Inputs           |   |       |                     | Outputs |   |       |       | PLL State    |  |

|------------------|---|-------|---------------------|---------|---|-------|-------|--------------|--|

| AV <sub>CC</sub> | G | CLK   | CLK                 | Y       | Y | FBOUT | FBOUT |              |  |

| GND              | Н | L     | Н                   | L       | Н | L     | Н     | Bypassed/off |  |

| GND              | Н | Н     | L                   | Н       | L | Н     | L     | Bypassed/off |  |

| X                | L | L     | Н                   | Z       | Z | Z     | Z     | off          |  |

| X                | L | Н     | L                   | Z       | Z | Z     | Z     | off          |  |

| 2.5V(nom)        | Н | L     | Н                   | L       | Н | L     | Н     | on           |  |

| 2.5V(nom)        | Н | Н     | L                   | Н       | L | Н     | L     | on           |  |

| 2.5V(nom)        | X | <20 N | ⁄IHz <sup>(1)</sup> | Z       | Z | Z     | Z     | off          |  |

Z: High impedance

X: Don't care

**Note 1:** For testing and power saving purposes, PI6CV857 will power down if the frequency of the reference inputs CLK,  $\overline{\text{CLK}}$  is well below the operating frequency range. For example, PI6CV857 will be powered down when the CLK,  $\overline{\text{CLK}}$  stop running.

### Pinout Table

| Pin Name         | Pin No.                         | I/O Type | Description                                                                                                                                                                                                                                                                                                 |  |  |

|------------------|---------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK<br>CLK       | 13<br>14                        | I        | Reference Clock input                                                                                                                                                                                                                                                                                       |  |  |

| Yx               | 3,5,10,20,22,27,<br>29,39,44,46 | О        | Clock outputs.                                                                                                                                                                                                                                                                                              |  |  |

| Yx               | 2,6,9,19,23,26,<br>30,40,43,47  |          | Complement Clock outputs.                                                                                                                                                                                                                                                                                   |  |  |

| FBOUT<br>FBOUT   | 32<br>33                        |          | Feedback output.                                                                                                                                                                                                                                                                                            |  |  |

| FBIN<br>FBIN     | 36<br>35                        | I        | Feedback input.                                                                                                                                                                                                                                                                                             |  |  |

| PWRDWN           | 37                              |          | Power down and output disable for all Yx and $\overline{Yx}$ outputs. When $\overline{PWRDWN} = 0$ , the part is powered down and the differential clock outputs are disabled to a 3-state. When $\overline{PWRDWN} = 1$ , all differential clock outputs are enabled and run at the same frequency as CLK. |  |  |

| V <sub>DDQ</sub> | 4,11,12,15,21,<br>28,34,38,45   | Power    | Power Supply for I/O.                                                                                                                                                                                                                                                                                       |  |  |

| AV <sub>CC</sub> | 16                              |          | Analog /core power supply. $AV_{CC}$ can be used to bypass the PLL for testing purposes. When $AV_{CC}$ is strapped to ground, PLL is bypassed and CLK is buffered directly to the device outputs.                                                                                                          |  |  |

| AGND             | 17                              | Ground   | Analog/core ground. Provides the ground reference for the analog/core circuitry                                                                                                                                                                                                                             |  |  |

| GND              | 1,7,8,18,24,25,<br>31,41,42,48  |          | Ground                                                                                                                                                                                                                                                                                                      |  |  |

# Absolute Maximum Ratings

(Over operating free-air temperature range)

| Symbol                              | Parameter                                                     | Min.  | Max.               | Units |  |

|-------------------------------------|---------------------------------------------------------------|-------|--------------------|-------|--|

| V <sub>DDQ</sub> , AV <sub>CC</sub> | I/O supply voltage range and analog/core supply voltage range | - 0.5 | 3.6                |       |  |

| $V_{\rm I}$                         | Input voltage range                                           | - 0.5 | W 10.5             | V     |  |

| $V_{\rm O}$                         | Output voltage range                                          | - 0.5 | $V_{\rm DDQ}$ +0.5 |       |  |

| Tstg                                | Storage temperature                                           | - 65  | 150                | °C    |  |

Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

# **DC** Specifications

# **Recommended Operating Conditions**

| Symbol           | Parameter                                                         | Min.                       | Nom. | Max.                       | Units     |

|------------------|-------------------------------------------------------------------|----------------------------|------|----------------------------|-----------|

| AV <sub>CC</sub> | Analog/core supply voltage                                        | 2.3                        | 2.5  | 2.7                        |           |

| V <sub>DDQ</sub> | Output supply voltage                                             | 2.3                        | 2.5  | 2.7                        |           |

| V <sub>IL</sub>  | Low-level input voltage for PWRDWN pin                            | -0.3                       |      | 0.7                        |           |

| V <sub>IH</sub>  | High-level input voltage for PWRDWN pin                           | 1.7                        |      | V <sub>DDQ</sub> +0.3      |           |

| V <sub>OH</sub>  | High-level output voltage                                         | 2.0                        |      | V <sub>DDQ</sub>           |           |

| V <sub>OL</sub>  | Low-level output voltage                                          | 0                          |      | 0.5                        | $oxed{V}$ |

| V <sub>IX</sub>  | Input differential-pair crossing voltage                          | (V <sub>DDQ</sub> /2) -0.2 |      | (V <sub>DDQ</sub> /2) +0.2 | ,         |

| V <sub>OX</sub>  | Output differential-pair crossing voltage at the DRAM clock input | (V <sub>DDQ</sub> /2) -0.2 |      | (V <sub>DDQ</sub> /2) +0.2 |           |

| V <sub>IN</sub>  | Input voltage level                                               | -0.3                       |      | V <sub>DDQ</sub> +0.3      |           |

| V <sub>ID</sub>  | Input differential voltage between CK and $\overline{\text{CK}}$  | 0.36                       |      | V <sub>DDQ</sub> +0.6      |           |

| T <sub>A</sub>   | Operating free air temperature                                    | 0                          |      | 70                         | °C        |

### **Electrical Characteristics**

| Parameter               |                                                                 | Test Conditions                   | Avcc, V <sub>DDQ</sub> | Min. | Тур. | Max. | Units |

|-------------------------|-----------------------------------------------------------------|-----------------------------------|------------------------|------|------|------|-------|

| V <sub>IK</sub>         | All inputs                                                      | $I_{\rm I} = -18 \text{mA}$       | 2.3V                   |      |      | -1.2 | V     |

| I <sub>I</sub> CK, FBIN |                                                                 | $V_I = V_{DDQ}$ or GND            |                        |      |      | +10  |       |

|                         | PWRDWN                                                          | $V_I = V_{DDQ}$ or GND            |                        |      |      | ±10  | μΑ    |

|                         | Dynamic supply current                                          |                                   | 2.7V                   |      |      | TBD  | mA    |

| I <sub>DDQ</sub>        | Static supply current                                           | CK & CK <20MHz<br>or PWRDWN = Low |                        |      |      | 100  | μΑ    |

| C <sub>I</sub>          | CK and $\overline{\text{CK}}$ FBIN and $\overline{\text{FBIN}}$ | $V_I = V_{DD}$ or GND             | 2.5V                   | 2.0  |      | 3.0  | pF    |

Timing Requirements (Over recommended operating free-air temperature).

|                   |                                            | $\begin{aligned} \mathbf{A_{VCC},\ V_{DDQ}} &= \mathbf{2.5V} \\ &\pm \mathbf{0.2V} \end{aligned}$ |      |       |  |

|-------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|------|-------|--|

| Symbol            | Description                                | Min.                                                                                              | Max. | Units |  |

| f                 | Operating clock frequency <sup>(1,2)</sup> | 60                                                                                                | 170  | MHz   |  |

| f <sub>CK</sub>   | Application clock frequency <sup>(3)</sup> | 95                                                                                                | 170  |       |  |

| t <sub>DC</sub>   | Input clock duty cycle                     | 40                                                                                                | 60   | %     |  |

| t <sub>STAB</sub> | PLL stabilization time after powerup       |                                                                                                   | 100  | μs    |  |

#### **Notes:**

- 1. The PLL is able to handle spread spectrum induced skew.

- 2. Operating clock frequency indicates a range over which the PLL is able to lock, but in which the clock is not required to meet the other timing parameters. (Used for low-speed debug).

- 3. Application clock frequency indicates a range over which the PLL meets all of the timing parameters.

### **AC Specifications**

Switching characteristics over recommended Operating free-air temperature range (unless otherwise noted)

|             |                                                                                                                                                       |              | $AV_{CC}, V_{DDQ} = 2.5V \pm 0.2V$ |        |         |       |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------|--------|---------|-------|--|

| Parameter   | Description                                                                                                                                           | Diagram      | Min.                               | Nom.   | Max     | Units |  |

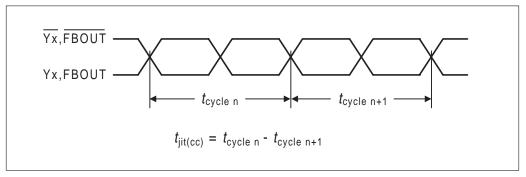

| tjit(cc)    | Cycle-to-cycle jitter                                                                                                                                 | see Figure 3 | -75                                |        | 75      |       |  |

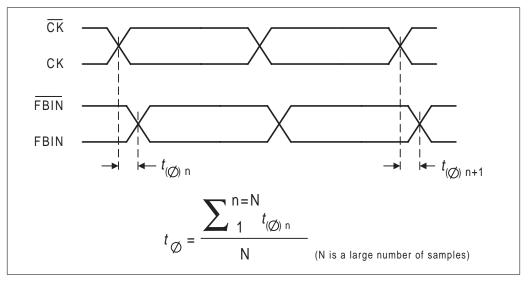

| $t(\theta)$ | Static phase error <sup>(1)</sup>                                                                                                                     | see Figure 4 | -50                                | 0      | 50      |       |  |

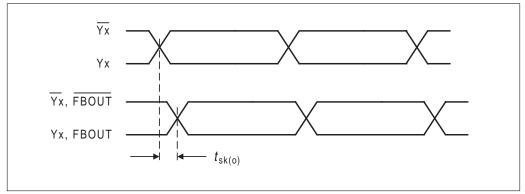

| tsk(o)      | Output clock skew                                                                                                                                     | see Figure 5 |                                    |        | 100 ps  |       |  |

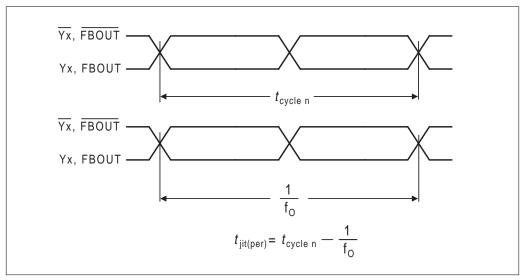

| tjit(per)   | Period jitter                                                                                                                                         | see Figure 6 | -75                                |        | 75      |       |  |

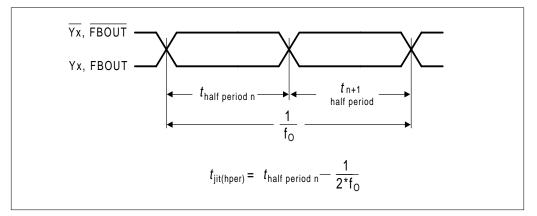

| tjit(hper)  | Half-period jitter                                                                                                                                    | see Figure 7 | -100                               |        | 100     |       |  |

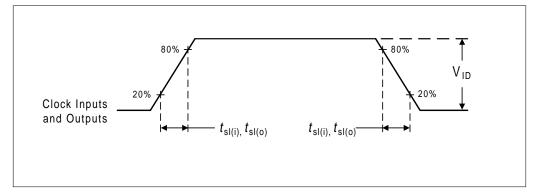

| tsl(i)      | Input clock slew rate <sup>(2)</sup>                                                                                                                  | see Figure 8 | 1.0                                |        | 2.0     | X7/   |  |

| tsl(o)      | Output clock slew rate <sup>(2)</sup>                                                                                                                 | see Figure 8 | 1.0                                |        | 2.0     | V/ns  |  |

|             | The PLL on the PI6CV857 iscapable of meeting all the above parameters while supporting SSC synthesizers <sup>(3)</sup> with the following parameters. |              |                                    |        |         |       |  |

|             | SSC modulation frequency                                                                                                                              |              | 30.00                              |        | 50.00   | kHz   |  |

|             | SSC clock input frequency deviation                                                                                                                   |              | 0.00                               |        | -0.50   | %     |  |

|             | PLL loop bandwidth                                                                                                                                    |              |                                    | 2      |         | MHz   |  |

|             | Phase angle                                                                                                                                           |              |                                    | -0.031 | degrees |       |  |

### **Notes:**

- 1. Static Phase Error does not include Jitter.

- 2. The slew rate is determined from the IBIS model and not from the test load.

- 3. The SSC requirements meet the Intel PC100 SDRAM Registered DIMM specification.

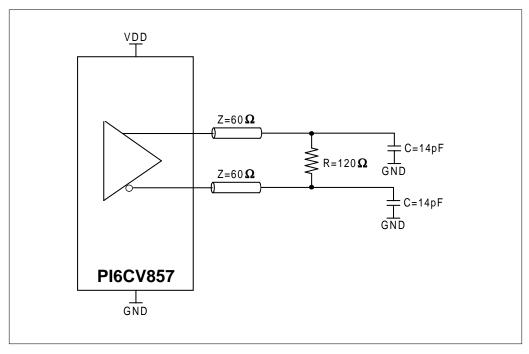

Figure 1. Output Load

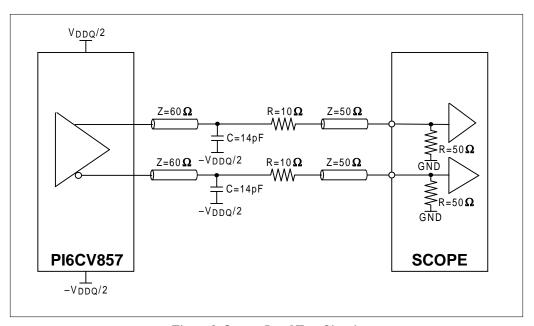

Figure 2. Output Load Test Circuit

6

Figure 3. Cycle-to-Cycle Jitter

Figure 4. Static Phase Offset

Figure 5. Output Skew

7

Figure 6. Period Jitter

Figure 7. Half-Period Jitter

Figure 8. Input and Output Slew Rates

8

### Plastic 48-Pin TSSOP Package Diagram (A)

### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com