# Precision Clock Generator for Laser Printers

#### **Features**

- Supports laser printer pixel rates up to 40 MHz. 70 MHz for "C" speed version.

- Jitter less than 300ps.

- Easily programmable frequency selections via parallel interface. Post divider (R) designed to load only during the Beam Detect interval.

- Source clock input can be from crystal or oscillator.

- Source clock rates from 8 MHz up to 22 MHz (from crystal or oscillator).

- Active LOW asynchronous reset input for synchronization with engine via Beam Detect input.

- Synchronized Beam Detect Output to support external state machines.

- · Glitch-less clock output after Beam Detect.

- Supports dynamic frequency changes on a line-per-line basis.

- Mixed line resolution supports half-toning and gray scale operations.

- Minimizes controller memory utilization (low-resolution text mixed with high-resolution images).

- On-chip VCO loop filter (no external components).

- On-chip crystal oscillator (modified Pierce).

- Single 5V power supply.

- Low power consumption.

- 20-pin wide body (300-mil) SOIC package (S)

## **Description**

The PI6C1201 is an advanced CMOS clock generator designed specifically to support pixel clock generation in low-cost laser printers. Capable of generating highly stable clock frequencies up to 70 MHz, this device supports printer engines with dot resolutions of 1,200 dpi and above. Page speeds may range from 4 pages per minute to better than 60 pages per minute.

Mixed-line resolution supports half-toning and gray scale operations (low-resolution text mixed with high-resolution images) and minimizes controller memory utilization

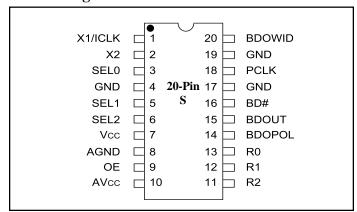

## **Pinout Diagram**

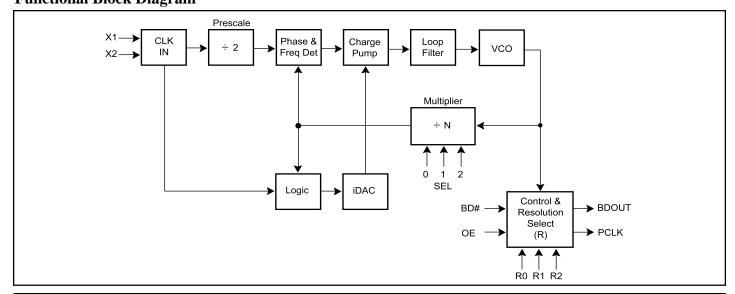

# **Functional Block Diagram**

182

# **Pin Description**

| Pin           | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | X1/ICLK          | <b>CRYSTAL, or input from external clock source</b> . This pin is connected to a crystal or may be used to input an external reference frequency. When connected to a crystal, a 33 pF (typ) capacitor should be connected from this pin to ground. When driven by an external clock there is no need for a capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2             | X2               | <b>CRYSTAL. Output of Ring Oscillator.</b> This pin should typically have a 22 pF capacitor to ground when used with a crystal. For fine-tuning the crystal frequency, this capacitor can be trimmed from 15 pF to 33 pF. If X1 is driven by an external clock source, there is no need for a capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4             | GND              | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3, 5, 6       | SEL(0-2)         | <b>Selects VCO/Crystal Multiplication Ratio</b> . These pins can be dynamically changed anytime (not recommended during active imaging). These inputs must be tied HIGH/LOW or driven actively to guarantee that the setting stays valid. Refer to Table 2 for additional information. These pins have internal pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7             | $v_{CC}$         | Digital Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8             | AGND             | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9             | OE               | <b>Output Enable</b> . When pulled HIGH, this pin will enable the PCLK and the BDOUT outputs. When pulled LOW, these pins are tri-stated. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10            | AV <sub>CC</sub> | Analog Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11,<br>12, 13 | R(0-2)           | <b>Output Resolution Selection</b> . Used to set the final dot resolution. The divide ratios set by these pins are all tightly aligned synchronous outputs designed to eliminate glitches and allow dynamic changes to the output clock dot resolution frequency on a per-line basis. These pins can only be changed during the BD# (Beam Detect) active interval. The signals should be externally latched at least one or two PCLK cycles prior to BD# going active to guarantee internal latches setup and hold times. R0 allows single-pin control for $1/4$ or $1/8$ mode (assuming R1 and R2 = 1). Please refer to Table 1 for further information. These pins have internal pull-up resistors.                                  |

| 14            | BDOPOL           | <b>Beam Detect Output Polarity:</b> This pin is used to set the polarity of the BDOUT output (pin 15). When this pin is LOW, the BDOUT polarity is active HIGH. When this pin is HIGH, the BDOUT polarity is active LOW. This pin is pulled up internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15            | BDOUT            | <b>Beam Detect Output</b> . This pin signals the start of a new line after synchronization has occurred. The BDOUT signal will go active when the incoming BD# signal is detected and synchronized. The width of this pulse is dependent upon the VCO frequency and the current PCLK setting. Please refer to the timing diagram for additional information. The polarity of BDOUT can be controlled by BDOPOL (pin 14) and the width can be set to 1 or 2 PCLKs by BDOWID (pin20). BDOUT can be tri-stated by the OE pin. BDOUT has a 12mA balanced drive CMOS output.                                                                                                                                                                |

| 16            | BD#              | <b>Beam Detect Input from Engine</b> . The engine signal that drives this pin indicates that the end (or beginning) of a line has been detected. Since this signal is typically an asynchronous strobe, this active-low <b>edge-sensitive</b> input is extremely metastable-resistant. This input has a TTL-compatible input threshold with hysteresis. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                     |

| 17            | GND              | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18            | PCLK             | <b>Pixel Clock Output</b> . The output frequency of this pin is a function of the crystal (or input clock) frequency (pre-scaled to ÷2), the multiply ratio as set by SEL(0-2) and the final divide ratio as set by R(0-2): PCLK = Crystal x (1/2) x [32, 16, or 8 as defined by SEL(0-1)] x (1/8 or 1/4 as controlled by R0 - assumes R1=R2=1). This output can be glitchlessly synchronized to an external asynchronous event by asserting the BD# input. The minimum indeterminacy of the alignment to the external event is controlled by the width of the VCO clock. Please refer to timing diagrams for additional information. The PCLK output can be tri-stated by the OE pin. This pin has a 12mA balanced-drive CMOS output. |

| 19            | GND              | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20            | BDOWID           | <b>Beam Detect Output Width:</b> This pin is used to set the width of the BDOUT output (pin 15). When this pin is LOW, the BDOUT width is two PCLK periods. When this pin is HIGH, the BDOUT width is one PCLK period. This pin has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

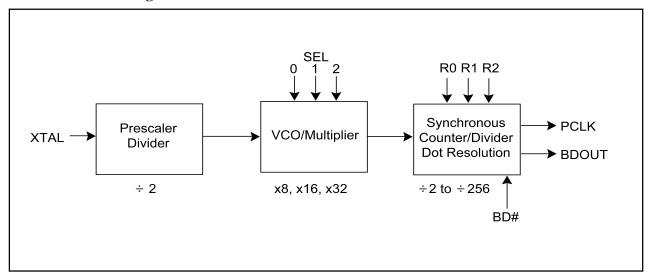

## **Basic PLL Flow Diagram**

184

Table 1. Dot Resolution Divider Pin Setting

| R2 | R1 | R0 | Function | R   |

|----|----|----|----------|-----|

| 0  | 0  | 0  | 0 ÷ 16   |     |

| 0  | 0  | 1  | ÷ 32     | 32  |

| 0  | 1  | 0  | ÷ 64     | 64  |

| 0  | 1  | 1  | ÷ 128    | 128 |

| 1  | 0  | 0  | ÷ 256    | 256 |

| 1  | 0  | 1  | ÷ 2      | 2   |

| 1  | 1  | 0  | ÷ 4      | 4   |

| 1  | 1  | 1  | ÷ 8      | 8   |

**Table 2. VCO Multiplier Pin Setting**

| SEL2 | SEL1 | SEL0 | Function |

|------|------|------|----------|

| 1    | 0    | 0    | Reserved |

| 1    | 0    | 1    | x8       |

| 1    | 1    | 0    | x32      |

| 1    | 1    | 1    | x16      |

## Note:

1. The relationship of the VCO to PCLK is controlled by the R synchronous divider.

For example:

(a) 1 PCLK = 4 VCO clocks if R0 = 0 & R1 = R2 = 1

(b) 1 PCLK = 8 VCO clocks if R0 = 1 & R1 = R2 = 1

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                                                 |

|---------------------------------------------------------------------|

| Ambient Temperature with Power Applied                              |

| Supply Voltage to Ground Potential (Inputs & Vcc only)0.3V to +7.0V |

| DC Input Voltage0.5V to +7.0V                                       |

| DC Output Current                                                   |

| Power Dissipation                                                   |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **DC Electrical Characteristics** ( $Vcc = 5V\pm10\%$ for "blank" and "A" speed, $Vcc = 5V\pm5\%$ for "C" speed. TA = 0°C to 70°C)

| Symbol                           | Description                               | Test Conditions <sup>(2)</sup>                    | Min.    | Typ. <sup>(3)</sup> | Max. | Units |

|----------------------------------|-------------------------------------------|---------------------------------------------------|---------|---------------------|------|-------|

| V <sub>IH</sub> <sup>(1)</sup>   | Input HIGH Voltage                        | All Inputs except X1 & BD#                        | 2.0     |                     |      | V     |

| VIHX1 <sup>(1)</sup>             | Input HIGH Voltage X1                     | X1 Input                                          | Vcc-1.0 | _                   |      | v     |

| V <sub>BDTH</sub> <sup>(1)</sup> | Input Threshold Voltage BD#               | $V_{CC} = 4.5V \text{ to } 5.5V$                  | 1.2     | _                   | 1.4  |       |

| V <sub>IL</sub> (1)              | Input LOW Voltage                         | All Inputs                                        | _       | _                   | 0.8  |       |

| Іпн                              | Input HIGH Current with Pull-up           | All Inputs except X1 VCC = Max., VIN = VCC        | _       | _                   | 5    | μА    |

| Іп                               | Input LOW Current with Pull-up            | All Inputs except X1,<br>VCC = Max., VIN = 0V     | -50     |                     | _    |       |

| ІнХ1                             | Input HIGH Current X1                     | X1 Input, VCC = Max.<br>VIN = VCC                 | _       | _                   | 150  |       |

| IILX1                            | Input LOW Current X1                      | X1 Input, VCC = Max.<br>VIN = 0V                  | -150    | _                   | _    |       |

| Vон                              | Output HIGH Voltage                       | All Outputs except X2<br>Vcc = Min., IoH = -12mA  | 2.4     | _                   | _    | V     |

| Vol                              | Output LOW Voltage                        | All Outputs except X2,<br>Vcc = Min., IoL = +12mA | _       | _                   | 0.4  |       |

| Ios <sup>(1,4)</sup>             | Short Circuit Current                     | Vcc = 5.25V<br>Vout = GND                         | 25      | _                   | _    | mA    |

| I <sub>c160</sub>                | Dynamic Supply Current                    | Vcc = 5.0V, X1 = 20 MHz<br>SEL = x16              | _       | _                   | 35   |       |

| I <sub>c240</sub>                | Dynamic Supply Current (for 6C1201A only) | Vcc = 5.0V, X1 = 15 MHz<br>SEL = x32              | _       | _                   | 50   |       |

| I <sub>c280</sub> <sup>(5)</sup> | Dynamic Supply Current (for 6C1201C only) | Vcc = 5.0V, X1 = 17.5 MHz,<br>SEL = x32           |         |                     | 60   |       |

#### **Notes:**

- 1. These parameters are guaranteed by design and measured at characterization only.

- 2. For Max. or Min. conditions, use appropriate values specified under Electrical Characteristics for the appropriate device type.

185

- 3. Typical values are shown at Vcc = 5.0V,  $+25^{\circ}C$  ambient and maximum loading.

- 4. Not more than one output should be shorted at one time. Duration of test should not exceed one second.

- 5. "C" speed operation is limited to a  $\pm 5\%$  Vcc tolerance

## **Switching Characteristics**

$Vcc = 5V \pm 10\%$  for "blank" and "A" Speed,  $Vcc = 5V \pm 5\%$  for "C" Speed. TA = 0° C to 70° C

| Symbol                                     | Description                                                                    | Test Conditions                                                          | Min.  | Тур.  | Max.  | Units |

|--------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------|-------|-------|-------|

| tR <sup>(1)</sup>                          | PCLK Output Rise Time (0.8V to 2.0V)                                           | CL 20 E                                                                  | _     | _     | 2     | ns    |

| tF <sup>(1)</sup>                          | PCLK Output Fall Time (2.0V to 0.8V)                                           | CL = 30 pF                                                               |       | _     | 2     |       |

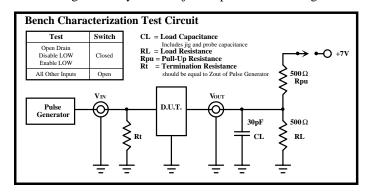

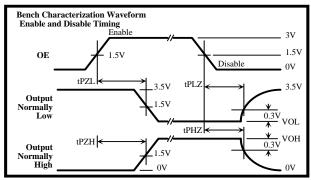

| tPZH <sup>(1)</sup><br>tPZL <sup>(1)</sup> | OE to PCLK Output Enable Time<br>(Please refer to the Test Circuit & Waveform) | $CL = 30 \text{ pF}, RL = 500\Omega$<br>$Rpu = 500\Omega \text{ to } 7V$ | 1.5   | _     | 7.5   |       |

| tPHZ <sup>(1)</sup><br>tPLZ <sup>(1)</sup> | OE to PCLK Output Disable Time (Please refer to the Test Circuit & Waveform)   | (for tPZL and tPLZ only)                                                 | 1.5   | _     | 6.0   |       |

| dT <sup>(1)</sup>                          | PCLK Duty Cycle                                                                |                                                                          |       | 50/50 | 45/55 | %     |

| FXTALin                                    | Crystal Input Frequency<br>(Production tested at 15.0 MHz)                     | Within the following VCO                                                 | 8     |       | 22    |       |

| Fin                                        | Driven Input Frequency (Production tested at 4,20,22, and 30 MHz)              | frequency range:                                                         | 8     | _     | 22    |       |

| Fvco <sup>(2)</sup>                        | VCO Farance (Mar DOLK 40 MIL)                                                  | "blank" Speed Grade                                                      | 120   |       | 176   | MHz   |

| Fvco <sup>(2)</sup>                        | VCO Frequency (Max. PCLK = 40 MHz)                                             | "A" Speed Grade                                                          | 120   | _     | 240   |       |

| Fvco <sup>(2)</sup>                        | VCO Frequency (Max. PCLK = 70 MHz)                                             | "C" Speed Grade (±5% Vcc)                                                | 120   | _     | 280   |       |

| Tjis <sup>(1)</sup>                        | PCLK one sigma jitter                                                          | X1 = 15 MHz,                                                             | _     | 50    | _     |       |

| Tjab <sup>(1)</sup>                        | PCLK short term peak-to-peak jitter                                            | SEL = x32, R = 8                                                         | _     | _     | 300   | ps    |

| Tvco <sup>(3)</sup>                        | VCO clock period                                                               |                                                                          | 3.571 |       | 8.333 | ne    |

| TPCLK <sup>(4)</sup>                       | PCLK clock period                                                              |                                                                          | _     |       |       | ns    |

#### **Notes:**

- 1. These parameters are guaranteed by design and measured at characterization only.

- 2. The VCO frequency can be determined by the following formula:

$$FVCO = \frac{FxTALin \text{ or } Fin}{2} \times N$$

N = VCO multiplier value. See Table 2

For X1 = 20 MHz and SEL = x16, then: Fvco =  $(20 \text{ MHz} / 2) \times 16 = 160 \text{ MHz}$ For X1 = 15 MHz and SEL = x32, then: Fvco =  $(15 \text{ MHz} / 2) \times 32 = 240 \text{ MHz}$

- 3. The VCO clock period is determined by the formula: Tvco = 1 / Fvco. For design aid only.

- 4. TPCLK = TVCO x R, R = output dot resolution divider function (see Table 1). For design aid only. Not subject to production testing.

Pulse Generator for All Pulses: Rate  $\leq 1.0$ MHz; Zout  $\leq 50 \Omega$ , tF, tR  $\leq 2.5$ ns

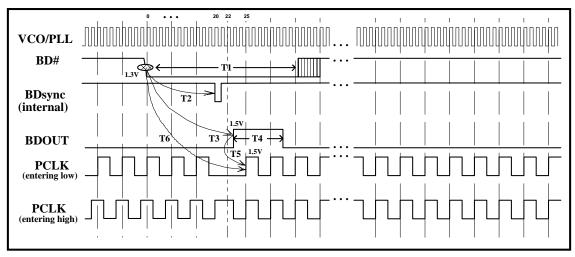

## Timing Table<sup>(4)</sup>

$Vcc = 5V \pm 10\%$  for "blank" and "A" Speed,  $Vcc = 5V \pm 5\%$  for "C" Speed. TA = 0° C to 70° C

| Sym.                | Description                                                       | Min.                                                          | Тур.               | Max.                                                              |

|---------------------|-------------------------------------------------------------------|---------------------------------------------------------------|--------------------|-------------------------------------------------------------------|

| T1                  | Minimum BD# Pulse Width <sup>(2)</sup>                            | 22 TVCO                                                       | _                  | _                                                                 |

| T2 <sup>(1)</sup>   | Time from BD# Active to BDsync                                    | 18 TVCO                                                       | _                  | 19 TVCO                                                           |

| Т3                  | Synchronous Time from BD# to BDOUT                                | 19 TVCO + 0.5 TPCLK<br>+ t <sub>D</sub> - 0.5 tJT3            | _                  | 20 TVCO + 0.5 TPCLK<br>+ t <sub>D</sub> + 0.5 tJT3                |

| T4 <sup>(1)</sup>   | Width of BDOUT Pulse BDOWID = 0<br>BDOWID = 1                     | 2 TPCLK -0.5 tJT4<br>1 TPCLK -0.5 tJT4                        | 2 TPCLK<br>1 TPCLK | 2 TPCLK + 0.5 tJT4<br>1 TPCLK + 0.5 tJT4                          |

| T5                  | Time from BDOUT active to the first valid rising edge of PCLK     | 0.47 TPCLK - 0.5 tJT5                                         | 0.5<br>TPCLK       | 0.5 TPCLK + 0.5 tJT5                                              |

| Т6                  | Total time from BD# active to the first valid rising edge of PCLK | T3 + T5 = 19 TVCO<br>+ 0.97 TPCLK + t <sub>D</sub> - 0.5 tJT6 | _                  | $T3 + T5 = 20 \text{ TVCO} + 1.0 \text{ TPCLK} + t_D + 0.5 $ tJT6 |

| $t_{\mathrm{D}}$    | On-chip total buffer delays                                       | See Note 3                                                    | _                  | See Note 3                                                        |

| tJT3 <sup>(5)</sup> | T3 peak-to-peak jitter                                            | 0ps                                                           | _                  | 300 ps                                                            |

| tJT4 <sup>(5)</sup> | T4 peak-to-peak jitter                                            | 0ps                                                           | _                  | 300 ps                                                            |

| tJT5 <sup>(5)</sup> | T5 peak-to-peak jitter                                            | 0ps                                                           | _                  | 300 ps                                                            |

| tJT6 <sup>(5)</sup> | T6 peak-to-peak jitter                                            | 0ps                                                           | _                  | 300 ps                                                            |

#### **Notes:**

- 1. These parameters are guaranteed by design and functional test only.

- 2. The width of the BD# pulse (T1) MUST meet the minimum width requirements of 22 Tvco. BD# pulses less than 22 Tvco will not achieve synchronization and will not generate BDOUT.

- synchronization and with the falling edge of BD# should be 6 ns or less.

3.  $t_D$  is extracted from initial product characterization. It varies with both Vcc and temperature. The following linear regression formulas may be used to calculate  $t_D$  for  $4.5\text{V} \le \text{Vcc} \le 5.5\text{V}$  and  $0^{\text{O}}\text{C} \le \text{T}_A \le 70^{\text{O}}\text{C}$ . This is provided for design purposes only. A  $\pm 10\%$  guardband of the calculated value will be used for production testing.

- a. Linear regression of  $t_D$  vs. Vcc at a fixed temperature:  $t_D$  = Slope x Vcc + Intercept

| Temperature<br>(°C) | 0      | 20     | 40     | 60     | 80     |

|---------------------|--------|--------|--------|--------|--------|

| Intercept (ns)      | 14.032 | 14.756 | 15.585 | 16.771 | 17.107 |

| Slope (ns/V)        | -1.224 | -1.296 | -1.396 | -1.568 | -1.564 |

b. Linear regression of  $t_D$  vs. Temperature at a fixed Vcc:  $t_D$  = Slope x Temperature + Intercept

| Vcc (V)        | 4.50  | 4.75  | 5.00  | 5.25  | 5.50  |

|----------------|-------|-------|-------|-------|-------|

| Intercept (ns) | 8.578 | 8.206 | 7.872 | 7.586 | 7.364 |

| Slope (ns/°C)  | 0.019 | 0.018 | 0.017 | 0.017 | 0.014 |

- 4. T<sub>VCO</sub> = VCO clock period. T<sub>PCLK</sub> = PCLK clock period.

5. Parameters obtained from initial characterization, not subject to production testing.

# **Timing Diagram**

## PLL to Output Clock and Beam Detect Reset Sequence

#### Note:

1. The PCLK frequency in this example is 1/4 the VCO frequency (R0=0 & R1=R2=1  $\rightarrow$  see Table 1) For measurement purposes the BD# falling edge should be less than 6ns for 90% to 10%.

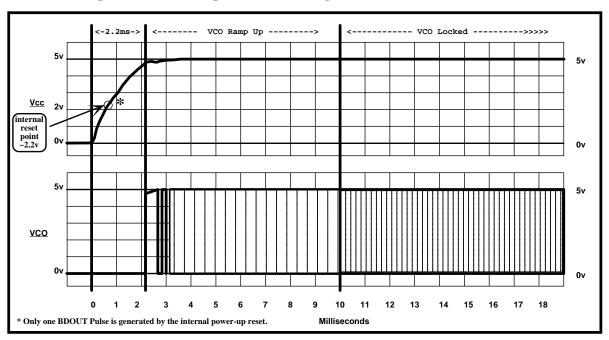

# Vcc Power-Up and VCO Ramp to Lock Timing (Provided for Implementation Reference Purposes only).

## **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com