# PI74FCT162344T

# Fast CMOS Address/Clock Driver

### **Product Features**

- · Ideal for address line driving and clock distribution

- Eight banks with 1:4 fanout with 3-state control

- Typical tsk(o) output skew < 500ps

- Balanced output drivers: ±24mA

- · Hysteresis on all inputs

- · Packages available:

- 56-pin 240-mil wide plastic TSSOP (A)

- 56-pin 300-mil wide plastic SSOP(V)

## **Product Description**

Pericom Semiconductor's PI74FCT series of logic circuits are produced in the Company's advanced 0.6 micron CMOS technology, achieving industry leading speed grades.

The PI74FCT162344T is an address/clock driver designed to provide the ability to fanout to memory arrays. Eight banks, each with a fanout of four, and 3-state control, provide efficient address distribution. One or more banks may be used for clock distribution.

The PI74FCT162344T has balanced output drivers. It is designed with current limiting resistors at its outputs to control the output edge rate resulting in lower ground bounce and undershoot. This eliminates the need for external terminating resistors for most interface applications.

## **Logic Block Diagram**

1

# **Product Pin Configuration**

|                   | 0  |            |                    |

|-------------------|----|------------|--------------------|

|                   |    |            |                    |

| OE <sub>1</sub> [ | 1  |            | 56 ☐ OE₄           |

| B <sub>11</sub> [ | 2  |            | 55 B81             |

| B12 [             | 3  |            | 54 B82             |

| GND [             | 4  |            | 53 GND             |

| B13 [             | 5  |            | 52 B83             |

| B14 [             | 6  |            | 51 B84             |

| Vcc [             | 7  |            | 50 Vcc             |

| A1 [              | 8  |            | 49 A8              |

| B21 [             | 9  |            | 48 B71             |

| B22 [             | 10 |            | 47 B72             |

| GND [             | 11 |            | 46 GND             |

| B23 [             | 12 | 54 DIN     | 45 B73             |

| B24 [             | 13 | A56<br>V56 | 44 B74             |

| A2 [              | 14 |            | 43 A7              |

| Аз [              | 15 |            | 42 A6              |

| B31 [             | 16 |            | 41 B <sub>61</sub> |

| B32 [             | 17 |            | 40 B62             |

| GND [             | 18 |            | 39 GND             |

| B33 [             | 19 |            | 38 B63             |

| B34 [             | 20 |            | 37 B64             |

| A4 [              | 21 |            | 36 A5              |

| Vcc [             | 22 |            | 35 VCC             |

| B41 [             | 23 |            | 34 B51             |

| ]                 | 24 |            | 33 B <sub>52</sub> |

| GND [             | 25 |            | 32 GND             |

| B43 [             | 26 |            | 31 B53             |

| B44 [             | 27 |            | 30 B54             |

| ŌĒ2 [             | 28 |            | 29 OE3             |

|                   |    |            |                    |

|                   |    |            |                    |

# **Product Pin Description**

| Pin Name | Description                               |

|----------|-------------------------------------------|

| ŌĒx      | 3-State Output Enable Inputs (Active LOW) |

| Ax       | Inputs                                    |

| Bxx      | 3-State Outputs                           |

| GND      | Ground                                    |

| Vcc      | Power                                     |

# Truth Table(1)

| ]           | Inputs |     |  |

|-------------|--------|-----|--|

| <b>O</b> Ex | Ax     | Bxx |  |

| L           | L      | L   |  |

| L           | Н      | Н   |  |

| Н           | X      | Z   |  |

**Note:** 1. H = High Voltage Level

L = Low Voltage Level

X = Don't Care

Z = High Impedance

## Capacitance ( $TA = 25^{\circ}C$ , f = 1 MHz)

| Parameters <sup>(1)</sup> | Description        | <b>Test Conditions</b> | Тур | Max. | Units |

|---------------------------|--------------------|------------------------|-----|------|-------|

| Cin                       | Input Capacitance  | $V_{IN} = 0V$          | 3.5 | 6.0  | pF    |

| Соит                      | Output Capacitance | Vout = 0V              | 3.5 | 8.0  | pF    |

### **Note:**

1. This parameter is determined by device characterization but is not production tested.

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                    | 65°C to +150°C |

|----------------------------------------|----------------|

| Ambient Temperature with Power Applied | 0°C to +70°C   |

| Supply Voltage to Ground Potential     | 0.5V to +7.0V  |

| DC Input Voltage                       | 0.5V to +7.0V  |

| DC Output Current                      | 60 to +120 mA  |

| Power Dissipation                      | 0.5W           |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Operating Range**

Ambient Temperature = -40°C to +85°C Vcc =  $5.0V \pm 10\%$

## **DC Electrical Characteristics** (Over the Operating Range, $TA = -40^{\circ}C$ to $+85^{\circ}C$ , $VCC = 5.0V \pm 10\%$ )

| Parameters | Description                          | Test Conditions <sup>(1)</sup>                                         |            |          | Min. | Typ <sup>(2)</sup> | Max. | Units |

|------------|--------------------------------------|------------------------------------------------------------------------|------------|----------|------|--------------------|------|-------|

| Voh        | Output HIGH Voltage                  | Vcc = Min, Vin = Vih or Vil IoH = -24mA                                |            | 2.4      | 3.3  | _                  | V    |       |

| Vol        | Output LOW Voltage                   | $V_{CC} = Min., V_{IN} = V$                                            | IH or VIL  | IoL=24mA | _    | 0.3                | 0.55 | V     |

| VIH        | Input HIGH Voltage                   | Guaranteed Logic H                                                     | IIGH Level |          | 2.0  | _                  | _    | V     |

| VIL        | Input LOW Voltage                    | Guaranteed Logic L                                                     | OW Level   |          | _    | _                  | 0.8  | V     |

| Im         | Input HIGH Current                   | Vcc = Max. Vin = Vcc (Input Pins)                                      |            | _        | _    | ±1                 | μΑ   |       |

| IIL        | Input LOW Current                    | Vcc = Max. Vin = GND (Input & I/O Pins)                                |            | _        | _    | ±1                 | μΑ   |       |

| Іохн       | High Impedance                       | Vcc=Max. Vout=2.7V                                                     |            | _        | _    | ±1                 | μΑ   |       |

| Iozl       | Output Current                       | (3-State Output Pins) Vout=0.5V                                        |            | _        | _    | ±1                 |      |       |

| Vik        | Clamp Diode Voltage                  | Vcc = Min., Iin = -18mA                                                |            | _        | -0.7 | -1.2               | V    |       |

| IODH       | Output HIGH Current                  | $V_{CC} = 5V$ , $V_{IN} = V_{IH}$ or $V_{IL}$ , $V_{OUT} = 1.5V^{(3)}$ |            | -60      | -115 | -150               | mA   |       |

| IODL       | Output LOW Current                   | $V_{CC} = 5V$ , $V_{IN} = V_{IH}$ or $V_{IL}$ , $V_{OUT} = 1.5V^{(3)}$ |            |          | 60   | 115                | 150  | mA    |

| Ios        | Short Circuit Current <sup>(4)</sup> | Vcc=Max., Vout=GND <sup>(4)</sup>                                      |            | -80      | -140 | -225               | mA   |       |

| Іоит       | Output Drive Current                 | $V_{CC} = Max., V_{OUT} = 2.5V^{(3)}$                                  |            | -50      | _    | -180               | mA   |       |

| VH         | Input Hysteresis                     |                                                                        |            |          | _    | 100                | _    | mV    |

#### **Notes:**

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 5.0V,  $+25^{\circ}C$  ambient and maximum loading.

- 3. This parameter is determined by device characterization but is not production tested.

- 4. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

## **Power Supply Characteristics**

| Parameters | Description                                        | Test Condition                                                                                 | Test Conditions <sup>(1)</sup>           |  |     | Max.                | Units      |

|------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------|--|-----|---------------------|------------|

| Icc        | Quiescent Power<br>Supply Current                  | Vcc = Max.                                                                                     | V <sub>IN</sub> = GND or V <sub>CC</sub> |  | 0.1 | 500                 | μА         |

| ΔΙcc       | Supply Current per<br>Input @ TTL HIGH             | $V_{CC} = Max.$                                                                                | $V_{IN} = 3.4 V^{(3)}$                   |  | 0.5 | 1.5                 | mA         |

| Іссь       | Supply Current per<br>Input per MHz <sup>(4)</sup> | Vcc = Max., Outputs Open $\overline{OE}x = GND$ One Bit Toggling 50% Duty Cycle                | Vin = Vcc<br>Vin = GND                   |  | 170 | 220                 | μA/<br>MHz |

| Ic         | Total Power Supply<br>Current <sup>(6)</sup>       | Vcc = Max.,<br>Outputs Open<br>fi = 10 MHz<br>50% Duty Cycle<br>$\overline{\text{OE}}$ x = GND | Vin = Vcc<br>Vin = GND                   |  | 1.7 | 2.7 <sup>(5)</sup>  | mA         |

|            |                                                    | One Bit Toggling                                                                               | $V_{IN} = 3.4 V$<br>$V_{IN} = GND$       |  | 2.0 | 3.5 <sup>(5)</sup>  |            |

|            |                                                    | Vcc = Max., Outputs Open fr = 2.5 MHz 50% Duty Cycle OEx = GND                                 | Vin = Vcc<br>Vin = GND                   |  | 3.4 | 4.9 <sup>(5)</sup>  |            |

|            |                                                    | 16 Bits Toggling                                                                               | $V_{IN} = 3.4 V$<br>$V_{IN} = GND$       |  | 5.4 | 10.9 <sup>(5)</sup> |            |

#### **Notes:**

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device.

- 2. Typical values are at Vcc = 5.0 V,  $+25^{\circ}\text{C}$  ambient.

- 3. Per TTL driven input ( $V_{IN} = 3.4 \text{ V}$ ); all other inputs at Vcc or GND.

- 4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 5. Values for these conditions are examples of the Icc formula. These limits are guaranteed but not tested.

- 6. IC = IQUIESCENT + IINPUTS + IDYNAMIC

- $IC = ICC + \Delta ICC DhNT + ICCD (fcp/2 + fiNi)$

- Icc = Quiescent Current

- $\Delta$ Icc = Power Supply Current for a TTL High Input (ViN = 3.4 V)

- DH = Duty Cycle for TTL Inputs High

- N<sub>T</sub> = Number of TTL Inputs at D<sub>H</sub>

- ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

- fcp = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- fi = Input Frequency

- Ni = Number of Inputs at fi

- All currents are in milliamps and all frequencies are in megahertz.

## **Switching Characteristics over Operating Range**

|                          |                                |                              | 162344AT |     | 162344CT |      | 162344ET |      |      |

|--------------------------|--------------------------------|------------------------------|----------|-----|----------|------|----------|------|------|

|                          |                                |                              | Co       | m.  | Com.     |      | Com.     |      |      |

| Parameters               | Description                    | Conditions <sup>(1)</sup>    | Min      | Max | Min      | Max  | Min      | Max  | Unit |

| tPLH<br>tPHL             | Propagation Delay<br>Ax to Bx  | $CL = 50pF$ $RL = 500\Omega$ | 1.5      | 4.8 | 1.5      | 4.3  | 1.5      | 3.8  | ns   |

| tpzh<br>tpzl             | Output Enable Time OEx to Bx   |                              | 1.5      | 6.2 | 1.5      | 5.8  | 1.5      | 5.0  | ns   |

| tphz<br>tplz             | Output Disable Time  OEx to Bx |                              | 1.5      | 5.6 | 1.5      | 5.2  | 1.5      | 4.6  | ns   |

| tsĸ1(o) <sup>(3,5)</sup> | Output Skew                    |                              | _        | 0.5 | _        | 0.35 | _        | 0.25 | ns   |

| tsk2(o) <sup>(4,5)</sup> | Output Skew                    |                              | _        | 0.5 | _        | 0.5  | _        | 0.3  | ns   |

#### **Notes:**

- 1. See test circuit and waveforms.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

- 3. Skew between outputs of the same bank and same package, switching in the same transition.

- 4. Skew between outputs of all banks of the same package with A1 through A8 tied together, switching in the same transition.

- 5. This parameter is guaranteed but not production tested.

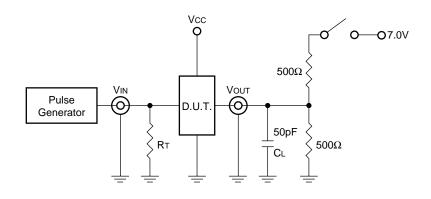

## Tests Circuits For All Outputs(1)

### **Switch Position**

| Test                      | Switch |

|---------------------------|--------|

| Disable LOW<br>Enable LOW | 7V     |

| All Other Tests           | Open   |

#### **DEFINITIONS:**

CL = Load capacitance: includes jig and probe capacitance.

$\hat{\mathbf{R}}$ T = Termination resistance: should be equal to ZOUT of the Pulse Generator.

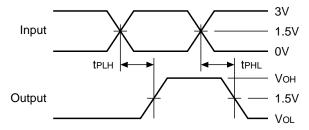

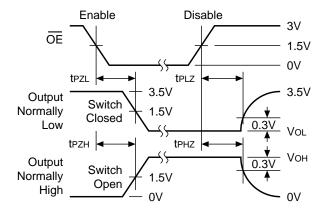

### SWITCHING WAVEFORMS

## **Propagation Delay**

### **Enable and Disable Times**

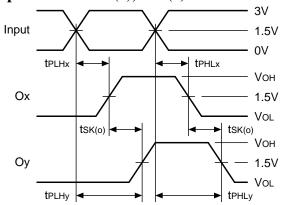

## Output Skew – tsk1(0), tsk2(0)

$$tsk(0) = |tPLHy - tPLHx|or|tPHLy - tPHLx|$$

#### Note:

$ts\kappa 1(o) = Ox$  and Oy are in the same bank.

tsk21(o) = Ox and Oy are in a different bank on the same port.