# High Speed and Performance

# PowerPC 604e RISC Microprocessor 250, 300, 333 and 350MHz

# **Highlights**

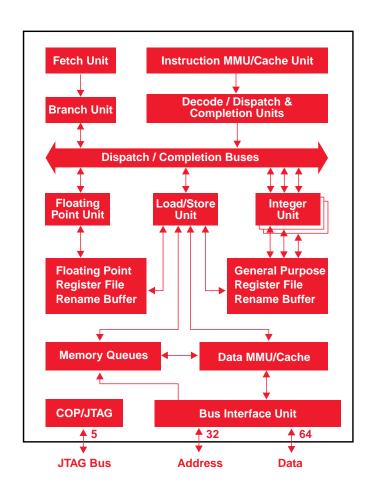

# **Dispatch Unit**

- Dispatch up to 4 instructions per cycle

- 8-instruction dispatch buffer

# **Completion Unit**

Completes up to 4 instructions plus 1 store and 1 branch per cycle

# Integer Unit

- 2 Simple Fixed Point units

- 1 Complex Fixed Point unit

# **Load/Store Unit**

- Hardware supported misaligned little endian accesses

- Hardware controlled load-multiple and store-multiple registers and byte strings

- Data alignment to byte addresses

- Out of order loads and stores

# **Integrated Floating Point Unit**

IEEE-754 standard single-and doubleprecision floating point arithmetic

#### Cache

- Separate instruction and data caches, each 32K bytes, 4-way set associative

- 32-byte cache line

- Physically indexed, physical tags

- Hardware invalidate all cache lines

- Write-in and write-through data cache

- Data cache line-fill buffer forwarding

- Software cache disable

# **Branch Prediction and Processing**

- 512-entry branch history table

- 64-entry branch target address cache, fully associative

- Branch prediction for unresolved branches

# **Memory Management Structure**

- 32-bit real memory support for up to 4 GB

- 64-entry 2-way instruction and data TLB

- Hardware controlled TLB mishandling

# **MultiprocessorSupport**

- Bus snooping

- 4-state MESI data cache coherency control

- Dual port data cache tags

- Software controlled Instruction cache coherency, programmable coherent instruction fetch mode

### **Bus Interface**

- 32-bit real address

- 64-bit data

- Processor Clock: Bus Clock ratios of 1:1,3:2, 2:1,5:2,3:1,7:2,4:1,9:2,5:1,11:2,6:1,13:2,7:1

# **Performance Monitor**

- Four programmable event counting registers

- Programmable trigger or interrupt signal

#### Testability

- IEEE 1149.1 (JTAG) compatible chip interface

- Level Sensitive Scan Design (LSSD)

# **Product Description**

The PowerPC 604e\* microprocessor is a 32-bit implementation of the PowerPC\* family of Reduced Instruction Set Computer (RISC) microprocessors. It is a functionally equivalent, enhanced microarchitecture derivative of the PowerPC 604e microprocessor using split voltages of 1.9 VDC for core logic and 3.3 VDC for I/O. The PowerPC 604e microprocessor is targeted at the workstation, PC server and power user desktop segments. The suite of operating environments available to systems designed in accordance with the PowerPC microprocessor Common Hardware Reference Platform Specification includes: Mac OS\*\*, AIX\*.

Enhancements to the PowerPC 604e microprocessor over previous releases include:

- Advanced .25 micron CMOS technology

- Higher clock frequencies with increased bus divider ratios

- Extended debug mode

| Specifications                 | PID 9q-604e and PID 10 q-604e                                                                                                                                                                                      |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                     | .25µm / .15µmLeff - CMOS technology, six levels of metal                                                                                                                                                           |

| Die Size                       | 47 mm <sup>2</sup>                                                                                                                                                                                                 |

| Number of Transistors          | ~5.1 million                                                                                                                                                                                                       |

| Performance (estimated)        | 11.1 SPECint95, 78 SPECfp95 @ 250/71, 1M L2 cache<br>12.9 SPECint95, 8.5 SPECfp95 @ 300/75, 1M L2 cache<br>13.9 SPECint95, 8.6 SPECfp95 @ 333/74, 1M L2 cache<br>14.6 SPECint95, 90 SPECfp95 @ 350/77, 1M L2 cache |

| Signal I/Os                    | 171                                                                                                                                                                                                                |

| Power Supply <sup>†</sup>      | 1.9 V ± 100 mV Core<br>3.3 V ± 5% I/O                                                                                                                                                                              |

| Power Dissipation (est, typ)   | 7.5W@333MHz                                                                                                                                                                                                        |

| Temperature Range <sup>†</sup> | 0°C to 85°C                                                                                                                                                                                                        |

| Packaging                      | BGA                                                                                                                                                                                                                |

© International Business Machines Corporation 1997 Printed in the United States of America 7-97

All Rights Reserved

- \* Indicates a trademark or registered trademark of the International Business Machines Corporation.

- \*\* All other products and company names are trademarks or registered trademarks of their respective holders.

The information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM's product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All the information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THEINFORMATION CONTAINED INTHIS DOCUMENTIS PROVIDED ON AN"ASIS" BASIS. In no event will IBM be liable for any damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6531 (800) POWERPC

The IBM home page can be found at: http://www.ibm.com

The IBM Microelectronics Division home page can be found at:

http://www.chips.ibm.com

This product's URL is:

http://www.chips.ibm.com/products/ppc