# ICs for Communications

ATM Switching Preprocessor ASP

PXB 4325 E Version 1.1

Preliminary Data Sheet 08.98

| PXB 4325 E                       | PXB 4325 E                      |                                              |  |

|----------------------------------|---------------------------------|----------------------------------------------|--|

| Revision His                     | story:                          | Current Version: 08.98                       |  |

| Previous Ver                     | sion:                           | None                                         |  |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |

|                                  |                                 |                                              |  |

|                                  |                                 |                                              |  |

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide: see our webpage at http://www.siemens.de/semiconductor/communication.

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4μC, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

MUSAC™-A, FALC™54, IWE™, SARE™, UTPT™, ASM™, ASP™, DigiTape™ are trademarks of Siemens AG.

#### Edition 08.98

This edition was realized using the software system FrameMaker'.

Published by Siemens AG.

HL SP

Balanstraße 73,

81541 München

© Siemens AG 1998.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| 1.1       ATM Layer Chip Set Overview       8         1.2       Nomenclature       10         1.3       Features       11         1.4       Logic Symbol       15         1.5       Functional Overview       16         1.6       Data Flow       17         1.6.1       Throughput       17         1.6.2       Upstream Data Flow       17         1.6.3       Downstream Data Flow       19         1.7       Header Translation       19         1.7.1       Upstream Address Reduction       21         1.7.2       Upstream Header Translation       22         1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.8       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Swit                                                                                                                                                                     | Table of Contents Pa |                                         | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------|------|

| 1.1       ATM Layer Chip Set Overview       .8         1.2       Nomenclature       .10         1.3       Features       .11         1.4       Logic Symbol       .15         1.5       Functional Overview       .16         1.6       Data Flow       .17         1.6.1       Throughput       .17         1.6.2       Upstream Data Flow       .17         1.6.3       Downstream Data Flow       .19         1.7       Header Translation       .19         1.7.1       Upstream Address Reduction       .21         1.7.2       Upstream Header Translation       .22         1.7.3       Downstream Header Translation       .22         1.8       Shared Buffer       .27         1.8       Shared Buffer Overview       .27         1.8       Shared Buffer Overview       .27         1.9       Special Cell Type Recognition       .29         1.10       Insertion and Extraction of Cells       .29         1.11       Communication Channel (RSATM)       .29         1.12       Cell Synchronization of Downstream Dataflow       .30         1.13       Recombining Function       .31         1.14       L                                                                                                                                                                     | 1                    | Overview                                | 8    |

| 1.2       Nomenclature       10         1.3       Features       11         1.4       Logic Symbol       15         1.5       Functional Overview       16         1.6       Data Flow       17         1.6.1       Throughput       17         1.6.2       Upstream Data Flow       17         1.6.3       Downstream Data Flow       19         1.7       Header Translation       19         1.7.1       Upstream Address Reduction       21         1.7.2       Upstream Header Translation       22         1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.8       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Cill Sy                                                                                                                                                                     | 1.1                  |                                         |      |

| 1.4       Logic Symbol       15         1.5       Functional Overview       16         1.6       Data Flow       17         1.6.1       Throughput       17         1.6.2       Upstream Data Flow       17         1.6.3       Downstream Data Flow       19         1.7       Header Translation       19         1.7.1       Upstream Address Reduction       21         1.7.2       Upstream Header Translation       22         1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2                                                                                                                                                            | 1.2                  | · · · · · · · · · · · · · · · · · · ·   |      |

| 1.5         Functional Overview         16           1.6         Data Flow         17           1.6.1         Throughput         17           1.6.2         Upstream Data Flow         17           1.6.3         Downstream Data Flow         19           1.7         Header Translation         19           1.7.1         Upstream Address Reduction         21           1.7.2         Upstream Header Translation         22           1.7.3         Downstream Header Translation         22           1.8         Shared Buffer Overview         27           1.8.1         Shared Buffer Overview         27           1.9         Special Cell Type Recognition         29           1.10         Insertion and Extraction of Cells         29           1.11         Communication Channel (RSATM)         29           1.12         Cell Synchronization of Downstream Dataflow         30           1.13         Recombining Function         31           1.14         Line Protection Switch (LPS) Mechanism         33           1.15         Clocks         35           2         Register Description         36           2.1         Receive Cell Buffer Access Register (RXR)         43 <td>1.3</td> <td>Features</td> <td>11</td>                                      | 1.3                  | Features                                | 11   |

| 1.5         Functional Overview         16           1.6         Data Flow         17           1.6.1         Throughput         17           1.6.2         Upstream Data Flow         17           1.6.3         Downstream Data Flow         19           1.7         Header Translation         19           1.7.1         Upstream Address Reduction         21           1.7.2         Upstream Header Translation         22           1.7.3         Downstream Header Translation         22           1.8         Shared Buffer Overview         27           1.8.1         Shared Buffer Overview         27           1.9         Special Cell Type Recognition         29           1.10         Insertion and Extraction of Cells         29           1.11         Communication Channel (RSATM)         29           1.12         Cell Synchronization of Downstream Dataflow         30           1.13         Recombining Function         31           1.14         Line Protection Switch (LPS) Mechanism         33           1.15         Clocks         35           2         Register Description         36           2.1         Receive Cell Buffer Access Register (RXR)         43 <td>1.4</td> <td>Logic Symbol</td> <td>15</td>                                  | 1.4                  | Logic Symbol                            | 15   |

| 1.6.1       Throughput       .17         1.6.2       Upstream Data Flow       .17         1.6.3       Downstream Data Flow       .19         1.7       Header Translation       .21         1.7.1       Upstream Address Reduction       .21         1.7.2       Upstream Header Translation       .22         1.7.3       Downstream Header Translation       .22         1.8       Shared Buffer Overview       .27         1.8.1       Shared Buffer Overview       .27         1.9       Special Cell Type Recognition       .29         1.10       Insertion and Extraction of Cells       .29         1.11       Communication Channel (RSATM)       .29         1.12       Cell Synchronization of Downstream Dataflow       .30         1.13       Recombining Function       .31         1.14       Line Protection Switch (LPS) Mechanism       .33         1.15       Clocks       .35         2       Register Description       .36         2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register Upstream (CONFUP)       .46         2.4       Configuration Register Upstream (CONFUP)       .46 <t< td=""><td>1.5</td><td></td><td></td></t<>                                                                         | 1.5                  |                                         |      |

| 1.6.1       Throughput       .17         1.6.2       Upstream Data Flow       .17         1.6.3       Downstream Data Flow       .19         1.7       Header Translation       .21         1.7.1       Upstream Address Reduction       .21         1.7.2       Upstream Header Translation       .22         1.7.3       Downstream Header Translation       .22         1.8       Shared Buffer Overview       .27         1.8.1       Shared Buffer Overview       .27         1.9       Special Cell Type Recognition       .29         1.10       Insertion and Extraction of Cells       .29         1.11       Communication Channel (RSATM)       .29         1.12       Cell Synchronization of Downstream Dataflow       .30         1.13       Recombining Function       .31         1.14       Line Protection Switch (LPS) Mechanism       .33         1.15       Clocks       .35         2       Register Description       .36         2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register Upstream (CONFUP)       .46         2.4       Configuration Register Upstream (CONFUP)       .46 <t< td=""><td>1.6</td><td>Data Flow</td><td>17</td></t<>                                                              | 1.6                  | Data Flow                               | 17   |

| 1.6.3       Downstream Data Flow       19         1.7       Header Translation       19         1.7.1       Upstream Address Reduction       21         1.7.2       Upstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register Upstream 0 (CONFUPO)       46         2.4       Configuration Register Upstream 1 (CONFUPO)       46         2.4       Configuration Register Upstream (CONFUPO)       48         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register On (IRRO)       50 <td>1.6.1</td> <td></td> <td></td>                                                      | 1.6.1                |                                         |      |

| 1.6.3       Downstream Data Flow       19         1.7       Header Translation       19         1.7.1       Upstream Address Reduction       21         1.7.2       Upstream Header Translation       22         1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48 <td>1.6.2</td> <td>Upstream Data Flow</td> <td>17</td>                                             | 1.6.2                | Upstream Data Flow                      | 17   |

| 1.7.1       Upstream Address Reduction       21         1.7.2       Upstream Header Translation       22         1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 1 (CONFUPO)       46         2.4       Configuration Register Upstream 0 (CONFUPO)       48         2.6       Configuration Register (DINTHED)       48         2.6       Configuration Register (DINTHED)                                                                                         | 1.6.3                | ·                                       |      |

| 1.7.2       Upstream Header Translation       22         1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Mask Register 0 (ISR0) <td>1.7</td> <td>Header Translation</td> <td>19</td>                            | 1.7                  | Header Translation                      | 19   |

| 1.7.2       Upstream Header Translation       .22         1.7.3       Downstream Header Translation       .22         1.8       Shared Buffer       .27         1.8.1       Shared Buffer Overview       .27         1.9       Special Cell Type Recognition       .29         1.10       Insertion and Extraction of Cells       .29         1.11       Communication Channel (RSATM)       .29         1.12       Cell Synchronization of Downstream Dataflow       .30         1.13       Recombining Function       .31         1.14       Line Protection Switch (LPS) Mechanism       .33         1.15       Clocks       .35         2       Register Description       .36         2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUPO)       .46         2.4       Configuration Register Upstream 1 (CONFUPO)       .46         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status                                                                              | 1.7.1                |                                         |      |

| 1.7.3       Downstream Header Translation       22         1.8       Shared Buffer       27         1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register (DMR)       50         2.7       Command Register (OMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Mask Register 0 (IMR0)       <                                                                                  | 1.7.2                | •                                       |      |

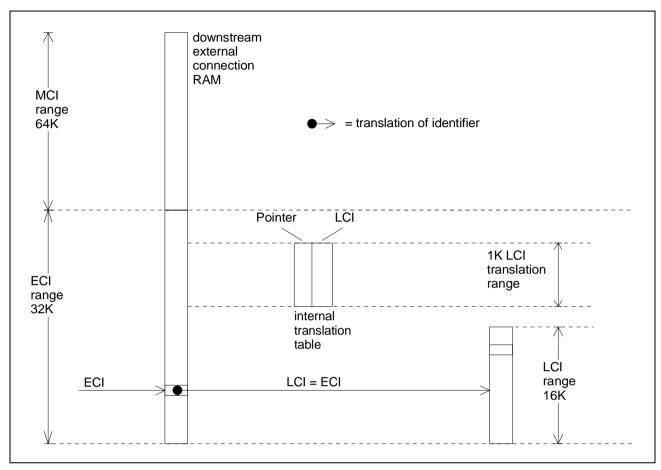

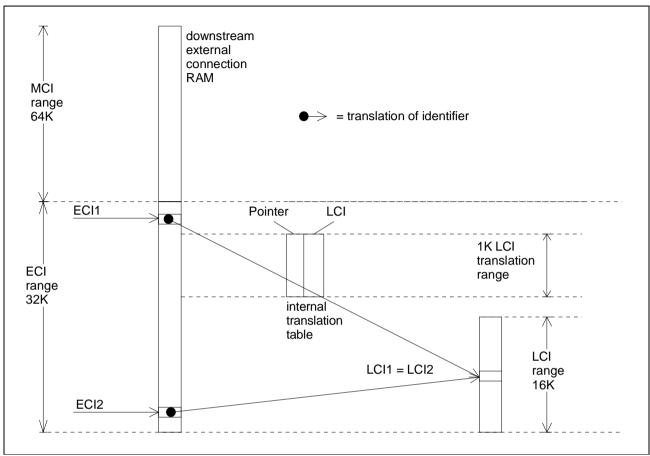

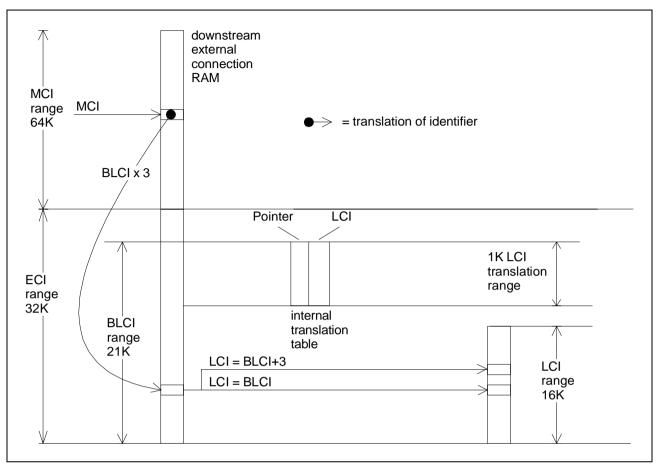

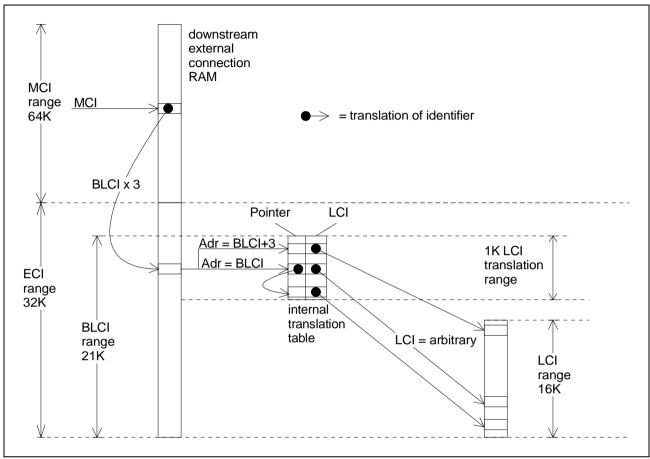

| 1.8       Shared Buffer       .27         1.8.1       Shared Buffer Overview       .27         1.9       Special Cell Type Recognition       .29         1.10       Insertion and Extraction of Cells       .29         1.11       Communication Channel (RSATM)       .29         1.12       Cell Synchronization of Downstream Dataflow       .30         1.13       Recombining Function       .31         1.14       Line Protection Switch (LPS) Mechanism       .33         1.15       Clocks       .35         2       Register Description       .36         2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Mask Register 0 (IMR0)       .55         2.10       Interrupt                                                                              | 1.7.3                | ·                                       |      |

| 1.8.1       Shared Buffer Overview       27         1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Mask Register 0 (IMR0)       52         2.10       Interrupt Mask Register 0 (IMR0)       55         2.10.2       Interru                                                                             | 1.8                  |                                         |      |

| 1.9       Special Cell Type Recognition       29         1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       55         2.10.1       Interrupt Mask Register 0 (IMR0)       55         2.10.2       Interrupt Header Capture Register Upstream (UINTADR)       56                                                          | 1.8.1                |                                         |      |

| 1.10       Insertion and Extraction of Cells       29         1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Status Register 0 and 1 (IMR0 and IMR1)       55         2.10.1       Interrupt Mask Register 0 and 1 (IMR0       55         2.10.2       Interrupt Mask Register 1 (IMR1)       55         2.10.2       Interrupt Header Capture Register Upstream (UINTADR)       56 <td>1.9</td> <td></td> <td></td>            | 1.9                  |                                         |      |

| 1.11       Communication Channel (RSATM)       29         1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Status Register 0 (ISR0)       52         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       55         2.10.1       Interrupt Mask Register 0 and 1 (IMR0)       55         2.10.2       Interrupt Header Capture Register Upstream (UINTADR)       56         2.11       Interrupt Header Capture Register Upstream (UINTADR) <td>1.10</td> <td>•</td> <td></td> | 1.10                 | •                                       |      |

| 1.12       Cell Synchronization of Downstream Dataflow       30         1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       55         2.10.1       Interrupt Mask Register 0 (IMR0)       55         2.10.2       Interrupt Mask Register 0 (IMR0)       55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       56         2.12       Downstream Header Capture 0 (DHCR0)       56                                                | 1.11                 |                                         |      |

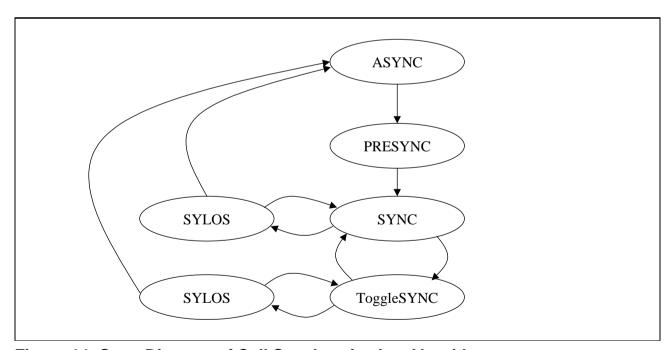

| 1.13       Recombining Function       31         1.14       Line Protection Switch (LPS) Mechanism       33         1.15       Clocks       35         2       Register Description       36         2.1       Receive Cell Buffer Access Register (RXR)       43         2.2       General Configuration Register (CONGEN)       45         2.3       Configuration Register Upstream 0 (CONFUP0)       46         2.4       Configuration Register Upstream 1 (CONFUP1)       47         2.5       Upstream Internal Header Register (UINTHED)       48         2.6       Configuration Register Downstream (CONFDN)       49         2.7       Command Register (CMR)       50         2.8       Interrupt Status Register 0 (ISR0)       52         2.9       Interrupt Status Register 1 (ISR1)       53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       55         2.10.1       Interrupt Mask Register 0 (IMR0)       55         2.10.2       Interrupt Header Capture Register Upstream (UINTADR)       56         2.11       Downstream Header Capture 0 (DHCR0)       56         2.12       Downstream Header Capture 1 (DHCR1)       57         2.14       High Speed Input Line Status (LINSTAT)       58                                                 | 1.12                 | · · · · · · · · · · · · · · · · · · ·   |      |

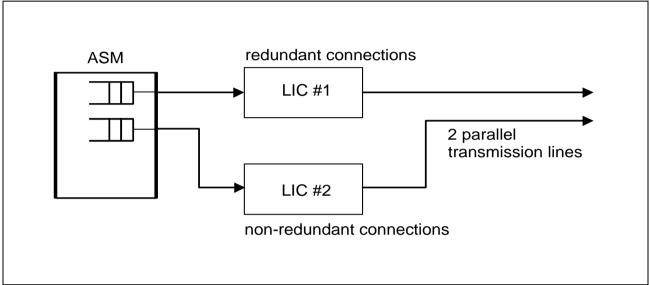

| 1.14       Line Protection Switch (LPS) Mechanism       .33         1.15       Clocks       .35         2       Register Description       .36         2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 1 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LIN                                 | 1.13                 | · · · · · · · · · · · · · · · · · · ·   |      |

| 1.15       Clocks       .35         2       Register Description       .36         2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register                                  | _                    |                                         |      |

| 2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                    | 1.15                 | , ,                                     |      |

| 2.1       Receive Cell Buffer Access Register (RXR)       .43         2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                    | 2                    | Register Description                    | 36   |

| 2.2       General Configuration Register (CONGEN)       .45         2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                          |                      | •                                       |      |

| 2.3       Configuration Register Upstream 0 (CONFUP0)       .46         2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                                                                                              |                      |                                         |      |

| 2.4       Configuration Register Upstream 1 (CONFUP1)       .47         2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                                                                                                                                                                      |                      |                                         |      |

| 2.5       Upstream Internal Header Register (UINTHED)       .48         2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                                                                                                                                                                                                                                              |                      |                                         |      |

| 2.6       Configuration Register Downstream (CONFDN)       .49         2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |                                         |      |

| 2.7       Command Register (CMR)       .50         2.8       Interrupt Status Register 0 (ISR0)       .52         2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                                         |      |

| Interrupt Status Register 0 (ISR0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                                         |      |

| 2.9       Interrupt Status Register 1 (ISR1)       .53         2.10       Interrupt Mask Register 0 and 1 (IMR0 and IMR1)       .55         2.10.1       Interrupt Mask Register 0 (IMR0)       .55         2.10.2       Interrupt Mask Register 1 (IMR1)       .55         2.11       Interrupt Header Capture Register Upstream (UINTADR)       .56         2.12       Downstream Header Capture 0 (DHCR0)       .56         2.13       Downstream Header Capture 1 (DHCR1)       .57         2.14       High Speed Input Line Status (LINSTAT)       .58         2.15       FCS1+FCS2 Error Counter Register (FECR)       .59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                                         |      |

| 2.10Interrupt Mask Register 0 and 1 (IMR0 and IMR1).552.10.1Interrupt Mask Register 0 (IMR0).552.10.2Interrupt Mask Register 1 (IMR1).552.11Interrupt Header Capture Register Upstream (UINTADR).562.12Downstream Header Capture 0 (DHCR0).562.13Downstream Header Capture 1 (DHCR1).572.14High Speed Input Line Status (LINSTAT).582.15FCS1+FCS2 Error Counter Register (FECR).59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                                         |      |

| 2.10.1       Interrupt Mask Register 0 (IMR0) <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                                         |      |

| 2.10.2Interrupt Mask Register 1 (IMR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | • • • • • • • • • • • • • • • • • • • • |      |

| 2.11Interrupt Header Capture Register Upstream (UINTADR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | · · · · · · · · · · · · · · · · · · ·   |      |

| 2.12Downstream Header Capture 0 (DHCR0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | ·                                       |      |

| 2.13 Downstream Header Capture 1 (DHCR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |                                         |      |

| 2.14 High Speed Input Line Status (LINSTAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                                         |      |

| 2.15 FCS1+FCS2 Error Counter Register (FECR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      | · · · · · · · · · · · · · · · · · · ·   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.16                 |                                         |      |

| Table of | Contents                                                      | Page |

|----------|---------------------------------------------------------------|------|

| 2.17     | Multicast RAM Part Offset Register (MCOF)                     | 61   |

| 2.18     | Queue Length Register High/Low Priority (QLEN)                |      |

| 2.19     | Internal Pointer RAM Location (MCRANGE)                       |      |

| 2.20     | TXR Queue Select Register (TXQSEL)                            |      |

| 2.21     | Upstream RAM Data Registers (URAM0LURAM2H)                    |      |

| 2.21.1   | General Mapping Registers to Dwords                           |      |

| 2.21.2   | Upstream RAM Dword Contents                                   |      |

| 2.21.2.1 | Upstream RAM : Dword0                                         |      |

| 2.21.2.2 | Upstream RAM : Dword1                                         |      |

| 2.21.2.3 | Upstream RAM : Dword2                                         | 66   |

| 2.22     | Address for Upstream RAM Entry (URADR)                        | 66   |

| 2.23     | Address for Downstream RAM Entry (DRADR)                      |      |

| 2.24     | Downstream RAM Data Registers (DRAM0LDRAM2H)                  |      |

| 2.24.1   | General Mapping to Dwords                                     |      |

| 2.24.2   | Downstream RAM Dword Contents: Point-to-Point Connection      | 68   |

| 2.24.2.1 | Downstream RAM : Dword0                                       | 68   |

| 2.24.2.2 | Downstream RAM : Dword1                                       | 69   |

| 2.24.2.3 | Downstream RAM : Dword2                                       |      |

| 2.24.3   | Downstream RAM Dword Contents: Point-to-Multipoint Connection | 71   |

| 2.24.3.1 | Downstream RAM : Dword0                                       |      |

| 2.25     | Pointer RAM Address (PRAMADR)                                 | 72   |

| 2.26     | Pointer RAM Pointer +E-Bit Entry (PRAMPT)                     |      |

| 2.27     | Pointer RAM LCI Entry (PRAMLCI)                               |      |

| 2.28     | RPC Algorithm Register (RPCALG)                               | 74   |

| 2.29     | Cell Header for Upstream Insertion (TXR02)                    |      |

| 2.30     | Cell Header for Downstream Insertion (TXR02)                  |      |

| 2.31     | Cell Payload (TXR327)                                         | 76   |

| 2.32     | Utopia Configuration Register 0 (CONUT0)                      | 77   |

| 2.33     | Utopia Configuration Register 1 (CONUT1)                      | 78   |

| 2.34     | Utopia Configuration Register 2 (CONUT2)                      | 78   |

| 2.35     | Downstream Test Connection Registers (DITC1LDITC2H)           | 79   |

| 2.35.1   | General Mapping Registers to Dwords                           |      |

| 2.35.2   | Downstream Test Connection Dword Contents                     | 79   |

| 2.36     | Upstream Test Connection Registers (UITC0LUITC2H)             | 80   |

| 2.36.1   | General Mapping Registers to Dwords                           |      |

| 2.36.2   | Upstream Test Connection Dword Contents                       | 80   |

| 2.37     | Test Register 0 (TSTR0)                                       | 81   |

| 2.38     | Test Register 1 (TSTR1)                                       | 82   |

| 2.39     | Test Register 2 (TSTR2)                                       |      |

| 2.40     | Version Register Low (VERL)                                   |      |

| 2.41     | Version Register High (VERH)                                  |      |

| 2.42     | RAM BIST Done Bits 0 (RBDONE0)                                |      |

| Table of C                                         | Table of Contents Pag                                                                                                                                                                 |                      |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.43<br>2.44<br>2.45                               | RAM BIST Done Bits 1 (RBDONE1)                                                                                                                                                        | 83                   |

| <b>3</b><br>3.1<br>3.2                             | Operation                                                                                                                                                                             | 85                   |

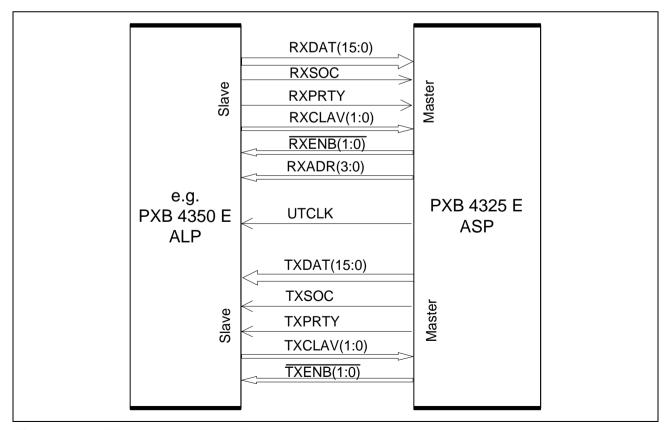

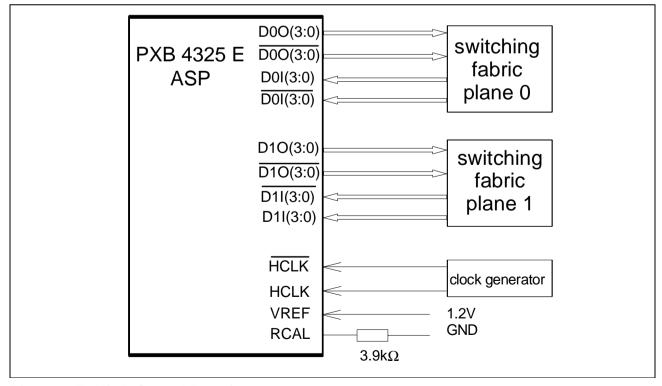

| 4<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Interfaces UTOPIA Interface High Speed Interface Upstream RAM Interface Downstream RAM Interface Communication Channel / RSATM Interface JTAG Interface Pin Definitions and Functions | 89<br>96<br>96<br>99 |

| <b>5</b><br>5.1<br>5.2                             | Electrical Characteristics                                                                                                                                                            | .109                 |

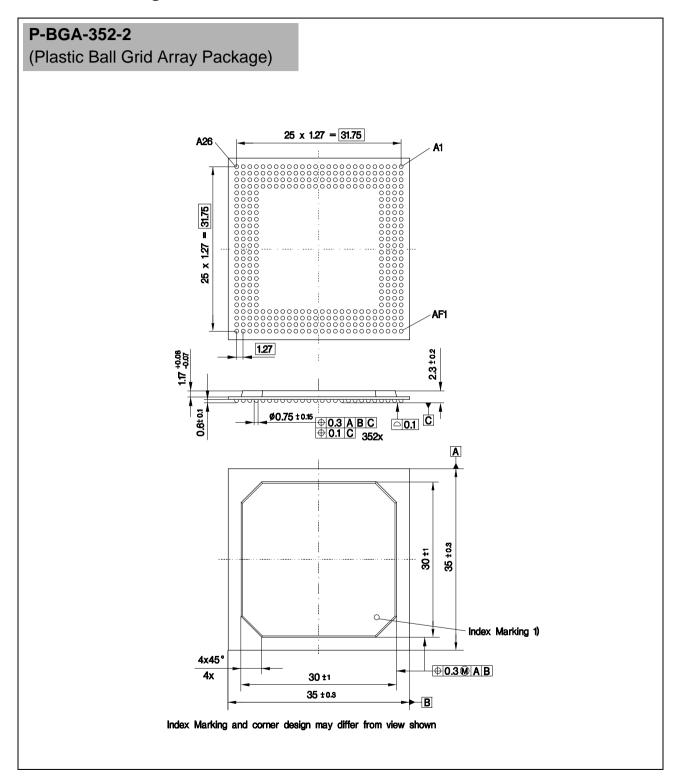

| 6                                                  | Package Outlines                                                                                                                                                                      | .110                 |

| <b>7</b><br>7.1<br>7.2                             | Overview ListsReferencesAcronyms                                                                                                                                                      | .112                 |

| List of Fig            | jures                                                                  | Page |

|------------------------|------------------------------------------------------------------------|------|

| Figure 1:<br>Figure 2: | ATM Switch Basic Configuration                                         | 9    |

| Figure 3:              | Nomenclature                                                           |      |

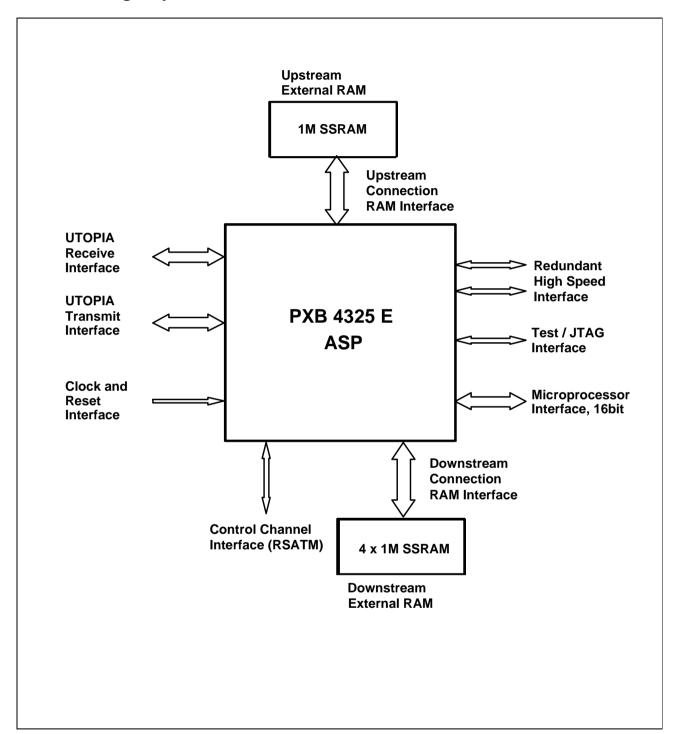

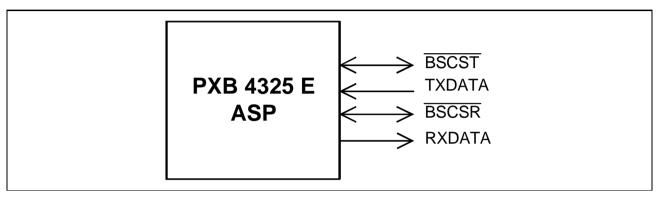

| Figure 4:              | Logic Symbol                                                           |      |

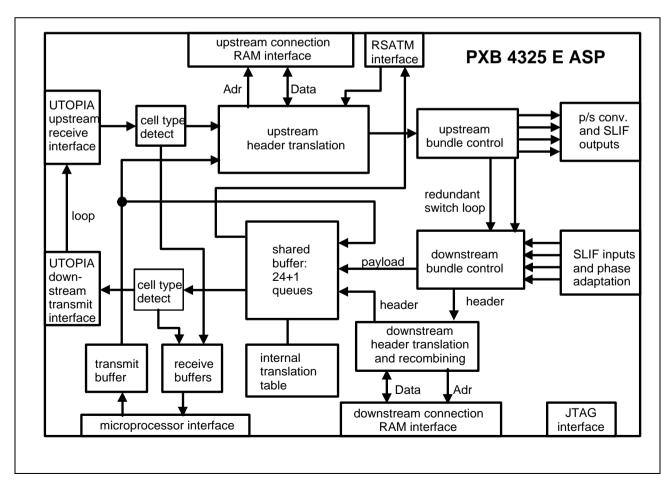

| Figure 5:              | Block Diagram                                                          |      |

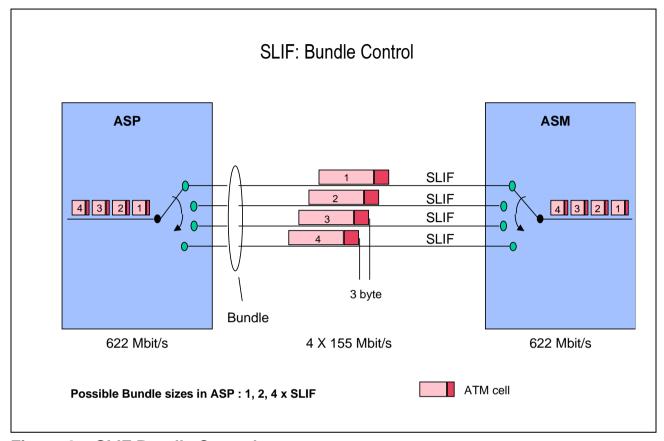

| Figure 6:              | SLIF Bundle Control                                                    | 18   |

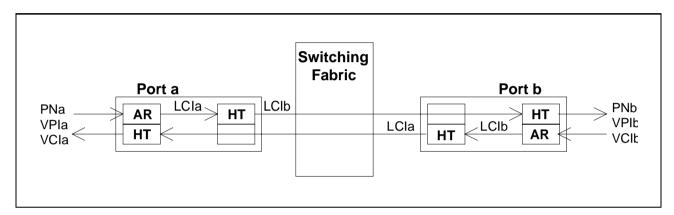

| Figure 7:              | Header Translation for Point-to-Point Connection                       |      |

|                        | with                                                                   |      |

|                        | AR = Address Reduction                                                 | 00   |

| Г:                     | HT = Header Translation                                                | 20   |

| Figure 8:              | Header Translation for Multicast and Merger Connections with           |      |

|                        | AR = Address Reduction                                                 | 0.4  |

| Ε'                     | HT = Header Translation                                                |      |

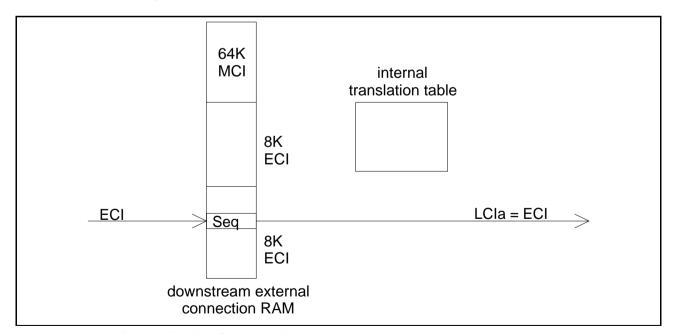

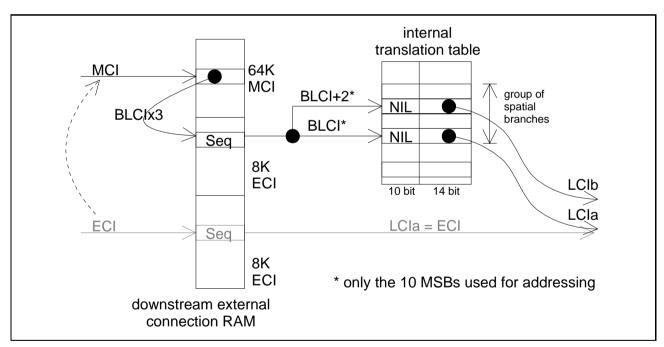

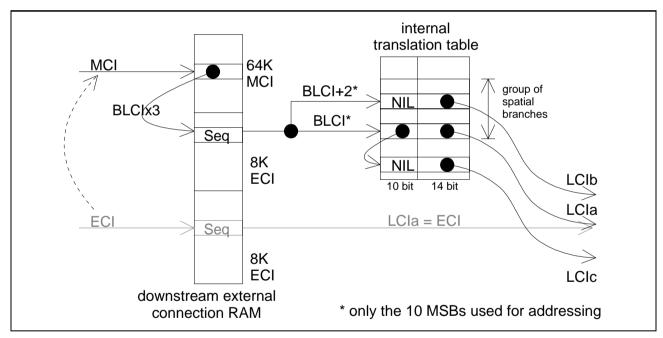

| Figure 9:              |                                                                        |      |

|                        | Downstream Header Translation for Merger Connections                   |      |

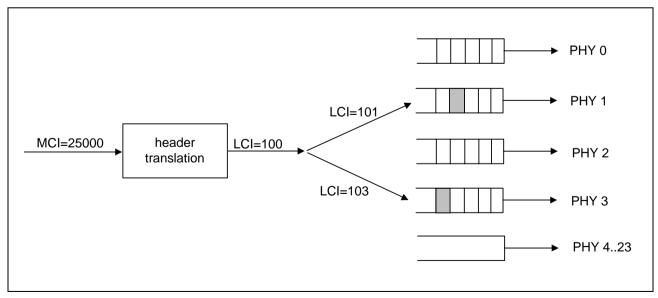

| -                      | Spatial Multicast without Header Translation                           | 25   |

|                        | Mixed Spatial and Logical Multicast with Downstream Header Translation |      |

| •                      | Example for Spatial Multicast                                          |      |

| •                      | State Diagram of Cell Synchronization Algorithm                        |      |

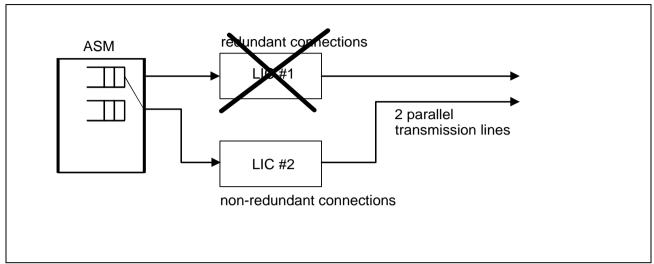

| •                      | Redundant LIC Configuration in Normal Case (Downstream Direction)      |      |

| •                      | Redundant LIC Configuration in Failure Case (Upstream Direction)       |      |

| •                      | Receive Cell Formats                                                   |      |

| •                      | Point-to-Point Connection                                              |      |

| Figure 19:             | Extension to a Third Party                                             | 86   |

|                        | Extension to a Further, Logical Multicast Branch                       |      |

| •                      | Original Receiver of Multi-Party Call Removed                          | 88   |

| Figure 22:             | Standardized UTOPIA Cell Format (16-bit)                               |      |

|                        | All Fields According to Standards, Unused Octets Shaded                |      |

| -                      | Proprietary UTOPIA Cell Format (16-bit)                                |      |

| •                      | UTOPIA Interface Example                                               |      |

| •                      | High Speed Interface                                                   |      |

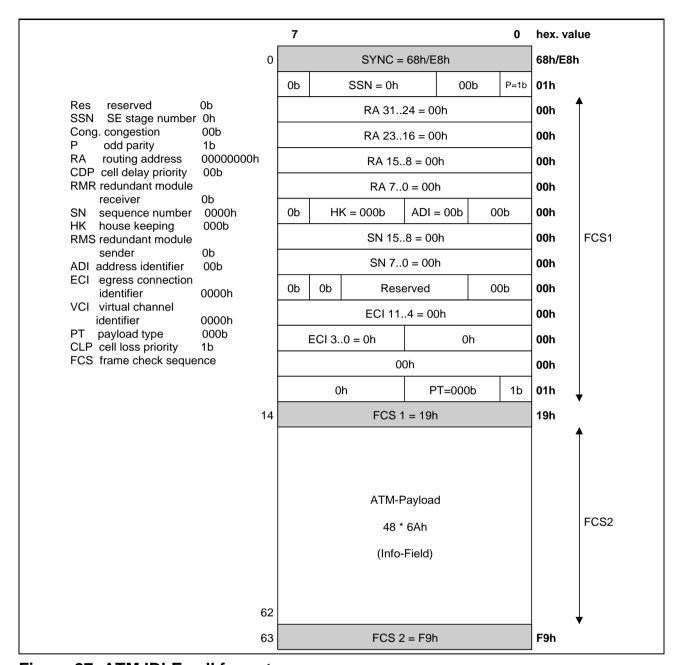

|                        | SLIF Cell Format                                                       |      |

|                        | ATM IDLE cell format                                                   |      |

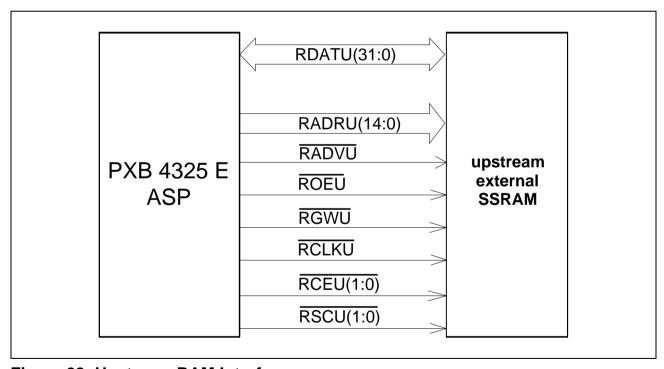

|                        | Upstream RAM Interface                                                 |      |

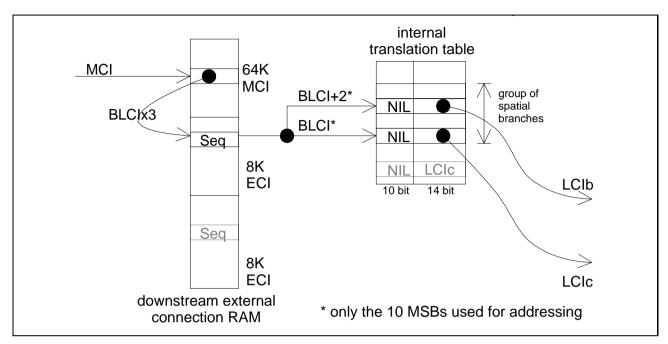

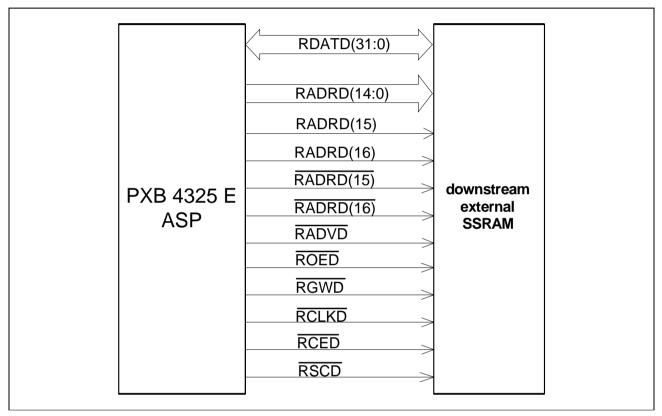

| •                      | Downstream External RAM                                                |      |

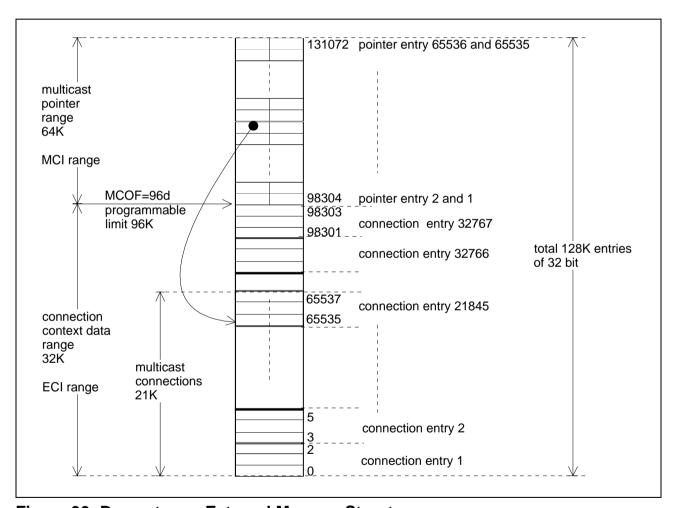

| •                      | Downstream External Memory Structure                                   |      |

|                        | RSATM Interface                                                        |      |

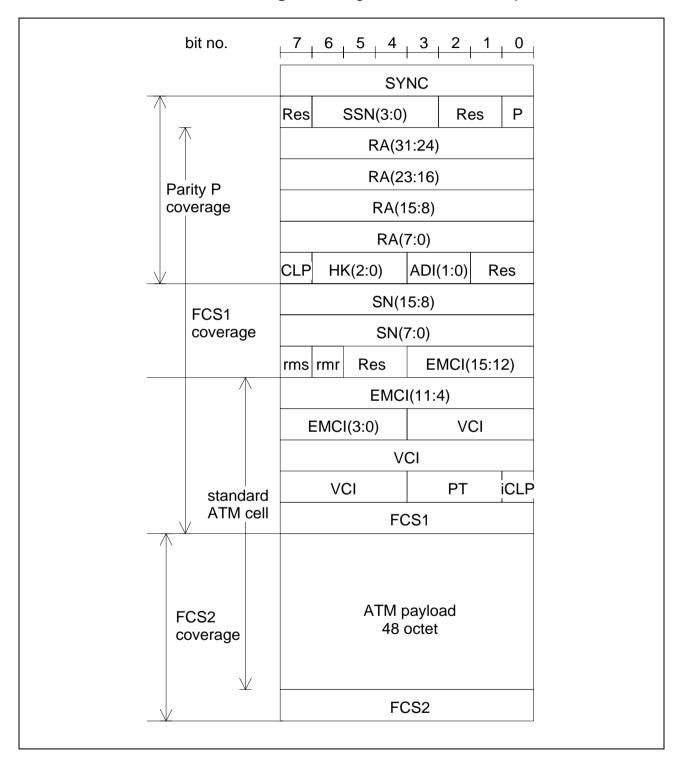

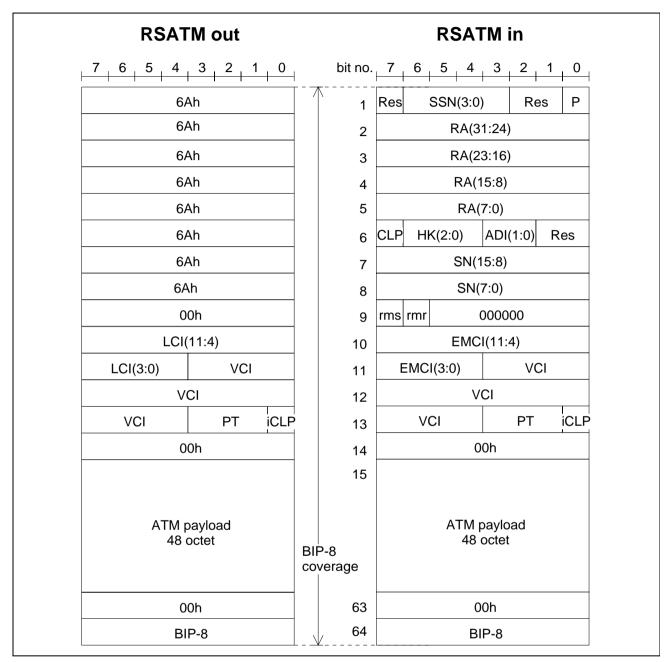

| Figure 32:             | Cell Formats at RSATM Interface                                        | .100 |

| List of Tables Pag |                                                                     | age  |

|--------------------|---------------------------------------------------------------------|------|

| Table 1:           | Queue Sizes for Cell Loss Probability 10 <sup>-11</sup>             |      |

| Table 2:           | Internal Cell Priority for Traffic Classes                          |      |

| Table 3:           | Possible Combinations of the SYLOS- and ASYN-Bit of each Input Line |      |

|                    | (SYLOS(7:0) and ASYN(7:0) of Register LINSTAT, page 58)             | 31   |

| Table 4:           | LIC Memory Overview for 3 Cases                                     | . 34 |

| Table 5:           | ASP Registers Overview                                              | 36   |

| Table 6:           | UTOPIA Polling Modes. The Numbers Indicate the Offset which is Adde | d to |

|                    | the PHY Number.                                                     | 90   |

| Table 7:           | Thermal Resistance                                                  | 111  |

7

#### 1 Overview

#### 1.1 ATM Layer Chip Set Overview

The ASP is a member of the Siemens ATM layer chip set. It consists of the six chips

- PXB 4310 E ATM Switching Matrix ASM

- PXB 4325 E ATM Switching Preprocessor ASP

- PXB 4330 E ATM Buffer Manager ABM

- PXB 4340 E ATM OAM Processor AOP

- PXB 4350 E ATM Layer Processor ALP

- PXB 4360 H ATM Content Addressable Memory Element CAME.

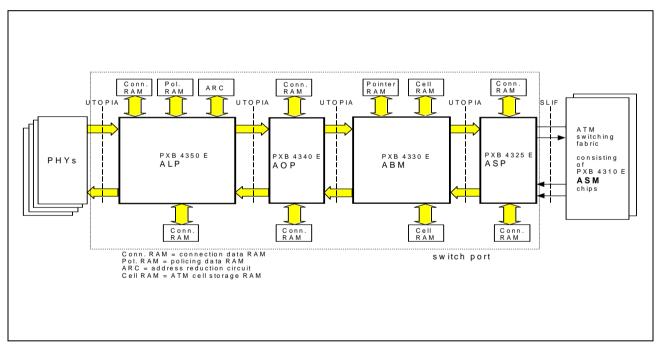

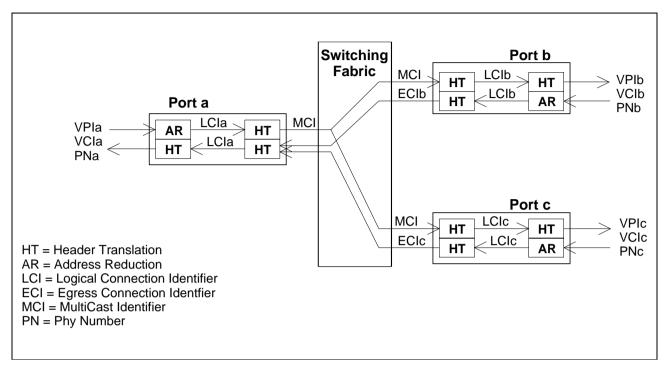

These chips form a complete chip set to build an ATM switch. A generic ATM switch consists of a switching fabric and switch ports as shown in **Figure 1**.

Figure 1 ATM Switch Basic Configuration

In the Siemens ATM layer chip set the switching fabric only does cell routing using the PXB 4310 E ASM, which can be used stand alone or in arrays to scale switching network throughput from 2.5 Gbit/s up to more than 40 Gbit/s. All other ATM layer functions are performed on the switch ports: policing, header translation and cell counting by the PXB 4350 E ALP, OAM functions by the PXB 4340 E AOP and traffic management by the PXB 4330 E ABM. The PXB 4325 E ASP is the access device to the switching fabric and adds/removes the routing header. It also supports redundant switching fabrics and does multicast.

Only two interfaces are used for data transfer: the industry standard UTOPIA [5, 6] Level 2 multi-PHY interfaces and the proprietary Switch Link InterFace SLIF. This is a serial, differential high speed link using LVDS [7, 8] levels.

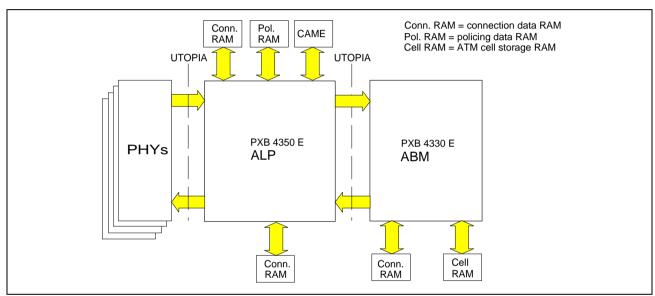

For low end applications a single board switch with 622 Mbit/s throughput can be built with only one PXB 4350 E ALP and one PXB 4330 E ABM. Such a mini-switch is basically one switch port stand alone, without switching network access via the PXB 4325 E ASP. If the full OAM functionality is not needed the PXB 4340 E AOP chip can be omitted as shown in **Figure 2**. Minimum OAM and multicast functionality is also built into the PXB 4350 E ALP. No external Address Reduction Circuit ARC is required if the built-in address reduction is used.

Figure 2 Mini Switch with 622 Mbit/s Throughput

Apart from the two applications of **Figure 1** and **2**, many other combinations of the chip set are possible in designing ATM switches. Functionality is selectable in many combinations due to the modular function split of the chip set. Address reduction, multicast, policing, redundant switching network and other functions can be implemented by appropriate chip combinations. The number of supported connections scales with the size of the external connection RAMs. The policing data RAM can be omitted if this function is not required.

Thus functionality and size of an ATM switch can be tailored exactly to what the respective application requires, without carrying the overhead of unnecessary functions.

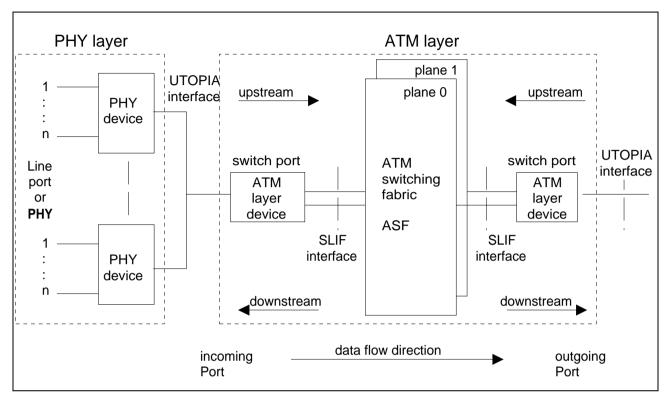

#### 1.2 Nomenclature

Figure 3 Nomenclature

- PHY = line port.

- PHY device = a component (chip) containing the PMD (physical media dependent) and TC (transmission convergence) sublayers of one or several line ports. Both PMD and TC together form the Physical or PHY layer. For the interface between PHY and ATM layer the UTOPIA interface is used.

- UTOPIA = Universal Test and OPerations Interface for ATM, defined by the ATM Forum in [5] and [6].

- Switch port = in the Siemens ATM switching strategy performs all ATM layer functions except routing.

- ATM layer device = combinations of the chips PXB 4350 E ALP, PXB 4340 E AOP, PXB 4330 E ABM and PXB 4325 E ASP as shown e.g. in Figure 1. They perform the ATM layer functions as header translation, policing, OAM, traffic management etc. and are interconnected with the UTOPIA interface.

- ATM switching fabric ASF = array of PXB 4310 E ASM chips, does space switching of ATM cells (routing); including the buffering of cells for cell level congestion.

- Planes 0 and 1 = two redundant switching fabrics, which should be identical.

- Incoming / outgoing port = refers to a connection with the data flow direction as shown in Figure 3.

- Upstream / downstream = refer to the ATM switching network; the direction towards the ASF is upstream, coming from the ASF is downstream.

# ATM Switching Preprocessor ASP

**PXB 4325 E**

Version 1.1 CMOS

#### 1.3 Features

#### **Performance**

- Performance up to STM-4/OC-12 equivalent ATM layer processing

- Throughput up to 687 Mbit/s bi-directional

- Up to 16384 connections in both directions

#### **UTOPIA** Interface

- Multiport UTOPIA Level 2 interface

- UTOPIA frequency up to 51.84 MHz

- Up to 8 PHY devices with up to 25.92 MHz clock

- Up to 4 PHY devices with up to 51.84 MHz clock

- Up to 24 PHYs addressable

- 4-fold multi-PHY UTOPIA interface with 4 CLAV/EN pairs for up to 4 PHY groups

- Up to 4 UTOPIA Level 1 PHYs

- Polling of PHYs with rotating priority in 3 modes: 4x6, 3x8 or 2x12

- Cell level handshake

- Selectable 8 or 16-bit UTOPIA data bus single- or multiport

- · Optional parity protection at UTOPIA interface

- One UTOPIA receive and transmit interface at the PHY side in master mode

#### **Cell Format at UTOPIA Interface**

- Support of standardized and proprietary UTOPIA cell format

- Proprietary cell format with 14 bit LCI in VPI and UDF1 field

- Standardized VPC only mode with 12 bit LCI in the VPI field

- Standardized VCC only mode with 14 bit LCI in the VCI field

| Туре       | Ordering Code | Package     |

|------------|---------------|-------------|

| PXB 4325 E | Q67003-H9309  | P-BGA-352-2 |

Special mode for PXB 4220 IWE8 device with E1/T1 port number transmitted in the UDF1 octet

#### **External RAM Interfaces**

- Two indepedent interfaces for upstream and downstream external RAM

- Use of standard Synchronous Static RAM devices 1 M organized 32 bit wide