### ULTRA LOW CAPACITANCE TVS ARRAY

### **APPLICATIONS**

- ✓ Low Voltage Wireless Equipment

- ✓ Sense & Control Circuits

- ✓ FireWire

- ✓ Ethernet 10/100 Base T

# SOT-23 PACKAGE

### IEC COMPATIBILITY (EN61000-4)

- ✓ 61000-4-2 (ESD): Air 15kv, Contact 8kv

- √ 61000-4-4 (EFT): 40A 5/50ns

### **FEATURES**

- ✓ Suitable for Low Capacitance High Speed V<sup>2</sup>D Protection

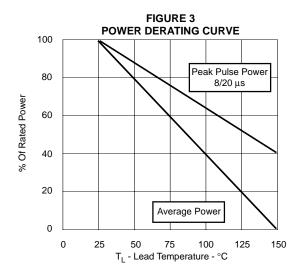

- √ 250 Watts Peak Pulse Power Dissipation per Line (8/20 µs)

- ✓ Unidirectional Configuration

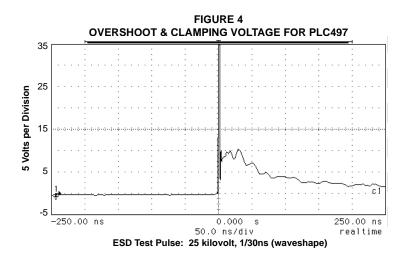

- ✓ ESD Protection > 25 kilovolts

- ✓ Ultra Low Capacitance < 2.5 pF @ 0V, 1 MHz</p>

- ✓ Standard SOT-23 Package

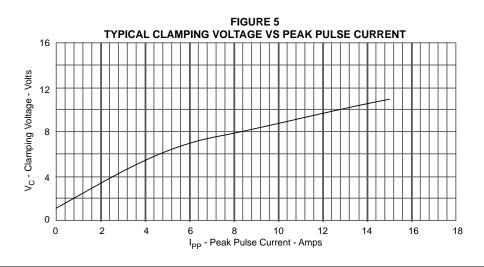

- ✓ Low Clamping Voltage < 5 Volts

</p>

- ✓ UL 94V-0 Flammability Classification

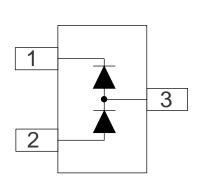

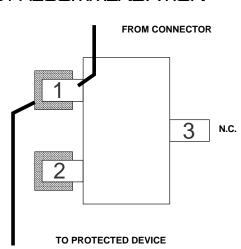

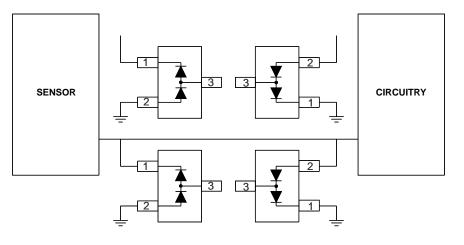

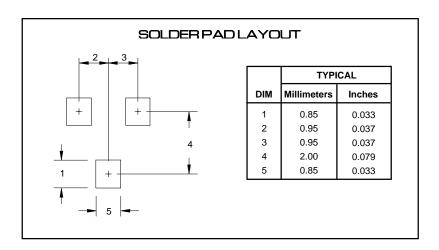

### CIRCUIT DIAGRAM & PCB LAYOUT RECOMMENDATION

# **DEVICE CHARACTERISTICS**

| MECHANICAL CHARACTERISTICS |        |                                   |                                       | MAXIMUM RATINGS               |                                               |                          |                                       |                                |

|----------------------------|--------|-----------------------------------|---------------------------------------|-------------------------------|-----------------------------------------------|--------------------------|---------------------------------------|--------------------------------|

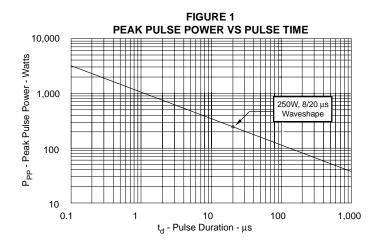

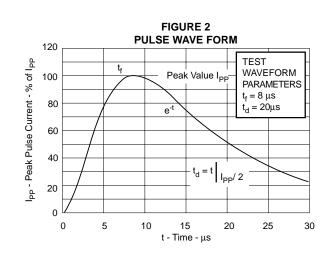

| PACKAGE<br>PACKAGING       |        | SOT-23 Surface<br>ape per EIA 481 |                                       | ''                            | (SEE FIGURE 1)                                | MPERATURE                | 250 Watts, 8/20 μs<br>-55°C to +150°C | s Waveshape                    |

|                            |        |                                   |                                       |                               |                                               |                          |                                       |                                |

| PROTEK                     | DEVICE | RATED<br>STAND-OFF<br>VOLTAGE     | CHARACT  BREAKDOWN  VOLTAGE  (NOTE 3) | MAXIMUM<br>REVERSE<br>LEAKAGE | @ 25° C Amb<br>MAXIMUM<br>CLAMPING<br>VOLTAGE | WORKING INVERSE BLOCKING | MAXIMUM CAPACITANCE (See Note 1)      | INVERSE<br>BLOCKING<br>LEAKAGE |

Note 1: Capacitance from Pin 1 to Pin 2 = 2.5 pF. Note 2: Apply positive voltage from pin 1 to pin 2 Note 3: Apply positive voltage from pin 2 to pin 1

2 5101.R2 7/01

# **DEVICE CHARACTERISTICS**

## DEVICE SPECIFIC APPLICATION NOTE

The PLC497 is an ultra low capacitance, unidirectional, TVS array designed to protect I/O or high-speed data lines from the effects of ESD or EFT. In addition, this series has a surge capability of 250 Watts  $P_{PP}$  line for an 8/20  $\mu s$  waveshape and offers ESD protection > 25kV.

The PLC497 is ideal for use in protecting and maintaining signal integrity in I/O and sensor circuit applications. When a transient occurs, the steering diodes are forward biased, conducting the transient current away from the sensitive circuitry. For most applications, ESD is considered a common mode (line-to-ground) transient event and EFT is considered a differential mode (line-to-line) transient event.

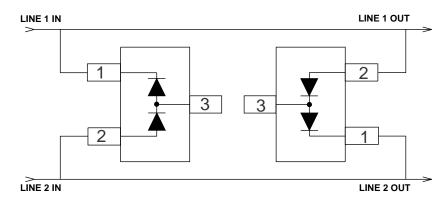

The PLC497 is designed to protect one unidirectional line. Figure 1 shows a typical differential mode (line-to-line) I/O port protection circuit application. Pins 1 and 2 are connected to the data lines. Pin 3 is not connected. To achieve bidirectional protection, two PLC497 units are placed in parallel with opposing polarities within the circuit layout.

In addition, the PLC497 can provide protection for sensor circuit applications. Figure 2, a typical common mode (line-to-ground) sensor circuit application, shows two TVS devices with pins 1 connected to the line, pins 2 connected to ground and pins three unconnected.. To acheive bidirectional protection in this application, a second pair of TVS devices is added in parallel with opposing polarities where pins 2 are connected to the line, pins 1 connected to ground and pins three unconnected.

### **Circuit Board Layout Recommendations**

Circuit board layout is critical for Electromagnetic Compatibility (EMC) protection. The following guidelines are recommended:

- ✓ The PLC497 should be placed near the input terminals or connectors. By placing the TVS close to the connectors, the device will divert the transient current immediately before it can be coupled into the nearby traces.

- ✓ The path length between the TVS device and the protected line should be minimized.

- ✓ All conductive loops including power and ground loops should be minimized.

- ✓ The transient current return path to ground should be kept as short as possible to reduce parasiticinductance.

- ✓ Ground planes should be used whenever possible. Ground vias are recommended for multilayer PCBs.

Figure 1. Typical Differential-Mode I/O Port Protection Circuit

Figure 2. Typical Common-Mode Sensor Protection Circuit

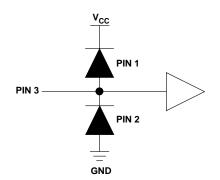

Figure 3. Steering Diode Array Circuit Schematic

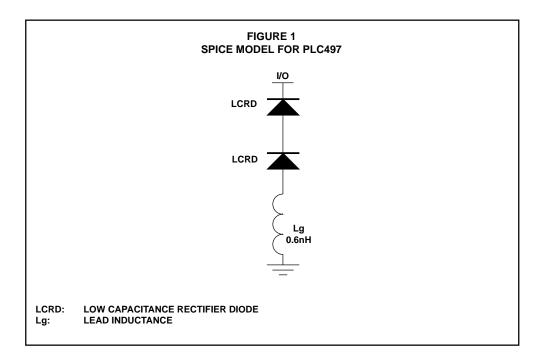

# SPICE MODEL & PARAMETERS

| TABLE 1 - SPICE PARAMETERS |          |                    |  |  |  |  |  |  |

|----------------------------|----------|--------------------|--|--|--|--|--|--|

| PARAMETER                  | UNIT     | LCRD               |  |  |  |  |  |  |

| BV                         | V        | 200                |  |  |  |  |  |  |

| IBV                        | μΑ       | 0.01               |  |  |  |  |  |  |

| Cjo                        | μA<br>pF | 5                  |  |  |  |  |  |  |

| ls                         | A        | 10E <sup>-14</sup> |  |  |  |  |  |  |

| Vj                         | V        | 0.6                |  |  |  |  |  |  |

| M                          | -        | 0.33               |  |  |  |  |  |  |

| N                          | -        | 1                  |  |  |  |  |  |  |

| Rs                         | Ohms     | 0.31               |  |  |  |  |  |  |

| TT                         | μs       | 1                  |  |  |  |  |  |  |

| EG                         | eV       | 1.11               |  |  |  |  |  |  |

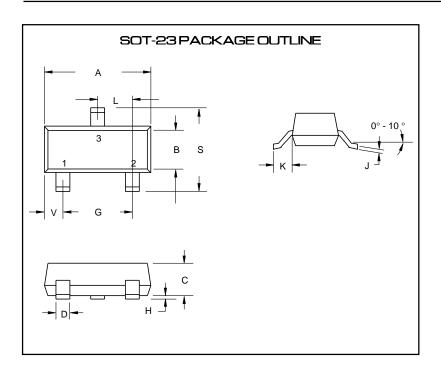

# PACKAGE OUTLINES & DIMENSIONS

### SOT-23 PACKAGE DIMENSIONS **MILLIMETERS INCHES** DIM MIN MAX MIN MAX 2.80 3.04 0.1102 0.1197 Α В 1.20 1.40 0.0472 0.0551 С 0.89 0.0350 0.0440 1.11 D 0.37 0.50 0.0150 0.0200 G 1.78 2.04 0.0701 0.0807 Н 0.013 0.100 0.0005 0.0040 J 0.085 0.177 0.0034 0.0070 Κ 0.45 0.60 0.0180 0.0236 0.89 1.02 0.0350 0.0401 S 2.10 2.50 0.0830 0.0984 0.45 0.60 0.0177 0.0236

### NOTES:

- Dimensioning and tolerance per ANSI Y 14.5M, 1985

- 2. Controlling Dimension: Inches

- 3. Maximum lead thickness includes lead finish thickness.

- 4. Minimum lead thickness is the minimum thickness of the base material.

- 4. Pin 3 is the cathode (Unidirectional only).

### COPYRIGHT © ProTek Devices 2001

SPECIFICATIONS: ProTek reserves the right to change the electrical and or mechanical characteristics described herein without notice (except JEDEC).

DESIGN CHANGES: ProTek reserves the right to discontinue product lines without notice, and that the final judgement concerning selection and specifications is the buyer's and that in furnishing engineering and technical assistance, ProTek assumes no responsibility with respect to the selection or specifications of such products.