# Features

- PC603e<sup>™</sup> Microprocessor (Embedded PowerPC<sup>™</sup> Core) at 100 200 MHz

- 140 MIPS at 100 MHz (Dhrystone 2.1)

- 280 MIPS at 200 MHz (Dhrystone 2.1)

- High-performance, Superscalar Microprocessor

- Disable CPU Mode

- Improved Low-power Core

- 16-Kbyte Data and 16-Kbyte Instruction Cache, Four-way Set Associative

- Memory Management Unit

- No Floating Point Unit

- Common On-chip Processor (COP)

- System Integration Unit (SIU)

- Memory Controller, Including Two Dedicated SDRAM Machines

- PCI up to 66 MHz (Available in Subsequent Versions)

- Hardware Bus Monitor and Software Watchdog Timer

- IEEE 1149.1 JTAG Test Access Port

• High-performance Communications Processor Module (CPM) with Operating Frequency up to 166 MHz

- PowerPC and CPM May Run at Different Frequencies

- Supports Serial Bit Rates up to 710 Mbps at 133 MHz

- Parallel I/O Registers

- On-board 24 KBytes of Dual-port RAM

- Two Multi-channel Controllers (MCCs) Each Supporting 128 Full-duplex, 64-Kbps, HDLC Lines

- Virtual DMA Functionality

- Two Bus Architectures: One 64-bit PowerPC and One 32-bit Local Bus (or PCI on PC8265)

- Two UTOPIA Level-2 Master/Slave Ports, Both with Multi-PHY Support. One Can Support 8/16 bit Data

- Three MIL Interfaces

- Eight TDM Interfaces (T1/E1), Two TDM Ports Can Be Glueless to T3/E3

- Power Consumption: 2.5W at 133 MHz

# Description

The PC8260 PowerQUICC II<sup>™</sup> is a versatile communications processor that integrates on one chip, a high-performance PowerPC (PC603e) RISC microprocessor, a highly flexible system integration unit, and many communications peripheral controllers that can be used in a variety of applications, particularly in communications and networking systems.

The core is an embedded variant of the PC603e microprocessor, specifically referred to later in this document as the EC603e, with 16 Kbytes of instruction cache and 16 Kbytes of data cache and no floating-point unit (FPU). The system interface unit (SIU) consists of a flexible memory controller that interfaces to almost any user-defined memory system, a 60x-to-PCI bus bridge (available in future revisions) and many other peripherals, making this device a complete system on a chip.

The communications processor module (CPM) includes all the peripherals found in the PC860, with the addition of three high-performance communication channels that support new emerging protocols (for example, 155-Mbps ATM and Fast Ethernet).

Equipped with dedicated hardware, the PC8260 can handle up to 256 full-duplex, time-division, multiplexed logical channels.

PowerPC-based Communications Processors

PC8260 PowerQUICC II<sup>™</sup>

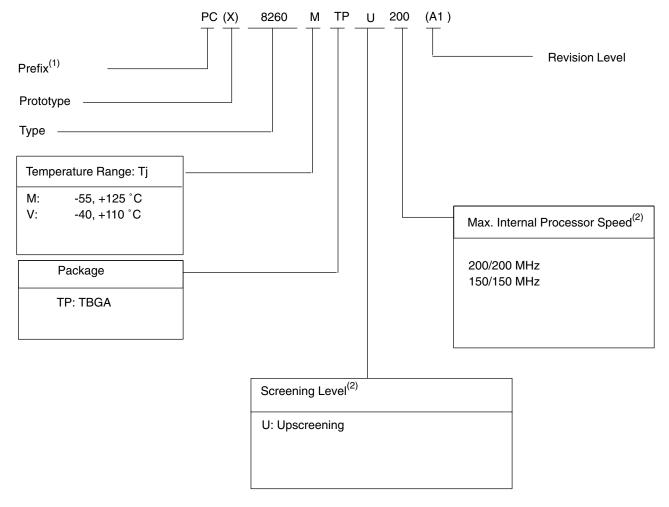

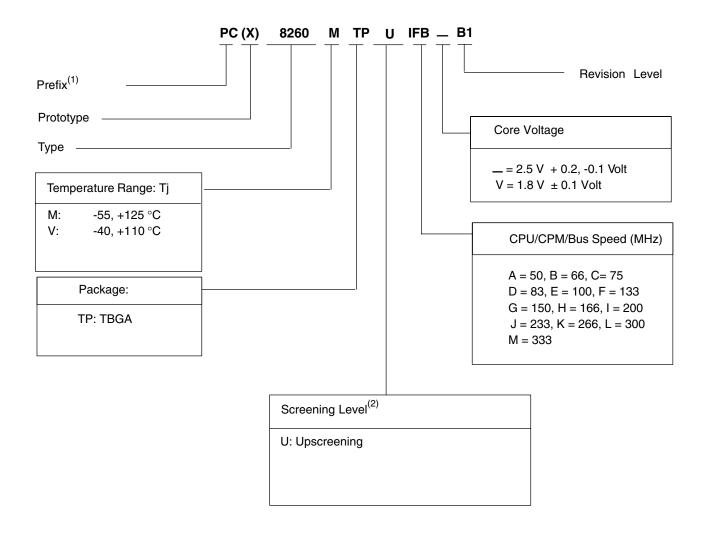

# Screening Quality Packaging

- This product is manufactured in full compliance with:

- Upscreening based upon Atmel standards.

- Full military temperature range (T<sub>J</sub> = -55°C, T<sub>J</sub> = +125°C)

- Industrial temperature range (T<sub>J</sub> = -40°C, T<sub>J</sub> = +110°C)

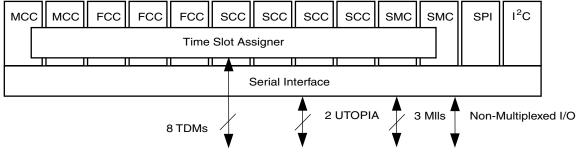

- Core power supply: 2.5V ± 5% (L-Spec for 200 MHz)

2.50V to 2.75V (R-Spec for 250 MHz) (tbc)

- I/O power supply: 3.0V to 3.6V

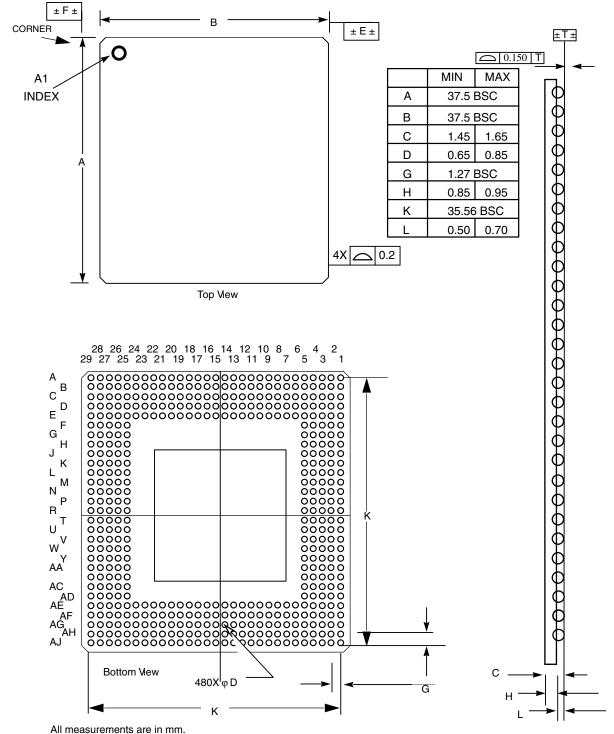

- 480-ball Tape Ball Grid Array package (TBGA 37.5 mm x 37.5 mm)

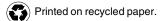

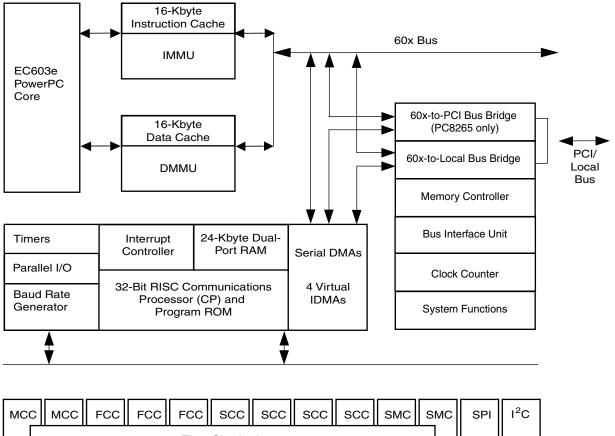

## PC8260 Architecture General Overview

The PC8260 has two external buses to accommodate bandwidth requirements from the highspeed system core and the very fast communications channels. The device is composed of the following three major functional blocks:

- A 64-bit PowerPC core derived from the EC603e with MMUs and caches.

- A system interface unit (SIU).

- A communications processor module (CPM). Both the system core and the CPM have an internal PLL, which allows independent optimization of the frequencies at which they run. The system core and CPM are both connected to the 60x bus.

## Figure 1. PC8260 Block Diagram

## EC603e Core

The EC603e core is derived from the PowerPC603e microprocessor without the floating-point unit and with power management modifications. The core is a high-performance low-power implementation of the PowerPC family of reduced instruction set computer (RISC) microprocessors. The EC603e core implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer data types of 8, 16 and 32 bits. The EC603e cache provides snooping to ensure data coherency with other masters. This helps ensure coherency between the CPM and system core.

The core includes 16 Kbytes of instruction cache and 16 Kbytes of data cache. It has a 64-bit split-transaction external data bus which is connected directly to the external PC8260 pins.

The EC603e core has an internal common on-chip (COP) debug processor. This processor allows access to internal scan chains for debugging purposes. It is also used as a serial connection to the core for emulator support.

The EC603e core performance for the SPEC 95 benchmark for integer operations ranges between 4.4 and 5.1 at 200 MHz. In Dhrystone 2.1 MIPS, the EC603e is 280 MIPS at 200 MHz (compared to 86 MIPS of the PC860 at 66 MHz).

The EC603e core can be disabled. In this mode, the PC8260 functions as a slave peripheral to an external core or to another PC8260 device with its core enabled.

## System Interface Unit (SIU)

The SIU consists of the following:

- A 60x-compatible parallel system bus configurable to 64-bit data width. The PC8260 supports 64-, 32-, 16-, and 8-bit port sizes. The PC8260 internal arbiter arbitrates between internal components that can access the bus (system core, PCI bridge, CPM, and one external master). This arbiter can be disabled, and an external arbiter can be used if necessary.

- A local (32-bit data, 32-bit internal and 18-bit external address) bus. This bus is used to enhance the operation of the very high-speed communication controllers. Without requiring extensive manipulation by the core, the bus can be used to store connection tables for ATM or buffer descriptors (BDs) for the communication channels or raw data that is transmitted between channels. The local bus is synchronous to the 60x bus and runs at the same frequency.

- The local bus can be configured as a 32-bit data and up to 66 MHz PCI (version 2.1) bus. In PCI mode the bus can be programmed as a host or as an agent. The PCI bus can be configured to run synchronously or asynchronously to the 60x bus. The PC8260 has an internal PCI bridge with an efficient 60x-to-PCI DMA for memory block transfers.

- Applications that require both the local bus and PCI bus need to connect an external PCI bridge.

- A memory controller supporting 12 memory banks that can be allocated for either the system or the local bus. The memory controller is an enhanced version of the PC8260 memory controller. It supports three user-programmable machines. Besides supporting all PC8260 features, the memory controller also supports SDRAM with page mode and address data pipeline

- Supports JTAG controller IEEE 1149.1 test access port (TAP).

- A bus monitor that prevents 60x bus lock-ups, a real-time clock, a periodic interrupt timer, and other system functions useful in embedded applications.

- Glueless interface to L2 cache and 4-/16-K-entry CAM.

## Communication Processor Module (CPM)

The CPM contains features that allow the PC8260 to excel in a variety of applications targeted mainly for networking and telecommunication markets.

The CPM is a superset of the PC8260 PowerQUICC CPM, with enhancements on the CP performance and additional hardware and microcode routines that support high bit rate protocols like ATM (up to 155 Mbps full-duplex) and Fast Ethernet (100 Mbps full-duplex).

The following list summarizes the major features of the CPM:

- The communications processor (CP) is an embedded 32-bit RISC controller residing on a separate bus (CPM local bus) from the 60x bus (used by the system core). With this separate bus, the CP does not affect the performance of the PowerPC core. The CP handles the lower layer tasks and DMA control activities, leaving the PowerPC core free to handle higher layer activities. The CP has an instruction set optimized for communications, but can also be used for general-purpose applications, relieving the system core of small often repeated tasks.

- Two serial DMAs (SDMAs) that can do simultaneous transfers, optimized for burst transfers to the 60x bus and to the local bus.

- Three full-duplex, serial fast communications controllers (FCCs) supporting ATM (155 Mbps) protocol through UTOPIA2 interface (there are two UTOPIA interfaces on the PC8260), IEEE 802.3 and Fast Ethernet protocols, HDLC up to E3 rates (45 Mbps) and totally transparent operation. Each FCC can be configured to transmit fully transparent and receive HDLC, or vice-versa.

- Two multichannel controllers (MCCs) that can handle an aggregate of 256 x 64 Kbps HDLC or transparent channels, multiplexed on up to eight TDM interfaces. The MCC also supports super-channels of rates higher than 64 Kbps and subchanneling of the 64-Kbps channels.

- Four full-duplex serial communications controllers (SCCs) supporting IEEE802.3/Ethernet, high-level synchronous data link control, HDLC, local talk, UART, synchronous UART, BISYNC and transparent.

- Two full-duplex serial management controllers (SMC) supporting GCI, UART, and transparent operations.

- Serial peripheral interface (SPI) and I<sup>2</sup>C bus controllers.

- Time-slot assigner (TSA) that supports multiplexing of data from any of the four SCCs, three FCCs, and two SMCs.

Software Compatibility Issues As much as possible, the PC8260 CPM features were made similar to those of the previous devices (PC860). The code ports easily from previous devices to the PC8260, except for new protocols supported by the PC8260.

Although many registers are new, most registers retain the old status and event bits, so an understanding of the programming models of the 68360, PC860, or PC850 is helpful. Note that the PC8260 initialization code requires changes from the PC8260 initialization code.

# PC8260 PowerQUICC II

## Differences Between PC860 and PC8260

The following PC860 features are not included in the PC8260:

- On-chip crystal oscillators (must use external oscillator)

- 4 MHz oscillator (input clock must be at the bus speed)

- Low power (standby) modes

- Battery-backup real-time clock (must use external battery-backup clock)

- BDM (COP offers most of the same functionality)

- True little endian mode (except the PCI bus)

- PCMCIA interface

- Infrared (IR) port

- QMC protocol in SCC (256 HDLC channels are supported by the MCCs)

- Multiply and accumulate (MAC) block in the CPM

- Centronics port (PIP)

- Asynchronous HDLC protocol (optional RAM microcode)

- Pulse-width modulated outputs

- SCC Ethernet controller option to sample 1 byte from the parallel port when a receive frame is complete.

- Parallel CAM interface for SCC (Ethernet)

Serial Protocol Table

Table 1 summarizes available protocols for each serial port.

#### Table 1. PC8260 Serial Protocols

|              | Port |     |     |     |

|--------------|------|-----|-----|-----|

| Protocol     | FCC  | SCC | MCC | SMC |

| ATM (Utopia) | x    |     |     |     |

| 100BaseT     | x    |     |     |     |

| 10BaseT      | x    | x   |     |     |

| HDLC         | x    | x   | x   |     |

| HDLC_BUS     |      | x   |     |     |

| Transparent  | x    | x   | x   | x   |

| UART         |      | x   |     | x   |

| DPLL         |      | x   |     |     |

| Multichannel |      |     | x   |     |

# PC8260 PowerQUICC II

| Pin Name | Ball |

|----------|------|

| BR       | W5   |

| BG       | F4   |

| ABB/IRQ2 | E2   |

| TS       | E3   |

| A0       | G1   |

| A1       | H5   |

| A2       | H2   |

| A3       | H1   |

| A4       | J5   |

| A5       | J4   |

| A6       | J3   |

| A7       | J2   |

| A8       | J1   |

| A9       | K4   |

| A10      | КЗ   |

| A11      | K2   |

| A12      | K1   |

| A13      | L5   |

| A14      | L4   |

| A15      | L3   |

| A16      | L2   |

| A17      | L1   |

| A18      | M5   |

| A19      | N5   |

| A20      | N4   |

| A21      | N3   |

| A22      | N2   |

| A23      | N1   |

| A24      | P4   |

| A25      | P3   |

| A26      | P2   |

| A27      | P1   |

| A28      | R1   |

| A29      | R3   |

| A30      | R5   |

## Pin Assignment

Table 2 shows the pinout of the PC8260.

#### Table 2. Pinout

| Pin Name | Ball |

|----------|------|

| A31      | R4   |

| ТТО      | F1   |

| TT1      | G4   |

| TT2      | G3   |

| ТТЗ      | G2   |

| TT4      | F2   |

| TBST     | D3   |

| TSIZ0    | C1   |

| TSIZ1    | E4   |

| TSIZ2    | D2   |

| TSIZ3    | F5   |

| AACK     | F3   |

| ARTRY    | E1   |

| DBG      | V1   |

| DBB/IRQ3 | V2   |

| D0       | B20  |

| D1       | A18  |

| D2       | A16  |

| D3       | A13  |

| D4       | E12  |

| D5       | D9   |

| D6       | A6   |

| D7       | B5   |

| D8       | A20  |

| D9       | E17  |

| D10      | B15  |

| D11      | B13  |

| D12      | A11  |

| D13      | E9   |

| D14      | B7   |

| D15      | B4   |

| D16      | D19  |

| D17      | D17  |

| D18      | D15  |

| D19      | C13  |

| D20      | B11  |

Table 2. Pinout (Continued)

| A | MEL |

|---|-----|

|   |     |

## Table 2. Pinout (Continued)

| Pin Name | Ball |

|----------|------|

| D21      | A8   |

| D22      | A5   |

| D23      | C5   |

| D24      | C19  |

| D25      | C17  |

| D26      | C15  |

| D27      | D13  |

| D28      | C11  |

| D29      | B8   |

| D30      | A4   |

| D31      | E6   |

| D32      | E18  |

| D33      | B17  |

| D34      | A15  |

| D35      | A12  |

| D36      | D11  |

| D37      | C8   |

| D38      | E7   |

| D39      | A3   |

| D40      | D18  |

| D41      | A187 |

| D42      | A14  |

| D43      | B12  |

| D44      | A10  |

| D45      | D8   |

| D46      | B6   |

| D47      | C4   |

| D48      | C18  |

| D49      | E16  |

| D50      | B14  |

| D51      | C12  |

| D52      | B10  |

| D53      | A7   |

| D54      | C6   |

| D55      | D5   |

| D56      | B18  |

| Pin Name                     | Ball |

|------------------------------|------|

| D57                          | B16  |

| D58                          | E14  |

| D59                          | D12  |

| D60                          | C10  |

| D61                          | E8   |

| D62                          | D6   |

| D63                          | C2   |

| DPO/RSRV/EXT_BR2             | B22  |

| IRQ1/DP1/EXT_BG2             | A22  |

| IRQ2/DP2/TLBISYNC/EXT_DBG2   | E21  |

| IRQ3/DP3/CKSTP_OUT/EXT_BR3   | D21  |

| IRQ4/DP4/CORE_SRESET/EXT_BG3 | C21  |

| IRQ5/DP5/TBEN/EXT_DBG3       | B21  |

| IRQ6/DP6/CSEO                | A21  |

| IRQ7/DP7/CSE1                | E20  |

| PSDVAL                       | V3   |

| TA                           | C22  |

| TEA                          | V5   |

| GBL/IRQ1                     | W1   |

| CI/BADDR29/IRQ2              | U2   |

| WT/BADDR30/IRQ3              | U3   |

| T2_HIT/IRQ4                  | Y4   |

| CPU_BG/BADDR31/IRQ5          | U4   |

| CPU_DBG                      | R2   |

| CPU_BR                       | Y3   |

| <u>CS0</u>                   | F25  |

| CS1                          | C29  |

| CS2                          | E27  |

| CS3                          | E28  |

| CS4                          | F26  |

| CS5                          | F27  |

| CS6                          | F28  |

| CS7                          | G25  |

| CS8                          | D29  |

| CS9                          | E29  |

| CS10/BCTL1                   | F29  |

# 12 PC8260 PowerQUICC II

| Pin Name                 | Ball |

|--------------------------|------|

| CS11/APO                 | G28  |

| BADDR27                  | T5   |

| BADDR28                  | U1   |

| ALE                      | T2   |

| BCTLO                    | A27  |

| PWE0/PSDQM0/PBS0         | C25  |

| PWE1/PSDDQM1/PBS1        | E24  |

| PWE2/PSDDQM2/PBS2        | D24  |

| PWE3/PSDDQM3/PBS3        | C24  |

| PWE4/PSDDQM4/PBS4        | B26  |

| PWE5PSDDQM5/PBS5         | A26  |

| PWE6/PSDDQM6/PBS6        | B25  |

| PWE7/PSDDQM7/PBS7        | A25  |

| PSDA10/PGL0              | E23  |

| PSDWE/PGPL1              | B24  |

| POE/OSDRAS/PGPL2         | A24  |

| PSDCAS/PGPL3             | B23  |

| PGTA/PUPMWAIT/PGPL4/PPBS | A23  |

| PSDAMUX/PGPL5            | D22  |

| LWE0/LSDDQM0/LBS0        | H28  |

| LWE1/LSDDQM1/LBS1        | H27  |

| LWE2/LSDDQM2/LBS2        | H26  |

| LWE3/LSDDQM3/LBS3        | G29  |

| LSDA10/LGPL0             | D27  |

| LSDWE/LGPL1              | C28  |

| LOE/LSDRAS/LGPL2         | E26  |

| LSDCAS/LGPL3             | D25  |

| LGTA/LUPMWAIT/LGPL4/LPBS | C26  |

| LGPL5                    | B27  |

| IWR                      | D28  |

| L_A14                    | N27  |

| L_A15/SMI                | T29  |

| L_A16                    | R27  |

| L_A17/CKSTP_OUT          | R26  |

| L_A18                    | R29  |

| L_A19                    | R28  |

**NEL**

## Table 2. Pinout (Continued)

| Pin Name          | Ball |

|-------------------|------|

| L_A20             | W20  |

| L_A21             | P28  |

| L_A22             | N26  |

| L_A23             | AA27 |

| L_A24             | P29  |

| L_A25             | AA26 |

| L_A26             | N25  |

| L_A27             | AA25 |

| L_A28/CORE_SRESET | AB29 |

| L_A29             | AB28 |

| L_A30             | P25  |

| L_A31             | AB27 |

| LCL_D0            | H29  |

| LCL_D1            | J29  |

| LCL_D2            | J28  |

| LCL_D3            | J27  |

| LCL_D4            | J26  |

| LCL_D5            | J25  |

| LCL_D6            | K25  |

| LCL_D7            | L29  |

| LCL_D8            | L27  |

| LCL_D9            | L26  |

| LCL_D10           | L25  |

| LCL_D11           | M29  |

| LCL_D12           | M28  |

| LCL_D13           | M27  |

| LCL_D14           | M26  |

| LCL_D15           | N29  |

| LCL_D16           | T25  |

| LCL_D17           | U27  |

| LCL_D18           | U26  |

| LCL_D19           | U25  |

| LCL_D20           | V29  |

| LCL_D21           | V28  |

| LCL_D22           | V27  |

| LCL_D23           | V26  |

Table 2. Pinout (Continued)

## Table 2. Pinout (Continued)

| Pin Name                                  | Ball |

|-------------------------------------------|------|

| LCL_D24                                   | W27  |

| LCL_D25                                   | W26  |

| LCL_D26                                   | W25  |

| LCL_D27                                   | Y29  |

| LCL_D28                                   | Y28  |

| LCL_D29                                   | Y25  |

| LCL_D30                                   | AA29 |

| LCL_D31                                   | AA28 |

| LCL_DP0                                   | L28  |

| LCL_DP1                                   | N28  |

| LCL_DP2                                   | T28  |

| LCL_DP3                                   | W28  |

| IRQ0/NMI_OUT                              | W28  |

| IRQ7INT_OUT/APE                           | D1   |

| TRST                                      | AH3  |

| тск                                       | AG5  |

| TMS                                       | AJ3  |

| TDI                                       | AE6  |

| TDO                                       | AF5  |

| TRIS                                      | AB4  |

| PORESET                                   | AG6  |

| HRESET                                    | AH5  |

| SRESET                                    | AF6  |

| QREQ                                      | AA3  |

| RSTCONF                                   | AJ4  |

| MODCK1/AP1/TC0/BNKSEL0                    | W2   |

| MODCK2/AP2/TC1/BNKSEL1                    | W3   |

| MODCK3/AP3/TC2/BNKSEL2                    | W4   |

| XFC                                       | AB2  |

| CLKIN                                     | AH4  |

| PA0/RESTART1/DREQ/FCC2_UTM_TXADDRS        | AC29 |

| PA1/REJECT1/FCC2_UTM_TXADDR1/DONE3        | AC25 |

| PA2/CLK20/FCC2_UTM_TXADDR0/DACK3          | AE28 |

| PA3/CLK19/FCC2_UTM_RXADDR0/DACK4/L1RXD1A2 | AG29 |

| PA4/REJECT2/FCC2/RXADDR1/DONE4            | AG28 |

| PA5/RESTART2/DREQ4/FCC2_UTM_RXADDR2       | AG26 |

# 14 PC8260 PowerQUICC II

| Pin Name                                                   | Ball |

|------------------------------------------------------------|------|

| PA6/L1RSYNCA1                                              | AE24 |

| PA7/SMSYN2/L1TSYNCA1/L1GNTA1                               | AH25 |

| PA8/SMRSXD2/L1RXD0A1/L1RXDA1                               | AF23 |

| PA6/L1RSYNCA1                                              | AE24 |

| PA7/SMSYN2/L1TSYNCA1/L1GNTA1                               | AH25 |

| PA8/SMRXD2/L1RXD0A1/L1RXDA1                                | AF23 |

| PA9/SMTXD2/L1TXD0A1                                        | AH23 |

| PA10/FCC1_UT8_RXD0/FCC1_UT16_RXD8/MSNUM5                   | AE22 |

| PA11/FCC1_UT8_RXD1/FCC1_UT16_RXD9/MSNUM4                   | AH22 |

| PA12/FCC1_UT8_RXD2/FCC1_UT16_RXD10/MSNUM3                  | AJ21 |

| PA13/FCC1_UT8_RXD3/FCC1_UT16_RXD11/MSNUM2                  | AH20 |

| PA14/FCC1_UT8_RXD4/FCC1_UT16_RXD12/FCC1_RXD3               | AG19 |

| PA15/FCC1_UT8_RXD5/FCC1_UT16_RXD13/FCC1_RXD2               | AF18 |

| PA16/FCC1_UT8_RXD6/FCC1_UT16_RXD14/FCC1_RXD1               | AF17 |

| PA17/FCC1_UT8_RXD7/FCC1_UT16_RXD15/FCC1_RXD0/FCC1_RXD      | AE16 |

| PA18/FCC1_UT8_TXD7/FCC1_UT16_TXD15/FCC1_TXD0/FCC1_TXD      | AJ16 |

| PA19/FCC1_UT8_TXD6/FCC1_UT16_TXD14/FCC1_TXD1               | AG15 |

| PA20/FCC1_UT8_TXD5/FCC1_UT16_TXD13/FCC1_TXD2               | AJ13 |

| PA21/FCC1_UT8_TXD4/FCC1_UT16_TXD12/FCC1_TXD3               | AE13 |

| PA22/FCC1_UT8_TXD3/FCC1_UT16_TXD11                         | AF12 |

| PA23/FCC1_UT8_TXD2/FCC1_UT16_TXD10                         | AG11 |

| PA24/FCC1_UT8_TXD1/FCC1_UT16_TXD9/MSNUM1                   | AH9  |

| PA25/FCC1_UT8_TXD0/FCC1_UT16_TXD8/MSNUM0                   | AJ8  |

| PA26/FCC1_UTM_RXCLAV/FCC1_UTS_RXCLAV/FCC1_MII_RX_ER        | AH7  |

| PA27/FCC1_UT_RXSOC/FCC1_MII_RX_DV                          | AF7  |

| PA28/FCC1_UTM_RXENB/FCC1_UTS_RXENB/FCC1_MII_TX_EN          | AD5  |

| PA29/FCC1_UT_TXSOC/FCC1_MII_TX_ER                          | AF1  |

| PA30/FCC1_UTM_TXCLAV/FCC1_UTS_TXCLAV/FCC1_MII_CRS/FCC1_RTS | AD3  |

| PA31/FCC1_UTM_TXENB/FCC1_UTS_TXENB/FCC1_MII_COL            | AB5  |

| PB4/FCC3_TXD3/FCC2_UT8_RXD0/L1RSYNCA2/FCC3_RTS             | AD28 |

| PB5/FCC3_TXD2/FCC2_UT8_RXD1/L1TSYNCA2/L1GNTA2              | AD26 |

| PB6/FCC3_TXD1/FCC2_UT8_RXD2/L1RXDA2/L1RXD0A2               | AD25 |

| PB7/FCC3_TXD0/FCC3_TXD/FCC2_UT8_RXD3/L1TXDA2/L1TXD0A2      | AE26 |

| PB8/FCC2_UT8_TXD3/FCC3_RXD0/FCC3_RXD/TXD3/L1RSYNCD1        | AH27 |

| PB9/FCC2_UT8_TXD2/FCC3_RXD1/L1TXD2A2/L1TSYNCD1/L1GNTD1     | AG24 |

| PB10/FCC2_UT8_TXD1/FCC3_RXD2/L1RXDD1                       | AH24 |

#### Table 2. Pinout (Continued)

## Table 2. Pinout (Continued)

| Pin Name                                                                    | Ball |

|-----------------------------------------------------------------------------|------|

| PB11/FCC3_RXD3/FCC2_UT8_TXD0/L1TXDD1                                        | AJ24 |

| PB12/FCC3_MII_CRS/L1CLKOB1/L1RSYNCC1/TXD2                                   | AG22 |

| PB13/FCC3_MII_COL/L1RQB1/L1TSYNCC1/L1GNTC1/L1TXD1A2                         | AH21 |

| PB14/FCC3_MIL_TX_EN/RXD3/L1RXDC1                                            | AG20 |

| PB15/FCC3_MIL_TX_ER/RXD2/L1TXDC1                                            | AF19 |

| PB14/FCC3_MIL_RX_ER/L1CLKOA1/CLK18                                          | AJ18 |

| PB17FCC3_MIL_RX_DV/L1RQA1/CLK17                                             | AJ17 |

| PB18/FCC2_UT8_RXD4/FCC2_RXD3/L1CLKOD2/L1RXD2A2                              | AE14 |

| PB19/FCC2_UT8_RXD5/FCC2_RXD2/L1RQD2/L1RXD3A2                                | AF13 |

| PB20/FCC2_UT8_RXD6/FCC2_RXD1/L1RSYNCD2/L1TXD1A1                             | AG12 |

| PB21/FCC2_UT8_RXD7/FCC2_RXD0/FCC2_RXD/<br>L1TSYNCD2/L1GNTD2/L1TXD2A1        | AH11 |

| PB22/FCC2_UT8_TXD7/FCC2_TXD0/FCC2_L1RXD1A1/L1RXDD2                          | AH16 |

| PB23/FCC2_UT8_TXD6/FCC2_TXD1/L1RXD2A1/L1RXDD2                               | AE15 |

| PB24/FCC2_UT8_TXD5/FCC2_TXD2/L1RXD3A1/L1RSYNCC2                             | AJ9  |

| PB25/FCC2_UT8_TXD4/FCC2_TXD3/L1TSYNCC2/L1GNTC2/L1TXD3A1                     | AE9  |

| PB26/FCC2_MII_CRS/FCC2_UT8_TXD1/L1RXDC2                                     | AJ7  |

| PB27/FCC2_MII_COL/FCC2_UT8_TXD0/L1TXDC2                                     | AH6  |

| PB28/FCC2_MII_RX_ER/FCC2_RTS/L1TSYNCB2/L1GNTB2/TXD1                         | AE3  |

| PB29/FCC2_UTM_RXCLAV/FCC2_UTS_RXCLAV/<br>L1RSYNCB2/FCC2_MII_TX_EN           | AE2  |

| PB30/FCC2_MII_RX_DV/FCC2_UT_TXSOC/1RXDB2                                    | AC5  |

| PB31/FCC2_MII_TX_ER/FCC2_UT_RXSOC/L1TXDB2                                   | AC4  |

| PC0/DREQ1/BRG07/SMSYN2/L1CLKOA2                                             | AB26 |

| PC1/DREQ2/BRGO6/L1RQA2                                                      | AD29 |

| PC2/FCC3_CD/FCC2_UT8_TXD3/DONE2                                             | AE29 |

| PC3/FCC3_CTS/FCC2_UT8_TXD2/DACk2/CTS4                                       | AE27 |

| PC4/FCC2_UTM_RXENB/FCC2_UTS_RXENB/SI2_L1ST4/FCC2_CD                         | AF27 |

| PC5/FCC2_UTM_TXCLAV/FCC2_UTS_TXCLAV/SI2_L1ST3/FCC2_CTS                      | AF24 |

| PC6/FCC1_CD/L1CLKOC1/FCC1_UTM_RXADDR2/FCC1_UTS_RXADDR2/<br>FCC1_UTM_RXCLAV1 | AJ26 |

| PC7/FCC1_CTS/L1RQC1/<br>FCC1_UTM_TXADDR2/FCC1_UTS_TXADDR2/FCC1_UTM_TSCLAV1  | AJ25 |

| PC8/CD4/RENA4/FCC1_UT16_TXD0/SI2_L1ST2/CTS3                                 | AF22 |

| PC9/CTS4/CLSN4/FCC1_UT16_TXD1/SI2_L1ST1/L1TSYNCA2/L1GNTA2                   | AE21 |

| PC10/CD3/RENA3/FCC1_UT16_TXD2/SI1_L1ST4/FCC2_UT8_RXD3                       | AE20 |

| PC11/CTS3/CLSN3/L1CLKOD1/L1TXD3A2/FCC2_UT8_RXD2                             | AE19 |

| Pin Name                                                           | Ball |

|--------------------------------------------------------------------|------|

| PC12/CD2/RENA2/SI1_L1ST3/FCC1_UTM_RXADDR1/FCC1_UTS_RXADDR1         | AE18 |

| PC13/CTS2/SLSN2/L1RQD1/FCC1_UTM_TXADDR1/FCC1_UTS_TXADDR1           | AH18 |

| PC14/CD1/RENA1/FCC1_UTM_RXADDR0/FCC1_UTS_RXADDR0                   | AH17 |

| PC15/CTS1/CLSN1/SMTXD2/FCC1_UTM_TXADDR0/FCC1_UTS_TXADDR0           | AG16 |

| PC16/CLK16/TIN3                                                    | AF15 |

| PC17/CLK15/TIN4/BRGO8                                              | AJ15 |

| PC18/CLK14/TGATE2                                                  | AH14 |

| PC19/CLK13/BRGO7                                                   | AG13 |

| PC20/CLK12/TGATE1                                                  | AH12 |

| PC21/CLK11/BTGO6                                                   | AJ11 |

| PC22/CLK10/DONE1                                                   | AG10 |

| PC23/CLK9/BRGO5/DACK1                                              | AE10 |

| PC24/FCC2_UT8_TXD3/CLK8/TOUT4                                      | AF9  |

| PC25/FCC2_UT8_TXD2/CLK7/BRGO4                                      | AE8  |

| PC26/CLK6/TOUT3/TMCLK                                              | AJ6  |

| PC27/FCC3_TXD/FCC3_TXD0/CLK5/BRGO3                                 | AG2  |

| PC28/CLK4/TIN1/TOUT2/CTS2/CLSN2                                    | AF3  |

| PC29/CLK3/TIN2/BRGO2/CTS1/CLSN1                                    | AF2  |

| PC30/FCC2_UT8_TXD3/CLK2/TOUT1                                      | AE1  |

| PC31/CLK1/BRGO1                                                    | AD1  |

| PD4/BRGO8/L1TSYNCD1/L1GNTD1/FCC3_RTS/SMRXD2                        | AC28 |

| PD5/FCC1_UT16_TXD3/DONE1                                           | AD27 |

| PD6/FCC1_UT16_TXD4/DACK1                                           | AF29 |

| PD7/SMSYN1/FCC1_UTM_TXADDR3/FCC1_UTS_TXADDR3/FCC1_TXCLAV2          | AF28 |

| PD8/SMRXD1/FCC2_UT_TXPRTY/BRGO5                                    | AG25 |

| PD9/SMTXD1/FCC2_UT_RXPRTY/BRGO3                                    | AH26 |

| PD10/L1CLKOB2/FCC2_UT8_RXD1/L1RSYNCB1/BRGO4                        | AJ27 |

| PD11/L1RQB2/FCC2_UT8_RXD0/L1TSYNCB1/L1GNTB1                        | AJ23 |

| PD12/SI1_L1ST2/L1RXDB1                                             | AG23 |

| PD13/SI1_L1ST1/L1RTDB1                                             | AJ22 |

| PD14/FCC1_UT16_RXD0/L1CLKOC2/L2CSCL                                | AE20 |

| PD15/FCC1_UT16_RXD1/L1RQC2/I2CSDA                                  | AJ20 |

| PD16/FCC1_UT_TXPRTY/L1TSYNCC1/L1GNTC1/SPIMISO                      | AG18 |

| PD17/FCC1_UT_RXPRTY/BRGO2/SPIMOSI                                  | AG17 |

| PD18/FCC1_UTM_RXADDR4/FCC1_UTS_RXADDR4/FCC1_UTM_RXCLAV3/<br>SPICLK | AF16 |

| Table 2. | Pinout | (Continued) |

|----------|--------|-------------|

|----------|--------|-------------|

## Table 2. Pinout (Continued)

| Pin Name                                                                 | Ball |

|--------------------------------------------------------------------------|------|

| PD19/FCC1_UTM_RXADDR4/FCC1_UTS_RXADDR4/FCC1_UTM_<br>TXCLAV3/SPISEL/BRGO1 | AH15 |

| PD20/RTS4/TENA4/FCC1_UT16_RXD2/L1RSYNCA2                                 | AJ14 |

| PD21/TXD4/FCC1_UT16_RXD3/L1RXD0A2/L1RXDA2                                | AH13 |

| PD22/RXD4/FCC1_UT16_TXD5/L1TXD0A2/L1TXDA2                                | AJ12 |

| PD23/RTS3/TENA3/FCC1_UT16_RXD4/L1RSYNCD1                                 | AE12 |

| PD24/TXD3/FCC1_UT16_RXD5/L1RXDD1                                         | AF10 |

| PD25/RXD3/FCC1_UT16_TXD6/L1TXDD1                                         | AG9  |

| PD26/RTS2/TENA2/FCC1_UT16_RXD6/L1RSYNCC1                                 | AH8  |

| PD27/TXD2/FCC1_UT16_RXD7/L1RXDC1                                         | AG7  |

| PD28/RXD2/FCC1_UT16_TXD7/L1TXDC1                                         | AE4  |

| PD29/RTS1/TENA1/FCC1_UTM_RXADDR3/FCC1_UTS_RXADDR3/<br>FCC1_UTM_RXCLAV2   | AG1  |

| PD30/FCC2_UTM_TXENB/FCC2_UTS_TXENB/TXD1                                  | AD4  |

| PD31/RXD1                                                                | AD2  |

| VCCSYN                                                                   | AB3  |

| VCCSYN1                                                                  | B9   |

| GNDSYN                                                                   | AB1  |

| THERMAL0 (thermal ball)                                                  | AA1  |

| THERMAL1 (thermal ball)                                                  | AG4  |

| SPARE1                                                                   | AE11 |

| SPARE4                                                                   | UF   |

| SPARE5                                                                   | AF25 |

| SPARE6                                                                   | V4   |

# PC8260 PowerQUICC II

| Pin Name   | Ball                                                                                                                                                                                                                                                                                   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Power  | AG21,AG14,<br>AG8, AJ1, AJ2,<br>AH1, AH2,AG3,<br>AF4, AE5,<br>AC27, Y27,<br>T27, P27, K26,<br>G27, AE25,<br>AF26, AG27,<br>AH28, AH29,<br>AJ28, AJ29,<br>C7,C14,C16,C2<br>0,C23, E10,<br>A28, A29, B28,<br>B29, C27, D26,<br>E25, H3, M4,<br>T3, AA4, A1,<br>A2, B1, B2, C3,<br>D4, E5 |

| Core Power | U28, U29, K28,<br>K29, A9, A19,<br>B19, M1, M2,<br>Y1, Y2, AC1,<br>AC2, AH19,<br>AJ19, AH10,<br>AJ10, AJ5                                                                                                                                                                              |

| Ground     | U28, U29, K28,<br>K29, A9, A19,<br>B19, M1, M2,<br>Y1, Y2, AC1,<br>AC2, AH19,<br>AJ19, AH10,<br>AJ10, AJ5                                                                                                                                                                              |

### Table 2. Pinout (Continued)

Note: Symbol Legend:

Overline:Signals with overlines, such as TA, are active lowUTM:Indicates that a signal is part of the UTOPIA master interfaceUTS:Indicates that a signal is part of the UTOPIA slave interface2UT8:Indicates that a signal is part of the 8-bit UTOPIA interfaceUT16:Indicates that a signal is part of the 16-bit UTOPIA interfaceMII:Indicates that a signal is part of the media independent interface

## Figure 2. PowerQUICC II External Signals

| Figure 2. FowerQUICC II External Signals         |                 |                |                                                                             |

|--------------------------------------------------|-----------------|----------------|-----------------------------------------------------------------------------|

| VCCSYN/GNDSYN/VCCSYN1/VDDH/VDD/VSS               | 100             | 32             | ← → A[0:31]                                                                 |

| P AR / L_A14 ← →                                 |                 | 5              | $ \longrightarrow TT[0:4] $                                                 |

| SMI/FRAME / L_A15 ↔                              | 1               | 4              |                                                                             |

|                                                  |                 |                | $\leftarrow \rightarrow TSIZ[0:3]$                                          |

| $\frac{TRDY}{L} A16 \longleftrightarrow$         | 1               | 1              | ←→ TBST                                                                     |

| CKSTOP_OUT/IRDY/ L_A17 ←→                        | 1               | 1              | ←→ <u>GBL/IRQ1</u>                                                          |

| STOP/ L_A18 ←→                                   | 1               | 1              | ←→ CI/BADDR29/IRQ2                                                          |

| DEVSEL/L_A19 ↔                                   | 1 L             | 1              | ←→ WT/BADDR30/IRQ3                                                          |

| ĪDSEL / L_A20 ↔                                  | 1               | 1              | < <u>L2_HIT</u> /IRQ4                                                       |

| PERR/L_A21                                       | 10              | 1              | $\longleftrightarrow CPU_BG/BADDR31/IRQ5$                                   |

|                                                  | C               | 1              | $\rightarrow \overline{CPU_DBG}$                                            |

|                                                  |                 | 1              |                                                                             |

|                                                  | A               |                |                                                                             |

| SERR/L_A22 ↔                                     | 1 L             | 6 1            | $\longleftrightarrow \overline{BR}$                                         |

| REQ0/L_A23 ↔                                     | 1               | 0 1            | $\longleftrightarrow \overline{BG}$                                         |

| REQ1 / L_A24 ↔                                   | 1               | 1              | ←→ ABB/IRQ2                                                                 |

| GNT0 / L_A25 ↔                                   | 1 B             | <b>X</b> 1     | $\leftrightarrow$ TS                                                        |

| GNT1 / L_A26 <                                   | <sup>1</sup> U  | 1              |                                                                             |

| $\overline{\text{CLK}}$ / L_A27 $\longleftarrow$ | 1               | в <sup>1</sup> | ←→ ARTRY                                                                    |

| CORE_SRESET/RST / L_A28 ↔                        | 1 S             | 1              | $\longleftrightarrow$ DBG                                                   |

| <br>INTA/ L_A29 ↔                                | 1               | U              | $  \overrightarrow{DBB}/\overline{IRQ3} $                                   |

| LOCK/ L_A30 ~~>                                  | 1               | S 64           |                                                                             |

| —                                                |                 |                | 5[0:00]                                                                     |

|                                                  | 1               | 1              | ← NC/DP0/RSRV/EXT_BR2                                                       |

| $AD[0:31]/LCL_D[0:31] \longleftrightarrow$       | 32              | 1              | ←→ IRQ1/DP1/EXT_BG2                                                         |

| C/BE[0:3] /LCL_DP[0:3] ←→                        | 4               | 1              | ← TRQ2/DP2/TLBISYNC/EXT_DBG2                                                |

| LBS[0:3]/LSDDQM [0:3]/LWE [0:3] <                | 4               | 1              | ← TRQ3/DP3/CKSTP_OUT/EXT_BR3                                                |

|                                                  |                 | 1              | ←→ IRQ4/DP4/CORE_SRESET/EXT_BG                                              |

| LGPL0/LSDA10 -                                   | 1               | 1              | ←→ IRQ5/DP5/TBEN/EXT_DBG3                                                   |

| LGPL1/LSDWE ←                                    | 1               | 1              | $\longleftrightarrow \overline{IRQ6/DP6/CSE0}$                              |

| LGPL2/LSDRASLOE                                  | M               | 1              | $\leftrightarrow$ IRQ7/DP7/CSE1                                             |

| LGPL3/LSDCAS                                     | E               | 1              |                                                                             |

|                                                  | M               | '<br>-         | $\longleftrightarrow \frac{PS_DVAL}{\overset{-}{\overset{-}{\overset{-}}}}$ |

| LPBS/LGPL4/LUPWAIT/LGTA ←→                       |                 | 1              | $\longleftrightarrow \overline{TA}$                                         |

| LGPL5 +                                          | '               | 1              |                                                                             |

| LWR ←→                                           | 1               | 1              | ← IRQ0/NMI_OUT                                                              |

| PA[0:31]                                         | <sup>32</sup> P | 1              | ← TRQ7/INT_OUT/APE                                                          |

| PB[4:31] ← →                                     | 28              | 10             | $\longrightarrow \overline{CS}[0:9]$                                        |

| PC[0:31] ← →                                     | 32              | 1              | $\longleftrightarrow$ $\overline{CS[10]/BCTL1/DBG_DIS}$                     |

| PD[4:31] ← →                                     | 28 <b>O</b>     | 1              | $\leftarrow \rightarrow \overline{CS[11]}/AP[0]$                            |

| PORESET                                          | 1               | 2              | $\longrightarrow$ BADDR[27:28]                                              |

| RSTCONF →                                        | 1               | 1              | → ALE                                                                       |

| HRESET +                                         | 1               | Mi             | $\rightarrow \frac{\Delta LL}{BCTL0}$                                       |

| SRESET                                           |                 | E 8            |                                                                             |

|                                                  | 1 R             | ∟ o<br>M 1     | → PWE[0:7]/PSDDQM[0:7]/PBS[0:7]                                             |

|                                                  | <sup>1</sup> S  |                | PSDA10/PGPL0                                                                |

|                                                  |                 | C 1            | → PSDWE/PGPL1                                                               |

| XFC →                                            | 1 T             | 1              | POE/PSDRAS/PGPL2                                                            |

|                                                  |                 | 1              | → PSDCAS/PGPL3                                                              |

| CLKIN →                                          | 1               | 1              | ←→ PGTA/PUPMWAIT/PGPL4/PPBS                                                 |

| $\overline{\text{TRIS}} \longrightarrow$         | C               | 1              | → PSDAMUX/PGPL5                                                             |

| BNKSEL[0]/TC[0]/AP[1]/MODCK1 ↔                   |                 | — 1            | TMS                                                                         |

| BNKSEL[1]/TC[1]/AP[2]/MODCK2                     | 1 K             | Ji             | ← TDI                                                                       |

| BNKSEL[2]/TC[2]/AP[3]/MODCK3 <                   | 1               | Τi             |                                                                             |

|                                                  |                 |                |                                                                             |

| $TERM[0:1] \longrightarrow$                      | 2               | A 1            |                                                                             |

| NC                                               | 4               | G 1            | → TDO                                                                       |

|                                                  |                 | _              | l                                                                           |

20 PC8260 PowerQUICC II

## **Signal Descriptions**

The PowerQUICC II system bus signals consist of all the lines that interface with the external bus. Many of these lines perform different functions, depending on how the user assigns them. Each signal's pin number can be found in Table 3.

| Table 3. | External Signals |

|----------|------------------|

|----------|------------------|

| Pin         | Signal Name                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR          | 60x Bus Request            | I/O  | This is an output when an external arbiter is used and an input when an internal arbiter is used. As an output, the PowerQUICC II asserts this pin to request ownership of the 60x bus. As an input, an external master should assert this pin to request 60x bus ownership from the internal arbiter.                                                                                                                                                            |

| BG          | 60x BusGrant               | I/O  | This is an output when an internal arbiter is used and an input when an internal arbiter is used. As an output, the PowerQUICC II asserts this pin to grant 60x bus ownership to an external bus master. As an input, an external arbiter should assert this pin to grant 60x bus ownership to the PowerQUICC II.                                                                                                                                                 |

| ABB<br>IRQ2 | 60x Address Bus Busy       | I/O  | As an output the PowerQUICC II asserts this pin for the duration of the address bus tenure. Following an AACK, which terminates the address bus tenure, the PowerQUICC II negates ABB for a fraction of a bus cycle and than stops driving this pin. As an input, the PowerQUICC II will not assume 60x bus ownership, as long as it senses this pin is asserted by an external 60x bus master.                                                                   |

|             | Interrupt Request 2        | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                   |

| TS          | T-S 60x Bus Transfer Start | I/O  | Assertion of this pin signals the beginning of a new address bus tenure.<br>The PowerQUICC II asserts this signal when one of its internal 60x bus<br>masters (core, dma, PCI bridge) begins an address tenure. When the<br>PowerQUICC II senses this pin being asserted by an external 60x bus<br>master, it will respond to the address bus tenure as required (snoop if<br>enabled, access internal PowerQUICC II resources and memory<br>controller support). |

| A[0:31]     | 60x Address Bus            | I/O  | When the PowerQUICC II is in the external master bus mode, these pins function as the 60x address bus. The PowerQUICC II drives the address of its internal 60x bus masters and will respond to addresses generated by external 60x bus masters. When the PowerQUICC II is in the internal master bus mode, these pins are used as address lines connected to memory devices and controlled by the PowerQUICC II's memory controller.                             |

| TT[0:4]     | 60x Bus Transfer Type      | I/O  | The 60x bus master drives these pins during the address tenure to specify the type of the transaction.                                                                                                                                                                                                                                                                                                                                                            |

| TBST        | 60x Bus Transfer Burst     | I/O  | The 60x bus master asserts this pin to indicate that the current transaction is a burst transaction (transfers 4 double words).                                                                                                                                                                                                                                                                                                                                   |

| TSIZ[0:3]   | 60x Transfer Size          | I/O  | The 60x bus master drives these pins with a value indicating the amount of bytes transferred in the current transaction.                                                                                                                                                                                                                                                                                                                                          |

| AACK        | 60x Address Acknowledge    | I/O  | A 60x bus slave asserts this signal to indicate that it has identified the address tenure. Assertion of this signal terminates the address tenure.                                                                                                                                                                                                                                                                                                                |

| ARTRY       | 60x Address Retry          | I/O  | Assertion of this signal indicates that the bus transaction should be<br>retried by the 60x bus master. The PowerQUICC II asserts this signal to<br>enforce data coherency with its internal cache and to prevent deadlock<br>situations.                                                                                                                                                                                                                         |

| Pin                      | Signal Name               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBG                      | 60x Data Bus Grant        | I/O  | This is an output when an internal arbiter is used and an input when an external arbiter is used. As an output, the PowerQUICC II asserts this pin to grant 60x data bus ownership to an external bus master. As an input, the external arbiter should assert this pin to grant 60x data bus ownership to the PowerQUICC II.                                                                              |

| DBB<br>IRQ3              | 60x Data Bus Busy         | I/O  | As an output the PowerQUICC II asserts this pin for the duration of the data bus tenure. Following a $\overline{TA}$ , which terminates the data bus tenure, the PowerQUICC II negates DBB for a fraction of a bus cycle and then stops driving this pin. As an input, the PowerQUICC II will not assume 60x data bus ownership, as long as it senses this pin is asserted by an external 60x bus master. |

|                          | Interrupt Request 3       | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                           |

| D[0:63]                  | 60x Data Bus              | I/O  | In write transactions, the 60x bus master drives the valid data on this bus. In read transactions, the 60x slave drives the valid data on this bus.                                                                                                                                                                                                                                                       |

| DP[0]<br>RSRV<br>EXT_BR2 | 60x Data Parity 0         | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 0 pin should provide odd parity (odd number of 1's) on the group of signals that include data parity 0 and D[0:7].                                                                                                                                                                       |

|                          | Reservation               | 0    | The value driven on this output pin represents the state of the coherency bit in the reservation address register that is used by the Iwarx and stwcx. instructions.                                                                                                                                                                                                                                      |

|                          | External Bus Request 2    | Ι    | An external master should assert this pin to request 60xbus ownership from the internal arbiter.                                                                                                                                                                                                                                                                                                          |

| IRQ1<br>DP[1]            | Interrupt Request 1       | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                           |

| EXT_BG2                  | 60x Data Parity 1         | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 1 pin should provide odd parity (odd number of 1's) on the group of signals that includes data parity 1 and D[8:15].                                                                                                                                                                     |

|                          | External Bus Grant 2      | 0    | The PowerQUICC II asserts this pin to grant 60x bus ownership to an external bus master.                                                                                                                                                                                                                                                                                                                  |

| IRQ2<br>DP[2]            | Interrupt Request 2       | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                           |

| TLBISYNC<br>EXT_DBG2     | 60x Data Parity 2         | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 2 pin should provide odd parity (odd number of 1's) on the group of signals that includes data parity 2 and S[16:23].                                                                                                                                                                    |

|                          | TLB Sync:                 | I    | This input pin can be used to synchronize 60x core instruction execution to hardware indications. Asserting this pin will force the core to stop instruction execution following a tlbsinc instruction execution. The core resumes instruction execution once this pin is negated.                                                                                                                        |

|                          | External Data Bus Grant 2 | 0    | The PowerQUICC II asserts this pin to grant 60x data bus ownership to an external bus master.                                                                                                                                                                                                                                                                                                             |

| d) |

|----|

| ł  |

| Pin                    | Signal Name            | Туре | Description                                                                                                                                                                                                                                    |

|------------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ3<br>DP[3]          | Interrupt Request 3    | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                |

| CKSTP_OUT<br>EXT_BR3   | 60x Data Parity 3      | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 3 pin should provide odd parity (odd number of 1's) on the group of signals that includes data parity 3 and D[24:31].         |

|                        | Checkstop Output       | 0    | Assertion of this pin indicates that the core is in its checkstop mode.                                                                                                                                                                        |

|                        | External Bus Request 3 | I    | An external master should assert this pin to request 60x bus ownership from the internal arbiter.                                                                                                                                              |

| IRQ4<br>DP[4]          | Interrupt Request 4    | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                |

| CORE_SRESET<br>EXT_BG3 | 60x Data Parity 4      | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 4 pin should provide odd parity (odd number of 1's) on the group of signals that includes data parity 4 and D[32:39].         |

|                        | Core system reset      | I    | Asserting this pin will force the core to branch to its reset vector.                                                                                                                                                                          |

|                        | External Bus Grant 3   | 0    | The PowerQUICC II asserts this pin to grant 60x data bus ownership to an external bus master.                                                                                                                                                  |

| IRQ5<br>DP[5]          | Interrupt Request 5    | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                |

| TBEN<br>EXT_DBG3       | 60x Data Parity 5      | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 5 pin should provide odd parity (odd number of 1's) on the group of signals that includes data parity 5 and D[40:47].         |

|                        | Time Base Enable       | I    | This is a count enable input to the Time Base counter in the core.                                                                                                                                                                             |

|                        | External Bus Grant3    | 0    | The PowerQUICC II asserts this pin to grant 60x data bus ownership to an external bus master.                                                                                                                                                  |

| IRQ6<br>DP[6]          | Interrupt Request 6    | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                |

| CSE[0]                 | 60x Data Parity 6      | I/O  | The 60x agent that drives the data bus, also drives the data parity signals. The value driven on the data parity 6 pin should provide odd parity (odd number of 1's) on the group of signals that include data parity 6 and D[48:55].          |

|                        | Cache Set Entry 0      | 0    | The cache set entry outputs from the core, represent the cache replacement set element for the current core transaction reloading into, or writing out of, the cache.                                                                          |

| IRQ7<br>DP[7]          | Interrupt Request 7    | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                |

| CSE[1]                 | 60x Data Parity 7      | I/O  | The 60x master or slave that drives the data bus, also drives the data parity signals. The value driven on the data parity 7pin should provide odd parity (odd number of 1's) on the group of signals that include data parity 7 and D[56:63]. |

|                        | Cache Set Entry 1      | 0    | The cache set entry outputs from the core, represent the cache replacement set element for the current core transaction reloading into, or writing out of, the cache.                                                                          |

| Pin                   | Signal Name                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSDVAL                | 60x Data Valid             | I/O  | Assertion of the PSDVAL pin indicates that a data beat is valid on the data bus. The difference between the TA pin and the PSDVAL pin is that the TA pin is asserted to indicate 60x data transfer terminations, while the PSDVAL signal is asserted with each data beat movement. Thus, always when TA is asserted, PSDVAL will be asserted, but, when PSDVAL is asserted, TA is not necessarily asserted. For example, when a double-double word (2x64 bits) transfer is initiated by the SDMA to a memory device that has 32 bits port size, PSDVAL will be asserted 3 times without TA and, finally, both pins will be asserted to terminate the transfer. |

| TA                    | Transfer Acknowledge       | I/O  | Assertion of the $\overline{TA}$ pin indicates that a 60x data beat is valid on the data bus. For 60x single beat transfers, assertion of this pin indicates the termination of the transfer. For 60x burst transfers, this pin will be asserted four times to indicate the transfer of four data beats, with the last assertion indicating the termination of the burst transfer.                                                                                                                                                                                                                                                                             |

| TEA                   | Transfer Error Acknowledge | I/O  | Assertion of this pin indicates a bus error. 60x masters within the<br>PowerQUICC II monitor the state of this pin. PowerQUICC II's internal<br>bus monitor may assert this pin if it has identified a 60x transfer that is<br>hung.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GBL<br>IRQ1           | Global                     | I/O  | When a 60x master within the chip initiates a bus transaction it drives<br>this pin. When an external 60x master initiates a bus transaction, it<br>should drive this pin. Assertion of this pin indicates that the transfer is<br>global and it should be snooped by caches in the system. The<br>PowerQUICC II data cache monitors the state of this pin.                                                                                                                                                                                                                                                                                                    |

|                       | Interrupt Request 1        | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CI<br>BADDR29<br>IRQ2 | Cache Inhibit              | 0    | This pin is an output pin. It is used for L2 cache control. For each BADDR29 PowerQUICC II 60x transaction initiated in the core, the state of this pin indicates if this transaction should be cached or not. Assertion of the CI pin indicates that the transaction should not be cached.                                                                                                                                                                                                                                                                                                                                                                    |

|                       | Burst Address 29           | 0    | There are five burst address output pins. These pins are outputs of the 60x memory controller. These pins are used in external master configuration and are connected directly to memory devices controlled by PowerQUICC II memory controller.                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | Interrupt Request 2        | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WT<br>BADDR30<br>IRQ3 | Write Through              | 0    | Output used for L2 cache control. For each core initiated PowerQUICC II 60x transaction, the state of this pin indicates if the transaction should be cached using write-through or copy-back mode. Assertion of $\overline{\text{WT}}$ indicates that the transaction should be cached using the write-through mode.                                                                                                                                                                                                                                                                                                                                          |

|                       | Burst Address 30           | 0    | There are five burst address output pins. These pins are outputs of the 60x memory controller. These pins are used in external master configuration and are connected directly to memory devices controlled by PowerQUICC II's memory controller.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | Interrupt Request 3        | Ι    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Table 3. | External Signals | (Continued) |

|----------|------------------|-------------|

|----------|------------------|-------------|

| Pin                       | Signal Name            | Туре | Description                                                                                                                                                                                                                                                                                                         |  |

|---------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L2_HIT<br>IRQ4            | L2 Cache Hit           | Ι    | This pin is used for L2 cache control. Assertion of this pin indicates that the 60x transaction will be handled by the L2 cache. In this case, the memory controller will not start an access to the memory it controls.                                                                                            |  |

|                           | Interrupt Request 4    | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                     |  |

| CPU_BG<br>BADDR31<br>IRQ5 | CPU BusGrant           | 0    | The value of the60x core bus grant is driven on this pin for the BADDR31 use of an external L2 cache. The driven bus grant is non qualified. that is, in the IRQ5 case of external arbiter, the user should qualify this signal with the bus grant input to the PowerQUICC II before connecting it to the L2 Cache. |  |

|                           | Burst address 31       | 0    | There are five burst address outputs of the 60x memory controller used<br>in the external master configuration and are connected directly to the<br>memory devices controlled by PowerQUICC II's memory controller.                                                                                                 |  |

|                           | Interrupt Request 5    | I    | This input is one of the eight external lines that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                     |  |

| CPU_DBG                   | CPU Bus Data Bus Grant | 0    | The value of the 60x core data bus grant is driven on this pin for the use of an external L2 cache.                                                                                                                                                                                                                 |  |

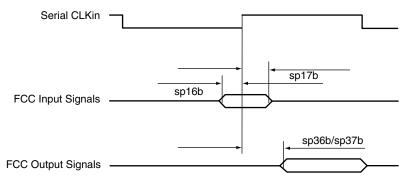

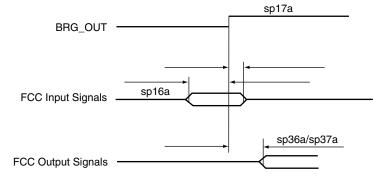

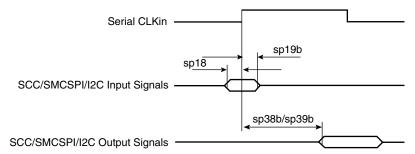

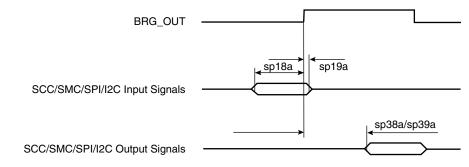

| CPU_BR                    | CPU Bus Request        | 0    | The value of the 60x core bus request is driven on this pin for the use of an external L2 cache.                                                                                                                                                                                                                    |  |