**ISSUE 6**

SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

## PM5362

## **TUPP-PLUS**

# SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

## **DATA SHEET**

**ISSUE 6: MARCH 1998**

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

### **CONTENTS**

| 1 | FEAT  | URES                               | 1  |

|---|-------|------------------------------------|----|

| 2 | APP   | ICATIONS                           | 5  |

| 3 | REF   | ERENCES                            | 6  |

| 4 | DES   | CRIPTION                           | 8  |

| 5 | PIN I | DIAGRAM                            | 10 |

| 6 | BLO   | CK DIAGRAM                         | 11 |

| 7 | PIN I | DESCRIPTION                        | 12 |

| 8 | FUN   | CTIONAL DESCRIPTION                | 41 |

|   | 8.1   | INPUT BUS DEMULTIPLEXER            | 41 |

|   | 8.2   | OUTPUT BUS MULTIPLEXER             | 41 |

|   | 8.3   | TRIBUTARY PAYLOAD PROCESSOR        | 42 |

|   |       | 8.3.1 CLOCK GENERATOR              | 42 |

|   |       | 8.3.2 INCOMING TIMING GENERATOR    | 42 |

|   |       | 8.3.3 INCOMING MULTIFRAME DETECTOR | 43 |

|   |       | 8.3.4 POINTER INTERPRETER          | 43 |

|   |       | 8.3.5 PAYLOAD BUFFER               | 47 |

|   |       | 8.3.6 OUTGOING TIMING GENERATOR    | 47 |

|   |       | 8.3.7 POINTER GENERATOR            | 48 |

|   | 8.4   | TRIBUTARY PATH OVERHEAD PROCESSOR  | 51 |

|   |       | 8.4.1 CLOCK GENERATOR              | 52 |

|   |       | 8.4.2 TIMING GENERATOR             | 52 |

|    |      | 8.4.3 ERROR MONITOR52                     |

|----|------|-------------------------------------------|

|    |      | 8.4.4 IN-BAND ERROR REPORT54              |

|    |      | 8.4.5 EXTRACT55                           |

|    | 8.5  | TRIBUTARY TRACE BUFFER55                  |

|    |      | 8.5.1 CLOCK GENERATOR55                   |

|    |      | 8.5.2 TIMING GENERATOR56                  |

|    |      | 8.5.3 EXTRACT                             |

|    |      | 8.5.4 ALARM MONITOR                       |

|    |      | 8.5.5 BUFFER                              |

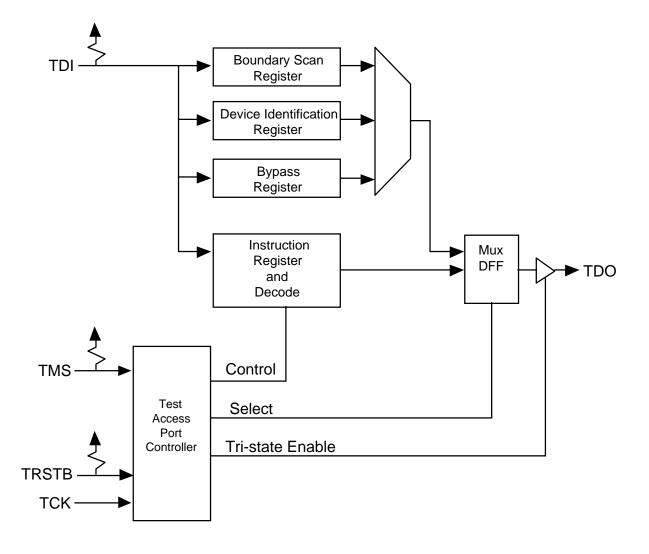

|    | 8.6  | JTAG TEST ACCESS PORT57                   |

|    | 8.7  | MICROPROCESSOR INTERFACE57                |

|    | 8.8  | REGISTER MEMORY MAP58                     |

| 9  | NORI | MAL MODE REGISTER DESCRIPTION66           |

|    | 9.1  | MASTER REGISTERS67                        |

|    | 9.2  | VTPP #1, VTPP #2 AND VTPP #3 REGISTERS109 |

|    | 9.3  | RTOP #1, RTOP #2 AND RTOP #3 REGISTERS143 |

|    | 9.4  | RTTB #1, RTTB #2 AND RTTB #3 REGISTERS236 |

| 10 | TEST | FEATURES DESCRIPTION261                   |

|    | 10.1 | I/O TEST MODE266                          |

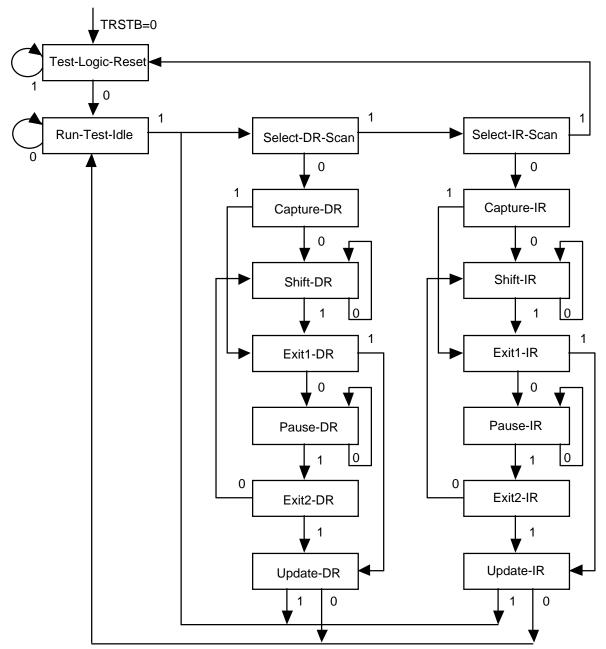

|    | 10.2 | JTAG TEST PORT274                         |

| 11 | OPE  | RATION276                                 |

|    | 11.1 | CONFIGURATION OPTIONS276                  |

|    | 11.2 | STS-1 MODE277                             |

|    | 11.3 AU3 MODE278                                |

|----|-------------------------------------------------|

|    | 11.4 AU4 MODE                                   |

|    | 11.5 JTAG SUPPORT281                            |

|    | 11.5.1 TAP CONTROLLER282                        |

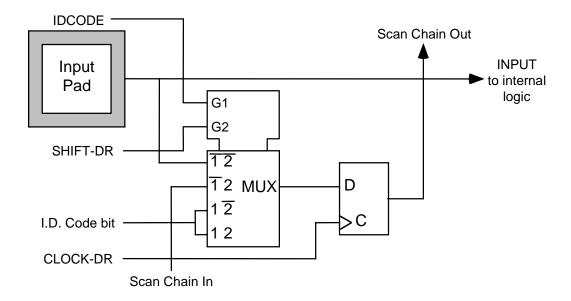

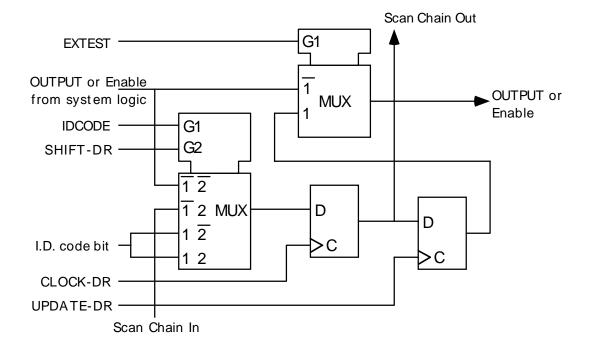

|    | 11.5.2 BOUNDARY SCAN INSTRUCTIONS285            |

| 12 | FUNCTIONAL TIMING                               |

| 13 | APPLICATION EXAMPLES                            |

| 14 | ABSOLUTE MAXIMUM RATINGS                        |

| 15 | D.C. CHARACTERISTICS311                         |

| 16 | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS |

| 17 | TUPP-PLUS TIMING CHARACTERISTICS322             |

| 18 | ORDERING AND THERMAL INFORMATION330             |

| 19 | MECHANICAL INFORMATION                          |

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

### **LIST OF REGISTERS**

| REGISTER 00H: MASTER INCOMING CONFIGURATION                                                 | 67  |

|---------------------------------------------------------------------------------------------|-----|

| REGISTER 01H: MASTER OUTGOING CONFIGURATION                                                 | 69  |

| REGISTER 02H: INPUT SIGNAL ACTIVITY MONITOR, ACCUMULATION TRIGGER                           | 72  |

| REGISTER 03H: MASTER RESET AND IDENTITY                                                     | 74  |

| REGISTER 04H: VTPP #1 CONFIGURATION                                                         | 75  |

| REGISTER 05H: VTPP #2 CONFIGURATION                                                         | 78  |

| REGISTER 06H: VTPP #3 CONFIGURATION                                                         | 81  |

| REGISTER 07H: TRIBUTARY PAYLOAD PROCESSOR AND LOM INTERRUPT ENABLE                          | 84  |

| REGISTER 08H: TRIBUTARY PAYLOAD PROCESSOR INTERRUPT AND LOM STATUS                          | 86  |

| REGISTER 09H: PARITY ERROR AND LOM INTERRUPT                                                | 88  |

| REGISTER 0AH: TRIBUTARY PATH OVERHEAD PROCESSOR AND TRIBUTARY TRACE BUFFER INTERRUPT ENABLE | 90  |

| REGISTER 0BH: TRIBUTARY PATH OVERHEAD PROCESSOR AND TRIBUTARY TRACE BUFFER INTERRUPT STATUS | 92  |

| REGISTER 0CH: RTOP #1 AND RTTB #1 CONFIGURATION                                             | 94  |

| REGISTER 0DH: RTOP #2 AND RTTB #2 CONFIGURATION                                             | 96  |

| REGISTER 0EH: RTOP #3 AND RTTB #3 CONFIGURATION                                             | 98  |

| REGISTER 10H: TRIBUTARY ALARM AIS CONTROL                                                   | 100 |

| REGISTER 11H: TRIBUTARY REMOTE DEFECT INDICATION  CONTROL                                   | 102 |

| REGISTER 12H: TRIBUTARY AUXILIARY REMOTE DEFECT INDICATION CONTROL                                 | 104 |

|----------------------------------------------------------------------------------------------------|-----|

| REGISTER 13H: TRIBUTARY PDI CONTROL                                                                | 107 |

| REGISTER 20H, 40H, 60H: VTPP, TU3 OR TU #1 IN TUG2 #1, CONFIGURATION AND STATUS                    | 109 |

| REGISTER 21H-26H, 41H-46H, 61H-66H: VTPP, TU #1 IN TUG2<br>#2 TO TUG2 #7, CONFIGURATION AND STATUS | 112 |

| REGISTER 27H, 47H, 67H: VTPP, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                    | 114 |

| REGISTER 28H-2EH, 48H-4EH, 68H-6EH: VTPP, TU #2 IN TUG2<br>#1 TO TUG2 #7, CONFIGURATION AND STATUS | 116 |

| REGISTER 2FH, 4FH, 6FH: VTPP, TU #2 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                           | 119 |

| REGISTER 30H-36H, 50H-56H, 70H-76H: VTPP, TU #3 IN TUG2<br>#1 TO TUG2 #7, CONFIGURATION AND STATUS | 120 |

| REGISTER 37H, 57H, 77H: VTPP, TU #3 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                           | 123 |

| REGISTER 38H-3EH, 58H-5EH, 78H-7EH: VTPP, TU #4 IN TUG2<br>#1 TO TUG2 #7, CONFIGURATION AND STATUS | 124 |

| REGISTER 3FH, 5FH, 7FH: VTPP, TU #4 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT                           | 127 |

| REGISTER A0H, C0H, E0H: VTPP, TU3 OR TU #1 IN TUG2 #1, ALARM STATUS                                | 128 |

| REGISTER A1H-A6H, C1H-C6H, E1H-E6H: VTPP, TU #1 IN TUG2 #2 TO TUG2 #7, ALARM STATUS                | 130 |

| REGISTER A7H, C7H, E7H: VTPP, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, AIS INTERRUPT                    | 132 |

| REGISTER A8H-AEH, C8H-CEH, E8H-EEH: VTPP, TU #2 IN TUG2<br>#1 TO TUG2 #7, ALARM STATUS             | 134 |

| REGISTER AFH, CFH, EFH: VTPP, TU #2 IN TUG2 #1 TO TUG2 #7 AIS INTERRUPT1                                                                                                                         | 36  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGISTER B0H-B6H, D0H-D6H, F0H-F6H: VTPP, TU #3 IN TUG2<br>#1 TO TUG2 #7, ALARM STATUS1                                                                                                          | 37  |

| REGISTER B7H, D7H, F7H: VTPP, TU #3 IN TUG2 #1 TO TUG2 #7, AIS INTERRUPT1                                                                                                                        | ∣39 |

| REGISTER B8H-BEH, D8H-DEH, F8H-FEH: VTPP, TU #4 IN TUG2<br>#1 TO TUG2 #7, ALARM STATUS1                                                                                                          | 40  |

| REGISTER BFH, DFH, FFH: VTPP, TU #4 IN TUG2 #1 TO TUG2 #7, AIS INTERRUPT1                                                                                                                        | 42  |

| REGISTER 100H, 200H, 300H: RTOP, TU3 OR TU #1 IN TUG2 #1, CONFIGURATION                                                                                                                          | 43  |

| REGISTER 101H, 201H, 301H: RTOP, TU3 OR TU #1 IN TUG2 #1, CONFIGURATION AND ALARM STATUS1                                                                                                        | 46  |

| REGISTER 102H, 202H, 302H: RTOP, TU3 OR TU #1 IN TUG2 #1, EXPECTED PATH SIGNAL LABEL1                                                                                                            | 49  |

| REGISTER 103H, 203H, 303H: RTOP, TU3 OR TU #1 IN TUG2 #1, ACCEPTED PATH SIGNAL LABEL1                                                                                                            | 50  |

| REGISTER 104H, 204H, 304H: RTOP, TU3 OR TU #1 IN TUG2 #1,<br>BIP-2/BIP-8 ERROR COUNT LSB1                                                                                                        | 51  |

| REGISTER 105H, 205H, 305H: RTOP, TU3 OR TU #1 IN TUG2 #1, BIP-2/BIP-8 ERROR COUNT MSB1                                                                                                           | 51  |

| REGISTER 106H, 206H, 306H: RTOP, TU3 OR TU #1 IN TUG2 #1, FEBE ERROR COUNT LSB                                                                                                                   | 53  |

| REGISTER 107H, 207H, 307H: RTOP, TU3 OR TU #1 IN TUG2 #1, FEBE ERROR COUNT MSB1                                                                                                                  | 153 |

| REGISTER 108H, 110H, 118H, 120H, 128H, 130H: REGISTER<br>208H, 210H, 218H, 220H, 228H, 230H: REGISTER 308H,<br>310H, 318H, 320H, 328H, 330H: RTOP, TU #1 IN TUG2 #2<br>TO TUG2 #7, CONFIGURATION | 155 |

| REGISTER 109H, 111H, 119H, 121H, 129H, 131H: REGISTER 209H, 211H, 219H, 221H, 229H, 231H: REGISTER 309H, 311H, 319H, 321H, 329H, 331H: RTOP, TU #1 IN TUG2 #2 TO TUG2 #7, CONFIGURATION AND ALARM STATUS | 158 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGISTER 10AH, 112H, 11AH, 122H, 12AH, 132H: REGISTER 20AH, 212H, 21AH, 222H, 22AH, 232H: REGISTER 30AH, 312H, 31AH, 322H, 32AH, 332H: RTOP, TU #1 IN TUG2 #2 TO TUG2 #7, EXPECTED PATH SIGNAL LABEL     | 161 |

| REGISTER 10BH, 113H, 11BH, 123H, 12BH, 133H: REGISTER 20BH, 213H, 21BH, 223H, 22BH, 233H: REGISTER 30BH, 313H, 31BH, 323H, 32BH, 333H: RTOP, TU #1 IN TUG2 #2 TO TUG2 #7, ACCEPTED PATH SIGNAL LABEL     | 162 |

| REGISTER 10CH, 114H, 11CH, 124H, 12CH, 134H: REGISTER 20CH, 214H, 21CH, 224H, 22CH, 234H: REGISTER 30CH, 314H, 31CH, 324H, 32CH, 334H: RTOP, TU #1 IN TUG2 #2 TO TUG2 #7, BIP-2 ERROR COUNT LSB          | 163 |

| REGISTER 10DH, 115H, 11DH, 125H, 12DH, 135H: REGISTER 20DH, 215H, 21DH, 225H, 22DH, 235H: REGISTER 30DH, 315H, 31DH, 325H, 32DH, 335H: RTOP, TU #1 IN TUG2 #2 TO TUG2 #7, BIP-2 ERROR COUNT MSB          | 163 |

| REGISTER 10EH, 116H, 11EH, 126H, 12EH, 136H: REGISTER 20EH, 216H, 21EH, 226H, 22EH, 236H: REGISTER 30EH, 316H, 31EH, 326H, 32EH, 336H: TU #1 IN TUG2 #2 TO TUG2 #7, FEBE ERROR COUNT LSB                 | 165 |

| REGISTER 10FH, 117H, 11FH, 127H, 12FH, 137H: REGISTER 20FH, 217H, 21FH, 227H, 22FH, 237H: REGISTER 30FH, 317H, 31FH, 327H, 32FH, 337H: TU #1 IN TUG2 #2 TO TUG2 #7, FEBE ERROR COUNT MSB                 | 165 |

| REGISTER 138H, 238H, 338H: RTOP, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, COPSL INTERRUPT                                                                                                                     | 167 |

| REGISTER 139H, 239H, 339H: RTOP, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, PSLM INTERRUPT                                                                                                                      | 169 |

| REGISTER 13AH, 23AH, 33AH: RTOP, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, PSLU INTERRUPT                                                                                                                      | 171 |

| REGI | STER 13BH, 23BH, 33BH: RTOP, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, RDI INTERRUPT                                                                                                                                         | 173 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGI | STER 13CH, 23CH, 33CH: RTOP, TU3 AUXILIARY RDI<br>INTERRUPT OR TU #1 IN TUG2 #1 TO TUG2 #7 RFI<br>INTERRUPT                                                                                                            | 175 |

| REGI | STER 13DH, 23DH, 33DH: RTOP, TU3 OR TU #1 IN TUG2 #1<br>TO TUG2 #7, IN BAND ERROR REPORTING<br>CONFIGURATION                                                                                                           | 177 |

| REGI | STER 13EH, 23EH, 33EH: RTOP, TU3 OR TU #1 IN TUG2 #1<br>TO TUG2 #7, CONTROLLABLE OUTPUT<br>CONFIGURATION                                                                                                               | 178 |

| REGI | STER 140H, 148H, 150H, 158H, 160H, 168H, 170H:<br>REGISTER 240H, 248H, 250H, 258H, 260H, 268H, 270H:<br>REGISTER 340H, 348H, 350H, 358H, 360H, 368H, 370H:<br>RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, CONFIGURATION         | 179 |

| REGI | STER 141H, 149H, 151H, 159H, 161H, 169H, 171H: REGISTER 241H, 249H, 251H, 259H, 261H, 269H, 271H: REGISTER 341H, 349H, 351H, 359H, 361H, 369H, 371H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND ALARM STATUS | 182 |

| REGI | STER 142H, 14AH, 152H, 15AH, 162H, 16AH, 172H: REGISTER 242H, 24AH, 252H, 25AH, 262H, 26AH, 272H: REGISTER 342H, 34AH, 352H, 35AH, 362H, 36AH, 372H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, EXPECTED PATH SIGNAL LABEL     | 185 |

| REGI | STER 143H, 14BH, 153H, 15BH, 163H, 16BH, 173H: REGISTER 243H, 24BH, 253H, 25BH, 263H, 26BH, 273H: REGISTER 343H, 34BH, 353H, 35BH, 363H, 36BH, 373H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, ACCEPTED PATH SIGNAL LABEL     | 186 |

| REGI | STER 144H, 14CH, 154H, 15CH, 164H, 16CH, 174H: REGISTER 244H, 24CH, 254H, 25CH, 264H, 26CH, 274H: REGISTER 344H, 34CH, 354H, 35CH, 364H, 36CH, 374H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, BIP-2 ERROR COUNT LSB          | 187 |

| REGISTER 145H, 14DH, 155H, 15DH, 165H, 16DH, 175H: REGISTER 245H, 24DH, 255H, 25DH, 265H, 26DH, 275H: REGISTER 345H, 34DH, 355H, 35DH, 365H, 36DH, 375H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, BIP-2 ERROR COUNT MSB | 187 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGISTER 146H, 14EH, 156H, 15EH, 166H, 16EH, 176H: REGISTER 246H, 24EH, 256H, 25EH, 266H, 26EH, 276H: REGISTER 346H, 34EH, 356H, 35EH, 366H, 36EH, 376H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, FEBE ERROR COUNT LSB  | 189 |

| REGISTER 147H, 14FH, 157H, 15FH, 167H, 16FH, 177H: REGISTER 247H, 24FH, 257H, 25FH, 267H, 26FH, 277H: REGISTER 347H, 34FH, 357H, 35FH, 367H, 36FH, 377H: RTOP, TU #2 IN TUG2 #1 TO TUG2 #7, FEBE ERROR COUNT MSB  | 189 |

| REGISTER 178H, 278H, 378H: RTOP, TU #2 IN TUG2 #1 TO TUG2<br>#7, COPSL INTERRUPT                                                                                                                                  | 191 |

| REGISTER 179H, 279H, 379H: RTOP, TU #2 IN TUG2 #1 TO TUG2<br>#7, PSLM INTERRUPT                                                                                                                                   | 192 |

| REGISTER 17AH, 27AH, 37AH: RTOP, TU #2 IN TUG2 #1 TO<br>TUG2 #7, PSLU INTERRUPT                                                                                                                                   | 193 |

| REGISTER 17BH, 27BH, 37BH: RTOP, TU #2 IN TUG2 #1 TO<br>TUG2 #7, RDI INTERRUPT                                                                                                                                    | 194 |

| REGISTER 17CH, 27CH, 37CH: RTOP, TU #2 IN TUG2 #1 TO<br>TUG2 #7, RFI INTERRUPT                                                                                                                                    | 195 |

| REGISTER 17DH, 27DH, 37DH: RTOP, TU #2 IN TUG2 #1 TO<br>TUG2 #7, IN BAND ERROR REPORTING<br>CONFIGURATION                                                                                                         | 196 |

| REGISTER 17EH, 27EH, 37EH: TU #2 IN TUG2 #1 TO TUG2 #7,<br>CONTROLLABLE OUTPUT CONFIGURATION                                                                                                                      | 197 |

| REGISTER 180H, 188H, 190H, 198H, 1A0H, 1A8H, 1B0H:<br>REGISTER 280H, 288H, 290H, 298H, 2A0H, 2A8H, 2B0H:                                                                                                          |     |

| REGISTER 380H, 388H, 390H, 398H, 3A0H, 3A8H, 3B0H:<br>RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, CONFIGURATION198                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGISTER 181H, 189H, 191H, 199H, 1A1H, 1A9H, 1B1H: REGISTER 281H, 289H, 291H, 299H, 2A1H, 2A9H, 2B1H: REGISTER 381H, 389H, 391H, 399H, 3A1H, 3A9H, 3B1H: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND ALARM STATUS |

| REGISTER 182H, 18AH, 192H, 19AH, 1A2H, 1AAH, 1B2H: REGISTER 282H, 28AH, 292H, 29AH, 2A2H, 2AAH, 2B2H: REGISTER 382H, 38AH, 392H, 39AH, 3A2H, 3AAH, 3B2H: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, EXPECTED PATH SIGNAL LABEL     |

| REGISTER 183H, 18BH, 193H, 19BH, 1A3H, 1ABH, 1B3H: REGISTER 283H, 28BH, 293H, 29BH, 2A3H, 2ABH, 2B3H: REGISTER 383H, 38BH, 393H, 39BH, 3A3H, 3ABH, 3B3H: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, ACCEPTED PATH SIGNAL LABEL     |

| REGISTER 184H, 18CH, 194H, 19CH, 1A4H, 1ACH, 1B4H: REGISTER 284H, 28CH, 294H, 29CH, 2A4H, 2ACH, 2B4H: REGISTER 384H, 38CH, 394H, 39CH, 3A4H, 3ACH, 3B4H: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, BIP-2 ERROR COUNT LSB          |

| REGISTER 185H, 18DH, 195H, 19DH, 1A5H, 1ADH, 1B5H: REGISTER 285H, 28DH, 295H, 29DH, 2A5H, 2ADH, 2B5H: REGISTER 385H, 38DH, 395H, 39DH, 3A5H, 3ADH, 3B5H: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, BIP-2 ERROR COUNT MSB          |

| REGISTER 186H, 18EH, 196H, 19EH, 1A6H, 1AEH, 1B6H: REGISTER 286H, 28EH, 296H, 29EH, 2A6H, 2AEH, 2B6H: REGISTER 386H, 38EH, 396H, 39EH, 3A6H, 3AEH, 3B6H: TU #3 IN TUG2 #1 TO TUG2 #7, FEBE ERROR COUNT LSB                 |

| REGISTER 187H, 18FH, 197H, 19FH, 1A7H, 1AFH, 1B7H:<br>REGISTER 287H, 28FH, 297H, 29FH, 2A7H, 2AFH, 2B7H:<br>REGISTER 387H, 38FH, 397H, 39FH, 3A7H, 3AFH, 3B7H:                                                             |

| REGISTER 1B8H, 2B8H, 3B8H: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, COPSL INTERRUPT                                                                                           | RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, FEBE ERROR<br>COUNT MSB                                                                                                   | 208 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TUG2 #7, PSLM INTERRUPT                                                                                                                                                 |                                                                                                                                                              | 210 |

| TUG2 #7, PSLU INTERRUPT                                                                                                                                                 |                                                                                                                                                              | 211 |

| TUG2 #7, RDI INTERRUPT                                                                                                                                                  |                                                                                                                                                              | 212 |

| TUG2 #7, RFI INTERRUPT                                                                                                                                                  | REGISTER 1BBH, 2BBH, 3BBH: RTOP, TU #3 IN TUG2 #1 TO TUG2 #7, RDI INTERRUPT                                                                                  | 213 |

| TUG2 #7, IN BAND ERROR REPORTING CONFIGURATION                                                                                                                          |                                                                                                                                                              | 214 |

| TUG2 #7, CONTROLLABLE OUTPUT CONFIGURATION                                                                                                                              | TUG2 #7, IN BAND ERROR REPORTING                                                                                                                             | 215 |

| REGISTER 2C0H, 2C8H, 2D0H, 2D8H, 2E0H, 2E8H, 2F0H: REGISTER 3C0H, 3C8H, 3D0H, 3D8H, 3E0H, 3E8H, 3F0H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, CONFIGURATION                  | · · · · · · · · · · · · · · · · · · ·                                                                                                                        | 216 |

| REGISTER 2C1H, 2C9H, 2D1H, 2D9H, 2E1H, 2E9H, 2F1H: REGISTER 3C1H, 3C9H, 3D1H, 3D9H, 3E1H, 3E9H, 3F1H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND ALARM STATUS | REGISTER 2C0H, 2C8H, 2D0H, 2D8H, 2E0H, 2E8H, 2F0H: REGISTER 3C0H, 3C8H, 3D0H, 3D8H, 3E0H, 3E8H, 3F0H:                                                        | 217 |

| REGISTER 2C2H, 2CAH, 2D2H, 2DAH, 2E2H, 2EAH, 2F2H:<br>REGISTER 3C2H, 3CAH, 3D2H, 3DAH, 3E2H, 3EAH, 3F2H:<br>RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, EXPECTED PATH            | REGISTER 2C1H, 2C9H, 2D1H, 2D9H, 2E1H, 2E9H, 2F1H:<br>REGISTER 3C1H, 3C9H, 3D1H, 3D9H, 3E1H, 3E9H, 3F1H:<br>RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, CONFIGURATION | 219 |

|                                                                                                                                                                         | REGISTER 2C2H, 2CAH, 2D2H, 2DAH, 2E2H, 2EAH, 2F2H:<br>REGISTER 3C2H, 3CAH, 3D2H, 3DAH, 3E2H, 3EAH, 3F2H:<br>RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, EXPECTED PATH | 222 |

| REGISTER 1C3H, 1CBH, 1D3H, 1DBH, 1E3H, 1EBH, 1F3H: REGISTER 2C3H, 2CBH, 2D3H, 2DBH, 2E3H, 2EBH, 2F3H: REGISTER 3C3H, 3CBH, 3D3H, 3DBH, 3E3H, 3EBH, 3F3H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, PATH SIGNAL LABEL     | 223 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGISTER 1C4H, 1CCH, 1D4H, 1DCH, 1E4H, 1ECH, 1F4H: REGISTER 2C4H, 2CCH, 2D4H, 2DCH, 2E4H, 2ECH, 2F4H: REGISTER 3C4H, 3CCH, 3D4H, 3DCH, 3E4H, 3ECH, 3F4H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, BIP-2 ERROR COUNT LSB | 224 |

| REGISTER 1C5H, 1CDH, 1D5H, 1DDH, 1E5H, 1EDH, 1F5H: REGISTER 2C5H, 2CDH, 2D5H, 2DDH, 2E5H, 2EDH, 2F5H: REGISTER 3C5H, 3CDH, 3D5H, 3DDH, 3E5H, 3EDH, 3F5H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, BIP-2 ERROR COUNT MSB | 224 |

| REGISTER 1C6H, 1CEH, 1D6H, 1DEH, 1E6H, 1EEH, 1F6H: REGISTER 2C6H, 2CEH, 2D6H, 2DEH, 2E6H, 2EEH, 2F6H: REGISTER 3C6H, 3CEH, 3D6H, 3DEH, 3E6H, 3EEH, 3F6H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, FEBE ERROR COUNT LSB  | 226 |

| REGISTER 1C7H, 1CFH, 1D7H, 1DFH, 1E7H, 1EFH, 1F7H: REGISTER 2C7H, 2CFH, 2D7H, 2DFH, 2E7H, 2EFH, 2F7H: REGISTER 3C7H, 3CFH, 3D7H, 3DFH, 3E7H, 3EFH, 3F7H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, FEBE ERROR COUNT MSB  | 226 |

| REGISTER 1F8H, 2F8H, 3F8H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, COPSL INTERRUPT                                                                                                                                     | 228 |

| REGISTER 1F9H, 2F9H, 3F9H: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, PSLM INTERRUPT                                                                                                                                      | 229 |

| REGISTER 1FAH, 2FAH, 3FAH: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, PSLU INTERRUPT                                                                                                                                      | 230 |

| REGISTER 1FBH, 2FBH, 3FBH: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, RDI INTERRUPT                                                                                                                                       | 231 |

| TUG2 #7, RFI INTERRUPT                                                                                | 232 |

|-------------------------------------------------------------------------------------------------------|-----|

| REGISTER 1FDH, 2FDH, 3FDH: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, IN BAND ERROR REPORTING CONFIGURATION   | 233 |

| REGISTER 1FEH, 2FEH, 3FEH: RTOP, TU #4 IN TUG2 #1 TO TUG2 #7, CONTROLLABLE OUTPUT CONFIGURATION       | 234 |

| REGISTER 1FFH, 2FFH, 3FFH: RTOP STATUS                                                                | 235 |

| REGISTER 400H, 440H, 480H: RTTB, TU3 OR TU #1 IN TUG2 #1, CONFIGURATION AND STATUS                    | 236 |

| REGISTER 401H-406H, 441H-446H, 481H-486H: RTTB, TU #1 IN TUG2 #2 TO TUG2 #7, CONFIGURATION AND STATUS | 238 |

| REGISTER 408H-40EH, 448H-44EH, 488H-48EH: RTTB, TU #2 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND STATUS | 240 |

| REGISTER 410H-416H, 450H-456H, 490H-496H: RTTB, TU #3 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND STATUS | 242 |

| REGISTER 418H-41EH, 458H-45EH, 498H-49EH: RTTB, TU #4 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND STATUS | 244 |

| REGISTER 420H, 460H, 4A0H: RTTB, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, TIM INTERRUPT                    | 246 |

| REGISTER 421H, 461H, 4A1H: RTTB, TU #2 IN TUG2 #1 TO TUG2 #7, TIM INTERRUPT                           | 248 |

| REGISTER 422H, 462H, 4A2H: RTTB, TU #3 IN TUG2 #1 TO TUG2 #7, TIM INTERRUPT                           | 249 |

| REGISTER 423H, 463H, 4A3H: RTTB, TU #4 IN TUG2 #1 TO TUG2 #7, TIM INTERRUPT                           | 250 |

| REGISTER 424H, 464H, 4A4H: RTTB, TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, TIU INTERRUPT                    | 251 |

| REGISTER 425H, 465H, 4A5H: RTTB, TU #2 IN TUG2 #1 TO TUG2 #7, TIU INTERRUPT                           | 253 |

| TUG2 #7, TIU INTERRUPT                                                      | 254 |

|-----------------------------------------------------------------------------|-----|

| REGISTER 427H, 467H, 4A7H: RTTB, TU #4 IN TUG2 #1 TO TUG2 #7, TIU INTERRUPT | 255 |

| REGISTER 428H, 468H, 4A8H: RTTB, TIU THRESHOLD                              | 256 |

| REGISTER 429H, 469H, 4A9H: RTTB, INDIRECT TRIBUTARY SELECT                  | 257 |

| REGISTER 42AH, 46AH, 4AAH: RTTB, INDIRECT ADDRESS SELECT                    | 258 |

| REGISTER 42BH, 46BH, 4ABH: RTTB, INDIRECT DATA SELECT                       | 260 |

| REGISTER 800H: MASTER TEST                                                  | 265 |

| TEST REGISTER 801H: (WRITE IN I/O TEST MODE)                                | 267 |

| TEST REGISTER 802H: (WRITE IN I/O TEST MODE)                                | 268 |

| TEST REGISTER 803H: (WRITE IN I/O TEST MODE)                                | 269 |

| TEST REGISTER 804H: (WRITE IN I/O TEST MODE)                                | 270 |

| TEST REGISTER 805H: (WRITE IN I/O TEST MODE)                                | 271 |

| TEST REGISTER 801H: (READ IN I/O TEST MODE)                                 | 272 |

| TEST REGISTER 802H: (READ IN I/O TEST MODE)                                 | 273 |

| TEST REGISTER 803H: (READ IN I/O TEST MODE)                                 | 274 |

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

### **LIST OF FIGURES**

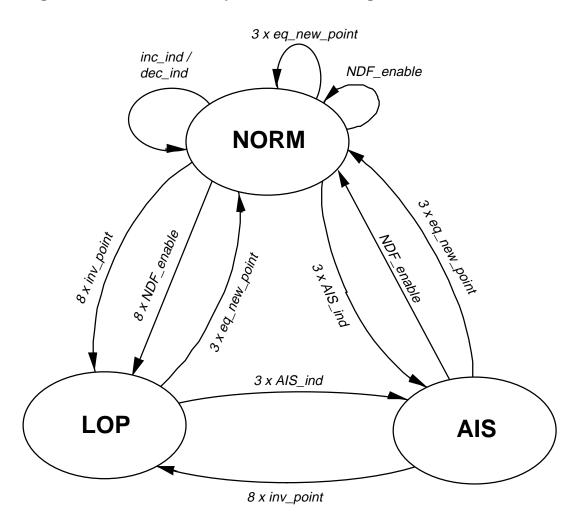

| FIGURE 1 - POINTER INTERPRETATION STATE DIAGRAM                        | 44  |

|------------------------------------------------------------------------|-----|

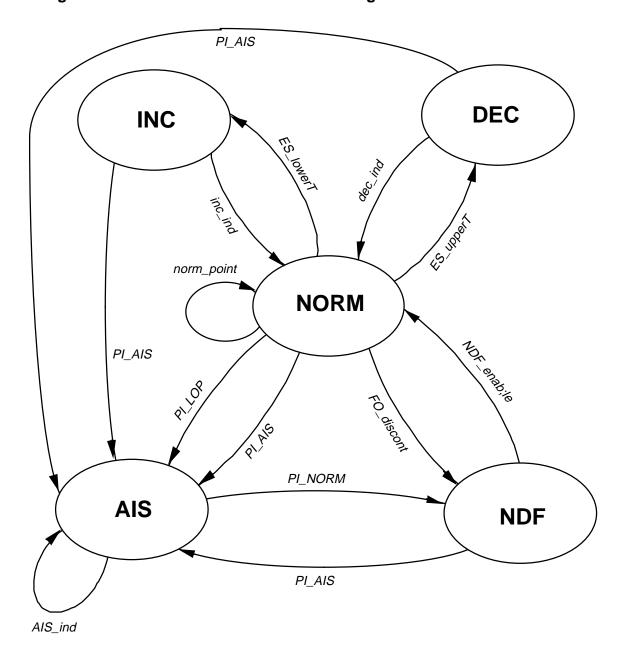

| FIGURE 2 - POINTER GENERATION STATE DIAGRAM                            | 49  |

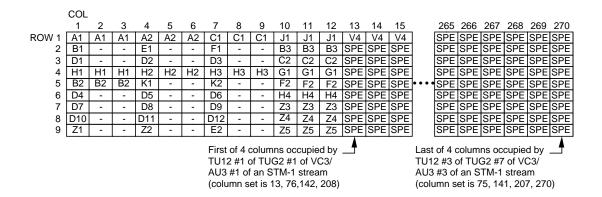

| FIGURE 3 - SONET STS-3 CARRYING VT1.5 WITHIN STS-1                     | 278 |

| FIGURE 4 - SDH STM-1 CARRYING TU12 WITHIN VC3/AU3                      | 278 |

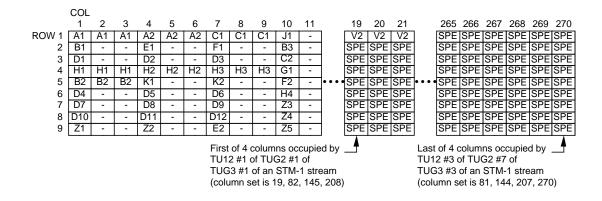

| FIGURE 5 - SDH STM-1 CARRYING TU12 WITHIN TUG3/AU4                     | 279 |

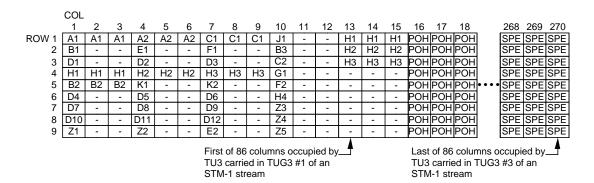

| FIGURE 6 - SDH STM-1 CARRYING TU3 WITHIN TUG3                          | 280 |

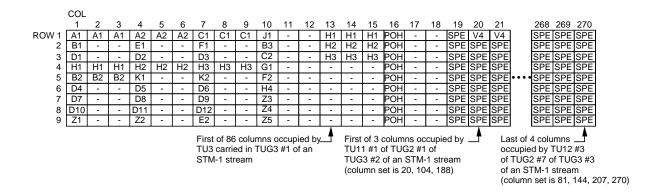

| FIGURE 7 - SDH STM-1 CARRYING MIX OF TU11, TU12, TU3 WITHIN TUG3/AU4   | 280 |

| FIGURE 8 - BOUNDARY SCAN ARCHITECTURE                                  | 281 |

| FIGURE 9 - TAP CONTROLLER FINITE STATE MACHINE                         | 283 |

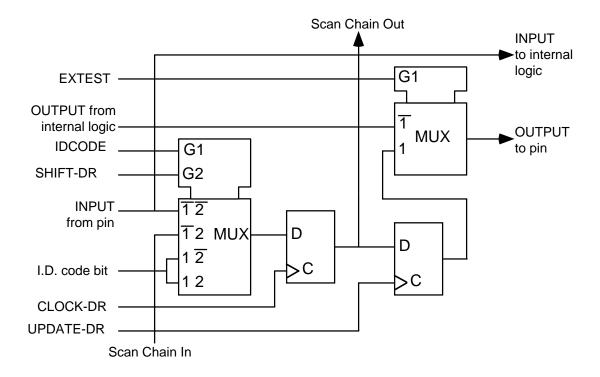

| FIGURE 10- INPUT OBSERVATION CELL (INPUT, CLOCK INPUT)                 | 290 |

| FIGURE 11- OUTPUT CELL (OUTPUT, CLOCK OUTPUT, OUTPUT ENABLE)           | 291 |

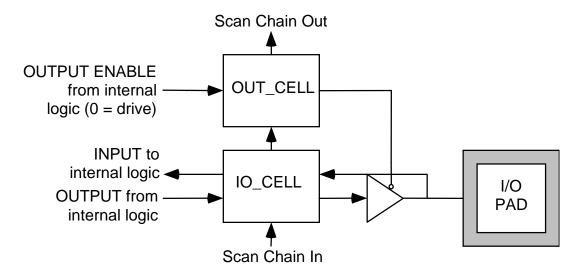

| FIGURE 12- BIDIRECTIONAL CELL (IO_CELL)                                | 292 |

| FIGURE 13- I/O CELL (I/O WITH OE PAIR)                                 | 292 |

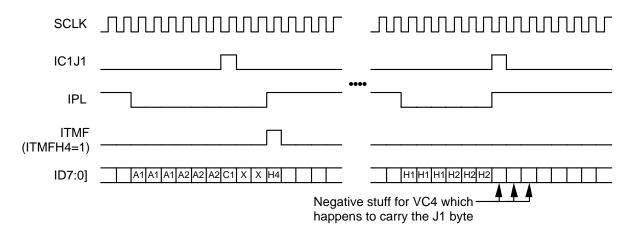

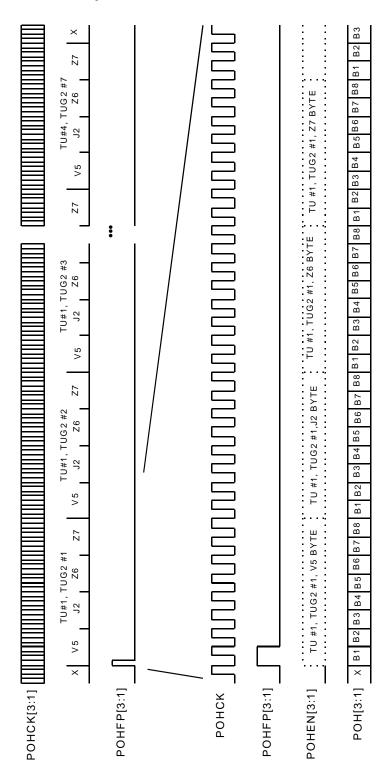

| FIGURE 14- INPUT BUS TIMING - SIMPLE STS-1/AU3 CASE                    | 293 |

| FIGURE 15- INPUT BUS TIMING - COMPLEX STS-1 / AU3 CASE                 | 294 |

| FIGURE 16- INPUT BUS TIMING - AU4 CASE                                 | 295 |

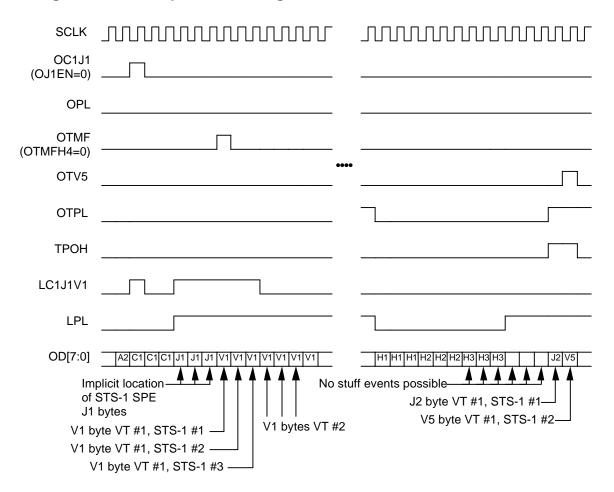

| FIGURE 17- OUTPUT BUS TIMING - LOCKED STS-1 SPES / AU3<br>VCS CASE 296 |     |

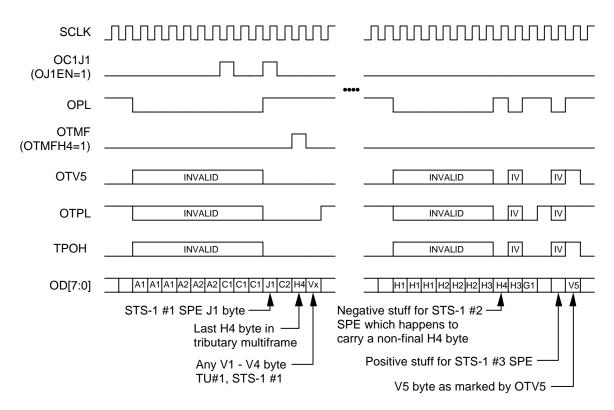

| FIGURE 18- OUTPUT BUS TIMING - FLOATING STS-1 SPES / AU3 VCS CASE      | 297 |

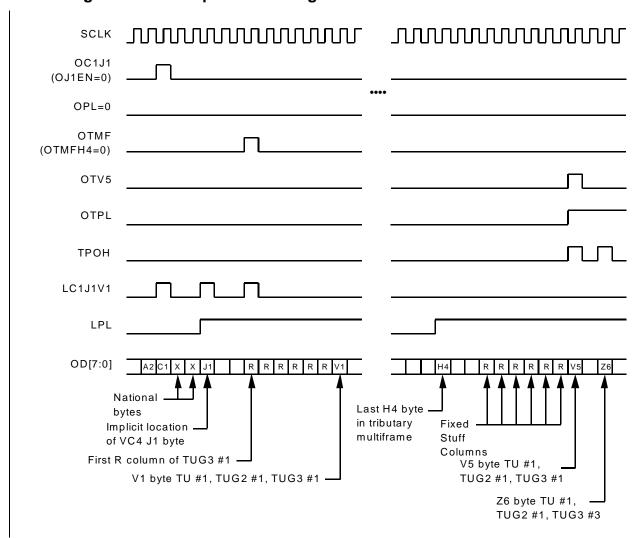

| FIGURE 19- OUTPUT BUS TIMING - LOCKED AU4 VC CASE                      | 299 |

| FIGURE 20- OUTPUT BUS TIMING - FLOATING AU4 VC CASE                                          | 300 |

|----------------------------------------------------------------------------------------------|-----|

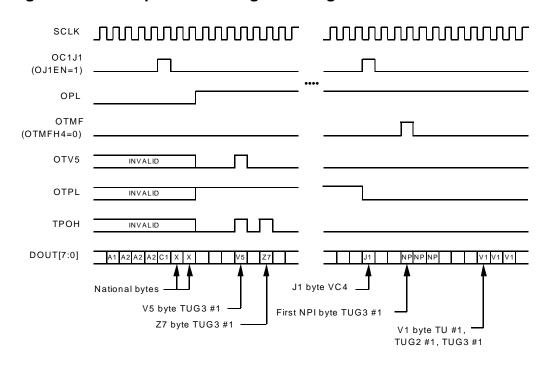

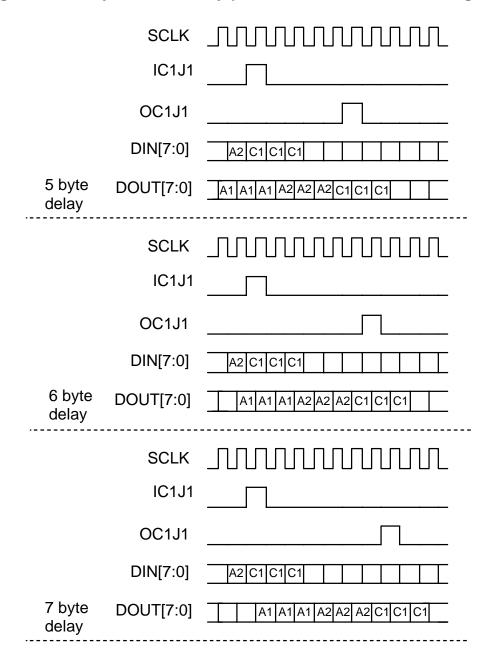

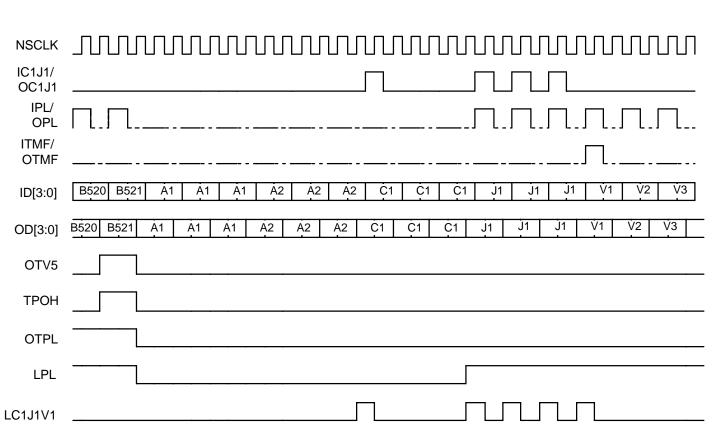

| FIGURE 21- BYTE INTERFACE, BY-PASSED MODE FUNCTIONAL TIMING                                  | 301 |

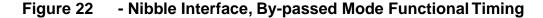

| FIGURE 22- NIBBLE INTERFACE, BY-PASSED MODE FUNCTIONAL TIMING                                | 302 |

| FIGURE 23- TRIBUTARY PATH OVERHEAD SERIALIZATION FUNCTIONAL TIMING                           | 304 |

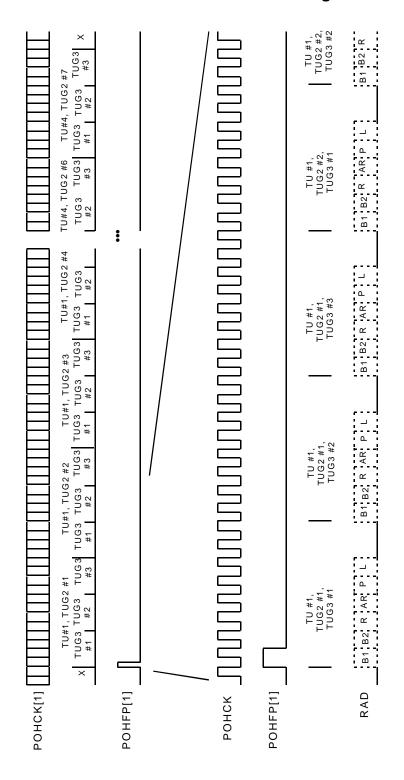

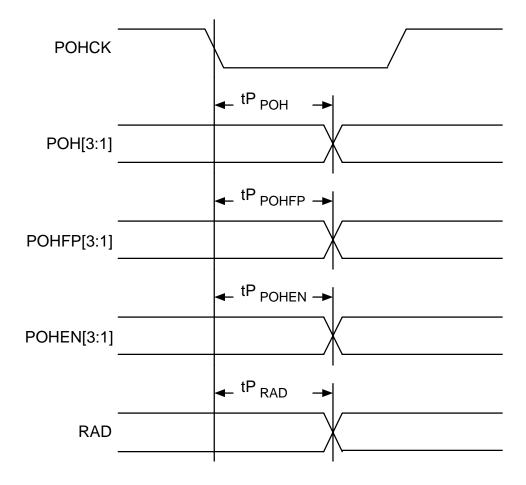

| FIGURE 24- RECEIVE ALARM PORT FUNCTIONAL TIMING                                              | 306 |

| FIGURE 25- NIBBLE INTERFACE MODE INPUT/OUTPUT FUNCTIONAL TIMING                              | 308 |

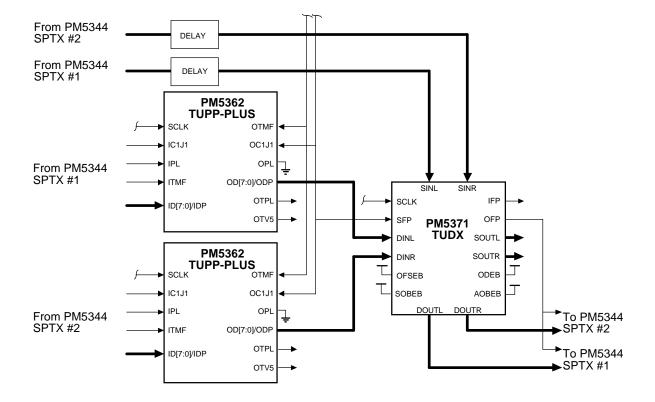

| FIGURE 26- SONET/SDH TRIBUTARY CROSS-CONNECT APPLICATION                                     | 309 |

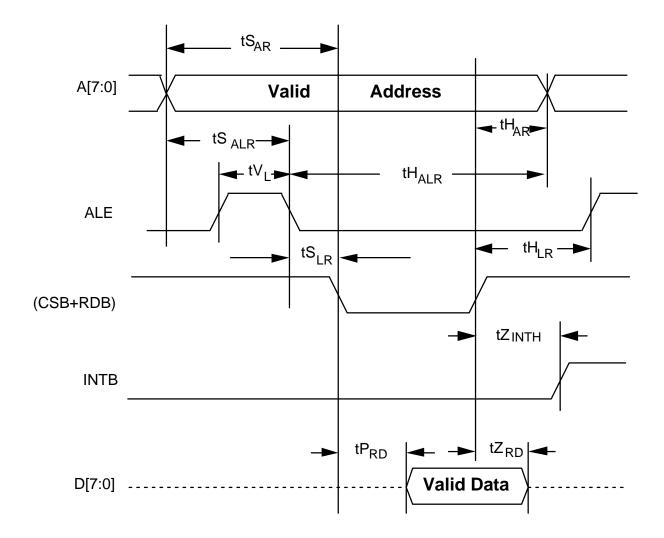

| FIGURE 27- MICROPROCESSOR INTERFACE READ TIMING (INTEL MODE)                                 | 315 |

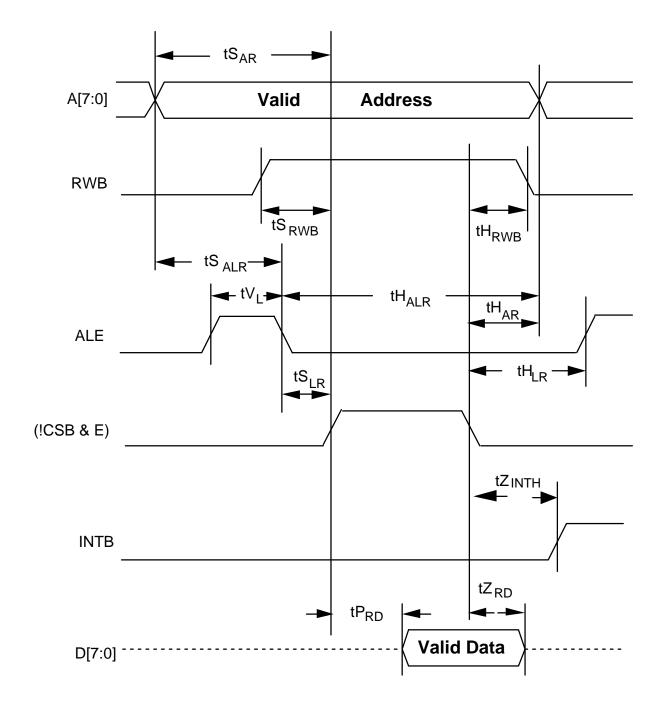

| FIGURE 28- MICROPROCESSOR INTERFACE READ TIMING (MOTOROLA MODE)                              | 316 |

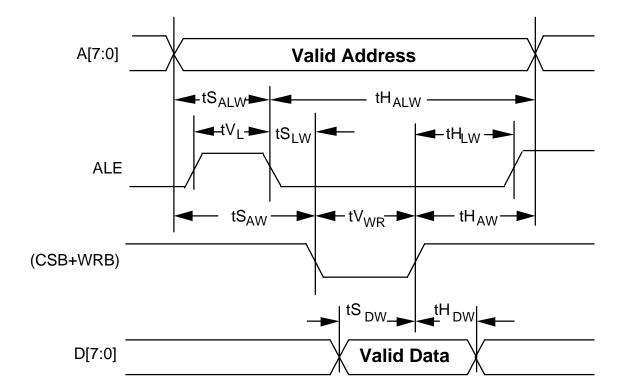

| FIGURE 29- MICROPROCESSOR INTERFACE WRITE TIMING (INTEL MODE)                                | 319 |

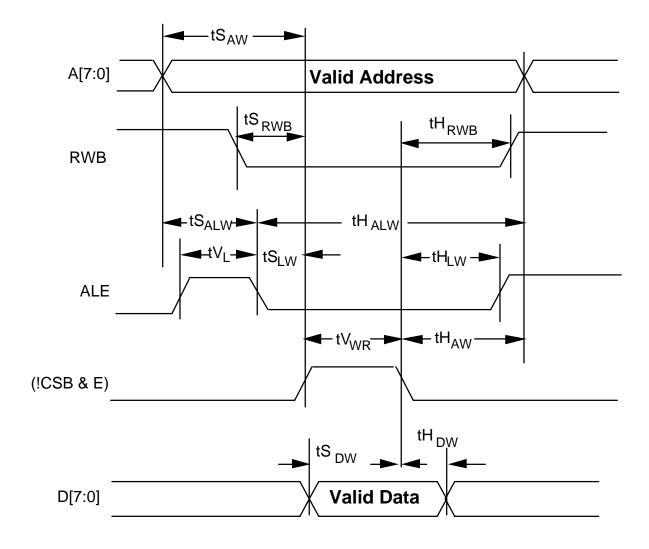

| FIGURE 30- MICROPROCESSOR INTERFACE WRITE TIMING (MOTOROLA MODE)                             | 320 |

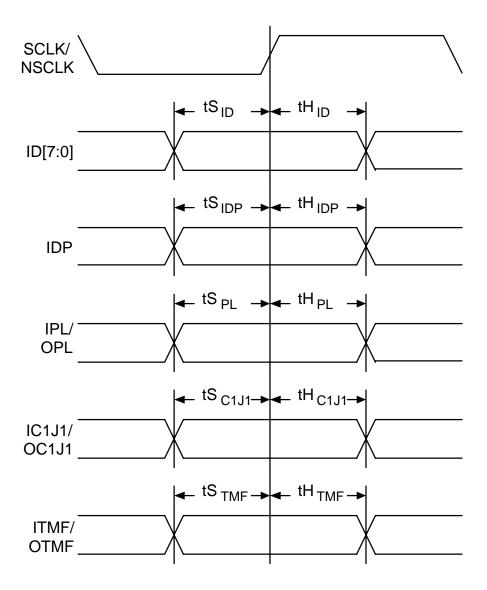

| FIGURE 31- INPUT TIMING                                                                      | 323 |

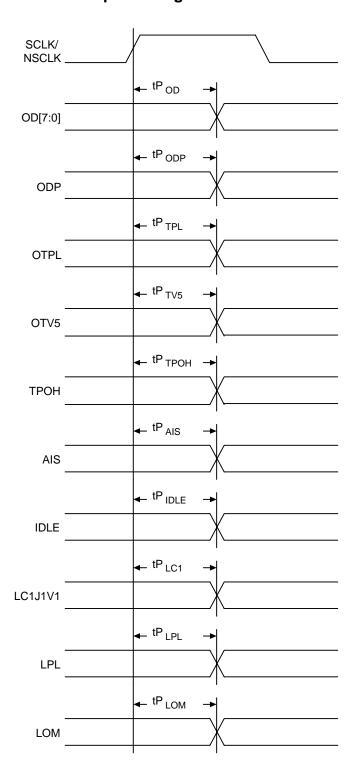

| FIGURE 32- STREAM OUTPUT TIMING                                                              | 326 |

| FIGURE 33- PATH OVERHEAD OUTPUT TIMING                                                       | 327 |

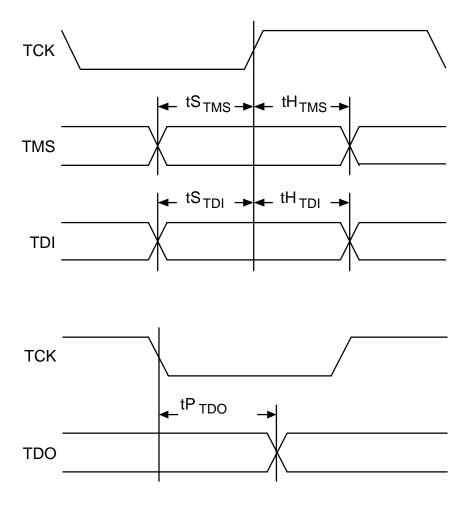

| FIGURE 34- JTAG PORT INTERFACE TIMING                                                        | 329 |

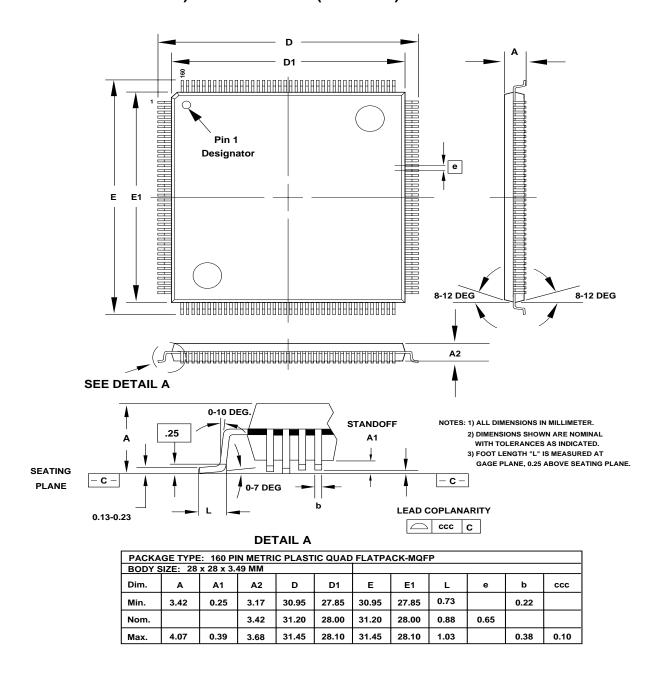

| FIGURE 35- METRIC PLASTIC QUAD FLATPACK - MQFP (BODY 28X28X3.49MM) 160 PIN MQFP - (R SUFFIX) | 331 |

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

### **LIST OF TABLES**

| TABLE 1             | - PATH SIGNAL LABEL MISMATCH STATE                       | 53  |

|---------------------|----------------------------------------------------------|-----|

| TABLE 2             | - TEST MODE REGISTER MEMORY MAP                          | 261 |

| TABLE 3             | - INSTRUCTION REGISTER                                   | 274 |

| TABLE 4             | - BOUNDARY SCAN PIN ORDER                                | 286 |

| TABLE 5             | - TUPP-PLUS ABSOLUTE MAXIMUM RATINGS                     | 310 |

| TABLE 6             | - TUPP-PLUS D.C. CHARACTERISTICS                         | 311 |

|                     | - MICROPROCESSOR INTERFACE READ ACCESS<br>27, FIGURE 28) | 314 |

|                     | - MICROPROCESSOR INTERFACE WRITE ACCESS 29, FIGURE 30)   | 318 |

| TABLE 9             | - TUPP-PLUS INPUT (FIGURE 31)                            | 322 |

| TABLE 10            | - TUPP-PLUS STREAM OUTPUT (FIGURE 32)                    | 325 |

| TABLE 11<br>33) 327 | - TUPP-PLUS PATH OVERHEAD OUTPUT (FIGURE                 |     |

| TABLE 12            | - JTAG PORT INTERFACE (FIGURE 34)                        | 328 |

| TABLE 13            | - TUPP-PLUS ORDERING INFORMATION                         | 330 |

| TABLE 14            | - TUPP-PLUS THERMAL INFORMATION                          | 330 |

ISSUE 6

DATA SHEET PMC-951010

SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

#### 1 FEATURES

- Configurable, multi-channel, payload processor for aligning SONET virtual tributaries (VTs) or SDH tributary units (TUs) in an STS-3 or STM-1 byte serial data stream.

- Transfers all incoming tributaries in the three STS-1 synchronous payload envelopes of an STS-3 byte serial stream to the three STS-1 synchronous payload envelopes of an outgoing STS-3 byte serial stream.

- Transfers all incoming tributaries in the single AU4 or three AU3 administrative units of an STM-1 byte serial stream to the single AU4 or three AU3 administrative units of an outgoing STM-1 byte serial stream.

- Compensates for pleisiochronous relationships between incoming and outgoing higher level (STS-1, AU4, AU3) payload frame rates through processing of the lower level (VT6, VT3, VT2, VT1.5, TU3, TU2, TU12, or TU11) tributary pointers.

- Configurable to process any legal mix of tributaries such as VT1.5, VT2, VT3, VT6, TU11, TU12, TU2, or TU3. Each VT group or TUG2 can be configured to carry one of four tributary types. TUG2s can be multiplexed into VC3s or TUG3s. Each TUG3 can also be configured to carry a single TU3.

- Independently configurable for AU3 or AU4 frame format on incoming and outgoing interfaces.

- Configurable to process 16-byte or 64-byte format tributary path trace messages (tributary trail trace identifiers).

- Optionally frames to the H4 byte in the path overhead to determine tributary multiframe boundaries. Inserts internally generated H4 bytes with leading logic 1 bits into the outgoing administrative units.

- Extracts and serializes the entire tributary path overhead for each tributary into lower speed serial streams.

- Extracts tributary size (SS) bits for each tributary into internal registers.

- Detects loss of pointer (LOP) and re-acquisition for each tributary and optionally generates interrupts.

- Detects tributary path alarm indication signal (AIS) and return to normal state for each tributary and optionally generates interrupts.

- Detects tributary elastic store underflow and overflow errors and optionally generates interrupts.

- Extracts tributary path trace message (trail trace identifier) for each tributary into internal buffers.

- Provides individual tributary path trace message buffer that holds the expected message and detects tributary path trace mismatch (trail trace identifier mismatch) alarms (TIM) and return to matched state for each tributary and optionally generates interrupts.

- Detects tributary path trace unstable (trail trace identifier unstable) alarms (TIU) and return to stable state for each tributary and optionally generates interrupts.

- Extracts tributary path signal label for each tributary into internal registers and detects change of tributary path signal label events (COPSL) for each tributary and optionally generates interrupts.

- Provides individual tributary path signal label register that hold the expected label and detects tributary path signal label mismatch alarms (PSLM) and return to matched state for each tributary and optionally generates interrupts.

- Detects tributary path signal label unstable alarms (PSLU) and return to stable state for each tributary and optionally generates interrupts.

- Detects tributary unequipped defect (UNEQ) and tributary path defect indication (PDI-V).

- Detects assertion and removal of tributary extended remote defect indications (RDI) for each tributary and optionally generates interrupts.

- Calculates and compares the tributary path BIP-2 error detection code for each tributary and configurable to accumulate the BIP-2 errors, on block or bit basis, in internal registers.

- Calculates and compares the TU3 path BIP-8 error detection code for each TU3 stream and accumulates the BIP-8 errors, on block or bit basis, in internal registers.

- Accumulates TU3 tributary far end block errors (FEBE) on a bit or a block basis, in internal registers.

- Allows insertion of all-zeros or all-ones tributary idle code with unequipped indication and valid pointer into any tributary under software control. Idle tributaries are identified by an output signal.

- Identifies outgoing tributaries that are in AIS state by an output signal. Allows software to force the AIS insertion on a per tributary basis.

- Inserts valid H4 byte and all-zeros fixed stuff bytes on the outgoing stream. Remaining path overhead bytes (J1, B3, C2, G1, F2, Z3, Z4, and Z5) can be configured to be set to all-zeros or to reflect the value of the corresponding POH bytes in the incoming stream.

- Inserts valid pointers, and all-zeros transport overhead bytes on the outgoing stream with valid "TeleCombus" control signals when configured to operate in locked mode.

- Supports in-band error reporting by updating the FEBE, RDI and auxiliary RDI bits in the V5 byte (G1 in TU3) with the status of the incoming stream.

- Provides low maximum tributary processing delay of 33 µs for VT1.5, 25 µs for VT2, 17 µs for VT3, and 9 µs for VT6 streams.

- Verifies parity on the IC1J1 and ISPE signals and on the incoming data stream and generates parity on the outgoing data stream.

- May be used for multiframe synchronization or ring closure at the head-end node of a SONET/SDH ring.

- Operates in conjunction with the PM5344 SPTX SONET/SDH Path Terminating Transceiver to align tributaries such that they can be switched by the PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect. Provides backwards compatibility with the PM5361 TUPP SONET/SDH Tributary Unit Payload Processor.

- Independently configurable incoming and outgoing interfaces that operate in byte interface mode from a single 19.44 MHz clock or in nibble interface mode from a single 38.88 MHz clock.

- Provides a generic 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Provides a standard 5 signal IEEE P1149.1 JTAG test port for boundary scan test purposes.

- Low power, +5 Volt, CMOS technology, TTL compatible inputs and outputs.

- 160 pin plastic quad flat pack (PQFP) package

ISSUE 6

SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

#### **APPLICATIONS**

- SONET/SDH Wideband Cross-Connect

- SONET/SDH Add-Drop Multiplexer

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

#### 3 **REFERENCES**

- American National Standard for Telecommunications Digital Hierarchy -Optical Interface Rates and Formats Specification, ANSI T1.105-1991.

- 2. American National Standard for Telecommunications Digital Hierarchy -Optical Interface Rates and Formats Specification - Supplement, ANSI T1.105a-1991.

- Committee T1 Contribution, "Draft of T1.105 SONET Rates and Formats", T1X1.5/94-033R2-1994.

- 4. Committee T1 Contribution, "Payload Defect Indication (PDI): triggers, Switch Priorities, Timing and Proposed Text", T1X1.5/94-135R1, 1994.

- 5. Committee T1 Contribution, "Proposed ITU-T Contribution on Enhanced Path RDI for SDH", T1X1.5/94-117, 1994.

- 6. ITU, Recommendation G.708 "Network Node Interface For The Synchronous Digital Hierarchy", 1993.

- 7. ITU, Recommendation G.709 "Synchronous Multiplexing Structure", 1993.

- 8. ITU, Recommendation G.782 "Types and general characteristics of synchronous digital hierarchy (SDH) equipment", 1990.

- 9. ITU, Recommendation G.783 "Characteristics of synchronous digital" hierarchy (SDH) equipment functional blocks", 1990.

- 10. Bell Communications Research SONET Transport Systems: Common Generic Criteria, TR-TSY-000253, Issue 2, December 1991.

- 11. Bell Communications Research SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 1, December 1994.

- 12. Bell Communications Research SONET Add-Drop Multiplex Equipment (SONET ADM) Generic Criteria, TR-NWT-000496, Issue 3, May 1992.

- Bell Communications Research SONET Dual-Fed Unidirectional Path Switched Ring (UPSR) Equipment Generic Criteria, GR-1400-CORE, Issue 1. March 1994.

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

14. European Telecommunications Standards Institute, Transmission and Multiplexing (TM); Generic Functional Requirements for SDH Transmission Equipment, Part 1, Generic Process and Performance, prETS 300 417-1-1, June 1995.

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

#### **DESCRIPTION**

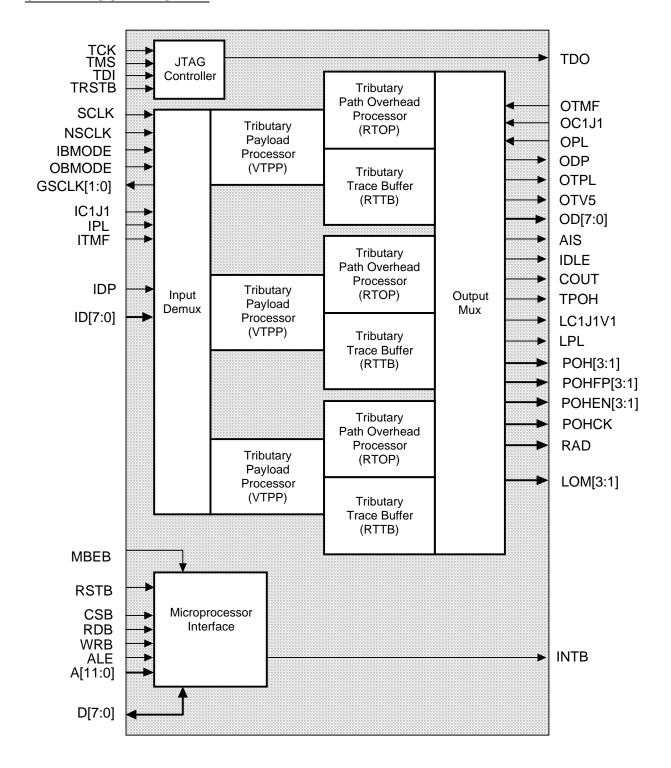

The PM5362 TUPP-PLUS SONET/SDH Tributary Unit Payload Processor / Performance Monitor is a monolithic integrated circuit that implements a configurable, multi-channel, payload processor that aligns and monitors performance of SONET virtual tributaries (VTs) or SDH tributary units (TUs.).

When configured for SONET compatible operation, the TUPP-PLUS transfers all tributaries in the three STS-1 synchronous payload envelopes of an incoming STS-3 byte serial stream to the three STS-1 synchronous payload envelopes of an outgoing STS-3 byte serial stream. Similarly, when configured for SDH compatible operation, the TUPP-PLUS transfers all tributaries in the single AU4 or three AU3 administrative units of an incoming STM-1 byte serial stream to a single AU4 or three AU3 administrative units of an outgoing STM-1 byte serial stream. The TUPP-PLUS compensates for pleisiochronous relationships between incoming and outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope frame rates through processing of the lower level (VT6, VT3, VT2, VT1.5, TU3, TU2, TU12, TU11) tributary pointers.

The TUPP-PLUS is configurable to process any legal mix of tributaries. Each VT group can be configured to carry any one of the four tributary types (VT1.5, VT2, VT3, or VT6) and each TUG2 can be configured to carry any one of three tributary types (TU11, TU12, or TU2). TUG2s can be multiplexed into a VC3 or a TUG3. Alternatively, each TUG3 can be configured to carry a TU3.

The TUPP-PLUS operates in conjunction with the PM5344 SONET/SDH Path Terminating Transceiver to align tributaries such that they can be switched by the PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect.

The TUPP-PLUS provides useful maintenance functions. They include, for each tributary, detection of loss of pointer, detection of AIS alarm, detection of tributary path signal label mismatch and unstable alarms, detection of tributary path trace mismatch and unstable alarms. Optionally, interrupts can be generated due to the assertion and removal of any of the above alarm conditions. The TUPP-PLUS counts received tributary path BIP-2 (BIP-8 for TU3) errors on a block or bit basis and counts FEBE indications. The TUPP-PLUS also allows insertion of tributary path AIS as a consequence of any of the above alarm conditions. In addition, the TUPP-PLUS may insert tributary idle (unequipped) into any tributary. Incoming tributary path trace messages and path signal labels are stored in a set of microprocessor accessible registers. The TUPP-PLUS can

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

also insert inverted new data flag fields that can be used to diagnose downstream pointer processing elements.

No auxiliary high speed clocks are required as the TUPP-PLUS operates from either a single 19.44 MHz or a single 38.88 MHz line rate clock. The TUPP-PLUS is configured, controlled and monitored via a generic 8-bit microprocessor bus interface.

The TUPP-PLUS is implemented in low power, +5 Volt, CMOS technology. It has TTL compatible inputs and outputs and is packaged in a 160 pin HPPQFP package.

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

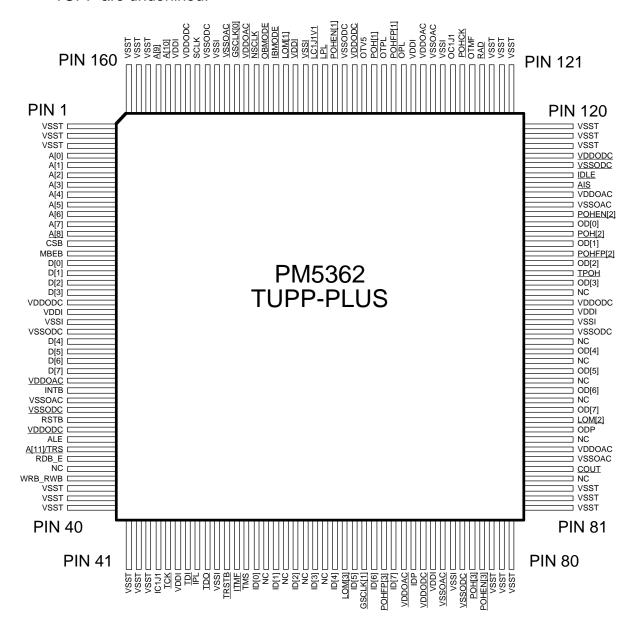

#### 5 PIN DIAGRAM

The TUPP-PLUS is packaged in an 160 pin PQFP package having a body size of 28 mm by 28 mm and a pin pitch of 0.65 mm. Pins added since the PM5361-TUPP are underlined.

ISSUE 6 SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

#### **6 BLOCK DIAGRAM**

ISSUE 6

SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR / PERFORMANCE MONITOR

### **PIN DESCRIPTION**

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                        |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK/    | Input | 153        | The system clock (SCLK) provides timing for TUPP-PLUS internal operations. SCLK is a 19.44 MHz, nominally 50% duty cycle, clock. When either incoming interface is in nibble mode (IBMODE set low) or the outgoing interface is in nibble mode (OBMODE set low), SCLK must be connected to GSCLK[0] externally. |

|          |       |            | In incoming byte interface mode (IBMODE set high), IC1J1, IPL, ITMF, IDP, ID[7:0], OTMF, OC1J1 and OPL are sampled on the rising edge of SCLK. In outgoing byte interface mode (OBMODE set high), ODP, OTPL, OTV5, OD[7:0], AIS, IDLE, TPOH, LC1J1V1, LPL, and LOM[3:1] are updated on the rising edge of SCLK. |

| VCLK     |       |            | The test vector clock (VCLK) signal is used during TUPP-PLUS production testing to verify manufacture.                                                                                                                                                                                                          |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NSCLK    | Input | 147        | The nibble interface mode system clock (NSCLK) provides timing for TUPP-PLUS internal operations in incoming or outgoing nibble interface mode (IBMODE or OBMODE set low). NSCLK is a 38.88 MHz, nominally 50% duty cycle, clock.                                                                                                                                                                                                                                                                                                        |

|          |       |            | In incoming nibble interface mode (IBMODE set low), IC1J1, IPL, ITMF, IDP, ID[3:0] are sampled on the rising edge of NSCLK. In outgoing nibble interface mode (OBMODE set low), OTMF, OC1J1 and OPL are sampled on the rising edge of NSCLK, and ODP, OTPL, OTV5, OD[7:0], AIS, IDLE, TPOH, LC1J1V1, LPL, and LOM[3:1] are updated on the rising edge of NSCLK. When the incoming and the outgoing interfaces are in byte mode (IBMODE and OBMODE both set high), NSCLK may be left unconnected. NSCLK has an integral pull-up resistor. |

| IBMODE   | Input | 145        | The incoming byte interface mode signal (IBMODE) configures the incoming interface mode of the TUPP-PLUS. When IBMODE is set low, nibble interface mode is selected. SCLK must be connected to GSCLK[0]. IC1J1, IPL, ITMF, IDP, ID[3:0] are sampled on the rising edge of NSCLK. When IBMODE is set high, byte interface mode is selected. IC1J1, IPL, ITMF, IDP, ID[7:0] are sampled on the rising edge of SCLK. IBMODE has an integral pull-up resister.                                                                               |

ISSUE 6

| Pin Name             | Туре   | Pin<br>No.              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OBMODE               | Input  | 146                     | The outgoing byte interface mode signal (OBMODE) configures the outgoing interface mode of the TUPP-PLUS. When OBMODE is set low, nibble interface mode is selected. SCLK must be connected to GSCLK[0]. OTMF, OC1J1 and OPL are sampled on the rising edge of NSCLK. ODP, OTPL, OTV5, OD[3:0], AIS, IDLE, LC1J1V1, LPL, and LOM[3:1] are updated on the rising edge of NSCLK. When OBMODE is set high, byte interface mode is selected. OTMF, OC1J1 and OPL are sampled on the rising edge of SCLK. ODP, OTPL, OTV5, OD[7:0], AIS, IDLE, LC1J1V1, LPL, and LOM[3:1] are updated on the rising edge of SCLK. OBMODE has an integral pull-up resister. |

| GSCLK[1]<br>GSCLK[0] | Output | <u>65</u><br><u>149</u> | The generated system clock (GSCLK[1:0]) signals provide timing for the TUPP-PLUS when nibble mode is selected at the incoming or outgoing interface (IBMODE or OBMODE set low). GSCLK[1:0] are a divide by two of NSCLK. GSCLK[0] must only be connected to SCLK externally when IBMODE or OBMODE is set low. GSCLK[1] is a exact replica of GSCLK[0] and can be used to supply timing to external devices that are operating in byte mode. GSCLK[1:0] are updated on the rising edge of NSCLK.                                                                                                                                                       |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC1J1    | Input | 44         | The input C1/J1 frame pulse (IC1J1) identifies the transport envelope and synchronous payload envelope frame boundaries on the incoming stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |       |            | In incoming byte interface mode (IBMODE set high), IC1J1 is set high while IPL is low to mark the first C1 byte of the transport envelope frame on the ID[7:0] bus. IC1J1 is set high while IPL is high to mark each J1 byte of the synchronous payload envelope(s) on the ID[7:0] bus. IC1J1 must be present at every occurrence of the first C1 and all J1 bytes. The TUPP-PLUS will ignore a pulse on IC1J1 at the byte position of the V1 byte of the first tributary of each VC3 or the top byte of the first fixed stuff column of each TUG3. IC1J1 is sampled on the rising edge of SCLK.                                                                                                                                     |

|          |       |            | In incoming nibble interface mode (IBMODE set low), IC1J1 is set high while IPL is low to mark the more significant nibble of the first C1 byte of the transport envelope frame on the ID[3:0] bus. IC1J1 is set high while IPL is high to mark the more significant nibble of each J1 byte of the synchronous payload envelope(s) on the ID[3:0] bus. IC1J1 must be present at every occurrence of the first C1 and all J1 bytes. The TUPP-PLUS will ignore a pulse on IC1J1 at the byte position of the V1 byte of the first tributary of each VC3 or the top byte of the first fixed stuff column of each TUG3. IC1J1 must be set low during the less significant nibble timeslots. IC1J1 is sampled on the rising edge of NSCLK. |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                   |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPL      | Input | 48         | The active high incoming payload active (IPL) signal identifies the bytes within the transport envelope frame on the incoming stream that carry the VC3 or VC4 virtual containers, or the STS-1 synchronous payload envelopes.                             |

|          |       |            | In incoming byte interface mode (IBMODE set high), IPL must be brought high to mark each payload byte on ID[7:0]. IPL is sampled on the rising edge of SCLK.                                                                                               |

|          |       |            | In incoming nibble interface mode (IBMODE set low), IPL must be brought high to mark the more significant nibble of each payload byte on ID[3:0]. IPL is ignored during the less significant nibble timeslots. IPL is sampled on the rising edge of NSCLK. |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

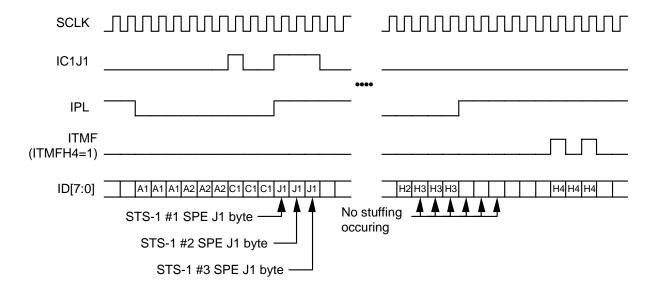

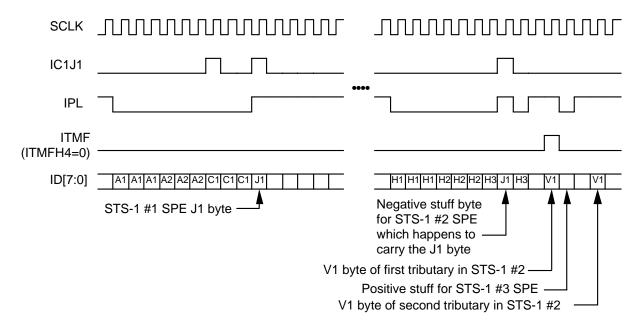

| ITMF     | Input | 52         | The active high incoming tributary multiframe (ITMF) signal identifies the first frame of the tributary multiframe for each STS-1 synchronous payload envelope, AU3, or AU4 administrative unit. ITMF is enabled by the setting the ITMFEN register bit high. When ITMFEN bit is low, the path overhead H4 byte is used to determine tributary multiframe boundaries. ITMF is selectable to pulse high during the third byte after J1 of the first tributary or during the H4 byte which indicates that the next frame is the first frame of the tributary multiframe. Selection between marking each H4 or the third byte after each J1 is controlled by the ITMFH4 register bit. Pulses on ITMF are only effective during the H4 or third byte after each J1 byte positions, as appropriate. ITMF is ignored at other byte positions. |

|          |       |            | In incoming byte interface mode (IBMODE set high), ITMF is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |       |            | In incoming nibble interface mode (IBMODE set low), ITMF marks the more significant nibble of H4 or the third byte after J1, as appropriate. It is ignored at the less significant nibble timeslots. ITMF is sampled on the rising edge of NSCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDP      | Input | 70         | The incoming data parity (IDP) signal carries the parity of the incoming signals.                                                                                                                                                                                                                                                                                                                                                                |

|          |       |            | In incoming byte interface mode (IBMODE set high), the parity calculation encompasses the ID[7:0] bus and optionally the IC1J1 and the IPL signals. IC1J1 and IPL can be included in the parity calculation by setting the INCC1J1 and INCPL register bits high, respectively. Odd parity is selected by setting the IOP register bit high, and even parity is selected by setting the IOP bit low. IDP is sampled on the rising edge of SCLK.   |

|          |       |            | In incoming nibble interface mode (IBMODE set low), The parity calculation encompasses the ID[3:0] bus and optionally the IC1J1 and the IPL signals. IC1J1 and IPL can be included in the parity calculation by setting the INCC1J1 and INCPL register bits high, respectively. Odd parity is selected by setting the IOP register bit high, and even parity is selected by setting the IOP bit low. IDP is sampled on the rising edge of NSCLK. |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID[0]    | Input | 54         | The incoming data bus (ID[7:0]) carries SONET/SDH frame data in byte serial format.                                                                                                                                                                                                                                                                                                                                                                 |

| ID[1]    |       | 56         | , i                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ID[2]    |       | 58         | In incoming byte interface mode (IBMODE set high), ID[7] is the most significant bit,                                                                                                                                                                                                                                                                                                                                                               |

| ID[3]    |       | 60         | corresponding to bit 1 of each serial word, the                                                                                                                                                                                                                                                                                                                                                                                                     |

| ID[4]    |       | 62         | bit transmitted first. ID[0] is the least significant bit, corresponding to bit 8 of each serial word,                                                                                                                                                                                                                                                                                                                                              |

| ID[5]    |       | 64         | the last bit transmitted. The ID[7:0] bus is                                                                                                                                                                                                                                                                                                                                                                                                        |

| ID[6]    |       | 66         | sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ID[7]    |       | 68         | In incoming nibble interface mode (IBMODE set low), ID[3] is the most significant bit of each nibble, corresponding to bit 1 or bit 5 of each serial word, the bit transmitted first and fifth, respectively. ID[0] is the least significant bit of each nibble, corresponding to bit 4 or bit 8 of each serial word, the fourth or last bit transmitted, respectively. ID[7:4] is ignored. The ID[3:0] bus is sampled on the rising edge of NSCLK. |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OC1J1    | Input | 127        | The outgoing composite frame pulse (OC1J1) marks the transport frame and synchronous payload envelope frame boundaries on the outgoing stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |       |            | In outgoing byte interface mode (OBMODE set high), and the OJ1EN register bit is set low, OC1J1 pulses high to mark the first C1 byte of the transport envelope frame on the OD[7:0] bus. The OPL input must be held low. The position of the J1 byte(s) is implicit and fixed to the bytes immediately following the last C1 byte. When the OJ1EN register bit is set high, the OC1J1 signal pulses high while OPL is low to mark the first C1 byte of the transport frame on the OD[7:0] bus and pulses high while OPL is high to mark each of the J1 bytes of the synchronous payload envelope(s) on the OD[7:0] bus. OC1J1 must be present at every occurrence of the first C1 byte and all J1 bytes. A V1 pulse added to the OC1J1 input will be ignored by the TUPP-PLUS. OC1J1 is sampled on the rising edge of SCLK.                                                                                                                                     |

|          |       |            | In outgoing nibble interface mode (OBMODE set low), and the OJ1EN register bit is set low, OC1J1 pulses high to mark the more significant nibble of the first C1 byte of the transport envelope frame on the OD[3:0] bus. The OPL input must be held low. The position of the J1 byte(s) is implicit and fixed to the bytes immediately following the last C1 byte. When the OJ1EN register bit is set high, the OC1J1 signal pulses high while OPL is low to mark the more significant nibble of the first C1 byte of the transport frame on the OD[3:0] bus and pulses high while OPL is high to mark each of the J1 bytes of the synchronous payload envelope(s) on the OD[3:0] bus. OC1J1 must be present at every occurrence of the first C1 byte and all J1 bytes. A V1 pulse added to the OC1J1 input will be ignored by the TUPP-PLUS. OC1J1 must be set low during the less significant nibble timeslots. OC1J1 is sampled on the rising edge of NSCLK. |

ISSUE 6

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTMF     | Input | 125        | The active high outgoing tributary multiframe (OTMF) signal identifies the first frame of the tributary multiframe for each AU3, or AU4 administrative unit, or STS-1 synchronous payload envelope. OTMF is selectable to pulse high during the third byte after J1 of the first tributary or during the H4 byte of the path overhead which indicates that the next frame is the first frame of the tributary multiframe. Selection between marking the third byte after each J1 or H4 bytes is controlled by the OTMFH4 bit. Pulses on OTMF are only effective during the H4 or third byte after each J1 byte positions, as appropriate. OTMF is ignored at other byte positions. |

|          |       |            | In outgoing byte interface mode (OBMODE set high), OTMF is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |