# PMIC-DVC-101

# FEATURES

- 4 analog inputs

expandable to 128 using the SCIC-DVC-101

- 12 bit A/D converter (480 KSPS)

- User configurable including sub-commutation

and super commutation

- 3 Digital Configurable Ports (16-bit inputs)

- Serial Input Port (115K baud)

- PCM NRZ-L or RNRZ-L (IRIG-106) output

- Selectable internal/external clock

- Provides time delay with external memory

- Single 5 Volt Operation

- 176 Lead Thin Quad Flatpack

- Available In Die Form

# APPLICATIONS

- Munitions Testing

- Industrial Instrumentation

- Patient Monitoring

- System Health Monitoring

# **GENERAL DESCRIPTION**

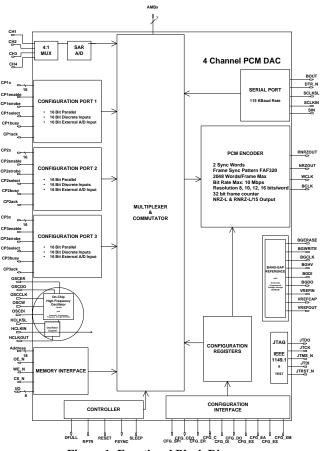

The 4 Channel PCM IC is a fully integrated, programmable, and expandable data acquisition system. It accepts four signal-conditioned analog input channels and performs pulse code modulation (PCM) non-return to zero level (NRZ-L) encoding to the IRIG-106-96 PCM standard. It has 16 discrete inputs, parallel and serial interfaces, can use an internal or external clock, optional memory delay, configuration memory for programmability, and power management capabilities for low power battery operation. A block diagram of the 4 Channel PCM IC is shown in Figure 1.

The 4 Channel PCM IC has a four-input analog multiplexer and a 12-bit successive approximation register (SAR) architecture analog-to-digital (A/D) converter that samples the input signal waveforms. The 4-to-1 analog multiplexer can pass four conditioned analog signals, each with a maximum bandwidth of 0 to 60 KHz. Signals may be captured by the onchip (internal) SAR A/D converter or by an external A/D converter, or both. An external multiplexer control port provides system expansion to a maximum of 128 analog channels.

The 4 Channel PCM IC has digital configuration ports that can be configured to receive 16-bit parallel data, 16-bit A/D converter inputs, and 16 discrete inputs. A serial port supports baud rates greater than 115K.

Once data is captured the digital multiplexer & commutator feed the digital signals into the PCM encoder.

The PCM encoder frames and synchronizes the data according to the IRIG-106-96 Telemetry Standard. This includes a selectable output bit rate from 62.5 kilobits per second (Kbps) to 10 megabits per second (Mbps).

**4 Channel PCM Integrated Circuit**

Figure 1: Functional Block Diagram

The PCM output code type is selectable for NRZ-L or RNRZ-L. The default at chip power-up is NRZ-L. The frame synchronization pattern is FAF320 in hexadecimal and is placed at the end of each frame. A 32-bit frame counter will increment per frame. An 8-bit sub-frame counter is available as a sub-frame ID code. The frame format is programmable from 8 to 2048 words-per-frame.

Sub-commutation capability is possible as defined per IRIG-106-96, section 4.3.2 "Frame Structure". The default mode is 7 words-per-frame and contains the four analog channels, discrete inputs, a frame counter word, and 2 sync words. Word alignment is most significant bit first. Alternative frame formats may be programmed into the configuration memory.

The 4 Channel PCM IC also has the capability to impart a time delay using external SRAM. A 2<sup>17</sup> maximum addressable memory is supported (125 ms for a single channel).

An externally selectable internal clock or an external reference may be used depending on required system precision.

©2000 Systems & Processes Engineering Corporation – SoC Products 101 West Sixth Street, Suite 200, Austin, Texas 78701-2932 Tel: 512/479-7732 Fax: 512/494-0756 e-mail: <u>socproducts.info@spec.com</u> URL: <u>http://www.spec.com</u> REV A1-6 -1-

HARDENED SUBMINIATURE TELEMETRY AND SENSOR SYSTEM DATA ACQUISITION CHIPSET

# PMIC-DVC-101

On warm-up, the 4 Channel PCM DAC will generate a PCM output within 50 milliseconds after primary power is applied.

Several power management techniques are used to improve low power battery operation. In operation, the chip selectively clocks only the functions that are needed to perform the task at hand. As well the chip may be powered down into a sleep mode which retains configuration data for quick restart.

#### PROGRAMMING

#### **Time Delay**

The 4 Channel PCM DAC IC can be configured to delay specific channels. Input pin TRIG synchronizes the delay to an external event.

#### **Configuration Interface**

The 4 Channel PCM DAC IC initializes in a powerup default configuration that is hard-coded in the internal logic. If the chip is in an external configuration mode, a configuration file is loaded via the configuration interface from an external PROM. The configuration file contains the configuration data for the device(s).

Multiple Devices with different configurations can be connected together in a "daisy chain", and a single

#### **SPECIFICATIONS**

| Parameter                     |           | Symbol            | Min                  | Тур  | Max                  | Units  |

|-------------------------------|-----------|-------------------|----------------------|------|----------------------|--------|

| Power Requirements            |           |                   |                      |      |                      |        |

| Supply Voltage                | Digital   | V <sub>DDD</sub>  | 4.5                  | 5.0  | 5.5                  | V      |

|                               | Analog    | V <sub>DDA</sub>  | 4.5                  | 5.0  | 5.5                  | V      |

| Supply Current                | Operating | I <sub>DD</sub>   |                      | TBD  |                      | mA     |

|                               | Low-Power | I <sub>PD</sub>   |                      | TBD  |                      | uA     |

| Power                         | Operating |                   |                      | TBD  |                      | mW     |

| Consumption                   | Low-Power |                   |                      | TBD  |                      | uW     |

| Dynamic Specifications        |           |                   |                      |      |                      |        |

| Operating Ambient Temperature |           | T <sub>A</sub>    | -40                  | 25   | 85.5                 | °C     |

| External Voltage Reference    |           | V <sub>REF</sub>  | 1.5                  | 2.25 | 2.5                  | V      |

| Internal Voltage Reference    |           | I <sub>REF</sub>  | 2.13                 | 2.25 | 2.37                 | V      |

| A/D Converter Resolution      |           | B <sub>A/D</sub>  |                      |      | 12                   | Bits   |

| Clock Frequency               |           | Fc                |                      | 23   |                      | MHz    |

| A/D Converter Conversion Rate |           | Fs                |                      | 480  | TBD                  | KSPS   |

| Analog Frequency Response     |           | BW <sub>A/D</sub> | DC                   | 60K  | TBD                  | Hz     |

| Signal to Noise               |           | S/N               | 54                   |      |                      | dB     |

| Total Harmonic Distortion     |           | THD               |                      | 0.4  | 1                    | %      |

| Interchannel Isolation        |           |                   |                      | 65   |                      | dB     |

| Interchannel Gain Mismatch    |           |                   |                      |      | ±0.5                 | dB     |

| Absolute Gain Error           |           |                   |                      | ± 1  | ± 2                  | %      |

| Gain Drift                    |           |                   |                      | 100  | 200                  | ppm/°C |

| Analog Inputs                 |           |                   |                      |      |                      |        |

| Signal Input Span             |           | V <sub>pp</sub>   | 0.1*V <sub>REF</sub> |      | 1.8*V <sub>REF</sub> | V      |

| Input Capacitance             |           | CIN               |                      |      | 15                   | pF     |

| Input Resistance              |           | R <sub>IN</sub>   | 1M                   |      |                      | Ω      |

| Clock                         |           |                   |                      |      |                      |        |

| Duty Ratio                    |           | CLK               | 45                   | 50   | 55                   | %      |

| Clock High Voltage            |           | V <sub>CLKH</sub> | $0.7 x V_{DDD}$      |      | V <sub>DDD</sub>     | V      |

| Clock Low Voltage             |           | V <sub>CLKL</sub> | 0                    |      | $0.3 x V_{DDD}$      | V      |

| Digital Inputs                |           |                   |                      |      |                      |        |

| Input High Voltage            |           | VINHD             | 2.4                  |      | V <sub>DDD</sub>     | V      |

| Input Low Voltage             |           | VINLD             | 0                    |      | 0.8                  | V      |

| Input Current                 |           | I <sub>IND</sub>  |                      |      | ± 1                  | μA     |

| Input Capacitance             |           | CIND              |                      |      | 10                   | pF     |

| Digital Outputs               |           |                   |                      |      |                      |        |

| Output High Voltage           |           | V <sub>OHD</sub>  | 4.0                  |      | V <sub>DDD</sub>     | V      |

| Output Low Voltage            |           | V <sub>OLD</sub>  | 0                    |      | 0.4                  | V      |

©2000 Systems & Processes Engineering Corporation – SoC Products 101 West Sixth Street, Suite 200, Austin, Texas 78701-2932 Tel: 512/479-7732 Fax: 512/494-0756 e-mail: <u>socproducts.info@spec.com</u> URL: <u>http://www.spec.com</u> REV A1-6 -2-

combined bit stream used to configure the chain of devices.

The PCM configuration data contains the following:

- Serial Port Configuration

- Parallel Port Configuration

- Discrete Port Configuration

- External A/D Port Configuration

- Sample Rate & Configuration

- PCM Coding Configuration

- Bits Per Word

- Words Per Minor Frame

- Minor Frames Per Major Frame

- Assignment of port data to word location in frame(s)

- Time Delay

Configuration software is available for the PC environment.

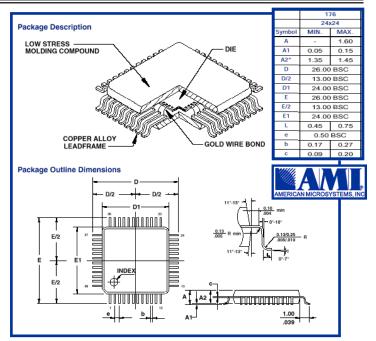

#### PACKAGING

The Thin Quad Flatpack (TQFP) plastic package family is a reduced thickness plastic surface mount package. The 176 lead TQFP packages are constructed using the latest wire bonding and molding technology to provide surface mount packages with a body thickness of 1.0 or 1.4mm. This package finds many applications where size and weight are a critical factor.

The Four Channel PCM IC will be available in die form.

HARDENED SUBMINIATURE TELEMETRY AND SENSOR SYSTEM DATA ACQUISITION CHIPSET