# P4C1024 HIGH SPEED 128K x 8 CMOS STATIC RAM

#### **FEATURES**

- High Speed (Equal Access and Cycle Times)

- 15/17/20/25/35 ns (Commercial)

- 20/25/35/45 ns (Industrial)

- Single 5 Volts ±10% Power Supply

- Easy Memory Expansion Using CE<sub>1</sub>, CE<sub>2</sub> and OE Inputs

- Common Data I/O

- Three-State Outputs

- **■** Fully TTL Compatible Inputs and Outputs

- Advanced CMOS Technology

- Fast t<sub>a</sub>

- Automatic Power Down

- Packages

- -32-Pin 300 mil DIP and SOJ

- -32-Pin 400 mil SOJ

#### DESCRIPTION

The P4C1024 is a 1,048,576-bit high-speed CMOS static RAM organized as 128Kx8. The CMOS memory requires no clocks or refreshing, and has equal access and cycle times. Inputs are fully TTL-compatible. The RAM operates from a single 5V±10% tolerance power supply.

Access times of 15 nanoseconds permit greatly enhanced system operating speeds. CMOS is utilized to reduce power consumption to a low level. The P4C1024 is a member of a family of PACE RAM™ products offering fast access times.

The P4C1024 device provides asynchronous operations with matching access and cycle times. Memory locations are specified on address pins  $A_0$  to  $A_{16}$ . Reading is accomplished by device selection  $(\overline{CE}_1$  low and  $CE_2$  high) and output enabling  $(\overline{OE})$  while write enable  $(\overline{WE})$  remains HIGH. By presenting the address under these conditions, the data in the addressed memory location is presented on the data input/output pins. The input/output pins stay in the HIGH Z state when either  $\overline{CE}_1$  or  $\overline{OE}$  is HIGH or  $\overline{WE}$  or  $CE_2$  is LOW.

Package options for the P4C1024 include 32-pin 300 mil DIP and SOJ packages as well as 400 mil SOJ.

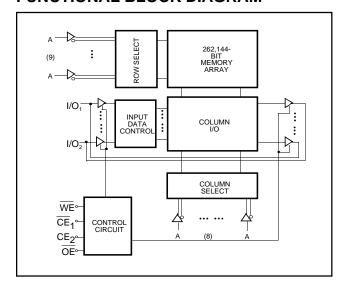

### **FUNCTIONAL BLOCK DIAGRAM**

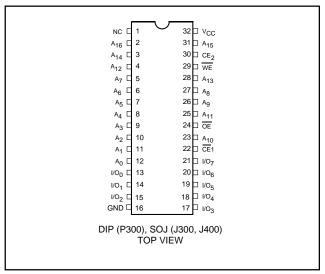

#### PIN CONFIGURATION

Means Quality, Service and Speed

# **RECOMMENDED OPERATING TEMPERATURE & SUPPLY VOLTAGE**

| Temperature Range (Ambient) | Supply Voltage                                           |

|-----------------------------|----------------------------------------------------------|

| Commercial (0°C to 70°C)    | $4.5 \text{V} \le \text{V}_{\text{CC}} \le 5.5 \text{V}$ |

| Industrial (-40°C to 85°C)  | 4.5 ≤ V <sub>cc</sub> ≤ 5.5V                             |

### **MAXIMUM RATINGS**

Stresses greater than those listed can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of this data sheet. Exposure to Maximum Ratings for extended periods can adversely affect device reliability.

| Symbol            | Parameter                                         | Min  | Max                   | Unit |

|-------------------|---------------------------------------------------|------|-----------------------|------|

| V <sub>cc</sub>   | Supply Voltage with Respect to GND                | -0.5 | 7.0                   | V    |

| V <sub>TERM</sub> | Terminal Voltage with Respect to GND (up to 7.0V) | -0.5 | V <sub>cc</sub> + 0.5 | V    |

| T <sub>A</sub>    | Operating Ambient Temperature                     | -55  | 125                   | °C   |

| S <sub>TG</sub>   | Storage Temperature                               | -65  | 150                   | °C   |

| I <sub>OUT</sub>  | Output Current into Low Outputs                   |      | 25                    | mA   |

| I <sub>LAT</sub>  | Latch-up Current                                  | >200 |                       | mA   |

### DC ELECTRICAL CHARACTERISTICS

(Over Recommended Operating Temperature & Supply Voltage)

| Symbol           | Parameter                                                              | Test Conditions                                                                                                                                                                                                                                                     | Min       | Max                   | Unit   |

|------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|--------|

| V <sub>OH</sub>  | Output High Voltage (I/O <sub>0</sub> - I/O <sub>7</sub> )             | $I_{OH} = -4mA, V_{CC} = 4.5V$                                                                                                                                                                                                                                      | 2.4       |                       | V      |

| V <sub>OL</sub>  | Output Low Voltage (I/O <sub>0</sub> - I/O <sub>7</sub> )              | I <sub>OL</sub> = 8 mA<br>I <sub>OL</sub> = 10 mA                                                                                                                                                                                                                   |           | 0.4<br>0.5            | V<br>V |

| V <sub>IH</sub>  | Input High Voltage                                                     |                                                                                                                                                                                                                                                                     | 2.2       | V <sub>cc</sub> + 0.3 | V      |

| V <sub>IL</sub>  | Input Low Voltage                                                      |                                                                                                                                                                                                                                                                     | -0.5      | 0.8                   | V      |

| I <sub>LI</sub>  | Input Leakage Current                                                  | $GND \leq V_{IN} \leq V_{CC}$ Ind'l. Com'l.                                                                                                                                                                                                                         | -10<br>-5 | +10<br>+5             | μΑ     |

| I <sub>LO</sub>  | Output Leakage Current                                                 | $ \begin{aligned} & \frac{\text{GND} \leq \text{V}_{\text{OUT}} \leq \text{V}_{\text{CC}} & \text{Ind'I.} \\ & \overline{\text{CE}}_{\text{1}} \geq \text{V}_{\text{IH}} \text{ or } \text{CE}_{\text{2}} \leq \text{V}_{\text{IL}} & \text{Com'I.} \end{aligned} $ | -10<br>-5 | +10<br>+5             | μΑ     |

| I <sub>os</sub>  | Output Short-Circuit<br>Current                                        | V <sub>OUT</sub> = GND, V <sub>CC</sub> = Max (Single output) not to exceed 30 second duration                                                                                                                                                                      |           | -350                  | mA     |

| I <sub>SB1</sub> | V <sub>cc</sub> Current<br>CMOS Standby Current<br>(CMOS Input Levels) | $V_{CC} = 5.5V$ , $I_{OUT} = 0$ mA<br>$\overline{CE}_1 \ge V_{CC}$ -0.2V, $CE_2 \le 0.2V$                                                                                                                                                                           |           | 20<br>(Standard)      | mA     |

# **CAPACITANCES**

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, f = 1.0 MHz)$

| Symbol           | Parameter          | Test Conditions       | Max | Unit |

|------------------|--------------------|-----------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$         | 8   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 10  | pF   |

# POWER DISSIPATION CHARACTERISTICS VS. SPEED

| Symbol          | Parameter                 | Temperature<br>Range | -15 | -17 | -20 | -25 | -35 | -45 | Unit |

|-----------------|---------------------------|----------------------|-----|-----|-----|-----|-----|-----|------|

| I <sub>cc</sub> | Dynamic Operating Current | Commercial           | 190 | 180 | 160 | 150 | 145 | N/A | mΑ   |

|                 | Dynamic Operating Current | Industrial           | N/A | N/A | 175 | 165 | 160 | 155 | mΑ   |

<sup>\*</sup>Tested with outputs open and all address and data inputs changing at the maximum write-cycle rate. The device is continuously enabled for writing, i.e.,  $CE_2 \ge V_{IH}$  (min),  $\overline{CE}_1$ , and  $\overline{WE} \le V_{IL}$  (max). Switching inputs are 0V and 3V.

### **AC ELECTRICAL CHARACTERISTICS - READ CYCLE**

(Over Recommended Operating Temperature & Supply Voltage)

| Comple ed        | mbol Parameter                      |     | 5   | -1  | 17  | -20 |     | -25 |     | -35 |     | -45 |     | Unit  |

|------------------|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Symbol           | Parameter                           | Min | Max | Oiiit |

| t <sub>RC</sub>  | Read Cycle Time                     | 15  |     | 17  |     | 20  |     | 25  |     | 35  |     | 45  |     | ns    |

| t <sub>AA</sub>  | Address Access Time                 |     | 15  |     | 17  |     | 20  |     | 25  |     | 35  |     | 45  | ns    |

| t <sub>AC</sub>  | Chip Enable Access<br>Time          |     | 15  |     | 17  |     | 20  |     | 25  |     | 35  |     | 45  | ns    |

| t <sub>oh</sub>  | Output Hold from<br>Address Change  | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | ns    |

| t <sub>LZ</sub>  | Chip Enable to<br>Output in Low Z   | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | ns    |

| t <sub>HZ</sub>  | Chip Disable to<br>Output in High Z |     | 8   |     | 9   |     | 9   |     | 11  |     | 15  |     | 20  | ns    |

| t <sub>OE</sub>  | Output Enable Low to Data Valid     |     | 6   |     | 7   |     | 9   |     | 10  |     | 15  |     | 20  | ns    |

| t <sub>OLZ</sub> | Output Enable Low to Low Z          | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>OHZ</sub> | Output Enable High to High Z        |     | 6   |     | 7   |     | 9   |     | 11  |     | 15  |     | 20  | ns    |

| t <sub>PU</sub>  | Chip Enable to<br>Power Up Time     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>PD</sub>  | Chip Disable to<br>Power Down Time  |     | 12  |     | 15  |     | 20  |     | 20  |     | 20  |     | 25  | ns    |

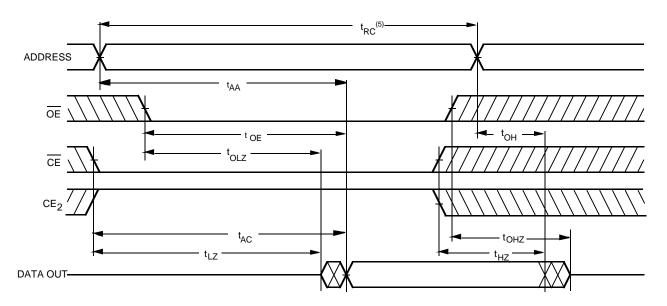

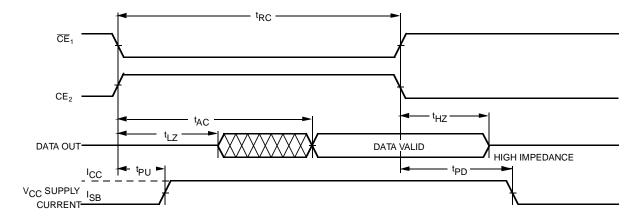

# READ CYCLE NO. 1 (OE CONTROLLED)(1)

### NOTES:

- 1.  $\overline{\text{WE}}$  is HIGH for READ cycle.

- 2.  $\overline{\text{CE}}_1$  and  $\overline{\text{OE}}$  is LOW and  $\text{CE}_2$  is HIGH for read cycle.

- ADDRESS must be valid prior to, or coincident with later of CE<sub>1</sub> transition LOW or CE<sub>2</sub> transition HIGH.

- 4. Transition is measured  $\pm$  200 mV from steady state voltage prior to change, with loading as specified in Figure 1. This parameter is sampled and not 100% tested.

- READ Cycle Time is measured from the last valid address to the first transitioning address.

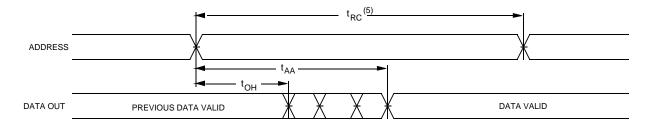

# **READ CYCLE NO. 2 (ADDRESS CONTROLLED)**

# READ CYCLE NO. 3 (CE-CONTROLLED)

# **AC CHARACTERISTICS - WRITE CYCLE**

(Over Recommended Operating Temperature & Supply Voltage)

| Symbol          | Parameter                           | -1  | 15  | -1  | 17  | -2  | 20  | -25 |     | -35 |     | -45 |     | Unit  |

|-----------------|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Syllibol        | Farameter                           | Min | Max | Oilit |

| t <sub>wc</sub> | Write Cycle Time                    | 15  |     | 17  |     | 20  |     | 25  |     | 35  |     | 45  |     | ns    |

| t <sub>cw</sub> | Chip Enable Time to End of Write    | 12  |     | 13  |     | 15  |     | 18  |     | 22  |     | 30  |     | ns    |

| t <sub>AW</sub> | Address Valid to<br>End of Write    | 12  |     | 13  |     | 15  |     | 20  |     | 25  |     | 35  |     | ns    |

| t <sub>AS</sub> | Address Set-up<br>Time              | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>wP</sub> | Write Pulse Width                   | 12  |     | 12  |     | 15  |     | 18  |     | 22  |     | 25  |     | ns    |

| t <sub>AH</sub> | Address Hold Time                   | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>DW</sub> | Data Valid to End of Write          | 7   |     | 7   |     | 8   |     | 10  |     | 15  |     | 20  |     | ns    |

| t <sub>DH</sub> | Data Hold Time                      | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>wz</sub> | Write Enable to<br>Output in High Z |     | 8   |     | 8   |     | 10  |     | 11  |     | 15  |     | 18  | ns    |

| t <sub>ow</sub> | Output Active from<br>End of Write  | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | 3   |     | ns    |

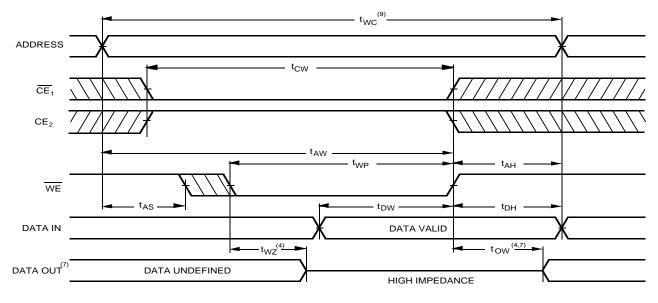

# WRITE CYCLE NO. 1 (WE CONTROLLED)(6)

#### Notes:

- 6.  $\overline{\text{CE}}_1$  and  $\overline{\text{WE}}$  are LOW and  $\text{CE}_2$  is HIGH for WRITE cycle.

- 7. OE is LOW for this WRITE cycle to show twz and tow.

- 8. If  $\overline{\text{CE}}_1$  goes HIGH or CE, goes LOW simultaneously with  $\overline{\text{WE}}$  HIGH, the output remains in a high impedance state.

- 9. Write Cycle Time is measured from the last valid address to the first transitioning address.

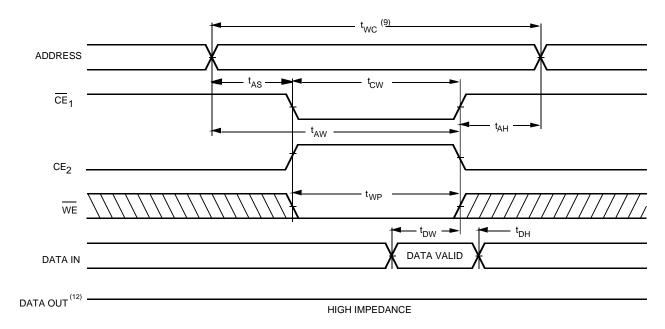

# TIMING WAVEFORM OF WRITE CYCLE NO.2 (CE CONTROLLED)(6)

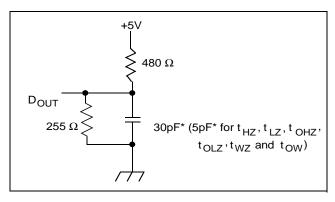

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise and Fall Times     | 3ns                 |

| Input Timing Reference Level  | 1.5V                |

| Output Timing Reference Level | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

### TRUTH TABLE

| Mode                      | <u>CE</u> ₁ | CE <sub>2</sub> | ŌĒ | WE | 1/0              | Power   |

|---------------------------|-------------|-----------------|----|----|------------------|---------|

| Standby                   | Н           | Х               | Х  | Х  | High Z           | Standby |

| Standby                   | Х           | L               | Х  | Χ  | High Z           | Standby |

| D <sub>OUT</sub> Disabled | L           | Н               | Н  | Н  | High Z           | Active  |

| Read                      | L           | Н               | L  | Н  | D <sub>OUT</sub> | Active  |

| Write                     | L           | Н               | Х  | L  | High Z           | Active  |

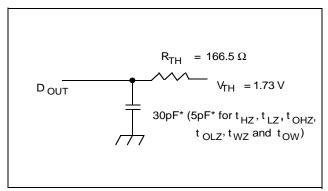

Figure 1. Output Load

### Note:

Because of the ultra-high speed of the P4C1024, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the  $V_{\rm CC}$  and ground planes directly up to the contactor fingers. A 0.01  $\mu F$  high frequency capacitor is also required between  $V_{\rm CC}$  and ground.

Figure 2. Thevenin Equivalent

To avoid signal reflections, proper termination must be used; for example, a  $50\Omega$  test environment should be terminated into a  $50\Omega$  load with 1.73V (Thevenin Voltage) at the comparator input, and a  $116\Omega$  resistor must be used in series with  $D_{\text{OUT}}$  to match  $166\Omega$  (Thevenin Resistance).

<sup>\*</sup> including scope and test fixture.

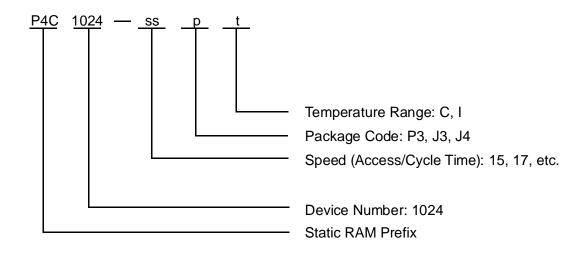

# **PACKAGE SUFFIX**

| Package<br>Suffix | Description                        |

|-------------------|------------------------------------|

| P3                | Plastic DIP, 300 mil wide standard |

| J3                | Plastic SOJ, 300 mil wide standard |

| J4                | Plastic SOJ, 400 mil wide standard |

# **TEMPERATURE RANGE SUFFIX**

| Temperature Range Suffix | Description                                  |

|--------------------------|----------------------------------------------|

| С                        | Commercial Temperature Range, 0°C to +70°C   |

| I                        | Industrial Temperature Range, -40°C to +85°C |

### **ORDERING INFORMATION**

Performance Semiconductor's part numbering scheme is as follows:

# **SELECTION GUIDE**

The P4C1024 is available in the following temperature, speed and package options.

| Temperature               | Package                                               | Speed (ns)                 |                            |                            |                            |                            |  |  |  |

|---------------------------|-------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|--|--|--|

| Range                     | . aonago                                              | -15                        | -17                        | -20                        | -25                        | -35                        |  |  |  |

| Commercial<br>Temperature | Plastic DIP 300<br>Plastic SOJ 300<br>Plastic SOJ 400 | -15P3C<br>-15J3C<br>-15J4C | -17P3C<br>-17J3C<br>-17J4C | -20P3C<br>-20J3C<br>-20J4C | -25P3C<br>-25J3C<br>-25J4C | -35P3C<br>-35J3C<br>-35J4C |  |  |  |

| Industrial<br>Temperature | Plastic DIP 300<br>Plastic SOJ 300<br>Plastic SOJ 400 | N/A<br>N/A<br>N/A          | N/A<br>N/A<br>N/A          | -20P3I<br>-20J3I<br>-20J4I | -25P3I<br>-25J3I<br>-25J4I | -35P3I<br>-35J3I<br>-35J4I |  |  |  |

N/A = Not Available