### **Features**

- 6.6 SPEC int 95, 5.5 SPECfp95 @ 266 MHz (estimated)

- Superscalar 603e core

- Integer unit (IU), floating-point unit (FPU) (user enabled or disabled), load/ store unit (LSU), system register unit (SRU), and a branch processing unit (BPU).

- 16-Kbyte instruction cache

- 16-Kbyte data cache

- Lockable L1 caches-entire cache or on a per-way basis up to 3 of 4 ways.

- Dynamic power management.

- High-bandwidth bus (32/64 bits data bus) to DRAM.

- Supports 1-Mbyte to 1-Gbyte DRAM memory.

- 32-bit PCI interface operating up to 66 MHz.

- PCI 2.1-compliant, 5.0 V tolerance

- Fint MAX = 250 MHz (tbc).

- FBus MAX = 66 MHz (tbc)

# **Description**

The PC8240 combines a PowerPC<sup>TM</sup> 603e core microprocessor with a PCI bridge. The PC8240's PCI support will allow system designers to rapidly design systems using peripherals already designed for PCI and the other standard interfaces. The PC8240 also integrates a high-performance memory controller which supports various types of DRAM and ROM. The PC8240 is the first of a family of products that provide system level support for industry standard interfaces with a PowerPC microprocessor core.

The peripheral logic integrates a PCI bridge, memory controller, DMA controller, EPIC interrupt controller,  $I_2O$  controller, and an  $I^2C$  controller. The 603e core is a full-featured, high-performance processor with floating-point support, memory management, 16-Kbyte instruction cache, 16-Kbyte data cache, and power management features. The integration reduces the overall packaging requirements and the number of discrete devices required for an embedded system.

The PC8240 contains an internal peripheral logic bus that interfaces the 603e core to the peripheral logic. The core can operate at a variety of frequencies, allowing the designer to trade off performance for power consumption. The 603e core is clocked from a separate PLL, which is referenced to the peripheral logic PLL. This allows the microprocessor and the peripheral logic block to operate at different frequencies, while maintaining a synchronous bus interface. The interface uses a 64- or 32-bit data bus (depending on memory data bus width) and a 32-bit address bus along with control signals that enable the interface between the processor and peripheral logic to be optimized for performance. PCI accesses to the PC8240's memory space are passed to the processor bus for snooping purposes when snoop mode is enabled.

The PC8240's features serve a variety of embedded applications. In this way, the 603e core and peripheral logic remain general-purpose. The PC8240 can be used as either a PCI host or an agent controller.

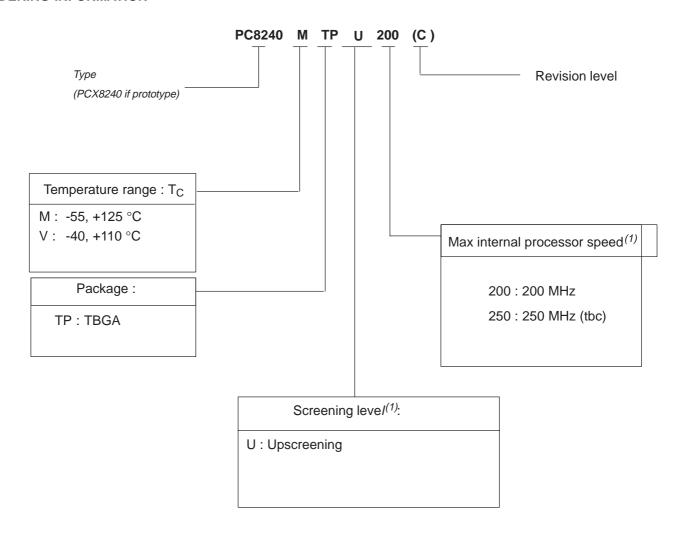

### SCREENING/QUALITY/PACKAGING

This product is manufactured in full compliance with:

- Upscreening based upon TCS standards.

- Full military temperature range

$$(T_c = 55^{\circ}C, T_c = +125^{\circ}C)$$

Industrial temperature range

$$(T_c = -40^{\circ}C, T_c = +110^{\circ}C)$$

- Core power supply :

- . 2.5 +/- 5 % V (L-Spec for 200 MHz)

- . 2.50 V to 2.75 V (R-Spec for 250 MHz) (tbc)

- I/O power supply: 3.0 to 3.6 V

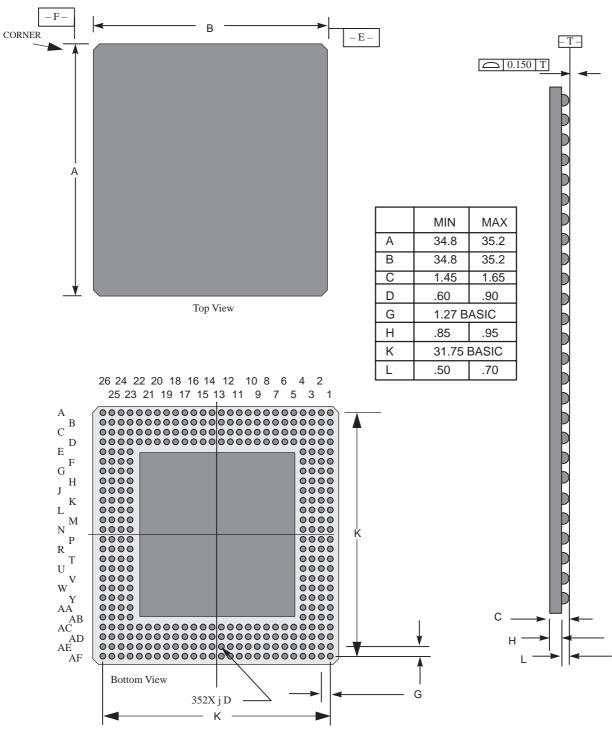

- 352 Tape Ball Grid Array (TBGA).

TP suffix

TBGA352

Tape Ball Grid Array

PC8240 Integrated Processor Family

Preliminary specification alpha SITE

July 2000

# **SUMMARY**

| A. GENERAL DESCRIPTION                                               | 3    |

|----------------------------------------------------------------------|------|

| 1. BLOCK DIAGRAM                                                     |      |

| 2. PINOUT LISTINGS                                                   | 4    |

| B. DETAILED SPECIFICATIONS                                           | 9    |

| 1. SCOPE                                                             | 9    |

| 2. APPLICABLE DOCUMENTS                                              | 9    |

| 3. REQUIREMENTS                                                      | 9    |

| 3.1. General                                                         | 9    |

| 3.2. Design and construction                                         |      |

| 3.2.1. Terminal connections                                          |      |

| 3.3. Absolute maximum ratings                                        |      |

| 3.4. Recommended Operating Conditions                                |      |

| 3.5. Thermal information                                             |      |

| 3.5.1. Thermal characteristics                                       |      |

| 3.5.2. Thermal Management Information                                |      |

| 3.5.4. Heat Sink Selection Example                                   |      |

| 3.6. Power consideration                                             |      |

| 3.7. Marking                                                         |      |

| 4. ELECTRICAL CHARACTERISTICS                                        |      |

| 4.1. Static characteristics                                          |      |

| 4.2. Dynamic Electrical Characteristics                              |      |

| 4.2.1. Clock AC Specifications                                       |      |

| 4.2.2. Input AC Timing Specifications                                |      |

| 4.2.3. Output AC Timing Specification                                | . 25 |

| 4.2.4. I2C AC Timing Specifications                                  | . 28 |

| 4.2.5. EPIC Serial Interrupt Mode AC Timing Specifications           |      |

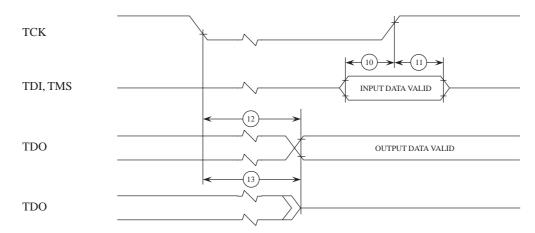

| 4.2.6. IEEE 1149.1 (JTAG) AC Timing Specifications                   |      |

| 5. PREPARATION FOR DELIVERY                                          |      |

| 5.1. Packaging                                                       |      |

| 5.2. Certificate of compliance                                       |      |

| 6. HANDLING                                                          |      |

| 6.1. Package description                                             |      |

| 6.1.1. Package Parameters for the PC8240                             |      |

| 6.1.2. Pin Assignments and Package Dimensions 6.2. PLL Configuration |      |

| 6.3. System Design Information                                       |      |

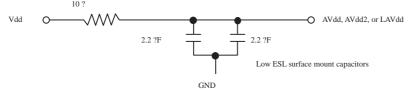

| 6.3.1. PLL Power Supply Filtering                                    |      |

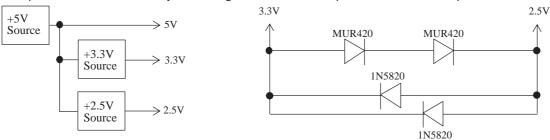

| 6.3.2. Power Supply Voltage Sequencing                               |      |

| 6.3.3. Power Supply Sizing                                           |      |

| 6.3.4. Decoupling Recommendations                                    |      |

| 6.3.5. Connection Recommendations                                    |      |

| 6.3.6. Pull-up/Pull-down Resistor Requirements                       | . 40 |

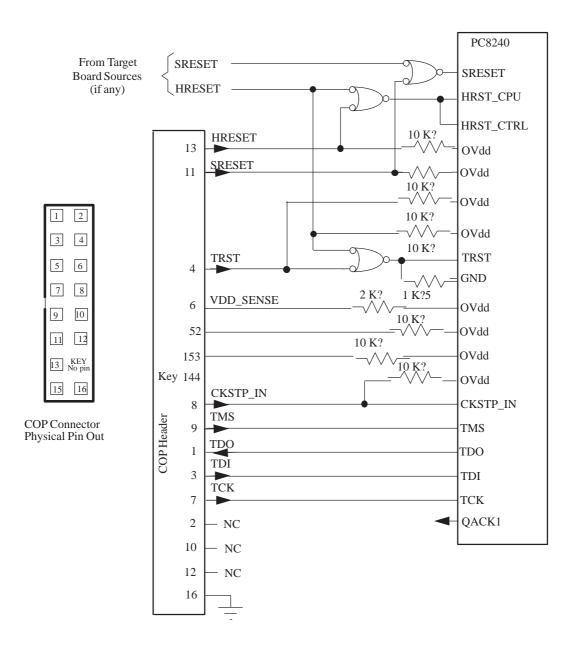

| 6.3.7. JTAG Configuration Signals                                    | . 40 |

| 7. DEFINITIONS                                                       | . 42 |

| 8. DIFFERENCES WITH COMMERCIAL PART                                  | . 42 |

| 9. ORDERING INFORMATION                                              | . 43 |

# A. GENERAL DESCRIPTION

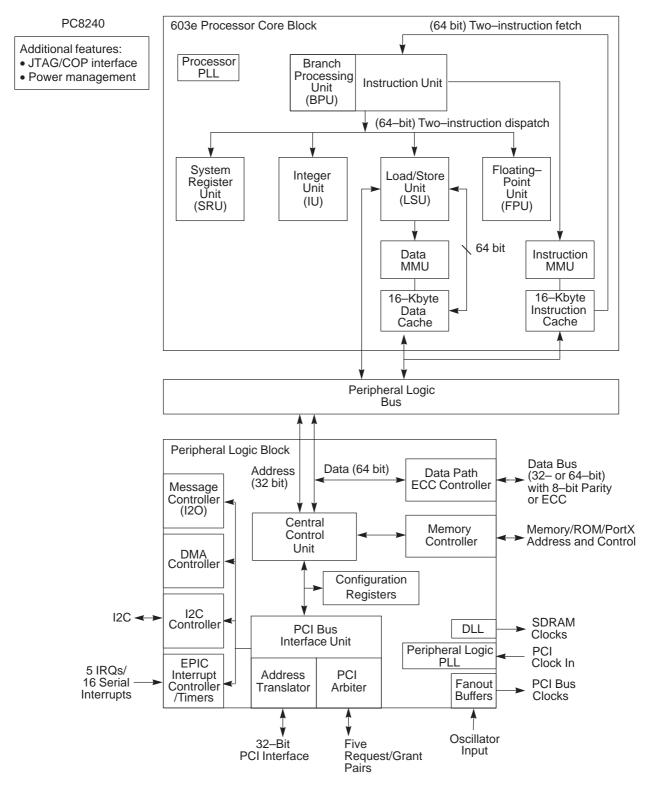

### 1. BLOCK DIAGRAM

The PC8240 integrated processor is comprised of a peripheral logic block and a 32-bit superscalar PowerPC 603e core, as shown in Figure 1.

Figure 1: Block Diagram

# 2. PINOUT LISTINGS

Table 1 provides the pinout listing for the PC8240, 352 TBGA package.

Table 1. PC8240 Pinout Listing

| Signal Name      | Package Pin Number                                                                                                                          | Pin Type     | Power<br>Supply | Output Driver Type | Notes   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------------|---------|

|                  | PCI Interfac                                                                                                                                | ce Signals   |                 |                    |         |

| C/BE[0-3]        | A25 F23 K23 P25                                                                                                                             | I/O          | OVdd            | DRV_PCI            | 6,15    |

| DEVSEL           | H26                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15    |

| FRAME            | J24                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15    |

| IRDY             | K25                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15    |

| LOCK             | J26                                                                                                                                         | Input        | OVdd            | _                  | 8       |

| AD[0-31]         | C22 D22 B22 B23 D19 B24 A24<br>B26 A26 C26 D25 D26 E23 E25<br>E26 F24 L26 L25 M25 M26 N23<br>N25 N26 R26 R25 T26 T25 U23<br>U24 U26 U25 V25 | I/O          | OVdd            | DRV_PCI            | 6,15    |

| PAR              | G25                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 15      |

| <u>GNT</u> [0-3] | V26 W23 W24 W25                                                                                                                             | Output       | OVdd            | DRV_PCI            | 6,15    |

| GNT4/DA5         | W26                                                                                                                                         | Output       | OVdd            | DRV_PCI            | 7,15    |

| REQ[0-3]         | AB26 AA25 AA26 Y25                                                                                                                          | Input        | OVdd            | _                  | 6,12    |

| REQ4/DA4         | Y26                                                                                                                                         | Input        | OVdd            | _                  | 12      |

| PERR             | G26                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15,18 |

| SERR             | F26                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15,16 |

| STOP             | H25                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15    |

| TRDY             | K26                                                                                                                                         | I/O          | OVdd            | DRV_PCI            | 8,15    |

| ĪNTA             | AC26                                                                                                                                        | Output       | OVdd            | DRV_PCI            | 15,16   |

| IDSEL            | P26                                                                                                                                         | Input        | OVdd            | _                  | _       |

|                  | Memory Inter                                                                                                                                | face Signals |                 |                    |         |

| MDL[0-31]        | AD17 AE17 AE15 AF15 AC14<br>AE13 AF13 AF12 AF11 AF10 AF9<br>AD8 AF8 AF7 AF6 AE5 B1 A1 A3<br>A4 A5 A6 A7 D7 A8 B8 A10 D10<br>A12 B11 B12 A14 | I/O          | Gvdd            | DRV_MEM_DATA       | 5,6,13  |

| MDH[0-31]        | AC17 AF16 AE16 AE14 AF14<br>AC13 AE12 AE11 AE10 AE9 AE8<br>AC7 AE7 AE6 AF5 AC5 E4 A2 B3<br>D4 B4 B5 D6 C6 B7 C9 A9 B10<br>A11 A13 B13 A15   | I/O          | Gvdd            | DRV_MEM_DATA       | 6,13    |

| Signal Name     | ame Package Pin Number                 |             | Power<br>Supply | Output Driver Type | Notes   |

|-----------------|----------------------------------------|-------------|-----------------|--------------------|---------|

| CAS/DQM[0-7]    | AB1 AB2 K3 K2 AC1 AC2 K1 J1            | Output      | Gvdd            | DRV_MEM_ADDR       | 6       |

| RAS/CS[0-7]     | Y4 AA3 AA4 AC4 M2 L2 M1 L1             | Output      | Gvdd            | DRV_MEM_ADDR       | 6       |

| FOE             | H1                                     | I/O         | Gvdd            | DRV_MEM_ADDR       | 3,4     |

| RCS0            | N4                                     | I/O         | Gvdd            | DRV_MEM_ADDR       | 3,4     |

| RCS1            | N2                                     | Output      | Gvdd            | DRV_MEM_ADDR       |         |

| SDMA[11 - 0]    | N1 R1 R2 T1 T2 U4 U2 U1 V1 V3<br>W1 W2 | Output      | Gvdd            | DRV_MEM_ADDR       | 6,14    |

| SDMA12/SDBA1    | P1                                     | Output      | Gvdd            | DRV_MEM_ADDR       | 14      |

| SDBA0           | P2                                     | Output      | Gvdd            | DRV_MEM_ADDR       | _       |

| PAR[0-7]        | AF3 AE3 G4 E2 AE4 AF4 D2 C2            | I/O         | Gvdd            | DRV_MEM_DATA       | 6,13,14 |

| SDRAS           | AD1                                    | Output      | Gvdd            | DRV_MEM_ADDR       | 3       |

| SDCAS           | AD2                                    | Output      | Gvdd            | DRV_MEM_ADDR       | 3       |

| CKE             | H2                                     | Output      | Gvdd            | DRV_MEM_ADDR       | 3,4     |

| WE              | AA1                                    | Output      | Gvdd            | DRV_MEM_ADDR       | _       |

| ĀS              | Y1                                     | Output      | Gvdd            | DRV_MEM_ADDR       | 3,4     |

|                 | EPIC Contr                             | rol Signals |                 |                    |         |

| IRQ_0/S_INT     | C19                                    | Input       | Ovdd            | _                  | _       |

| IRQ_1/S_CLK     | B21                                    | I/O         | Ovdd            | DRV_PCI            | _       |

| IRQ_2/S_RST     | AC22                                   | I/O         | Ovdd            | DRV_PCI            | _       |

| IRQ_3/S_FRAME   | AE24                                   | I/O         | Ovdd            | DRV_PCI            | _       |

| IRQ_4/ L_INT    | A23                                    | I/O         | Ovdd            | DRV_PCI            | _       |

|                 | I <sup>2</sup> C Contro                | ol Signals  |                 |                    |         |

| SDA             | AE20                                   | I/O         | Ovdd            | DRV_STD            | 10,16   |

| SCL             | AF21                                   | I/O         | Ovdd            | DRV_STD            | 10,16   |

|                 | Clock Ou                               | t Signals   | 1               | I                  |         |

| PCI_CLK [0-3]   | AC25 AB25 AE26 AF25                    | Output      | GVdd            | DRV_PCI_CLK        | 6       |

| PCI_CLK4/DA3    | AF26                                   | Output      | GVdd            | DRV_PCI_CLK        | _       |

| PCI_SYNC_OUT    | AD25                                   | Output      | GVdd            | DRV_PCI_CLK        | _       |

| PCI_SYNC_IN     | AB23                                   | Input       | GVdd            | _                  | _       |

| SDRAM_CLK [0-3] | D1 G1 G2 E1                            | Output      | GVdd            | DRV_MEM_ADDR       | 6       |

| Signal Name               | Package Pin Number  | Pin Type       | Power<br>Supply | Output Driver Type | Notes    |  |  |  |

|---------------------------|---------------------|----------------|-----------------|--------------------|----------|--|--|--|

| SDRAM_SYNC_OUT            | C1                  | Output         | GVdd            | DRV_MEM_ADDR       | _        |  |  |  |

| SDRAM_SYNC_IN             | НЗ                  | Input          | GVdd            | _                  | _        |  |  |  |

| CKO/DA1                   | B15                 | Output         | Ovdd            | DRV_STD            | _        |  |  |  |

| OSC_IN                    | AD21                | Input          | Ovdd            | _                  | _        |  |  |  |

| Miscellaneous Signals     |                     |                |                 |                    |          |  |  |  |

| HRST_CTRL                 | A20                 | Input          | OVdd            | _                  | _        |  |  |  |

| HRST_CPU                  | A19                 | Input          | OVdd            | _                  | _        |  |  |  |

| MCP                       | A17                 | Output         | OVdd            | DRV_STD            | 3,4,17   |  |  |  |

| NMI                       | D16                 | Input          | OVdd            | _                  | _        |  |  |  |

| SMI                       | A18                 | Input          | OVdd            | _                  | 10       |  |  |  |

| SRESET                    | B16                 | Input          | OVdd            | _                  | 10       |  |  |  |

| TBEN                      | B14                 | Input          | OVdd            | _                  | 10       |  |  |  |

| QACK/DA0                  | F2                  | Output         | OVdd            | DRV_STD            | 3,4      |  |  |  |

| CHKSTOP_IN                | D14                 | Input          | OVdd            | _                  | 10       |  |  |  |

| MAA[0-2]                  | AF2 AF1 AE1         | Output         | GVdd            | DRV_MEM_DATA       | 3,4,6    |  |  |  |

| MIV                       | A16                 | Output         | OVdd            | DRV_STD            | _        |  |  |  |

| PMAA[0-2]                 | AD18 AF18 AE19      | Output         | OVdd            | DRV_STD            | 3,4,6,15 |  |  |  |

|                           | Test/Configur       | ration Signals |                 | ,                  | ı        |  |  |  |

| PLL_CFG[0-4]/<br>DA[10-6] | A22 B19 A21 B18 B17 | Input          | OVdd            | _                  | 4,6      |  |  |  |

| TEST[0-1]                 | AD22 B20            | Input          | OVdd            | _                  | 1,6,9    |  |  |  |

| TEST2                     | Y2                  | Input          | GVdd            | _                  | 11       |  |  |  |

| TEST3                     | AF20                | Input          | OVdd            | _                  | 10       |  |  |  |

| TEST4                     | AC18                | I/O            | OVdd            | DRV_STD            | 10       |  |  |  |

| тск                       | AF22                | Input          | OVdd            | _                  | 9,12     |  |  |  |

| TDI                       | AF23                | Input          | OVdd            | _                  | 9,12     |  |  |  |

| TDO                       | AC21                | Output         | OVdd            | DRV_PCI            | _        |  |  |  |

| TMS                       | AE22                | Input          | OVdd            | _                  | 9,12     |  |  |  |

| TRST                      | AE23                | Input          | OVdd            | _                  | 9,12     |  |  |  |

| Signal Name | Package Pin Number                                                                                                                                                                                                                | Pin Type                                       | Power<br>Supply | Output Driver Type | Notes |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|--------------------|-------|--|--|--|--|--|--|

|             | Power and Ground Signals                                                                                                                                                                                                          |                                                |                 |                    |       |  |  |  |  |  |  |

| GND         | AA2 AA23 AC12 AC15 AC24 AC3<br>AC6 AC9 AD11 AD14 AD16<br>AD19 AD23 AD4 AE18 AE2 AE21<br>AE25 B2 B25 B6 B9 C11 C13<br>C16 C23 C4 C8 D12 D15 D18<br>D21 D24 D3 F25 F4 H24 J25 J4<br>L24 L3 M23 M4 N24 P3 R23 R4<br>T24 T3 V2 V23 W3 | Ground 52 terminals                            | _               | _                  | _     |  |  |  |  |  |  |

| LVdd        | AC20 AC23 D20 D23 G23 P23<br>Y23                                                                                                                                                                                                  | Reference<br>voltage<br>3.3v,5.0v              | LVdd            | _                  | _     |  |  |  |  |  |  |

| GVdd        | AB3 AB4 AC10 AC11 AC8 AD10<br>AD13 AD15 AD3 AD5 AD7 C10<br>C12 C3 C5 C7 D13 D5 D9 E3 G3<br>H4 K4 L4 N3 P4 R3 U3 V4 Y3                                                                                                             | Power for<br>Memory<br>Drivers<br>2.5v,3.3v    | GVdd            | _                  | _     |  |  |  |  |  |  |

| Ovdd        | AB24 AD20 AD24 C14 C20 C24<br>E24 G24 J23 K24 M24 P24 T23<br>Y24                                                                                                                                                                  | PCI / Stnd<br>3.3v                             | Ovdd            | _                  | _     |  |  |  |  |  |  |

| Vdd         | AA24 AC16 AC19 AD12 AD6<br>AD9 C15 C18 C21 D11 D8 F3<br>H23 J3 L23 M3 R24 T4 V24 W4                                                                                                                                               | Power for<br>Core 2.5v                         | Vdd             | _                  | _     |  |  |  |  |  |  |

| LAVdd       | D17                                                                                                                                                                                                                               | Power for<br>DLL 2.5v                          | LAVdd           | _                  | _     |  |  |  |  |  |  |

| AVdd        | C17                                                                                                                                                                                                                               | Power for<br>PLL (CPU<br>Core Logic)<br>2.5v   | AVdd            | _                  | _     |  |  |  |  |  |  |

| AVdd2       | AF24                                                                                                                                                                                                                              | Power for<br>PLL<br>(Peripheral<br>Logic) 2.5v | AVdd2           | _                  | _     |  |  |  |  |  |  |

|             | Manufacto                                                                                                                                                                                                                         | uring Pins                                     |                 |                    |       |  |  |  |  |  |  |

| DA2         | C25                                                                                                                                                                                                                               | I/O                                            | OVdd            | DRV_PCI            | 2     |  |  |  |  |  |  |

| DA[11-13]   | AD26 AF17 AF19                                                                                                                                                                                                                    | I/O                                            | OVdd            | DRV_PCI            | 2,6   |  |  |  |  |  |  |

| DA[14-15]   | F1 J2                                                                                                                                                                                                                             | I/O                                            | GVdd            | DRV_MEM_ADDR       | 2,6   |  |  |  |  |  |  |

- 1 Place pull-up resistors of 120 Ohms or less on the TEST[0–1] pins.

- 2 Treat these pins as No Connects unless using debug address functionality.

- 3 This pin has an internal pull-up resistor which is enabled only when the PC8240 is in the reset state. The value of the internal pull-up resistor is not guaranteed, but is sufficient to insure that a '1' is read into configuration bits during reset.

- 4 This pin is a reset configuration pin.

- 5 DL[0] is a reset configuration pin and has an internal pull-up resistor which is enabled only when the PC8240 is in the reset state. The value of the internal pull-up resistor is not guaranteed, but is sufficient to insure that a '1' is read into configuration bits during reset

- 6 Multi-pin signals such as AD[0–31] or DL[0–31] have their physical package pin numbers listed in order corresponding to the signal names. Ex: AD0 is on pin C22, AD1 is on pin D22,... AD31 is on pin V25.

- 7 GNT4 is a reset configuration pin and has an internal pull-up resistor which is enabled only when the PC8240 is in the reset state. The value of the internal pull-up resistor is not guaranteed, but is sufficient to insure that a '1' is read into configuration bits during reset.

- 8 Recommend a weak pull-up resistor (2K 10K Ohm) be placed on this PCI control pin to LVdd.

- 9 V<sub>IH</sub> and V<sub>IL</sub> for these signals are the same as the PCI V<sub>IH</sub> and V<sub>IL</sub> entries in Table ". DC Electrical Specifications".

- 10 Recommend a weak pull-up resistor (2K 10K Ohm) be placed on this pin to OVdd.

- 11 Recommend a weak pull-up resistor (2K 10K Ohm) be placed on this pin to GVdd.

- 12 This pin has an internal pull-up resistor; the value of the internal pull-up resistor is not guaranteed, but is sufficient to prevent unused inputs from floating.

- 13 Output Valid specifications for this pin are memory interface mode dependent (Registered or Flow-through), see Table ". Output AC Timing Specifications".

- 14 Non-DRAM Access Output Valid specification applies to this pin during non-DRAM accesses, see specification 12b3 in Table "Output AC Timing Specifications".

- 15 This pin is affected by programmable PCI\_HOLD\_DEL parameter, see Section AUCUN LIEN "PCI Signal Output Hold Timing".

- 16 This pin is an open drain signal.

- 17 This pin can be programmed to be driven (default) or can be programmed to be open drain; see PMCR2 register description in the MOTOROLA PC8240 User's Manual for details.

- 18 This pin is a Sustained Tri-State pin as defined by the PCI Local Bus Specification.

# **B. DETAILED SPECIFICATIONS**

#### 1. SCOPE

This drawing describes the specific requirements for the PC8240 processor, in compliance with TCS standard screening.

#### 2. APPLICABLE DOCUMENTS

1) MIL-STD-883: Test methods and procedures for electronics.

2) MIL-PRF-38535: General specifications for microcircuits.

#### 3. REQUIREMENTS

#### 3.1. General

The microcircuits are in accordance with the applicable documents and as specified herein.

#### 3.2. Design and construction

#### 3.2.1. Terminal connections

The terminal connections are shown Table 1 (§ A. GENERAL DESCRIPTION).

### 3.3. Absolute maximum ratings

Absolute maximum ratings are stress rating only and functional operation at the maximum is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

Table 2. Absolute maximum rating for the PC8240

| Characteristic <sup>1</sup>                    | Symbol           | Range        | Unit |

|------------------------------------------------|------------------|--------------|------|

| Supply Voltage - CPU Core and Peripheral Logic | V <sub>dd</sub>  | -0.3 to 2.75 | V    |

| Supply Voltage - Memory Bus Drivers            | GVdd             | -0.3 to 3.6  | V    |

| Supply Voltage - PCI and Standard I/O Buffers  | OVdd             | -0.3 to 3.6  | V    |

| Supply Voltage - PLLs and DLL                  | AVdd/AVdd2/LAVdd | -0.3 to 2.75 | V    |

| Supply Voltage - PCI Reference                 | V <sub>IN</sub>  | -0.3 to 3.6  | V    |

| Input Voltage <sup>2</sup>                     | LVdd             | -0.3 to 5.4  | V    |

| Storage Temperature Range                      | T <sub>STG</sub> | -55 to 150   | С    |

- 1 Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage of the device.

- 2 PCI inputs with LVdd = 5 V 5 % V DC may be correspondingly stressed at voltages exceeding LVdd + 0.5 V DC.

### 3.4. Recommended Operating Conditions

**Table 3. Recommended Operating Conditions**

| Characteristic <sup>1</sup>         |                    | Symbol          | Recommended<br>Value | Unit | Notes |

|-------------------------------------|--------------------|-----------------|----------------------|------|-------|

| Supply Voltage                      |                    | Vdd             | 2.5 ± 5 %            | V    | 4,6   |

| I/O Buffer supply for               | PCI and Standard   | OVdd            | 3.3 ± 0.3            | V    | 6     |

| Supply Voltages for I               | Memory Bus Drivers | GVdd            | 3.3 ± 5%             | V    | 8     |

|                                     |                    |                 | 2.5 ± 5%             | V    | 8     |

| PLL Supply Voltage - CPU Core Logic |                    | AVdd            | 2.5 ± 5 %            | V    | 4,6   |

| PLL Supply Voltage                  | - Peripheral Logic | AVdd2           | 2.5 ± 5 %            | V    | 4,7   |

| DLL Supply Voltage                  |                    | LAVdd           | 2.5 ± 5 %            | V    | 4,7   |

| PCI Reference                       |                    | LVdd            | 5.0 ± 5 %            | V    | 9,10  |

|                                     |                    |                 | 3.3 ± 0.3            | V    | 9,10  |

| Input Voltage                       | PCI Inputs         | V <sub>IN</sub> | 0 to 3.6 or 5.75     | V    | 2,3   |

| All Other Inputs                    |                    |                 | 0 to 3.6             | V    | 5     |

| Operating Temperate                 | ure                | T <sub>C</sub>  | -55 to +125          | С    |       |

### Note:

- 1 These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

- 2 PCI pins are designed to withstand LVdd + 0.5 V dc when LVdd is connected to a 5.0V dc power supply.

- 3 PCI pins are designed to withstand LVdd + 0.5 V dc when LVdd is connected to a 3.3 V dc power supply.

- 4 Voltage specification is 2.50 V to 2.70 V for R-Spec (250 MHz)

### Cautions:

- 5 Input voltage (V<sub>IN</sub>) must not be greater than the supply voltage (Vdd/AVdd/AVdd2/LAVdd) by more than 2.5 V at all times including during power-on reset.

- 6 OVdd must not exceed Vdd/AVdd/AVdd2/LAVdd by more than 1.8 V at any time including during power-on reset.

- 7 Vdd/AVdd/AVdd2/LAVdd must not exceed OVdd by more than 0.6 V at any time including during power-on reset.

- 8 GVdd must not exceed Vdd/AVdd/AVdd2/LAVdd by more than 1.8 V at any time including during power-on reset.

- **9** LVdd must not exceed Vdd/AVdd/AVdd2/LAVdd by more than 5.4 V at any time including during power-on reset.

- 10 LVdd must not exceed OVdd by more than 3.6 V at any time including during power-on reset.

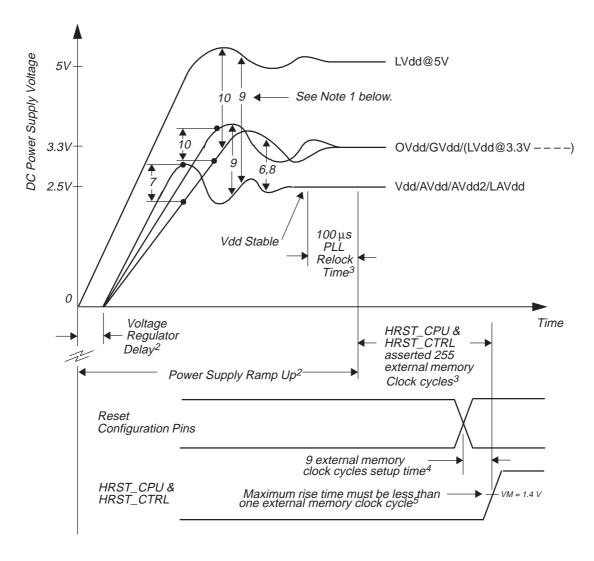

- 1 Numbers associated with waveform separations correspond to caution numbers listed in Table 3 "Recommended Operating Conditions".

- 2 Refer to Paragraph "Power Supply Voltage Sequencing" (see summary) for additional information on this topic.

- 3 Refer to Table 9 for additional information on PLL Relock and reset signal assertion timing requirements.

- 4 Refer to Table 10 for additional information on reset configuration pin setup timing requirements.

- 5 HRST\_CPU/HRST\_CTRL must transition from a logic 0 to a logic 1 in less than one SDRAM\_SYNC\_IN clock cycle for the device to be in the non-reset state.

Figure 2: Supply Voltage Sequencing and Separation Cautions

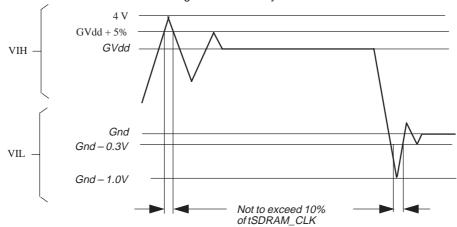

Figure 3 shows the undershoot and overshoot voltage of the memory interface of the PC8240.

Figure 3: Overshoot/Undershoot Voltage

### 3.5. Thermal information

#### 3.5.1. Thermal characteristics

Table 4 provides the package thermal characteristics for the PC8240.

**Table 4. Package Thermal Characteristics**

| Characteristics                          | Symbols         | Min | Units |

|------------------------------------------|-----------------|-----|-------|

| Die Junction-to-Case Thermal Resistance  | θ <sub>JC</sub> | 1.8 | C/W   |

| Die Junction-to-Board Thermal Resistance | $\theta_{JB}$   | 4.8 | C/W   |

#### 3.5.2. Thermal Management Information

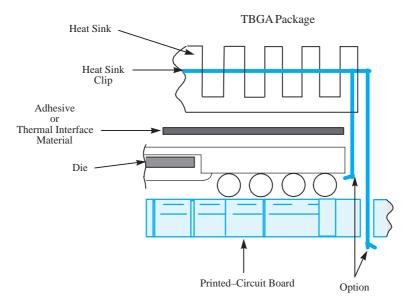

This section provides thermal management information for the tape ball grid array (TBGA) package for air-cooled applications. Proper thermal control design is primarily dependent upon the system-level design-the heat sink, airflow and thermal interface material. To reduce the die-junction temperature, heat sinks may be attached to the package by several methods-adhesive, spring clip to holes in the printed-circuit board or package, and mounting clip and screw assembly; see Figure 4.

Figure 4: Package Exploded Cross-Sectional View with Several Heat Sink Options

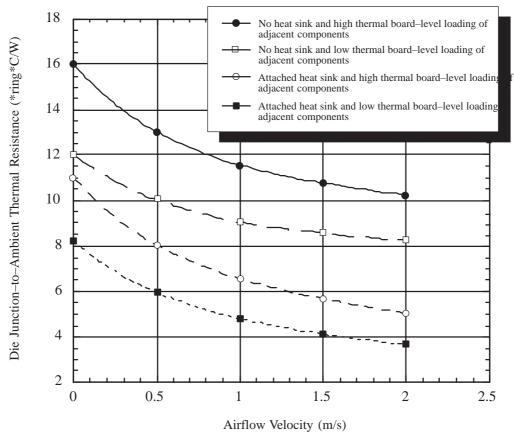

Figure 5 depicts the die junction-to-ambient thermal resistance for four typical cases:

- 1 A heat sink is not attached to the TBGA package and there exists high board-level thermal loading of adjacent components.

- 2 A heat sink is not attached to the TBGA package and there exists low board-level thermal loading of adjacent components.

- 3 A heat sink (e.g. ChipCoolers #HTS255-P) is attached to the TBGA package and there exists high board-level thermal loading of adjacent components.

- 4 A heat sink (e.g. ChipCoolers #HTS255-P) is attached to the TBGA package and there exists low board-level thermal loading of adjacent components.

Figure 5: Die Junction-to-Ambient Resistance

The board designer can choose between several types of heat sinks to place on the PC8240. There are several commercially-available heat sinks for the PC8240 provided by the following vendors:

Chip Coolers Inc. 800-227-0254 (USA/Canada)

333 Strawberry Field Rd. 401-739-7600

Warwick, RI 02887-6979

International Electronic Research Corporation (IERC) 818-842-7277

135 W. Magnolia Blvd.

Burbank, CA 91502

Internet: www.ctscorp.com

Thermalloy 972-243-4321

2021 W. Valley View Lane Dallas, TX 75234-8993 Internet: www.thermalloy.com

Internet: www.chipcoolers.com

781-406-3000

Wakefield Engineering

100 Cummings Center, Suite 157H

Beverly, MA 01915

Internet: www.wakefield.com

Aavid Engineering 972-551-7330

250 Apache Trail Terrell, TX 75160

Internet: www.aavid.com

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost.

#### 3.5.3. Internal Package Conduction Resistance

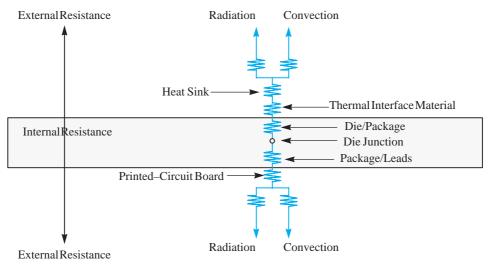

For the TBGA, cavity down, packaging technology, shown in Figure 4, the intrinsic conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-ball thermal resistance

Figure 6 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

(Note the internal versus external package resistance)

For this cavity-down, wire-bond TBGA package, heat generated on the active side of the chip is conducted through the silicon, the die attach and package spreader, then through the heat sink attach material (or thermal interface material), and finally to the heat sink where it is removed by forced-air convection.

Figure 6: C4 Package with Heat Sink Mounted to a Printed-Circuit Board

### 3.5.3.1. Adhesives and Thermal Interface Materials

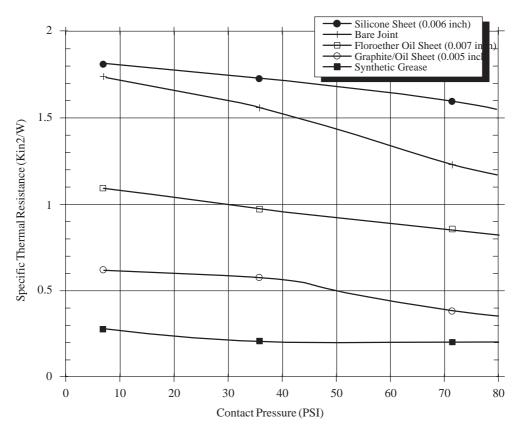

A thermal interface material is recommended at the package lid-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 7 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. That is, the bare joint results in a thermal resistance approximately 7 times greater than the thermal grease joint.

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 6). Therefore, the synthetic grease offers the best thermal performance, considering the low interface pressure. Of course, the selection of any thermal interface material depends on many factors—thermal performance requirements, manufacturability, service temperature, dielectric properties, cost, etc.

Figure 7: Thermal Performance of Select Thermal Interface Material

The board designer can choose between several types of thermal interface. Heat sink adhesive materials should be selected based upon high conductivity, yet adequate mechanical strength to meet equipment shock/vibration requirements. There are several commercially-available thermal interfaces and adhesive materials provided by the following vendors:

Dow-Corning Corporation 800-248-2481

**Dow-Corning Electronic Materials**

PO Box 0997

Midland, MI 48686-0997 Internet: www.dow.com

Chomerics, Inc. 781-935-4850

77 Dragon Court

Woburn, MA 01888-4014 Internet: www.chomerics.com

Thermagon Inc. 888-246-9050

3256 West 25th Street Cleveland, OH 44109-1668 Internet: www.thermagon.com

Loctite Corporation 860-571-5100

1001 Trout Brook Crossing Rocky Hill, CT 06067-3910 Internet: www.loctite.com

The following section provides a heat sink selection example using one of the commercially available heat sinks.

### 3.5.4. Heat Sink Selection Example

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$T_J = T_A + T_R + (\theta_{JC} + \theta_{INT} + \theta_{SA}) * P_D$

Where:

T<sub>J</sub> is the die-junction temperature

TA is the inlet cabinet ambient temperature

T<sub>R</sub> is the air temperature rise within the computer cabinet

$\theta_{JC}$  is the junction-to-case thermal resistance

$\theta_{\mbox{\scriptsize INT}}$  is the adhesive or interface material thermal resistance

$\theta_{\mbox{\scriptsize SA}}$  is the heat sink base-to-ambient thermal resistance

PD is the power dissipated by the device

During operation the die-junction temperatures ( $T_J$ ) should be maintained less than the value specified in Table . The temperature of the air cooling the component greatly depends upon the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature ( $T_A$ ) may range from 30 to 40 ¡C. The air temperature rise within a cabinet ( $T_R$ ) may be in the range of 5 to 10 ¡C. The thermal resistance of the thermal interface material ( $\theta_{INT}$ ) is typically about 1 ¡C/W. Assuming a  $T_A$  of 30 ¡C, a  $T_R$  of 5 ¡C, a  $T_R$  of 5 ¡C, a  $T_R$  of 5 jC, a  $T_R$  of 5 j

Die-junction temperature:  $T_J = 30 \text{ jC} + 5 \text{ jC} + (1.8 \text{ jC/W} + 1.0 \text{ jC/W} + \theta_{SA}) * 5.0 \text{ W}$

For preliminary heat sink sizing, the heat sink base-to-ambient thermal resistance is needed from the heat sink manufacturer.

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature, is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature-airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink attach, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, etc.

Due to the complexity and the many variations of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board, as well as, system-level designs. To expedite system-level thermal analysis, several "compact" thermal-package models are available within FLOTHERM®. These are available upon request.

#### 3.6. Power consideration

Table 5 provides *preliminary* power consumption data for the PC8240.

### **Table 5. Preliminary Power Consumption**

At recommended operating conditions (see Table 3) with GVdd = 3.3 V  $\pm$  5 % and LVdd = 3.3 V  $\pm$  5%

| Mode       | PCI Bus Clock / Memory Bus Clock<br>CPU Clock Frequency (MHz) |               |               |               |                |                |                | Units          | Notes |         |

|------------|---------------------------------------------------------------|---------------|---------------|---------------|----------------|----------------|----------------|----------------|-------|---------|

|            | 33/66/<br>166                                                 | 33/66/<br>200 | 33/66/<br>233 | 33/83/<br>250 | 33/100/<br>200 | 33/100/<br>250 | 66/100/<br>200 | 66/100/<br>250 |       |         |

| Typical    | 2.5                                                           | 2.8           | 3.2           | 3.4           | 3.0            | 3.5            | 3.0            | 3.6            | W     | 1, 5    |

| Max - FP   | 3.0                                                           | 3.4           | 3.8           | 4.1           | 3.6            | 4.2            | 3.6            | 4.3            | W     | 1, 2    |

| Max - INT  | 2.7                                                           | 3.0           | 3.4           | 3.7           | 3.3            | 3.8            | 3.4            | 3.8            | W     | 1, 3    |

| Doze       | 1.8                                                           | 2.0           | 2.2           | 2.4           | 2.2            | 2.6            | 2.2            | 2.6            | W     | 1, 4, 6 |

| Nap        | 700                                                           | 700           | 700           | 800           | 900            | 900            | 900            | 900            | mW    | 1, 4, 6 |

| Sleep      | 500                                                           | 500           | 500           | 500           | 500            | 500            | 800            | 800            | mW    | 1, 4, 6 |

|            |                                                               |               |               |               |                |                |                |                |       |         |

|            |                                                               |               |               | I/O Po        | wer Suppli     | es             |                |                |       |         |

| Mode       | Minimum                                                       |               |               |               | Maxi           | mum            |                | Units          | Notes |         |

| Typ - OVdd |                                                               | 200 600       |               |               |                | mW             | 7,8            |                |       |         |

| Typ - GVdd |                                                               | 30            | 00            |               |                | 90             | 00             |                | mW    | 7,9     |

# Notes:

- 1 The values include Vdd, AVdd, AVdd2, and LVdd but do not include I/O Supply Power, see Section 6.3.3 for information on OVdd and GVdd supply power.

- 2 Maximum FP power is measured at Vdd = 2.625V with dynamic power management enabled while running an entirely cacheresident, looping, floating point multiplication instruction.

- 3 Maximum INT power is measured at Vdd = 2.625V with dynamic power management enabled while running entirely cache-resident, looping, integer instructions.

- 4 Power saving mode maximums are measured at Vdd = 2.625V while the device is in doze, nap, or sleep mode.

- 5 Typical power is measured at Vdd = AVdd = 2.5V, OVdd = 3.3V where a nominal FP value, a nominal INT value, and a value where there is a continuous flush of cache lines with alternating ones and zeroes on 64 bit boundaries to local memory are averaged.

- 6 Power saving mode data measured with only two PCI\_CLKs and two SDRAM\_CLKs enabled.

- 7 The typical minimum I/O power values were results of the PC8240 performing cache resident integer operations at the slowest frequency combination of 33:66:166 (PCI:Mem:CPU) MHz.

- **8** The typical maximum OVdd value resulted from the PC8240 operating at the fastest frequency combination of 66:100:250 (PCI:Mem:CPU) MHz and performing continuous flushes of cache lines with alternating ones and zeroes to PCI memory.

- 9 The typical maximum GVdd value resulted from the PC8240 operating at the fastest frequency combination of 66:100:250 (PCI:Mem:CPU) MHz and performing continuous flushes of cache lines with alternating ones and zeroes on 64 bit boundaries to local memory.

### Note:

To calculate the power consumption at low temperature (-55°C), use a 1.25 factor.

# 3.7. Marking

The document where are defined the marking are identified in the related reference documents. Each microcircuit are legible and permanently marked with the following information as minimum:

- ATMEL Logo,

- Manufacturer's part number,

- Class B identification if applicable,

- Date-code of inspection lot,

- ESD identifier if available,

- Country of manufacturing.

# 4. ELECTRICAL CHARACTERISTICS

# 4.1. Static characteristics

Table 6 provides the DC electrical characteristics for the PC8240.

# **Table 6. DC Electrical Specifications**

At recommended operating conditions (See Table 3)

| Characteristics                                                   | Conditions <sup>4</sup>                      | Symbols          | Min      | Max      | Units |

|-------------------------------------------------------------------|----------------------------------------------|------------------|----------|----------|-------|

| Input High Voltage                                                | PCI only                                     | V <sub>IH</sub>  | 0.5*OVdd | LVdd     | V     |

| Input Low Voltage                                                 | PCI only                                     | V <sub>IL</sub>  | _        | .3*OVdd  | V     |

| Input High Voltage                                                | All other pins (GVdd = 3.3V)                 | V <sub>IH</sub>  | 2.0      | 3.3      | V     |

| Input High Voltage                                                | All other pins (GVdd = 2.5V)                 | V <sub>IH</sub>  | 1.8      | 2.5      | V     |

| Input Low Voltage                                                 | All inputs except OSC_IN                     | V <sub>IL</sub>  | GND      | 0.8      | V     |

| PCI_SYNC_IN Input High Voltage                                    |                                              | CVIH             | 0.5*OVdd | _        | V     |

| PCI_SYNC_IN Input Low Voltage                                     |                                              | CV <sub>IL</sub> | GND      | 0.3*OVdd | V     |

| Input Leakage Current <sup>5</sup> for pins using DRV_PCI driver. | 0.5 V V <sub>IN</sub> 2.7 V<br>@ LVdd = 4.75 | ΙL               | _        | 70       | A     |

| Input Leakage Current <sup>5</sup> for pins using DRV_PCI driver. | 0.5 V V <sub>IN</sub> 5.5 V<br>@ LVdd = 5.5  | ΙL               | _        | TBD      | A     |

| Input Leakage Current <sup>5</sup> all others                     | LVdd = 3.6 V<br>GVdd 3.465                   | ΙL               | _        | 10       | А     |

| Output High Voltage                                               | $I_{OH} = N/A^3 \text{ (GVdd} = 3.3V)$       | V <sub>OH</sub>  | 2.4      | _        | V     |

| Output Low Voltage                                                | $I_{OL} = N/A^3 $ (GVdd = 3.3V)              | V <sub>OL</sub>  | _        | 0.4      | V     |

| Output High Voltage                                               | $I_{OH} = N/A^3 \text{ (GVdd = 2.5V)}$       | V <sub>OH</sub>  | 1.85     | _        | V     |

| Output Low Voltage                                                | $I_{OL} = N/A^3 $ (GVdd = 2.5V)              | V <sub>OL</sub>  | _        | 0.6      | V     |

| Capacitance <sup>2</sup>                                          | V <sub>IN</sub> =0 V, f=1MHz                 | C <sub>IN</sub>  | _        | 7.0      | pF    |

### Notes:

- 1 See Table for pins with internal pull-up resistors.

- 2 Capacitance is periodically sampled rather than 100% tested.

- 3 See Table for the typical drive capability of a specific signal pin based upon the type of output driver associated with that pin as listed in .

- 4 These specifications are for the default driver strengths indicated in Table .

- 5 Leakage current is measured on input pins and on output pins in the high impedance state. The leakage current is measured for nominal OVdd/LVdd and Vdd or both Ovdd/LVdd and Vdd must vary in the same direction.

Table 7 provides information on the characteristics of the output drivers referenced in . The values are from the PC8240 IBIS model (v1.0) and are not tested, for additional detailed information see the complete IBIS model listing at http://www.mot.com/SPS/PowerPC/teksupport/tools/IBIS/kahlua\_1.ibs.txt

Table 7. Drive Capability of PC8240 Output Pins

| Driver Type  | Programmable<br>Output<br>Impedance (Ohms) | Supply<br>Voltage | I <sub>OH</sub> | loL  | Units | Notes |

|--------------|--------------------------------------------|-------------------|-----------------|------|-------|-------|

| DRV_STD      | 20                                         | OVdd = 3.3V       | TBD             | TBD  | mA    | 2, 5  |

|              | 40 (default)                               | OVdd = 3.3V       | TBD             | TBD  | mA    | 2, 5  |

|              | 25                                         | LVdd = 3.3        | 11.0            | 20.6 | mA    | 1, 4  |

| DRV_PCI      |                                            | LVdd = 5.0        | 5.6             | 10.3 | mA    | 1,4   |

|              | 50 (default)                               | LVdd = 3.3        | 5.6             | 10.3 | mA    | 1, 4  |

|              |                                            | LVdd = 5.0        | 5.6             | 10.3 | mA    | 1, 4  |

|              | 8 (default)                                | GVdd = 2.5        | TBD             | TBD  | mA    | 3, 6  |

|              |                                            | GVdd = 3.3        | 89.0            | 76.3 | mA    | 2, 5  |

| DRV_MEM_ADDR | 13.3                                       | GVdd = 2.5        | TBD             | TBD  | mA    | 3, 6  |

| DRV_PCI_CLK  |                                            | GVdd = 3.3        | 55.9            | 46.4 | mA    | 2, 5  |

|              | 20                                         | GVdd = 2.5        | TBD             | TBD  | mA    | 3, 6  |

|              |                                            | GVdd = 3.3        | 36.7            | 30.0 | mA    | 2, 5  |

|              | 40                                         | GVdd = 2.5        | TBD             | TBD  | mA    | 3, 6  |

|              |                                            | GVdd = 3.3        | TBD             | TBD  | mA    | 2, 5  |

|              | 20 (default)                               | GVdd = 2.5        | TBD             | TBD  | mA    | 3, 6  |

|              |                                            | GVdd = 3.3        | 36.7            | 30.0 | mA    | 2, 5  |

| DRV_MEM_DATA | 40                                         | GVdd = 2.5        | TBD             | TBD  | mA    | 3, 6  |

|              |                                            | GVdd = 3.3        | 18.7            | 15.0 | mA    | 2, 5  |

#### Notes:

- 1 For DRV\_PCI, I<sub>OH</sub> read from the listing in the pull-up mode, I(Min) column, at the 0.33V label by interpolating between the 0.3 V and 0.4 V table entries' current values which corresponds to the PCI V<sub>OH</sub> = 2.97 = 0.9\*LVdd (LVdd = 3.3 V) where Table Entry Voltage = LVdd PCI V<sub>OH</sub>.

- For all others with Ovdd or GVdd = 3.3 V,  $I_{OH}$  read from the listing in the pull-up mode, I(Min) column, at the 0.9 V table entry which corresponds to the  $V_{OH}$  = 2.4 V where Table Entry Voltage = O/GVdd PCI  $V_{OH}$ .

- 3 For GVdd = 2.5 V, I<sub>OH</sub> read from the listing in the pull-up mode, I(Min) column, at the TBD V table entry which corresponds to the V<sub>OH</sub> = TBD V where Table Entry Voltage = GVdd V<sub>OH</sub>.

- 4 For DRV\_PCI,  $I_{OL}$  read from the listing in the pull-down mode, I(Max) column, at 0.33 V = PCI  $V_{OL}$  = 0.1\*LVdd (LVdd = 3.3 V) by interpolating between the 0.3 V and 0.4 V table entries.

- 5 For all others with OVdd or GVdd = 3.3 V, I<sub>OL</sub> read from the listing in the pull-down mode, I(Max) column, at the 0.4 V table entry.

- 6 For GVdd = 2.5 V, I<sub>OL</sub> read from the listing in the pull-down mode, I(Max) column, at the TBD V table entry.

### 4.2. Dynamic Electrical Characteristics

This section provides the AC electrical characteristics for the PC8240. After fabrication, functional parts are sorted by maximum processor core frequency as shown in Table and Section , "Clock AC Timing Specifications" in table 9 and tested for conformance to the AC specifications for that frequency. The processor core frequency is determined by the bus (PCI\_SYNC\_IN) clock frequency and the settings of the PLL\_CFG[0-4] signals. Parts are sold by maximum processor core frequency; see Section <1>. , "Ordering Information"

Table 8 provides the operating frequency information for the PC8240.

### **Table 8. Operating Frequency**

At recommended operating conditions (See Table 3) with GVdd = 3.3 V  $\pm$  5% and LVdd = 3.3 V  $\pm$  5%

| Characteristic <sup>1</sup> | 200 MHz |     | 250 | Units |     |

|-----------------------------|---------|-----|-----|-------|-----|

|                             | Min     | Max | Min | Max   |     |

| Processor Frequency (CPU)   | 100     | 200 | 100 | 250   | MHz |

| Memory Bus Frequency        |         | MHz |     |       |     |

| PCI Input Frequency         |         | MHz |     |       |     |

#### Notes:

1 Caution: The PCI\_SYNC\_IN frequency and PLL\_CFG[0–4] settings must be chosen such that the resulting peripheral logic/memory bus frequency, CPU (core) frequency, and PLL (VCO) frequencies do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0–4] signal description in Section 6.2., "PLL Configuration," for valid PLL\_CFG[0–4] settings and PCI\_SYNC\_IN frequencies.

# 4.2.1. Clock AC Specifications

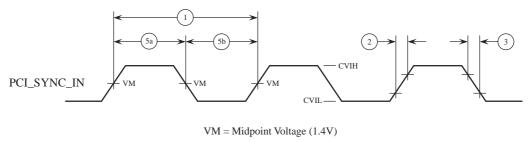

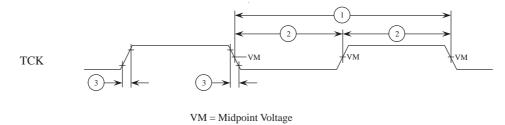

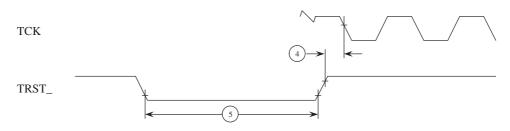

Table 9 provides the clock AC timing specifications as defined in Section

# **Table 9. Clock AC Timing Specifications**

At recommended operating conditions (See Table 3) with GVdd = 3.3 V  $\pm~5\%$  and LVdd = 3.3 V  $\pm~5\%$

| Num | Characteristics and Conditions <sup>1</sup>           | Min                                        | Max                                           | Unit | Notes |

|-----|-------------------------------------------------------|--------------------------------------------|-----------------------------------------------|------|-------|

|     | Frequency of Operation (PCI_SYNC_IN)                  | 25                                         | 66                                            | MHz  |       |

| 1   | PCI_SYNC_IN Cycle Time                                | 40                                         | 15                                            | ns   |       |

| 2,3 | PCI_SYNC_IN Rise and Fall Times                       | _                                          | 2.0                                           | ns   | 2     |

| 4   | PCI_SYNC_IN Duty Cycle Measured at 1.4 V.             | 40                                         | 60                                            | %    |       |

| 5a  | PCI_SYNC_IN Pulse Width High Measured at 1.4V         | 6                                          | 9                                             | ns   | 3     |

| 5b  | PCI_SYNC_IN Pulse Width Low Measured at 1.4V          | 6                                          | 9                                             | ns   | 3     |

| 7   | PCI_SYNC_IN Short Term Jitter (Cycle to Cycle)        | _                                          | <500                                          | ps   |       |

| 8a  | PCI_CLK[0-4] Skew (Pin to Pin)                        | 0                                          | 500                                           | ps   |       |

| 8b  | SDRAM_CLK[0-3] Skew (Pin to Pin)                      | TBD TBD                                    |                                               | ps   | 8     |

| 9   | PCI_SYNC_IN Long Term Jitter                          | <b>—</b> <500                              |                                               | ps   |       |

| 10  | Internal PLL Relock Time                              | _                                          | 100                                           | μs   | 3,4,6 |

|     | DLL Lock Range with DLL_EXTEND = 0 disabled (Default) | 0 (NT <sub>clk</sub> - t <sub>lo</sub>     | oop - t <sub>fix0</sub> ) 7                   | ns   | 7     |

|     | DLL Lock Range with DLL_EXTEND = 1 enabled            | 0 (NT <sub>clk</sub> - T <sub>clk</sub> /2 | 2 - t <sub>loop</sub> - t <sub>fix0</sub> ) 7 | ns   | 7     |

|     | Frequency of Operation (OSC_IN)                       | 25                                         | 66                                            | MHz  |       |

|     | OSC_IN Cycle Time                                     | 40                                         | 15                                            | ns   |       |

|     | OSC_IN Rise and Fall Times                            | _                                          | 5                                             | ns   | 5     |

|     | OSC_IN Duty Cycle Measured at 1.4 V.                  | 40                                         | 60                                            | %    |       |

|     | OSC_IN Frequency Stability                            | _                                          | 100                                           | ppm  |       |

|     | OSC_IN Jitter (Cycle to Cycle)                        | _                                          | <tbd< td=""><td>ps</td><td></td></tbd<>       | ps   |       |

|     | OSC_IN V <sub>IH</sub> (Loaded)                       | TBD                                        |                                               | V    |       |

|     | OSC_IN V <sub>IL</sub> (Loaded)                       |                                            | TBD                                           | V    |       |

- 1 These specifications are for the default driver strengths indicated in Table 7.

- 2 Rise and fall times for the PCI\_SYNC\_IN input are measured from 0.4 to 2.4 V.

- 3 Specification value at maximum frequency of operation.

- 4 Relock time is guaranteed by design and characterization. Relock time is not tested.

- 5 Rise and fall times for the OSC\_IN input is guaranteed by design and characterization. OSC\_IN input rise and fall times are not tested.

- Relock timing is guaranteed by design. PLL-relock time is the maximum amount of time required for PLL lock after a stable Vdd and PCI\_SYNC\_IN are reached during the reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRST\_CPU / HRST\_CTRL must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the reset sequence.

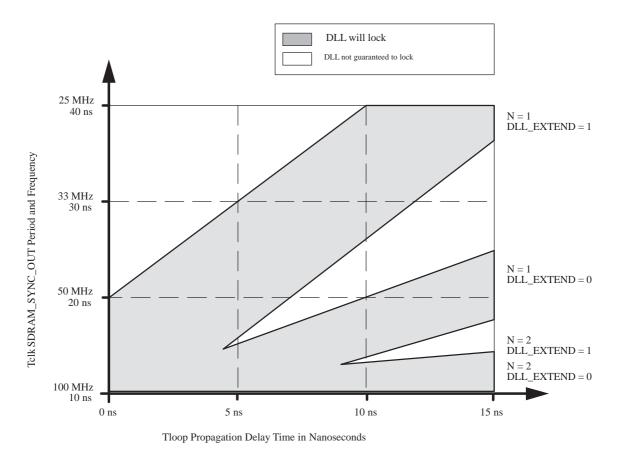

- 7 DLL\_EXTEND is bit 7 of the PMC2 register <72>. N is a non-zero integer (1, 2, 3, ...). T<sub>clk</sub> is the period of one SDRAM\_SYNC\_OUT clock cycle in ns. t<sub>loop</sub> is the propagation delay of the DLL synchronization feedback loop (PC board runner) from SDRAM\_SYNC\_OUT to SDRAM\_SYNC\_IN in ns; 6.25 inches of loop length (unloaded PC board runner) corresponds to approximately 1 ns of delay. t<sub>fix0</sub> is a fixed delay inherent in the design when the DLL is at tap point 0 and the DLL is contributing no delay; t<sub>fix0</sub> equals approximately 3 ns. See Figure 9 for DLL locking ranges.

- Pin to pin skew includes quantifying the additional amount of clock skew (or jitter) from the DLL besides any intentional skew added to the clocking signals from the variable length DLL synchronization feedback loop, i.e. the amount of variance between the internal sys-logic\_clk and the SDRAM\_SYNC\_IN signal after the DLL is locked. While pin to pin skew between SDRAM\_CLKs can be measured, the relationship between the internal sys-logic\_clk and the external SDRAM\_SYNC\_IN can not be measured and is guaranteed by design.

Figure 8: PCI\_SYNC\_IN Input Clock Timing Diagram

Figure 9: DLL Locking Range Loop Delay vs. Frequency of Operation

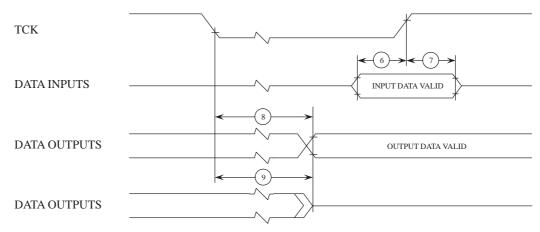

#### 4.2.2. Input AC Timing Specifications

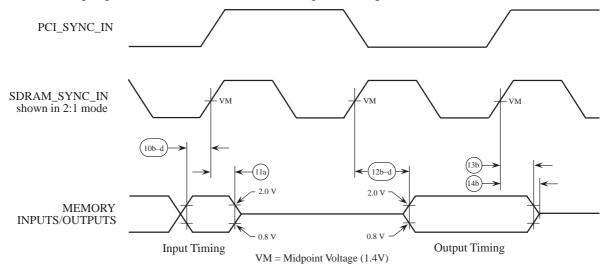

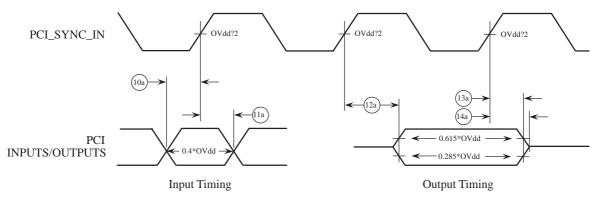

Table 10 provides the input AC timing specifications. See Figure 10 and Figure 11.

### **Table 10. Input AC Timing Specifications**

At recommended operating conditions (See Table 3) with GVdd =  $3.3~V~\pm~5\%$  and LVdd =  $3.3~V~\pm~5\%$

| Num  | Characteristic                                                                                | Min                | Max | Units | Notes |

|------|-----------------------------------------------------------------------------------------------|--------------------|-----|-------|-------|

| 10a  | PCI Input Signals Valid to PCI_SYNC_IN (Input Setup)                                          | 2.0                |     | ns    | 2,3   |

| 10b1 | Memory Control & Data Input Signals in Flow Through Mode Valid to SDRAM_SYNC_IN (Input Setup) | 4.0                | l   | ns    | 1,3   |

| 10b2 | Memory Control & Data Input Signals in Registered Mode Valid to SDRAM_SYNC_IN (Input Setup)   | TBD                |     | ns    | 1,3   |

| 10c  | Epic, Misc. Debug Input Signals Valid to SDRAM_SYNC_IN (Input Setup)                          | TBD                |     | ns    | 1,3   |

| 10d  | I <sup>2</sup> C Input Signals Valid to SDRAM_SYNC_IN (Input Setup)                           | TBD                | _   | ns    | 1,3   |

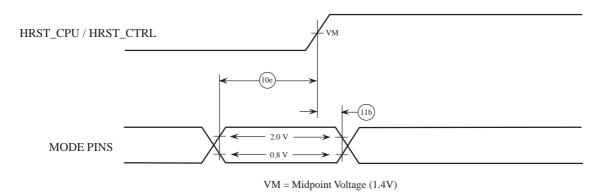

| 10e  | Mode select Inputs Valid to HRST_CPU / HRST_CTRL (Input Setup)                                | 9*t <sub>CLK</sub> |     | ns    | 1,3-5 |

| 11a  | PCI_SYNC_IN (SDRAM_SYNC_IN) to Inputs Invalid (Input Hold)                                    | 1.0                |     | ns    | 1,2,3 |

| 11b  | HRST_CPU / HRST_CTRL to Mode select Inputs Invalid (Input Hold)                               | TBD                | _   | ns    | 1,3,5 |

- 1 All memory and related interface input signal specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the V<sub>M</sub> = 1.4 V of the rising edge of the memory bus clock, SDRAM\_SYNC\_IN. SDRAM\_SYNC\_IN is the same as PCI\_SYNC\_IN in 1:1 mode, but is twice the frequency in 2:1 mode (processor/memory bus clock rising edges occur on every rising and falling edge of PCI\_SYNC\_IN). See Figure 10.

- 2 All PCI signals are measured from OVdd/2 of the rising edge of PCI\_SYNC\_IN to 0.4\*OVdd of the signal in question for 3.3 V PCI signaling levels. See Figure 11.

- 3 Input timings are measured at the pin.

- 4 t<sub>CLK</sub> is the time of one SDRAM\_SYNC\_IN clock cycle.

- 5 All mode select input signals specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the V<sub>M</sub> = 1.4 V of the rising edge of the HRST\_CPU / HRST\_CTRL signal. See Figure 12.

Figure 10: Input - Output Timing Diagram Referenced to SDRAM\_SYNC\_IN

Figure 11: Input - Output Timing Diagram Referenced to PCI\_SYNC\_IN

Figure 12: . Input Timing Diagram for Mode Select Signals

#### 4.2.3. Output AC Timing Specification

Table 11 provides the processor bus AC timing specifications for the PC8240. See Figure 10 and Figure 11.

**Table 11. Output AC Timing Specifications**

At recommended operating conditions (See Table 3) with GVdd =  $3.3~V~\pm~5\%$  and LVdd =  $3.3~V~\pm~5\%$

| Num  | Characteristic <sup>3,6</sup>                                                                                      | Min | Max | Units | Notes |

|------|--------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

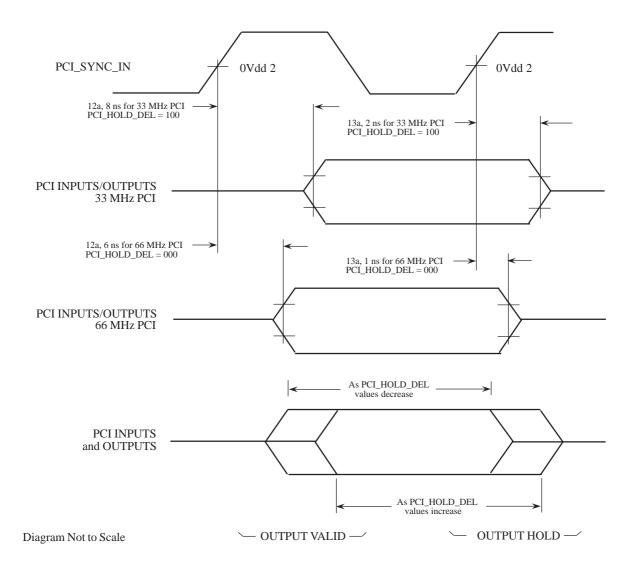

| 12a  | PCI_SYNC_IN to Output Valid, 66 MHz PCI, with $\overline{\text{MCP}}$ pulled-down to logic 0 state. See Table .    | _   | 6.0 | ns    | 2,4   |

|      | PCI_SYNC_IN to Output Valid, 33 MHz PCI, with $\overline{\text{MCP}}$ in the default logic 1 state. See Table .    | _   | 8.0 | ns    | 2,4   |

| 12b1 | SDRAM_SYNC_IN to Output Valid<br>(For Memory Control & Data Signals accessing DRAM in Flow<br>Through Mode)        | _   | 7.0 | ns    | 1     |

| 12b2 | SDRAM_SYNC_IN to Output Valid (For Memory Control & Data Signals accessing DRAM in Registered Mode)                | _   | TBD | ns    | 1     |

| 12b3 | SDRAM_SYNC_IN to Output Valid (For Memory Control & Data Signals accessing non-DRAM.)                              | _   | TBD | ns    | 1     |

| 12c  | SDRAM_SYNC_IN to Output Valid (For All Others)                                                                     | _   | 7.0 | ns    | 1     |

| 12d  | SDRAM_SYNC_IN to Output Valid (For I <sup>2</sup> C)                                                               | _   | TBD | ns    | 1     |

| 13a  | Output Hold, 66 MHz PCI, with MCP and CKE pulled-down to logic 0 states. See Table 12.                             | 0.5 | _   | ns    | 2,4,5 |

|      | Output Hold, 33 MHz PCI, with MCP in the default logic 1 state and CKE pulled-down to logic 0 state. See Table 12. | 2.0 | _   | ns    | 2,4,5 |

| 13b  | Output Hold (All Others)                                                                                           | 0   | _   | ns    | 1     |

| 14a  | PCI_SYNC_IN to Output High Impedance (For PCI)                                                                     | _   | TBD | ns    | 2,4   |

| 14b  | SDRAM_SYNC_IN to Output High Impedance (For All Others)                                                            | _   | TBD | ns    | 1     |

- 1 All memory and related interface output signal specifications are specified from the V<sub>M</sub> = 1.4 V of the rising edge of the memory bus clock, SDRAM\_SYNC\_IN to the TTL level (0.8 or 2.0 V) of the signal in question. SDRAM\_SYNC\_IN is the same as PCI\_SYNC\_IN in 1:1 mode, but is twice the frequency in 2:1 mode (processor/memory bus clock rising edges occur on every rising and falling edge of PCI\_SYNC\_IN). See Figure 10.

- 2 All PCI signals are measured from OVdd/2 of the rising edge of PCI\_SYNC\_IN to 0.285\*OVdd or 0.615\*OVdd of the signal in question for 3.3 V PCI signaling levels. See Figure 11.

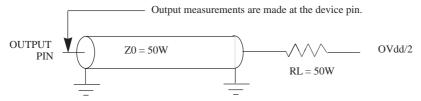

- 3 All output timings assume a purely resistive 50 ohm load (See Figure 13). Output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 4 PCI Bussed signals are composed of the following signals: <u>LOCK</u>, <u>IRDY</u>, <u>C/BE</u>[0–3], PAR, <u>TRDY</u>, <u>FRAME</u>, <u>STOP</u>, <u>DEVSEL</u>, <u>PERR</u>, <u>SERR</u>, AD[0–31], <u>REQ</u>[4–0], <u>GNT</u>[4–0], <u>IDSEL</u>, <u>INTA</u>.

- 5 PCI hold times can be varied, see AUCUN LIEN "PCI Signal Output Hold Timing" section for information on programmable PCI output hold times. The values shown for item 13a are for PCI compliance.

- 6 These specifications are for the default driver strengths indicated in Table 3.

Figure 13: AC Test Load for the PC8240

### 4.2.3.1. PCI Signal Output Hold Timing

In order to meet minimum output hold specifications relative to PCI\_SYNC\_IN for both 33 MHz and 66 MHz PCI systems, the PC8240 has a programmable output hold delay for PCI signals. The initial value of the output hold delay is determined by the values on the  $\overline{\text{MCP}}$  and CKE reset configuration signals. Further output hold delay values are available by programming the PCI\_HOLD\_DEL value of the PMCR2 configuration register.

Table 12 describes the bit values for the PCI\_HOLD\_DEL values in PMCR2.

Table 12. Power Management Configuration Register 2-0x72

| Bit | Name         | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–4 | PCI_HOLD_DEL | xx0            | PCI output hold delay values relative to PCI_SYNC_IN. The initial values of bits 6 and 5 are determined by the reset configuration pins MCP and CKE, respectively. As these two pins have internal pull-up resistors, the default value after reset is 0b110.                                                                                                                    |

|     |              |                | While the minimum hold times are guaranteed at shown values, changes in the actual hold time can be made by incrementing or decrementing the value in these bit fields of this register via software or hardware configuration. The increment is in approximately 400 picosecond steps. Lowering the value in the three bit field decreases the amount of output hold available. |

|     |              |                | <ul> <li>66 MHz PCI. Pull-down MCP configuration pin with a 2K or less value resistor. This setting guarantees the minimum output hold, item 13a, and the maximum output valid, item 12a, times as specified in Table are met for a 66 MHz PCI system. See Figure 14.</li> <li>001</li> <li>010</li> <li>011</li> </ul>                                                          |

|     |              |                | 100 33 MHz PCI. This setting guarantees the minimum output hold, item 13a, and the maximum output valid, item 12a, times as specified in Table are met for a 33 MHz PCI system. See Figure 14.  101 110 (Default if reset configuration pins left unconnected)                                                                                                                   |

Figure 14: PCI\_HOLD\_DEL Affect on Output Valid and Hold Time

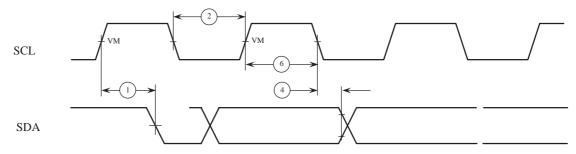

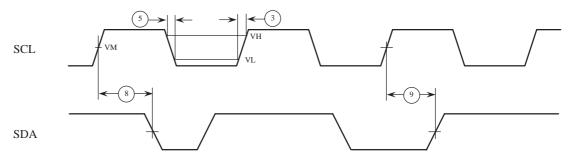

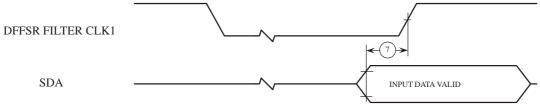

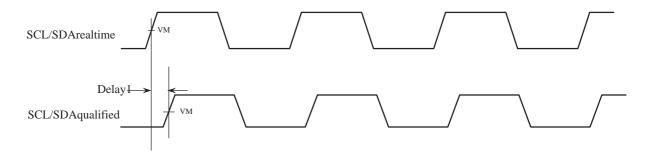

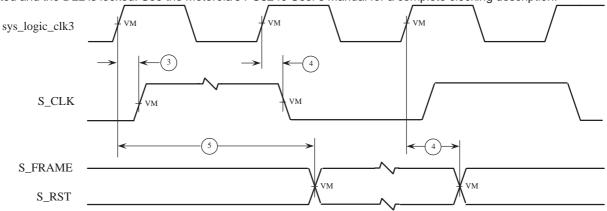

### 4.2.4. I<sup>2</sup>C AC Timing Specifications

Table 13 provides the I<sup>2</sup>C input AC timing specifications for the PC8240.

# Table 13. I<sup>2</sup>C Input AC Timing Specifications

At recommended operating conditions (See Table 3) with GVdd = 3.3 V  $\pm$  5% and LVdd = 3.3 V  $\pm$  5%

| Num | Characteristic                                                                                                                                    | Min                                                                                                                                                                       | Max | Unit | Notes    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|

|     |                                                                                                                                                   |                                                                                                                                                                           |     |      |          |

| 1   | Start condition hold time                                                                                                                         | 4.0                                                                                                                                                                       | _   | CLKs | 1,2      |

| 2   | Clock low period (The time before the PC8240 will drive SCL low as a transmitting slave after detecting SCL low as driven by an external master.) | 8.0 + (16 x 2 <sup>FDR[4:2]</sup> ) x (5 -<br>4({FDR[5],FDR[1]} == b'10) -<br>3({FDR[5],FDR[1]} == b'11) -<br>2({FDR[5],FDR[1]} == b'00) -<br>1({FDR[5],FDR[1]} == b'01)) | _   | CLKs | 1,2,4, 5 |

| 3   | SCL/SDA rise time (from 0.5v to 2.4v)                                                                                                             | _                                                                                                                                                                         | 1   | mS   |          |

| 4   | Data hold time                                                                                                                                    | 0                                                                                                                                                                         | _   | nS   | 2        |

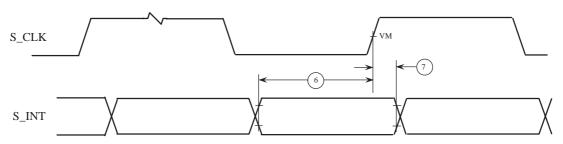

| 5   | SCL/SDA fall time (from 2.4 to 0.5v)                                                                                                              | _                                                                                                                                                                         | 1   | mS   |          |