# ORCA® OR3LP26B Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface

## Introduction

Lattice has developed a solution for designers who need the many advantages of an FPGA-based design implementation, coupled with the high bandwidth of an industry-standard PCI interface. The *ORCA* OR3LP26B (a member of the Series 3+ FPSC family) provides a full-featured 33/50/66 MHz, 32-/64-bit PCI interface, fully designed and tested, in hardware, plus FPGA logic for user-programmable functions.

# **PCI Bus Core Highlights**

- Implemented in an ORCA Series 3 OR3L125B base array, displacing the bottom ten rows of 28 columns.

- Core is a well-tested ASIC model.

- Fully compliant to Revision 2.2 of PCI Local Bus specification.

- Operates at PCI bus speeds up to 66 MHz on a 32-/64-bit wide bus.

- Comprises two independent controllers for Master and Target.

- Meets/exceeds all requirements for PICMG\* Hot Swap friendly silicon, full Hot Swap model, per the CompactPCI\* Hot Swap specification, PICMG 2.1 R1.0.

- PCI SIG Hot Plug (R1.0) compliant.

- Four internal FIFOs individually buffer both directions of both the Master and Target interfaces:

- Both Master FIFOs are 64 bits wide by 32 bits deep.

- Both Target FIFOs are 64 bits wide by 16 bits deep.

- Capable of no-wait-state, full-burst PCI transfers in either direction, on either the Master or Target interface. The dual 64-bit data paths extend into the FPGA logic, permitting full-bandwidth, simultaneous bidirectional data transfers of up to 528 Mbytes/s to be sustained indefinitely.

- Can be configured to provide either two 64-bit buses (one in each direction) to be multiplexed between Master and Target, or four independent 32-bit buses.

- Provides many hardware options in the PCI core that are set during FPGA logic configuration.

- Operates within the requirements of the PCI 5 V and 3.3 V signaling environments and 3.3 V commercial environmental conditions, allowing the same device to be used in 5 V or 3.3 V PCI systems.

- FPGA is reconfigurable via the PCI interface's configuration space (as well as conventionally), allowing the FPGA to be field-updated to meet latebreaking requirements of emerging protocols.

Table 1. ORCA OR3LP26B PCI FPSC Solution—Available FPGA Logic

| Device   | Usable Gates <sup>†</sup> | Number of LUTs | Number of<br>Registers |     | Max User<br>I/Os | Array<br>Size | Number of PFUs |

|----------|---------------------------|----------------|------------------------|-----|------------------|---------------|----------------|

| OR3LP26B | 60K—120K                  | 4032           | 5304                   | 64K | 259              | 18 x 28       | 504            |

<sup>†</sup> The embedded core and interface comprise approximately 85K standard-cell ASIC gates in addition to these usable gates. The usable gate counts range from a logic-only gate count to a gate count assuming 30% of the PFUs/SLICs being used as RAMs. The logic-only gate count includes each PFU/SLIC (counted as 108 gates per PFU/SLIC), including 12 gates per LUT/FF pair (eight per PFU), and 12 gates per SLIC/FF pair (one per PFU). Each of the four PIOs per PIC is counted as 16 gates (two FFs, fast-capture latch, output logic, CLK drivers, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32 x 4 RAM (or 512 gates) per PFU.

<sup>\*</sup> PICMG and CompactPCI are registered trademarks of the PCI Industrial Computer Manufacturers Group.

**Page**

# **Table of Contents**

**Contents**

| Contents                                                                             | Page     |

|--------------------------------------------------------------------------------------|----------|

| Introduction                                                                         | 1        |

| PCI Bus Core Highlights                                                              |          |

| FPSC Highlights                                                                      |          |

| Software Support                                                                     |          |

| Description                                                                          |          |

| What Is an FPSC?                                                                     | 5        |

| FPSC Overview                                                                        |          |

| FPSC Gate Counting                                                                   |          |

| FPGA/Embedded Core Interface                                                         |          |

| ORCA Foundry Development System                                                      |          |

| FPSC Design Kit                                                                      |          |

| FPGA Logic Overview                                                                  |          |

| PLC Logic                                                                            |          |

| PIC Logic                                                                            |          |

| System Features                                                                      |          |

| Routing                                                                              |          |

| Configuration                                                                        |          |

| Boundary Scan                                                                        |          |

| OR3LP26B Overview                                                                    |          |

| Device Layout                                                                        |          |

| PCI Local Bus                                                                        |          |

| OR3LP26B PCI Bus Core Overview                                                       |          |

| PCI Bus Interface                                                                    |          |

| Embedded Core Options/FPGA Configuration                                             |          |

| PCI Bus Core Detailed Description                                                    |          |

| PCI Bus Commands                                                                     |          |

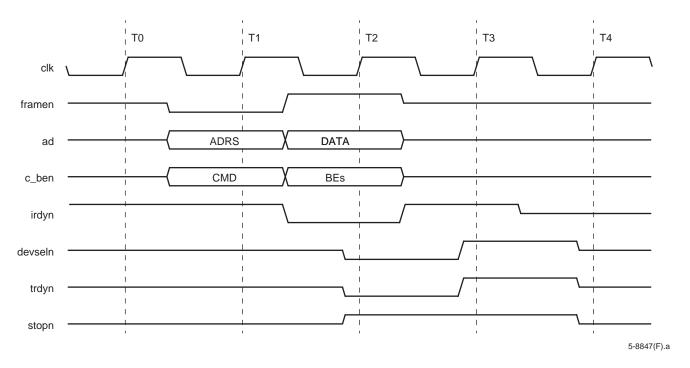

| PCI Protocol Fundamentals                                                            |          |

| FIFO Memories and Control                                                            |          |

| PCI Bus Pin Information                                                              |          |

| PCI Bus Core Detailed Description Dual Port                                          |          |

| Embedded Core/FPGA Interface Signal Descript                                         | tions 19 |

| Embedded Core/FPGA Interface Signal Location                                         | ıs25     |

| Embedded Core Bit Stream Configurable Option                                         |          |

| Understanding FIFO Packing/Unpacking                                                 |          |

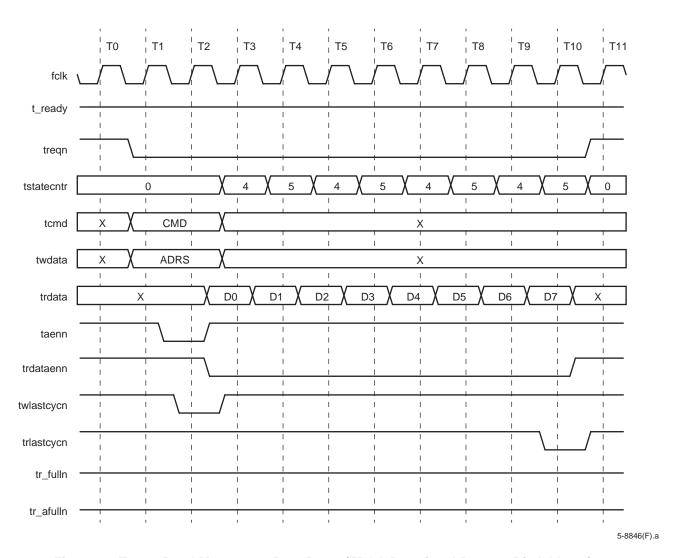

| Embedded Core/FPGA Interface Operation                                               |          |

| Embedded Core/FPGA Interface Operation Sum                                           |          |

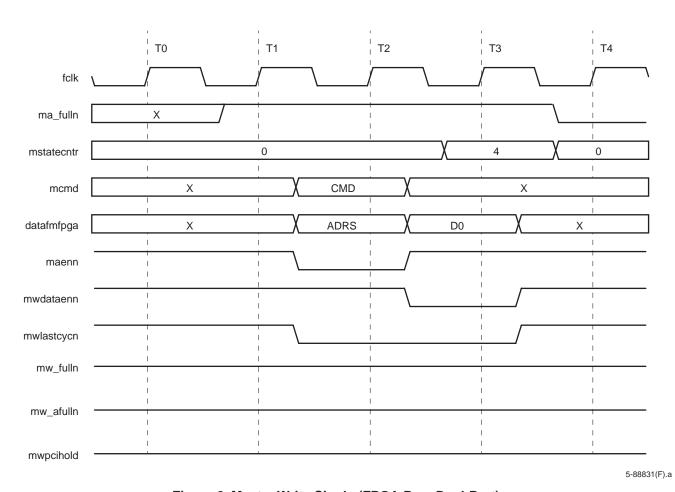

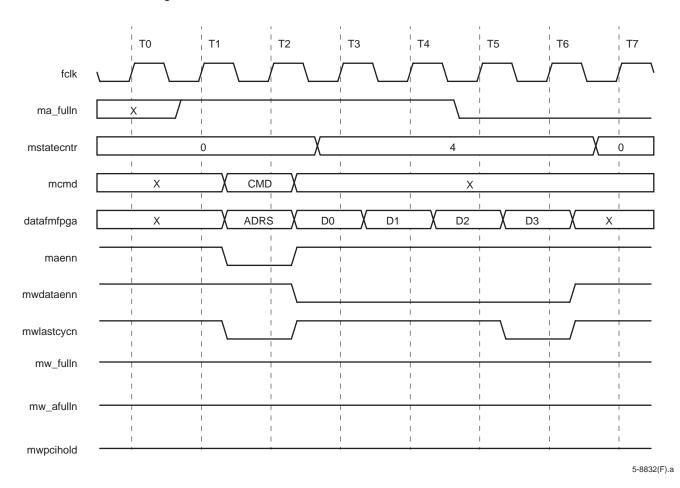

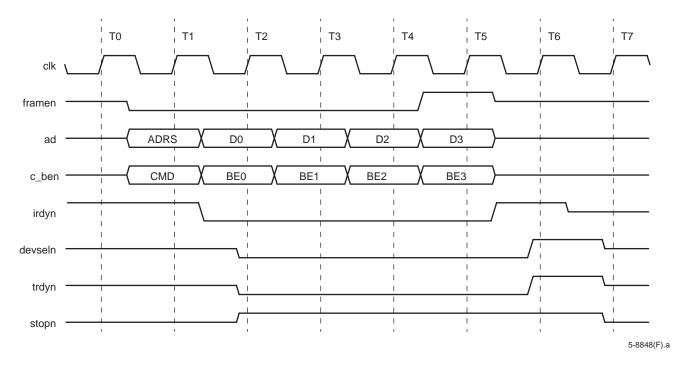

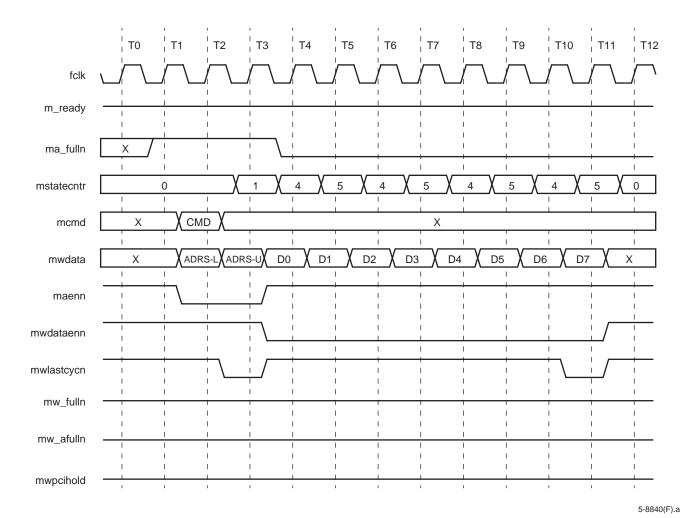

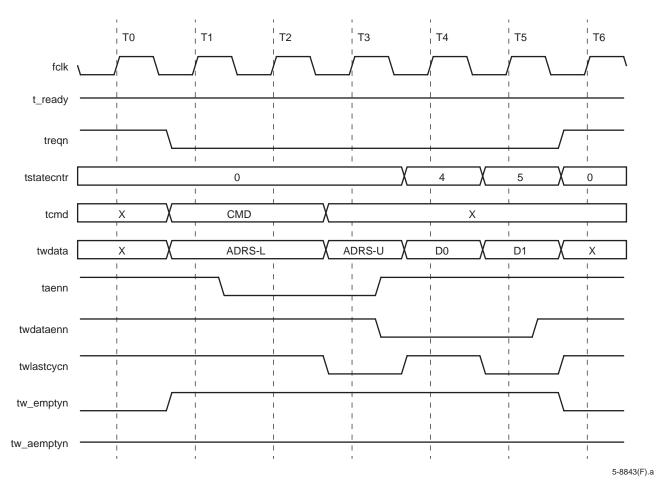

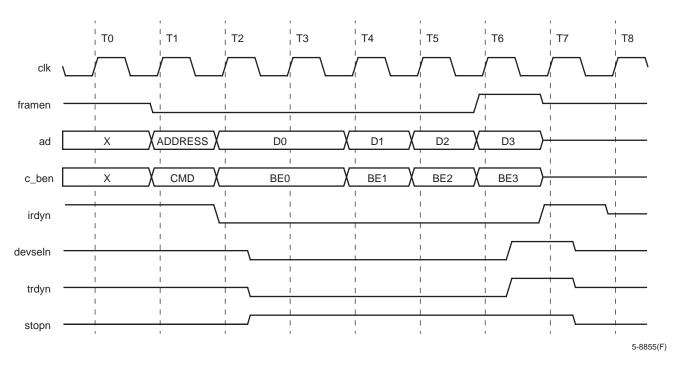

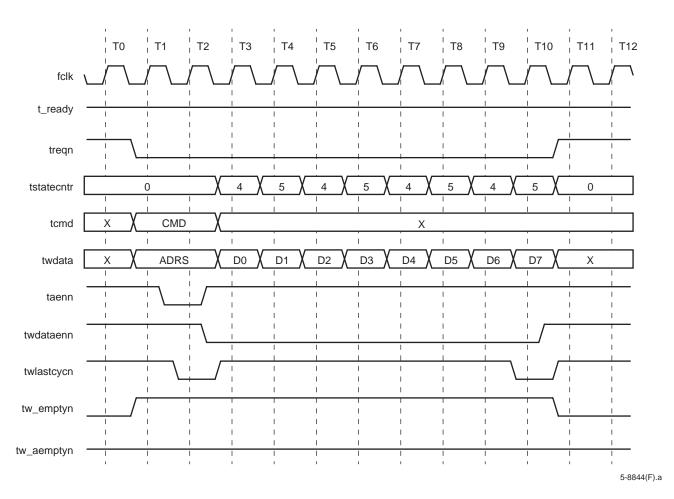

| Master (FPGA Initiated) Write                                                        |          |

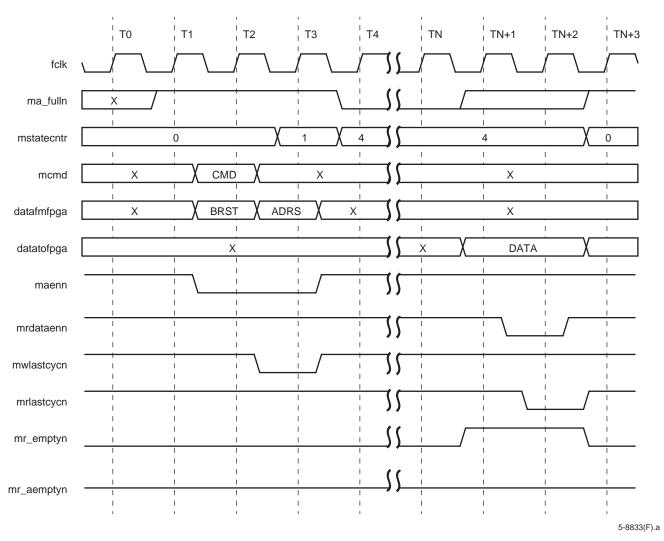

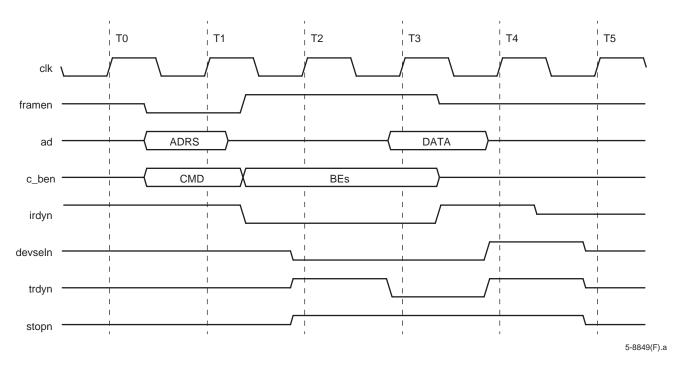

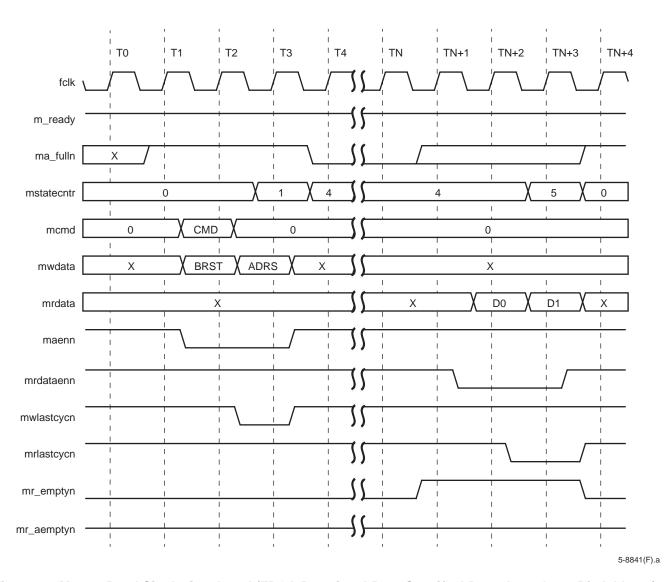

| Master (FPGA Initiated) Read                                                         |          |

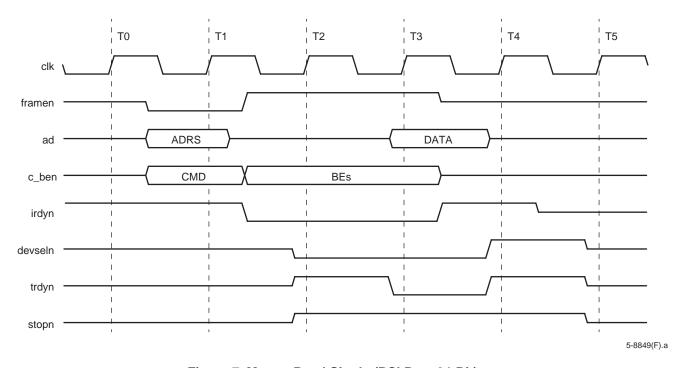

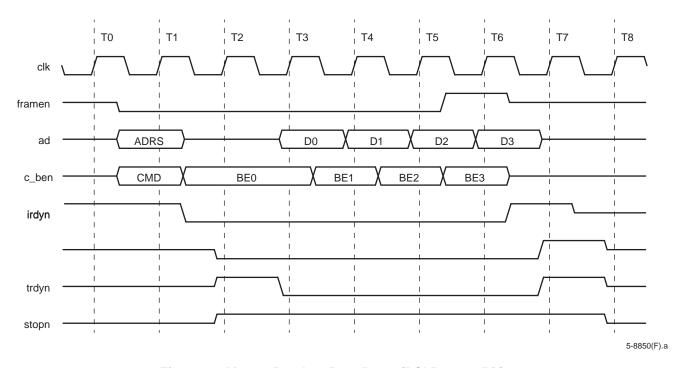

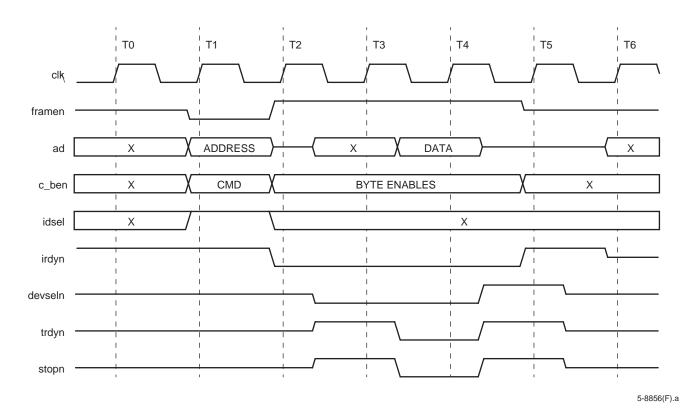

| Target (PCI Bus Initiated) Write                                                     |          |

| Target (PCI Bus Initiated) Read                                                      |          |

| PCI Bus Core Detailed Description Quad Port                                          |          |

| Embedded Core/FPGA Interface Signal Descript                                         |          |

| Embedded Core/FPGA Interface Signal Location                                         |          |

| Embedded Core Bit Stream Configurable Option                                         |          |

| Understanding FIFO Packing/Unpacking                                                 |          |

| Embedded Core/FPGA Interface Operation<br>Embedded Core/FPGA Interface Operation Sum |          |

| Master (FPGA Initiated) Write                                                        |          |

| Master (FPGA Initiated) Write                                                        |          |

| Target (PCI Bus Initiated) Write                                                     |          |

| Target (PCI Bus Initiated) Write<br>Target (PCI Bus Initiated) Read                  |          |

| Configuration Space of the PCI Core                                                  |          |

| PCI Bus Configuration Space Organization                                             |          |

| FPSC Configuration                                                                   |          |

| Configuration via PCI Bus                                                            |          |

| g                                                                                    | — .      |

| Readback via PCI interface                    | 125 |

|-----------------------------------------------|-----|

| Interaction Among Configuration Modes         |     |

| Clocking Options at FPGA/Core Boundary        |     |

| PCI Clock as System Clock                     |     |

| Local Clock as System Clock                   | 126 |

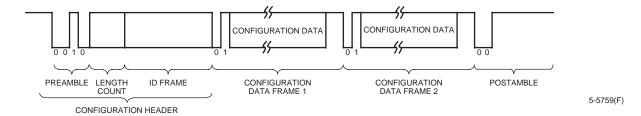

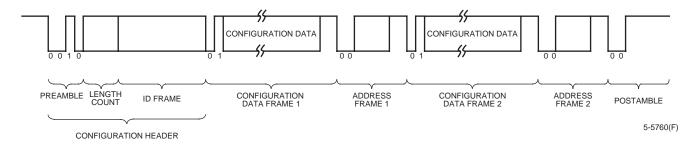

| FPGA Configuration Data Format                | 128 |

| Using ORCA Foundry to Generate                |     |

| Configuration RAM Data                        | 128 |

| FPGA Configuration Data Frame                 | 128 |

| Bit Stream Error Checking                     | 130 |

| FPGA Configuration Modes                      |     |

| Powerup Sequencing for Series OR3LP26B Device | 131 |

| Absolute Maximum Ratings                      | 131 |

| Recommended Operating Conditions              |     |

| Electrical Characteristics                    | 133 |

| Timing Characteristics                        | 134 |

| Description                                   | 134 |

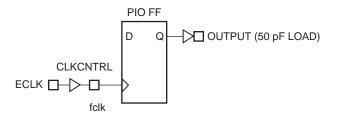

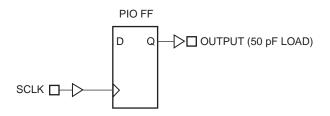

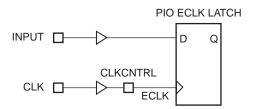

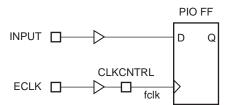

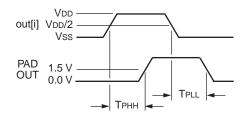

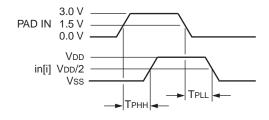

| Clock Timing                                  | 135 |

| Input/Output Buffer Measurement Conditions    | 146 |

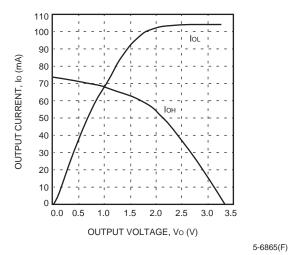

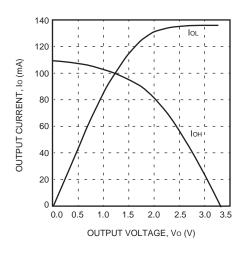

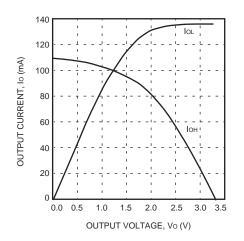

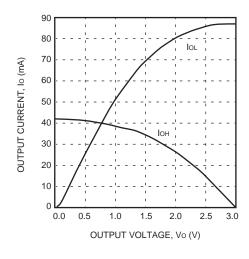

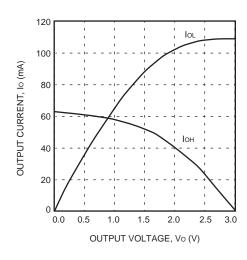

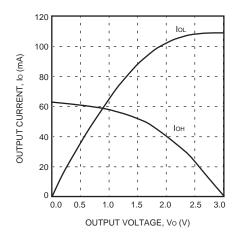

| Output Buffer Characteristics                 |     |

| Estimating Power Dissipation                  | 148 |

| Pin Information                               | 149 |

| Package Compatibility                         | 152 |

| Package Thermal Characteristics Summary       | 176 |

| ΘJA                                           | 176 |

| ψJC                                           | 176 |

| ΘJC                                           | 176 |

| ΘJB                                           | 176 |

| FPGA Maximum Junction Temperature             | 176 |

| Package Coplanarity                           | 177 |

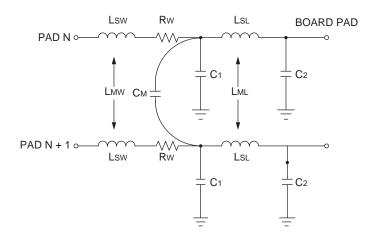

| Package Parasitics                            | 178 |

| Package Outline Diagrams                      | 179 |

| Terms and Definitions                         | 179 |

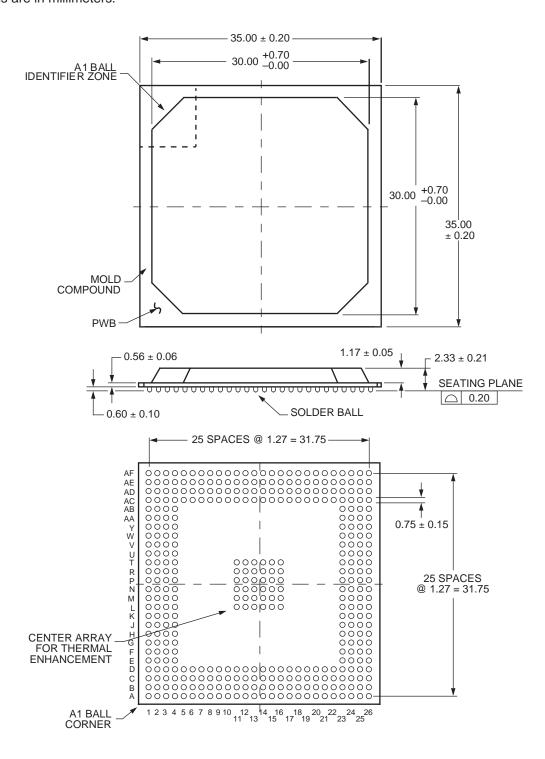

| 352-Pin PBGA                                  | 180 |

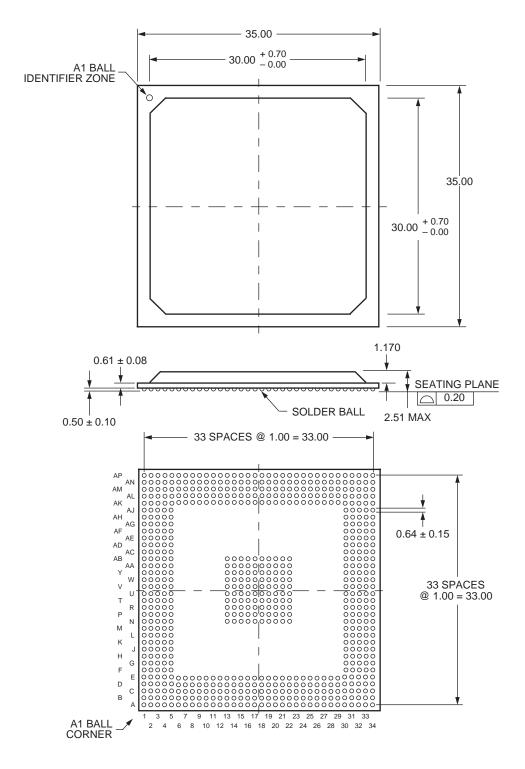

| 680-Pin PBGA                                  | 181 |

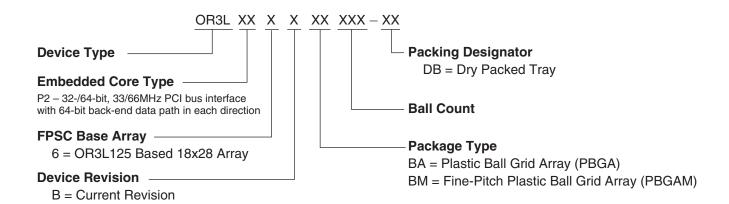

| Ordering Information                          | 182 |

|                                               |     |

2 Lattice Semiconductor

# PCI Bus Core Highlights (continued)

#### ■ Master:

- Generates all defined command codes except interrupt acknowledge and special cycle.

- Capable of accessing its own local Target.

- Capable of acting as the system's configuration agent by booting up with the Master logic enabled.

- Supports multiple options for Master bus requests, to increase PCI bus bandwidth.

- Supports single-cycle I/O space accesses.

- Provides option to delay PCI access until FIFO is full on Master writes to increase PCI bandwidth.

- Supports programmable latency timer control.

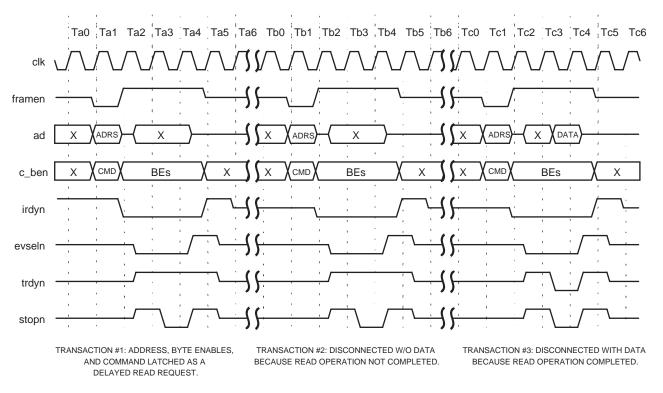

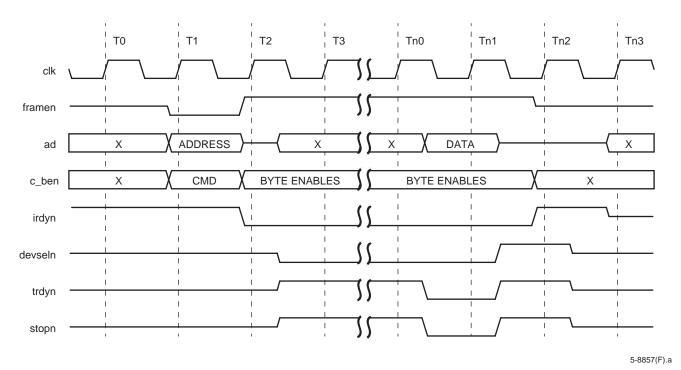

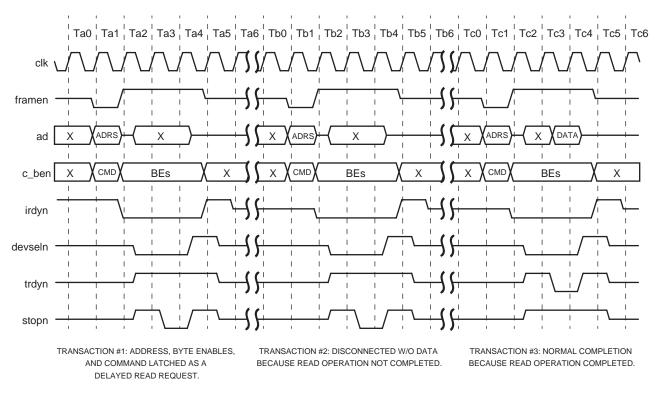

#### ■ Target:

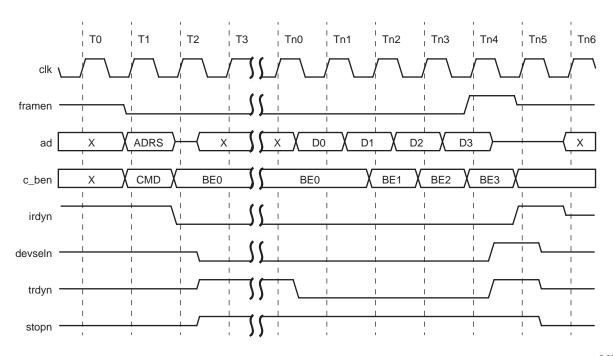

- Responds legally to all command codes: interrupt acknowledge, special cycle, and reserved commands ignored; memory read multiple and line handled as memory read; memory write and invalidate handled as memory write.

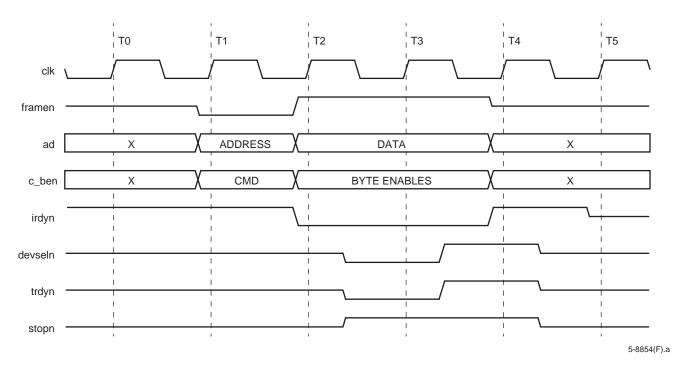

- Implements Target abort, disconnect, retry, and wait cycles.

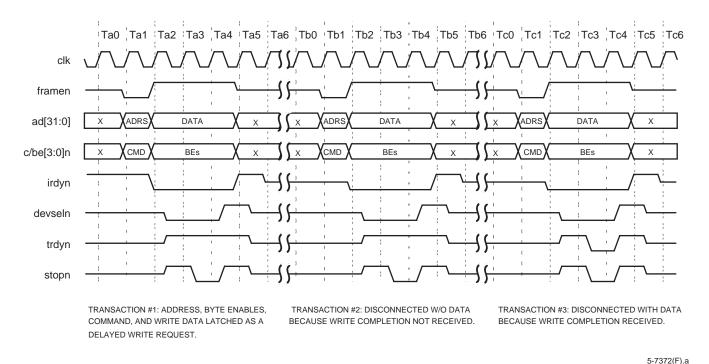

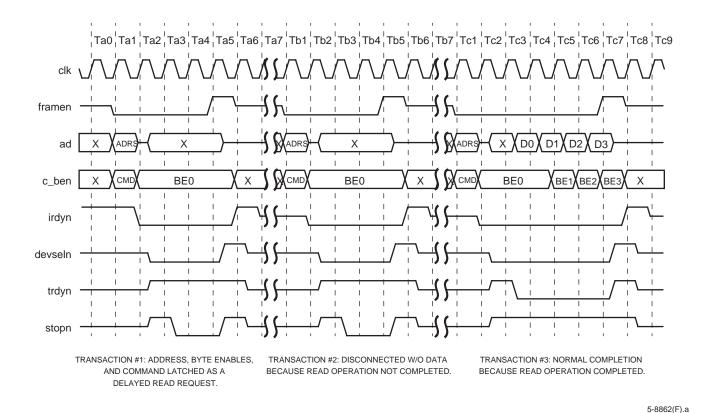

- Handles delayed transactions.

- Handles fast back-to-back transactions.

- Method of handling retries is programmable at FPGA configuration to allow tailoring to different Target data access latencies.

- Decodes at medium speed.

- Provides option to delay PCI access until FIFO is full on Target reads to increase PCI bandwidth.

- Supports dual-address cycles (both as Master and Target).

- Supports all six base address registers (BARs), as either memory (32-bit or 64-bit) or I/O. Any legal page size can be independently specified for each BAR during FPGA configuration.

- Independent Master and Target clocks can be supplied to the PCI FIFO interface from the FPGA-based logic.

- Provides versatile clocking capabilities with FPGA clocks sourced from PCI bus clock or elsewhere.

FIFO interface buffers asynchronous clock domains between the PCI interface and FPGA-based logic.

- PCI interface timing: meets or exceeds 33 MHz, 50 MHz, and 66 MHz PCI requirements.

| Parameter            | 33 MHz  | 50 MHz  | 66 MHz  |

|----------------------|---------|---------|---------|

| Device Clock = > Out | 11.0 ns | 7.5 ns  | 6.0 ns  |

| Device Setup Time    | 7.0 ns  | 4.5 ns  | 3.0 ns  |

| Board Prop. Delay    | 10.0 ns | 6.5 ns  | 5.0 ns  |

| Board Clock Skew     | 2.0 ns  | 1.5 ns  | 1.0 ns  |

| Total Budget         | 30.0 ns | 20.0 ns | 15.0 ns |

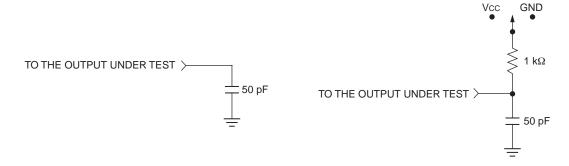

| Load Capacitance     | 50 pF   | 50 pF   | 10 pF   |

- Configuration options:

- Class code, revision ID.

- Latency timer.

- Cache line size.

- Subsystem ID.

- Subsystem vendor ID.

- Maximum latency, minimum grant.

- Interrupt line.

- Hot Plug/Hot Swap capability.

- Generates interrupts on intan as directed by the FPGA.

- PCI I/O output drivers can be programmed for fast or slew-limited operation.

- Automatically detects 5 V or 3.3 V PCI bus signaling environment and provides appropriate I/O signaling, under 3.3 V commercial conditions.

- Ideally suited for such applications as:

- PCI-based graphics/video/multimedia.

- Bridges to ISA/EISA/MCA, LAN, SCSI, Ethernet, ATM, or other bus architectures.

- High-bandwidth data transfer in proprietary systems.

# **FPSC Highlights**

- Implemented as an embedded core into the advanced Series 3+ ORCA FPSC architecture.

- Allows the user to integrate the core with up to 120K gates of programmable logic, all in one device, and provides up to 259 user I/O pins in addition to the PCI interface pins.

- FPGA portion retains all of the features of the ORCA 3 FPGA architecture:

- High-performance, cost-effective, 0.25 μm

5-level metal technology.

- Twin-quad programmable function unit (PFU)

architecture with eight 16-bit look-up tables

(LUTs) per PFU, organized in two nibbles for use

in nibble- or byte-wide functions. Allows for mixed

arithmetic and logic functions in a single PFU.

# FPSC Highlights (continued)

- Softwired LUTs (SWL) allow fast cascading of up to three levels of LUT logic in a single PFU.

- Supplemental logic and interconnect cell (SLIC) provides 3-statable buffers, up to 10-bit decoder, and PAL\*-like AND-OR-INVERT (AOI) in each programmable logic cell (PLC).

- Up to three ExpressCLK inputs allow extremely fast clocking of signals on- and off-chip plus access to internal general clock routing.

- Dual-use microprocessor interface (MPI) can be used for configuration, readback, device control, and device status, as well as for a general-purpose interface to the FPGA. Glueless interface to i960<sup>†</sup> and PowerPC<sup>‡</sup> processors with user-configurable address space provided.

- Programmable clock manager (PCM) adjusts clock phase and duty cycle for input clock rates from 5 MHz to 120 MHz. The PCM may be combined with FPGA logic to create complex functions, such as digital phase-locked loops (DPLL), frequency counters, and frequency synthesizers or clock doublers. Two PCMs are provided per device.

- True internal 3-state, bidirectional buses with simple control provided by the SLIC.

- 32 x 4 RAM per PFU, configurable as single or dual port. Create large, fast RAM/ROM blocks (128 x 8 in only eight PFUs) using the SLIC decoders as bank drivers.

- Built-in boundary scan (*IEEE* §1149.1 JTAG) and TS\_ALL testability function to 3-state all I/O pins.

- High-speed on-chip interface provided between FPGA logic and embedded core to reduce bottlenecks typically found when interfacing off-chip.

- Supported in two packages: 352-pin PBGA and 680-pin PBGAM.

- \* PAL is a trademark of Advanced Micro Devices, Inc.

- † *i960* is a registered trademark of Intel Corporation.

- ‡ PowerPC is a registered trademark of International Business Machines Corporation.

- § *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

**Note**: This document will conform to the nomenclature of the PCI Local Bus Specification, as follows:

| Term     | Meaning |

|----------|---------|

| byte     | 8 bits  |

| word     | 16 bits |

| DWORD    | 32 bits |

| Quadword | 64 bits |

# **Software Support**

- Supported by ORCA Foundry software and thirdparty CAE tools for implementing ORCA Series 3+ devices and simulation/timing analysis with embedded PCI bus core.

- PCI core configuration options and simulation netlists generated by FPSC Configuration Manager utility in ORCA Foundry software.

- Preference files provided for timing interface between PCI bus core and FPGA logic.

# **Description**

#### What Is an FPSC?

FPSCs, or field-programmable system chips, are devices that combine field-programmable logic with ASIC or mask-programmed logic on a single device. FPSCs provide the time to market and flexibility of FPGAs, the design effort savings of using soft intellectual property (IP) cores, and the speed, design density, and economy of ASICs.

#### **FPSC Overview**

Lattice's Series 3+ FPSCs are created from Series 3 ORCA FPGAs. To create a Series 3+ FPSC, several rows of programmable logic cells (see FPGA Logic Overview section for FPGA logic details) are removed from a Series 3 ORCA FPGA, and the area is replaced with an embedded logic core. Other than replacing some FPGA gates with ASIC gates, at greater than 10:1 efficiency, none of the FPGA functionality is changed—all of the Series 3 FPGA capability is retained: MPI, PCMs, boundary scan, etc. The rows of programmable logic are replaced at the bottom of the device, allowing pins on the bottom and sides of the replaced rows to be used as I/O pins for the embedded core. The remainder of the device pins retain their FPGA functionality as do special function FPGA pins within the embedded core area.

## **FPSC Gate Counting**

The total gate count for an FPSC is the sum of its embedded core (standard-cell/ASIC gates) and its FPGA gates. Because FPGA gates are generally expressed as a usable range with a nominal value, the total FPSC gate count is sometimes expressed in the same manner. Standard-cell/ASIC gates are, however, 10 to 25 times more silicon area efficient than FPGA gates. Therefore, an FPSC with an embedded function is gate equivalent to an FPGA with a much larger gate count.

#### FPGA/Embedded Core Interface

The interface between the FPGA logic and the embedded core is designed to look like FPGA I/Os from the FPGA side, simplifying interface signal routing and providing a unified approach with general FPGA design. Effectively, the FPGA is designed as if signals were going off of the device to the embedded core, but the on-chip interface is much faster than going off-chip and requires less power. All of the delays for the interface are precharacterized and accounted for in the *ORCA* Foundry Development System.

Clock spines also can pass across the FPGA/embedded core boundary. This allows for fast, low-skew clocking between the FPGA and the embedded core. Many of the special signals from the FPGA, such as DONE and global set/reset, are also available to the embedded core, making it possible to fully integrate the embedded core with the FPGA as a system.

For even greater system flexibility, FPGA configuration RAMs are available for use by the embedded core. This allows for user-programmable options in the embedded core, in turn allowing for greater flexibility. Multiple embedded core configurations may be designed into a single device with user-programmable control over which configurations are implemented, as well as the capability to change core functionality simply by reconfiguring the device.

## **ORCA** Foundry Development System

The *ORCA* Foundry Development System is used to process a design from a netlist to a configured FPSC. This system is used to map a design onto the *ORCA* architecture and then place and route it using *ORCA* Foundry's timing-driven tools. The development system also includes interfaces to, and libraries for, other popular CAE tools for design entry, synthesis, simulation, and timing analysis.

The ORCA Foundry Development System interfaces to front-end design entry tools and provides the tools to produce a configured FPSC. In the design flow, the user defines the functionality of the FPGA portion of the FPSC and embedded core settings at two points in the design flow: at design entry and at the bit stream generation stage.

# **Description** (continued)

Following design entry, the development system's map, place, and route tools translate the netlist into a routed FPSC. A static timing analysis tool is provided to determine device speed and a back-annotated netlist can be created to allow simulation. Timing and simulation output files from *ORCA* Foundry are also compatible with many third-party analysis tools. Its bit stream generator is then used to generate the configuration data which is loaded into the FPSC's internal configuration RAM. When using the bit stream generator, the user selects options that affect the functionality of the FPSC. Combined with the front-end tools, *ORCA* Foundry produces configuration data that implements the various logic and routing options discussed in this data sheet.

## **FPSC Design Kit**

Development is facilitated by an FPSC Design Kit which, together with *ORCA* Foundry and third-party synthesis and simulation engines, provides all software and documentation required to design and verify an FPSC implementation. Included in the kit are the FPSC Configuration Manager, *Verilog\** and *VHDL\** gate-level structural netlists, all necessary synthesis libraries, and complete online documentation. The kit's software couples with *ORCA* Foundry under the control of the *ORCA* Foundry Control Center (OFCC), providing a seamless FPSC design environment. More information can be obtained by visiting the *ORCA* website or contacting a local sales office, both listed on the last page of this document.

#### **FPGA Logic Overview**

ORCA Series 3 FPGA logic is a new generation of SRAM-based FPGA logic built on the successful Series 2 FPGA line, with enhancements and innovations geared toward today's high-speed designs and tomorrow's systems on a single chip. Designed from the start to be synthesis friendly and to reduce place and route times while maintaining the complete routability of the ORCA Series 2 devices, the Series 3 more than doubles the logic available in each logic block and incorporates system-level features that can further reduce logic requirements and increase system speed. ORCA Series 3 devices contain many new patented enhancements and are offered in a variety of packages, speed grades, and temperature ranges.

ORCA Series 3 FPGA logic consists of three basic elements: programmable logic cells (PLCs), programma-

ble input/output cells (PICs), and system-level features. An array of PLCs is surrounded by PICs. Each PLC contains a programmable function unit (PFU), a supplemental logic and interconnect cell (SLIC), local routing resources, and configuration RAM. Most of the FPGA logic is performed in the PFU, but decoders, *PAL*-like functions, and 3-state buffering can be performed in the SLIC. The PICs provide device inputs and outputs and can be used to register signals and to perform input demultiplexing, output multiplexing, and other functions on two output signals. Some of the system-level functions include the new microprocessor interface (MPI) and the programmable clock manager (PCM).

## **PLC Logic**

Each PFU within a PLC contains eight 4-input (16-bit) look-up tables (LUTs), eight latches/flip-flops (FFs), and one additional flip-flop that may be used independently or with arithmetic functions.

The PFU is organized in a twin-quad fashion: two sets of four LUTs and FFs that can be controlled independently. LUTs may also be combined for use in arithmetic functions using fast-carry chain logic in either 4-bit or 8-bit modes. The carry-out of either mode may be registered in the ninth FF for pipelining. Each PFU may also be configured as a synchronous 32 x 4 single- or dual-port RAM or ROM. The FFs (or latches) may obtain input from LUT outputs or directly from invertible PFU inputs, or they can be tied high or tied low. The FFs also have programmable clock polarity, clock enables, and local set/reset.

The SLIC is connected to PLC routing resources and to the outputs of the PFU. It contains 3-state, bidirectional buffers and logic to perform up to a 10-bit AND function for decoding, or an AND-OR with optional INVERT (AOI) to perform *PAL*-like functions. The 3-state drivers in the SLIC and their direct connections to the PFU outputs make fast, true 3-state buses possible within the FPGA logic, reducing required routing and allowing for real-world system performance.

<sup>\*</sup> Verilog and VHDL are registered trademarks of Cadance Design Systems, Inc.

## **Description** (continued)

## **PIC Logic**

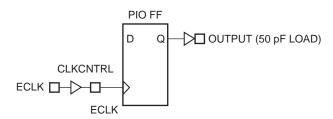

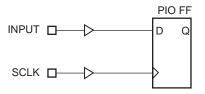

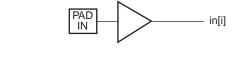

The Series 3 PIC addresses the demand for everincreasing system clock speeds. Each PIC contains four programmable inputs/outputs (PIOs) and routing resources. On the input side, each PIO contains a fast-capture latch that is clocked by an ExpressCLK. This latch is followed by a latch/FF that is clocked by a system clock from the internal general clock routing. The combination provides for very low setup requirements and zero hold times for signals coming on-chip. It may also be used to demultiplex an input signal, such as a multiplexed address/data signal, and register the signals without explicitly building a demultiplexer. Two input signals are available to the PLC array from each PIO, and the *ORCA* Series 2 capability to use any input pin as a clock or other global input is maintained.

On the output side of each PIO, two outputs from the PLC array can be routed to each output flip-flop, and logic can be associated with each I/O pad. The output logic associated with each pad allows for multiplexing of output signals and other functions of two output signals.

The output FF, in combination with output signal multiplexing, is particularly useful for registering address signals to be multiplexed with data, allowing a full clock cycle for the data to propagate to the output. The I/O buffer associated with each pad is the same as the *ORCA* Series 3 buffer.

## **System Features**

The Series 3 also provides system-level functionality by means of its dual-use microprocessor interface (MPI) and its innovative programmable clock manager (PCM). These functional blocks allow for easy glueless system interfacing and the capability to adjust to varying conditions in today's high-speed systems. Since these and all other Series 3 features are available in every Series 3+ FPSC, they can also interface to the embedded core providing for easier system integration.

#### Routing

The abundant routing resources of *ORCA* Series 3 FPGA logic are organized to route signals individually or as buses with related control signals. Clocks are routed on a low-skew, high-speed distribution network and may be sourced from PLC logic, externally from any I/O pad, or from the very fast ExpressCLK pins.

ExpressCLKs may be glitchlessly and independently enabled and disabled with a programmable control signal using the new StopCLK feature. The improved PIC routing resources are now similar to the patented intra-PLC routing resources and provide great flexibility in moving signals to and from the PIOs. This flexibility translates into an improved capability to route designs at the required speeds when the I/O signals have been locked to specific pins.

## Configuration

The FPGA logic's functionality is determined by internal configuration RAM. The FPGA logic's internal initialization/configuration circuitry loads the configuration data at powerup or under system control. The RAM is loaded by using one of several configuration modes, including serial EEPROM, the microprocessor interface, or the embedded function core.

## **Boundary Scan**

Boundary scan is implemented in the OR3LP26B device as with any of the OR3LXXB family of parts. The PCI core side of the device contains the same boundary-scan registers. After performing a boundary-scan test, it is highly recommended that the device be reset through the PCI **rstn** pin. This reset will clear out any PCI core internal registers that may have been set during the boundary-scan tests.

#### **More Series 3 Information**

For more information on Series 3 FPGAs, please refer to the Series 3 FPGA data sheet, available on the Lattice website.

#### **OR3LP26B Overview**

#### **Device Layout**

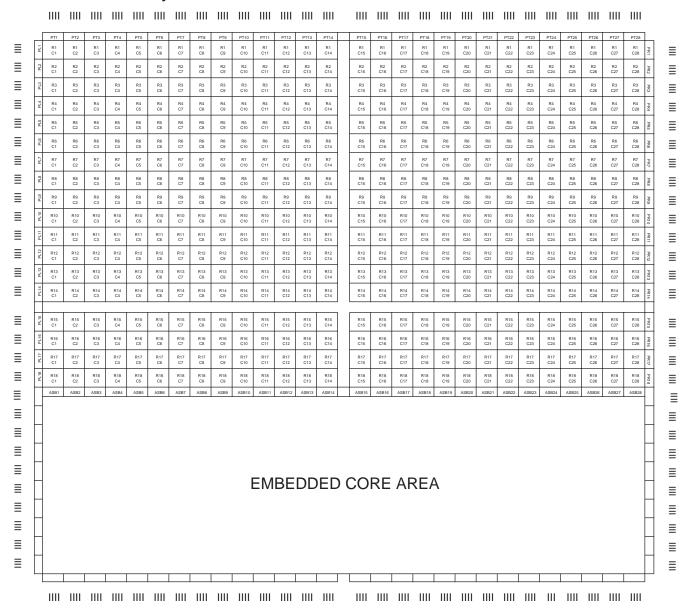

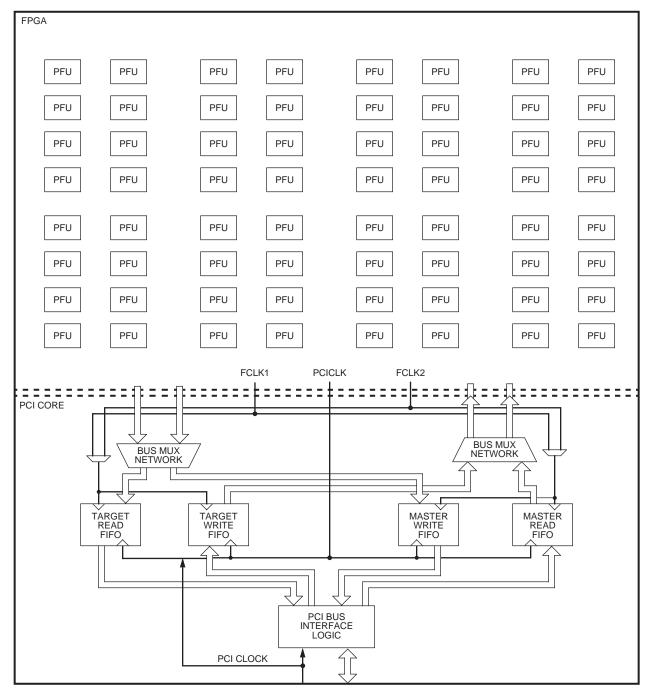

The OR3LP26B FPSC provides a PCI local bus core (with FIFOs) combined with FPGA logic. The device is based on a 2.5 V OR3L125B FPGA. The OR3L125B has a 28 x 28 array of programmable logic cells (PLCs). For the OR3LP26B, the bottom ten rows of PLCs in the array were replaced with the embedded PCI bus core. Table 3 shows a schematic view of the OR3LP26B. The upper portion of the device is an 18 x 28 array of PLCs surrounded on the left, top, and right by programmable input/output cells (PICs). At the bottom of the PLC array are the core interface cells (CICs) connecting to the embedded core region. The embedded core region contains the PCI bus functionality of the device. It is surrounded on the left, bottom, and right by PCI bus dedicated I/Os as well as power and special function FPGA pins. Also shown are the interquad routing blocks (hIQ, vIQ) present in the Series 3 FPGA devices. System-level functions (located in the corners of the PLC array), routing resources, and configuration RAM are not shown in Figure 1.

#### **PCI Local Bus**

PCI local bus, or simply, PCI bus, has become an industry-standard interface protocol for use in applications ranging from desktop PC busing to high-bandwidth backplanes in networking and communications equipment. The PCI bus specification\* provides for both 5 V and 3.3 V signaling environments. The interface clock speed is specified in the range from dc to 66 MHz with detailed specifications at 33 MHz and 66 MHz as well as recommendations for 50 MHz operation. Data paths are defined as either 32-bit or 64-bit. These data path and frequency combinations allow for the peak data transfer rates described in Table 2.

Table 2. PCI Local Bus Data Rates

| Clock<br>Frequency<br>(MHz) | Data Path Width (bits) | Peak Data Rate<br>(Mbytes) |

|-----------------------------|------------------------|----------------------------|

| 33                          | 32                     | 132                        |

| 33                          | 64                     | 264                        |

| 66                          | 32                     | 264                        |

| 66                          | 64                     | 528                        |

The PCI bus is electrically specified so that no glue logic is required to interface to the bus—PCI devices interface directly to the PCI bus. Other features include registers for device and subsystem identification and autoconfiguration, support for 64-bit addressing, and multi-Master capability that allows any PCI bus Master access to any PCI bus Target.

<sup>\*</sup> PCI Local Bus Specification Rev. 2.2, PCI SIG, December 18, 1998.

## OR3LP26B Overview (continued)

#### Table 3. OR3LP26B Array

#### OR3LP26B Overview (continued)

#### **OR3LP26B PCI Bus Core Overview**

The OR3LP26B embedded core comprises a PCI bus interface with independent Master and Target controllers, FIFO memories and control logic for data buffering, a dual-/quad-port interface to the FPGA logic which performs data packing and multiplexing, and logic to support embedded core and FPGA configuration. Each of these areas is briefly described in the following paragraphs. A detailed description of all of the features and functionality of the OR3LP26B embedded core is provided in the next section.

#### **PCI Bus Interface**

The OR3LP26B PCI bus interface is compliant to Revision 2.2 of the PCI Local Bus specification. It is capable of no-wait-state, full-burst operation at all of the rate/data width combinations described in Table 2 as well as at a 50 MHz specification that provides a speed increase over the 33 MHz specification and a larger bus loading capability than the 66 MHz specification. The OR3LP26B operates in either the 3.3 V or 5 V PCI signaling environment and is automatically configured for the appropriate environment by a PCI bus **vio** pin.

Independent Master and Target controllers are provided for use in systems requiring Master/Target or Target only operation. Six 32-bit base address registers (BARs) are provided for choosing the address space of the PCI device, and these six registers can be combined in pairs to produce 64-bit BARs. Dual address cycles are supported in both 32-bit and 64-bit addressing modes. The BARs work in either the I/O or the memory space of the device, and can be configured as prefetchable or nonprefetchable.

#### OR3LP26B Overview (continued)

Independent data paths exist for the Master and Target controllers. This allows for separate operation of Master and Target functions, and the capability for a Master to talk to a Target on the same device.

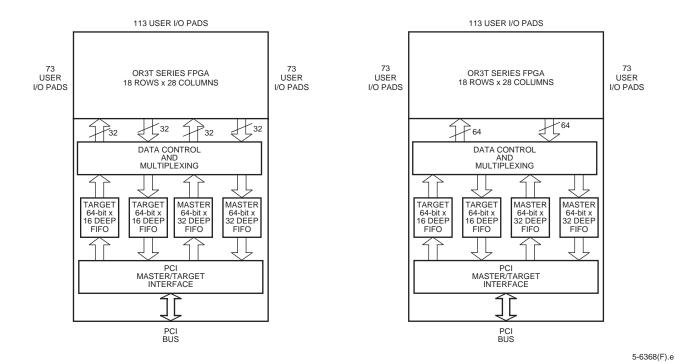

In dual-port mode, the Master and Target controllers share two 64-bit data paths, one in each direction, between the FIFOs and the FPGA logic. This provides for full-rate transfers in both 32- and 64-bit PCI bus operation.

Quad-port mode provides two 32-bit data paths for each controller: one in each direction. This mode allows for simultaneous reads and writes on either the Master or Target controller.

Diagrams for dual-port and quad-port operation are shown in Figure 1.

Note: User I/O pin count includes three ExpressCLK pins.

Figure 1. ORCA OR3LP26B PCI FPSC Block Diagram

## **Embedded Core Options/FPGA Configuration**

In addition to the Series 3 FPGA configuration modes (less Master parallel), the OR3LP26B can also be configured via the PCI bus. Configuration as discussed here has two meanings. There is configuration of the FPGA logic, and there is configuration of the options available in the embedded core. Both are accomplished through the FPGA configuration process (some PCI configuration options may also be set via registers within the PCI bus core). Readback of FPGA and PCI core options is also possible using the PCI bus or Series 3 FPGA readback modes. The PCI bus core will be functional in the default PCI bus configuration space, as defined in the PCI bus 2.2 specification, prior to an initial configuration of the FPGA logic or the embedded core options.

# **PCI Bus Core Detailed Description**

The following sections describe the operation of the embedded core PCI bus interface.

## **PCI Bus Commands**

The PCI core supports all commands required by the PCI specification. The following table describes each command. Subsequent sections will describe the protocols in which the commands are used.

**Table 4. PCI Bus Command Descriptions**

| Command<br>Code<br>(Binary) | Command                       | Master<br>Generates | Target<br>Accepts | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------------------|-------------------------------|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0000                        | Interrupt<br>Acknowl-<br>edge | _                   | _                 | Only implemented as Master by agents that interface to the system CPU and as Target by agents that incorporate the system interrupt controller.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 0001                        | Special<br>Cycle              | _                   | _                 | Target ignores, per PCI Specification section 3.6.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0010                        | I/O Read                      | V                   | V                 | Fully implemented.  Target: Bursting is prevented by disconnecting with data on the first data phase. If signal deltrn is asserted low, I/O (and memory) reads are handled as delayed transactions; no wait-states are generated. If signal deltrn is deasserted high, the unit waits for the data from the FPGA application, inserting wait-states (up to the maximum allowed, after which a retry is issued).  Master: Bursting is allowed, and no wait-states are generated.                                                                             |  |

| 0011                        | I/O Write                     | V                   | V                 | Fully implemented.  Target: Bursting is prevented by disconnecting with data on the first data phase. If signal deltrn is asserted low, I/O writes are handled as delayed transactions; no wait-states are generated.  Master: Bursting is allowed, and no wait-states are generated.                                                                                                                                                                                                                                                                       |  |

| 0100                        | (reserved)                    | _                   | _                 | Target ignores, per PCI Specification section 3.1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0101                        | (reserved)                    | _                   | _                 | Target ignores, per PCI Specification section 3.1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0110                        | Memory<br>Read                | V                   | V                 | Fully implemented.  Target: Bursting is allowed. If signal deltrn is asserted low, memory (and I/O) reads are handled as delayed transactions. If signal deltrn is deasserted high, the unit waits for the data from the FPGA application, inserting wait-states (up to the maximum allowed, after which a retry is issued). If signal trburstpendn is asserted low and the Target Read FIFO is empty, wait-states are inserted (up to the maximum allowed, after which a retry is issued).  Master: Bursting is allowed, and no wait-states are generated. |  |

Table 4. PCI Bus Command Descriptions (continued)

| Command<br>Code<br>(Binary) | Command                           | Master<br>Generates | Target<br>Accepts | Description                                                                                                                                                                                                                                                                                     |

|-----------------------------|-----------------------------------|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0111                        | Memory<br>Write                   | V                   | V                 | Fully implemented.  Target: Writes are posted, bursting is allowed, and no wait-states are generated.  Master: Bursting is allowed, and no wait-states are generated.                                                                                                                           |

| 1000                        | (reserved)                        | _                   | _                 | Target ignores, per PCI Specification section 3.1.1.                                                                                                                                                                                                                                            |

| 1001                        | (reserved)                        | _                   | _                 | Target ignores, per PCI Specification section 3.1.1.                                                                                                                                                                                                                                            |

| 1010                        | Configura-<br>tion Read           | V                   | V                 | Fully implemented.  Target: Bursting is disallowed, and no wait-states are generated.  Target disconnects with data on first data word. The FPGA portion of the device is not involved in Target configuration transactions.  Master: Bursting is allowed, and no wait-states are generated.    |

| 1011                        | Configura-<br>tion Write          | V                   | V                 | Fully implemented.  Target: Bursting is disallowed, and no wait-states are generated.  Target disconnects with data on first data word. The FPGA portion of the device is not involved in Target configuration transactions.  Master: Bursting is allowed, and no wait-states are generated.    |

| 1100                        | Memory<br>Read<br>Multiple        | V                   | V                 | Fully implemented. Both the Master and the Target treat this instruction the same as a memory read (0110); the user's FPGA logic is responsible for ensuring that the Master operation meets the special requirement that the read request ends on a cacheline boundary.                        |

| 1101                        | Dual<br>Access<br>Cycle           | V                   | V                 | Fully implemented. Per PCI Specification section 3.9, the PCI core will automatically convert a 64-bit address to a 32-bit address if the upper 32 bits are all zeros.                                                                                                                          |

| 1110                        | Memory<br>Read Line               | V                   | V                 | Fully implemented. Both the Master and the Target treat this instruction the same as a memory read (0110); the user's FPGA logic is responsible for ensuring that the Master operation meets the special requirement that the read request continues to the next cacheline boundary.            |

| 1111                        | Memory<br>Write and<br>Invalidate | V                   | V                 | Fully implemented. Both the Master and the Target treat this instruction the same as a memory write (0111); the user's FPGA logic is responsible for ensuring that the Master operation meets the special requirement that writes of complete cachelines, with all byte enables, are performed. |

# **PCI Bus Core Detailed Description**

(continued)

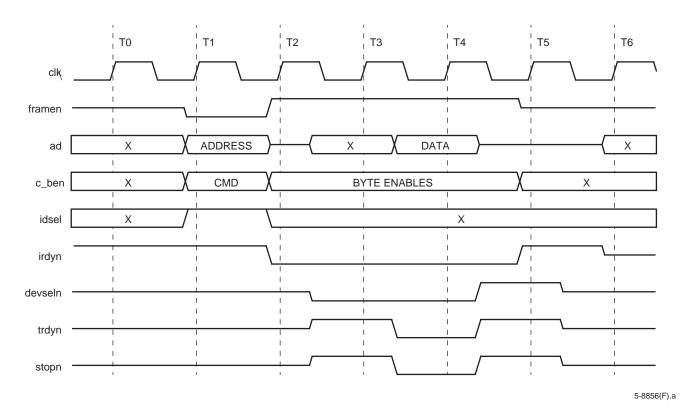

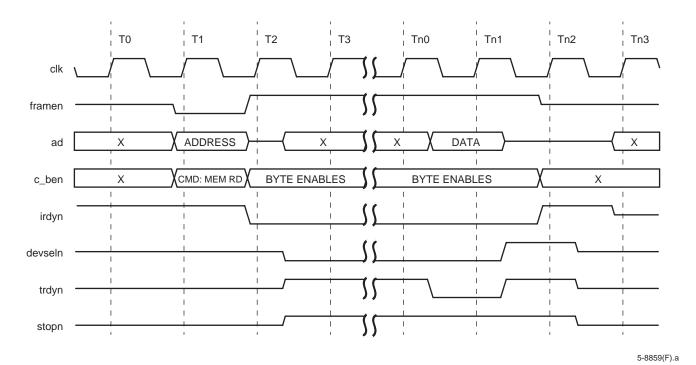

#### **PCI Protocol Fundamentals**

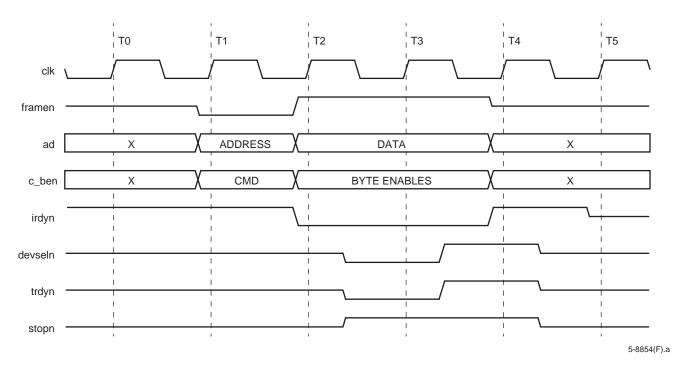

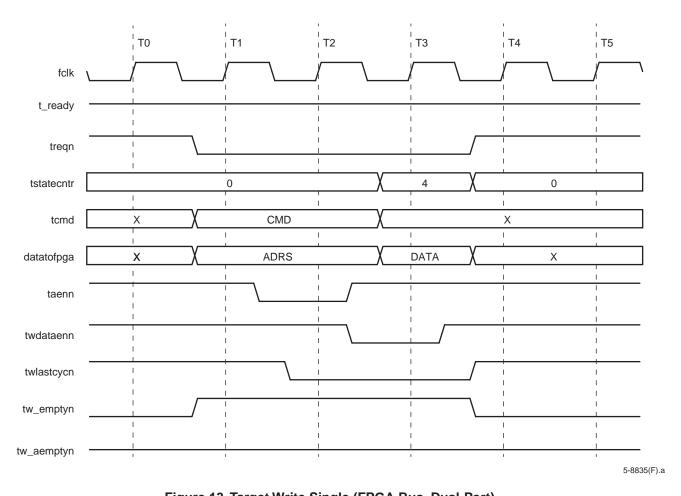

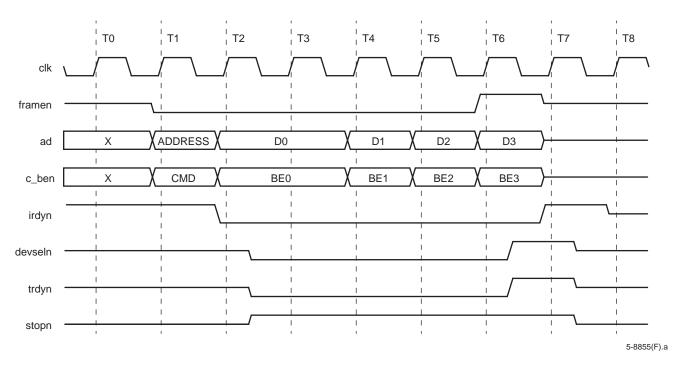

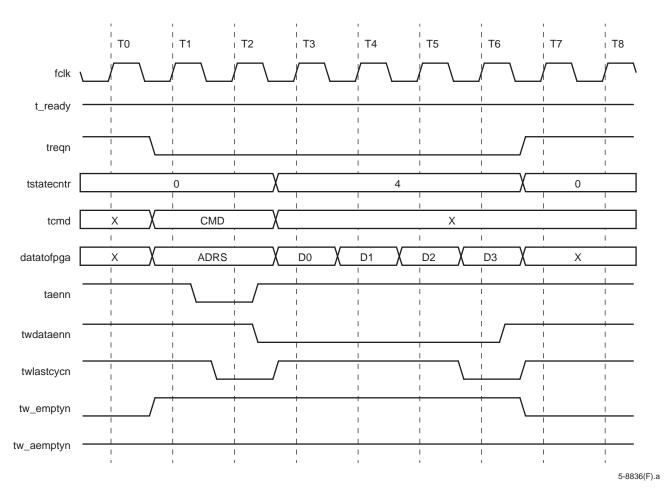

#### **Basic Transfer Control**

The following paragraphs describe various aspects of the PCI protocol and the way they are handled by the PCI core.

Addressing. The PCI Specification defines three types of address spaces. The first, configuration address space, is a physical address of space and is intended as a means for powerup software to identify agents and configure them before other address spaces have allocated. The second, I/O address space, is intended for mapping control functions. Control function page sizes in configuration space should be no more than 256 bytes. The third, memory address space, is intended for bulk data transfer. It has features to facilitate this, such as special commands for cache implementation, large page sizes, and mechanisms for prefetching. The PCI core handles all three address space types as both a Master and a Target.

Byte Alignment. On all write operations (configuration, I/O, and memory space, and including the memory write and invalidate instruction), for both the PCI core's Master and Target functions, byte enables are fully implemented from/to the FPGA interface. Note, however, that even though the PCI core implements the ability to control byte enables for the memory write and invalidate instruction, the PCI Specification requires that this instruction assert all byte enables, and this is the FPGA application's responsibility. On read operations, the utility of byte enables is more dubious since the data must be enroute from the PCI bus from Target to Master, at the time that the corresponding byte enables are enroute on the PCI bus Master to Target (unless wait-states are inserted). The PCI core, therefore, does not implement byte enable control for Master or Target reads. Byte enables on master read operations are always asserted, and target ignores the byte enables that are sent, in accordance with PCI Specification requirements.

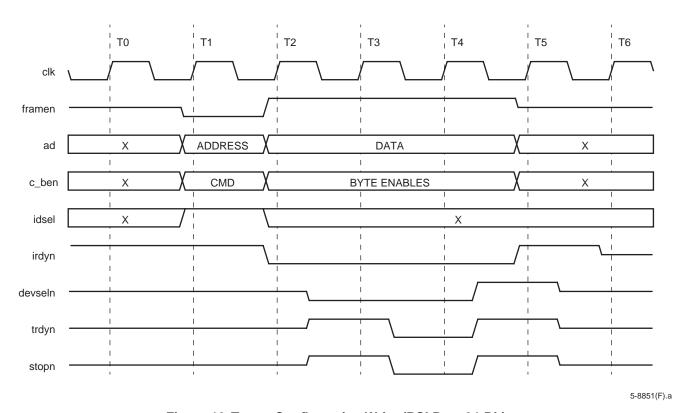

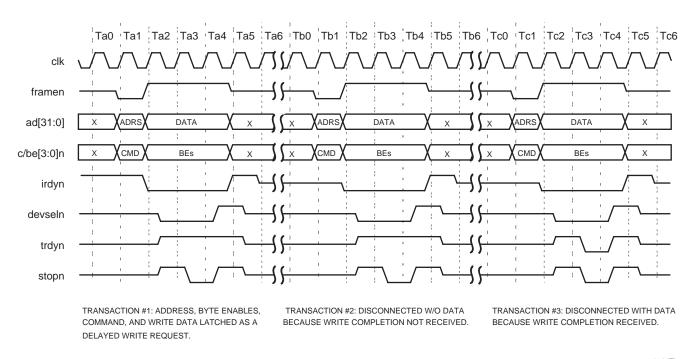

#### **Device Selection (devseln)**

The target is responsible for responding to a master's request by asserting the PCI bus signal **devseln**. **devseln** may be asserted one, two, or three clocks after the address phrase of a transaction, corresponding to fast, medium, or slow decode, respectively. The PCI core's target is capable of preforming a medium-speed decode response. The decode response speed has a significant impact on the overall latency and bandwidth of nonburst PCI transactions, but its impact decreases greatly for burst transactions, particularly for burst lengths of the size of the PCI core's FIFOs.

#### Address/Data Stepping

Stepping is an optional feature added to the PCI Specification to accommodate agents whose bus drive capability is insufficient to handle large groups of signals changing state in one clock cycle. Continuous stepping allows weak drivers multiple cycles for signal transition. Discrete stepping partitions the bus into two or more groups of bits that transition on successive clock cycles. However, stepping exacts a heavy toll on performance, cutting maximum bandwidth by at least 50% and increasing latency. The PCI core is designed for maximum throughput with high-performance buffers, so stepping is unnecessary and not implemented. The wait cycle control, bit 7 of the command register, is therefore hardwired to a zero.

#### **Reset Operation**

The PCI bus contains a signal, **rstn**, that performs a PCI reset function. When the reset occurs, all state machines in the ASIC are placed in their idle state, the configuration space BARs are reset to their mask values, and the command registers are reset. The reset does not reset the FPGA logic. The PCI reset signal is fed from the ASIC to the FPGA logic to be used by the designer.

#### Interrupt Acknowledge

The interrupt acknowledge command is a read by the system CPU implicitly addressed to the system interrupt controller. Other agents, including the PCI core, are not required to implement this instruction; the PCI core's Master does not generate it and its Target ignores it.

# **PCI Bus Core Detailed Description**

(continued)

#### **Arbitration Parking**

The PCI Specification requires that all master agents properly handle bus parking, which means that when that agent receives an asserted **gntn** without the agent having asserted **reqn**, the agent still must drive signal **par** and buses AD and c\_ben. The PCI core meets this requirement.

#### **Parity**

The PCI core implements all required and optional features, including the following:

- Master generates parity on all addresses placed on the bus.

- Sending agent generates parity on all data placed on the bus.

- Target calculates parity on all addresses received from the bus.

- Receiving agent calculates parity on all data received from the bus.

- The detected parity error bit in the status register is set whenever an agent calculates corrupted parity.

- The signal **perrn** is generated whenever an agent calculates corrupted parity and the parity error response bit is set in the command register.

#### **66 MHz Operation**

The PCI core is fully compliant to PCI Specification requirements at all clock rates up to 66 MHz. All 33 MHz requirements are also met.

#### **Timing Budget**

The PCI core's timing budget is summarized in Table 5. Note that the 66 MHz timing requirements only allow 5 ns for signal propagation (TPROP), as compared to 10 ns at 33 MHz. The effect of the reduction is to also reduce the number of agents that the bus can support, although the actual number is not specified in the PCI Specification and is dependent on the design of the hardware components. The four components of the timing budget are TVAL (valid output delay), TPROP (propagation time), TSU (input setup time), and TSKEW (clock skew); of these, only TVAL and TSU are controlled by the PCI component, and TPROP and TSKEW are system parameters. Table 5 includes a third column (also shown in the PCI Specification). This column indicates the performance attainable if all 66 MHz requirements are met except TPROP = 10 ns, which is the 33 MHz

value. In this case, the total budget increases from 15 ns (66 MHz) to 20 ns (50 MHz).

**Table 5. Timing Budgets**

| Timing Element        | 33 MHz | 50 MHz | 66 MHz | Unit |

|-----------------------|--------|--------|--------|------|

| Cycle Time            | 30.0   | 20.0   | 15.0   | ns   |

| Valid Output<br>Delay | 11.0   | 7.5    | 6.0    | ns   |

| Propagation<br>Time   | 10.0   | 6.5    | 5.0    | ns   |

| Input Setup Time      | 7.0    | 4.5    | 3.0    | ns   |

| Clock Skew            | 2.0    | 1.5    | 1.0    | ns   |

#### 64-Bit Addressing

The PCI core fully supports 64-bit addressing, whether or not the PCI core is configured to utilize the 64-bit data extension. When the PCI core is a 64-bit target being addressed by 64-bit master, the PCI core will decode the address one cycle faster so that dual-address operation will have no performance impact; see PCI Specification section 3.9 for details.

Section 3.9 of the PCI Specification also states that a Master that supports 64-bit addressing must nevertheless generate requests utilizing a single address instead of a dual address when the upper 32 bits are all zeros. This shortens the request time by one cycle when communicating with 32-bit Targets. It is the FPGA application's responsibility to ensure that this requirement is met.

#### **FIFO Memories and Control**

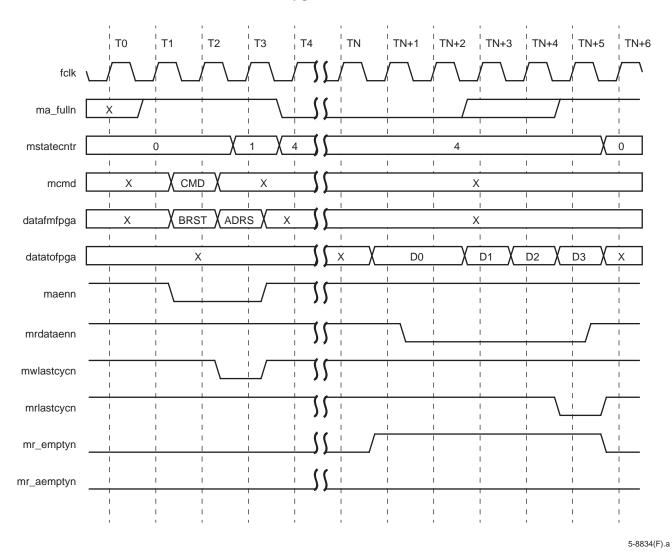

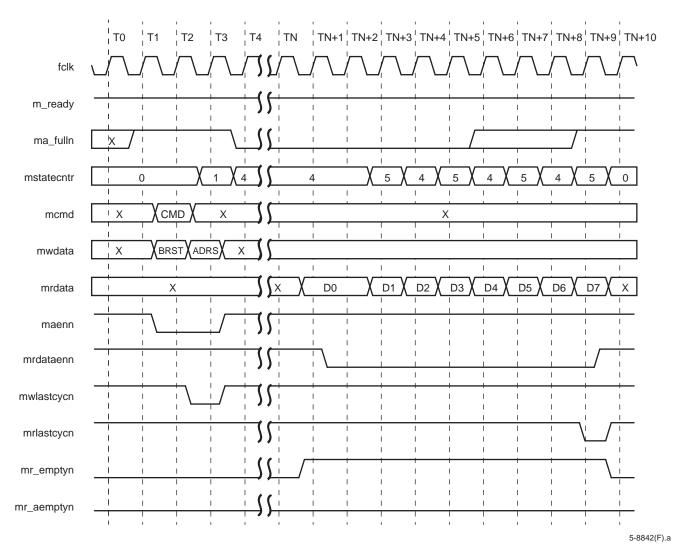

The OR3LP26B embedded core contains four FIFO memories and supporting control logic. Two FIFOs are for the master interface data and two for the target interface data. These FIFOs are always configured to operate in 64-bit mode and also carry byte enable bits on a per-byte basis (e.g., the 64-bit FIFO actually carries 64 bits of data and 8 byte enable bits for a total of 72 bits). During 32-bit transactions, the FPSC will pack the data to fully utilize the memories. All FIFOs have four flags: Full, Almost Full (Full-4), Empty, and Almost Empty (Empty+4). (See Table 6.) The FPGA application is provided with the Full/Empty signal and Almost Full/Empty signal associated with the FPGA side of the FIFO. In addition, the FPGA application is provided with the PCI side's Full/Empty signal (but not the Almost Full/Empty signal), to enable checking for operation completion. Clocking for the FPGA side of all FIFOs is flexible, with options for different clocks for the Master and Target FIFOs, sourced by the FPGA logic, or by the PCI bus clock.

Table 6. FIFO Flags Provided to FPGA Application

|                  | Write Operation    |          | <b>Read Operation</b> |           |

|------------------|--------------------|----------|-----------------------|-----------|

|                  | FPGA Side          | PCI Side | FPGA Side             | PCI Side  |

| Master Operation | mw_fulln mw_emptyn |          | mr_emptyn             | mr_fulln  |

| waster Operation | mw_afulln          |          | mr_aemptyn            |           |

| Target Operation | tw_emptyn          | tw_fulln | tr_fulln              | tr_emptyn |

| larger Operation | tw_aemptyn         |          | tr_afulln             |           |

#### **PCI Bus Pin Information**

This section describes signals on the PCI bus interface and at the embedded core/FPGA interface. Some signal definitions change name and location based on the mode of operation. Modes of operation are described following the signal descriptions. PCI bus signal package pin locations can be found in Table 70.

**Table 7. PCI Bus Pin Descriptions**

| Symbol           | I/O  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Pins      | -1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| clk              | I    | Clock. Provides timing for all transactions on the PCI bus and is an input to the OR3LP26B device. All PCI signals, except rstn and intan, are sampled on the rising edge of clk, and all other PCI bus timing parameters are defined with respect to this edge. The signal clk operates up to 66 MHz, and the minimum frequency is dc.                                                                                                                                         |

| rstn             | I    | <b>Reset.</b> An active-low signal used to reset the entire PCI bus. <b>rstn</b> is asynchronous to <b>clk</b> . During <b>rstn</b> , all PCI output signals are 3-stated.                                                                                                                                                                                                                                                                                                      |

| Address and Data | Pins |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ad[31:0]         | I/O  | <b>Address and Data.</b> Multiplexed on the same PCI pins. A PCI bus transaction consists of an address phase followed by one or more data phases.                                                                                                                                                                                                                                                                                                                              |

|                  |      | During data phases, ad[7:0] contain the least significant byte and ad[31:24] contain the most significant byte. During memory commands, the ad[31:2] lines specify the address and ad[1:0] specify the type of bursting sequence to use. The table below outlines the bursting sequence based on the values of ad[1:0].                                                                                                                                                         |

|                  |      | <ul> <li>ad[1:0] Bursting sequence.</li> <li>00 Linear incrementing.</li> <li>01 Disconnect after first transfer.</li> <li>10 Disconnect after first transfer.</li> <li>11 Disconnect after first transfer.</li> </ul>                                                                                                                                                                                                                                                          |

| c_ben[3:0]       | I/O  | Bus Command and Byte Enables. Active-low signals multiplexed on the same PCI pins. During the address phase of a transaction, c_ben[3:0] define the bus command. During the data phase, c_ben[3:0] are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes carry meaningful data.                                                                                                                                         |

| par              | I/O  | Parity. Specifies even parity across ad[31:0] and c_ben[3:0]. par is stable and valid one clock after the address phase. For data phases, par is stable and valid one clock after irdyn is asserted on a write transaction or trdyn is asserted on a read transaction. Once par is valid, it remains valid until one clock after the completion of the current data phase. The Master drives par for address and write data phases; the Target drives par for read data phases. |

Table 7. PCI Bus Pin Descriptions (continued)

| Symbol             | I/O       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Control  | Pins      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

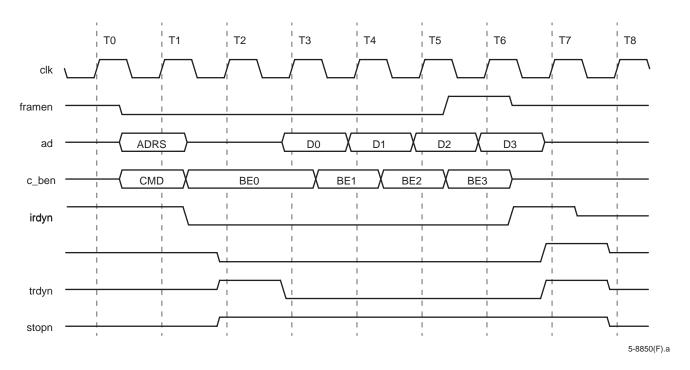

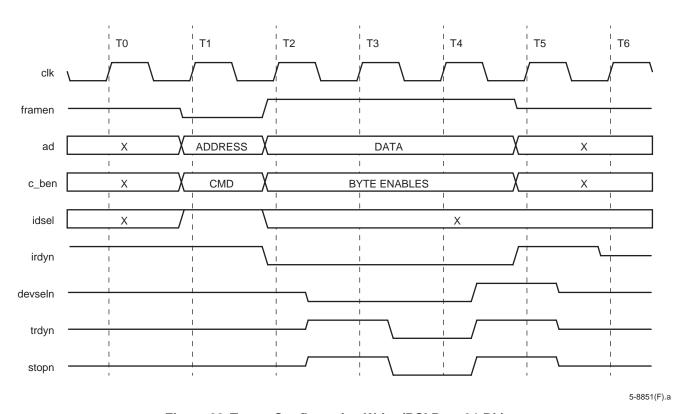

| framen             | I/O       | <b>Cycle Frame.</b> An active-low signal driven by the current Master to indicate the beginning and duration of an access. The signal framen is asserted to indicate a bus transaction is beginning. While <b>framen</b> is asserted, data transfers continue. When <b>framen</b> is deasserted, the transaction is in the final phase or has completed.                                                                                                                                                                                                                                                                                                                                                                                                 |

| irdyn              | I/O       | Initiator Ready. An active-low signal indicating the bus Master's ability to complete the current data phase of the transaction. The signal irdyn is used in conjunction with trdyn. A data phase is completed on any clock cycle during which both irdyn and trdyn are asserted. During a write, irdyn indicates that valid data is present on ad[31:0]. During a read, it indicates the Master is prepared to accept data. Wait cycles are inserted until both irdyn and trdyn are asserted together.                                                                                                                                                                                                                                                  |

| trdyn              | I/O       | <b>Target Ready.</b> An active-low signal asserted to indicate the readiness of the Target's agent to complete the current data phase of the transaction. The signal <b>trdyn</b> is used in conjunction with <b>irdyn</b> . A data phase is completed on any clock where both <b>trdyn</b> and <b>irdyn</b> are sampled active. During reads, <b>trdyn</b> indicates that valid data is present on <b>ad[31:0]</b> lines. During write cycles, <b>trdyn</b> indicates that the Target is prepared to accept data.                                                                                                                                                                                                                                       |

| stopn              | I/O       | <b>STOPn.</b> Indicates that the current Target is requesting the Master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| idsel              | I         | <b>Initialization Device Select.</b> Used as a chip select during PCI configuration read and write transactions. Generally, the user ties <b>idsel</b> to one of the upper 24 address lines, <b>ad[31:8]</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| devseln            | I/O       | <b>Device Select.</b> An active-low input indicating that a device on the bus has been selected. As an output, it indicates that the driving device has decoded its address as the Target of the current access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Arbitration Pins ( | for Bus M | aster Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| reqn               | 0         | <b>Request.</b> An active-low signal that indicates to the arbiter that the asserting agent desires use of the bus. In the OR3LP26B, this signal is asserted when the OR3LP26B Master controller needs access to the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| gntn               | I         | <b>Grant.</b> An active-low signal that indicates to the OR3LP26B that access to the PCI bus has been granted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Error Reporting F  | Pins      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| perrn              | I/O       | Parity Error. An active-low signal for the reporting of data parity errors during all PCI transactions except a special cycle. The <b>perrn</b> pin is a sustained 3-state signal and must be driven active by the agent receiving data two clocks following the data when a data parity error is detected. The minimum duration of <b>perrn</b> is one clock for each data phase that a data parity error is detected. If sequential data phases each have a data parity error, the <b>perrn</b> signal will be asserted for more than a single clock. <b>perrn</b> is driven high for one clock before being 3-stated. The signal <b>perrn</b> is not asserted until it has claimed the access by asserting <b>devseln</b> and completed a data phase. |

Table 7. PCI Bus Pin Descriptions (continued)

| Symbol                  | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| serrn                   | 0        | <b>System Error.</b> An active-low open drain signal pulsed by agents to report errors other than parity. <b>serrn</b> is sampled every <b>clk</b> edge, so any agent asserting <b>serrn</b> must ensure it is valid for at least one clock period. The OR3LP26B asserts <b>serrn</b> if a Master abort sequence is asserted when the Master controller is accessing the PCI bus.         |

| Interrupt Pins          |          |                                                                                                                                                                                                                                                                                                                                                                                           |

| intan                   | 0        | <b>PCI Interrupt.</b> The OR3LP26B asserts this active-low open drain signal when it requests an interrupt from the PCI compliant interrupt controller.                                                                                                                                                                                                                                   |

| 64-Bit Bus Extens       | ion Pins |                                                                                                                                                                                                                                                                                                                                                                                           |

| ad[63:32]               | I/O      | <b>64-Bit Address and Data.</b> These signals provide the upper 32 bits of address and data when in PCI 64-bit operation. During an address phase (when using the DAC command and when <b>req64n</b> is asserted), these address bits are transferred. During a data phase, the data is valid when <b>req64n</b> and <b>ack64n</b> are both asserted. Otherwise, these bits are 3-stated. |

| c_ben[7:4]              | I/O      | Byte Enables. These are the upper four, active-low, bus command and byte enables when in PCI 64-bit operation. During an address phase (when using the DAC command and when req64n is asserted), the bus command is transferred. During a data phase, these bits are the active-low byte enables for data bits 64:32. Otherwise, these bits are 3-stated.                                 |

| req64n                  | I/O      | Request 64-Bit Transfer. This active-low signal is asserted by the current bus Master to indicate that it desires to transfer data using 64 bits. The signal req64n has the same meaning as framen for 32-bit transfers.                                                                                                                                                                  |

| ack64n                  | I/O      | <b>Acknowledge 64-Bit Transfer.</b> The Target drives this signal low to indicate that it has decoded its own address as the Target of the current access and that it can do 64-bit transfers. The signal <b>ack64n</b> has the same timing as <b>devseln</b> in 32-bit transfers.                                                                                                        |

| par64                   | I/O      | Upper Double-Word Parity. The even parity bit that covers ad[63:32] and c_ben[7:4]. PAR64 is valid one clock after the initial address phase when req64n is asserted and the DAC command is indicated on c_ben[7:4]. It is also valid the clock cycle after the second address phase of a DAC command when req64n is asserted.                                                            |

| <b>Hot Swap Functio</b> | n Pins   |                                                                                                                                                                                                                                                                                                                                                                                           |

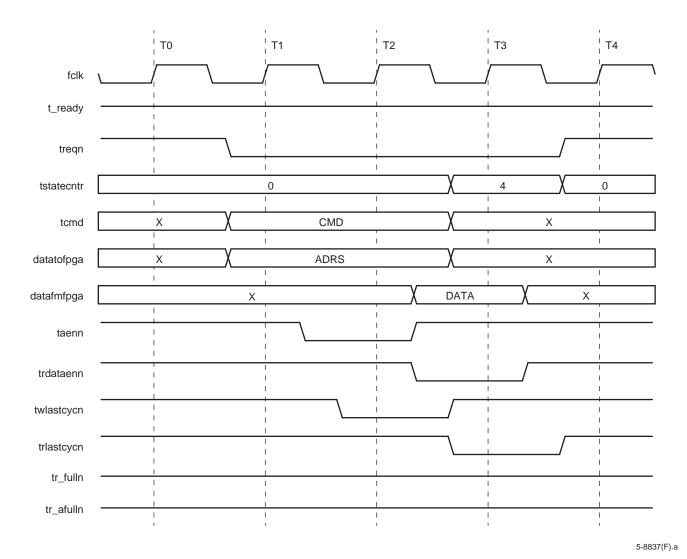

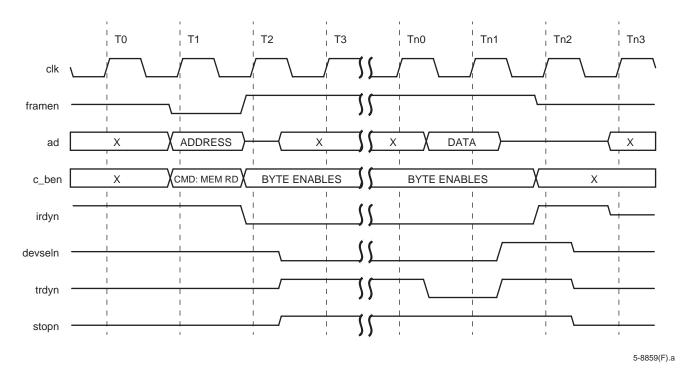

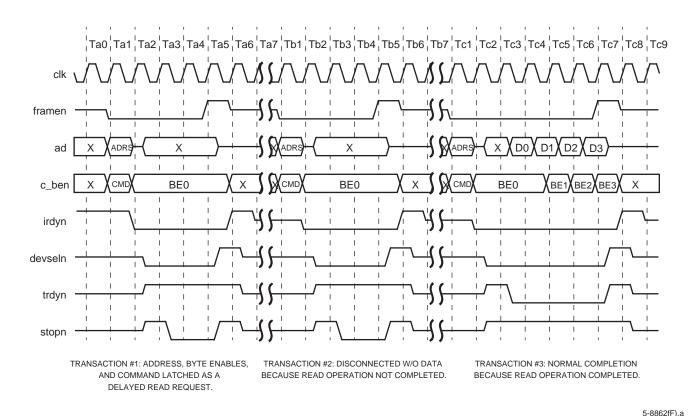

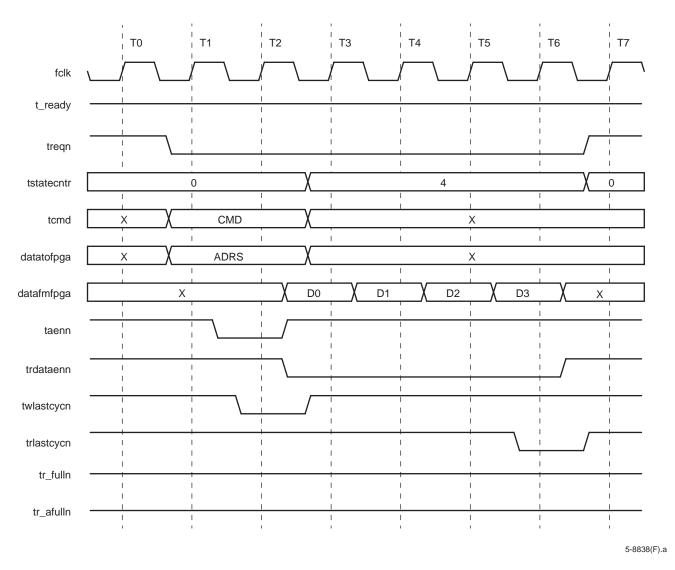

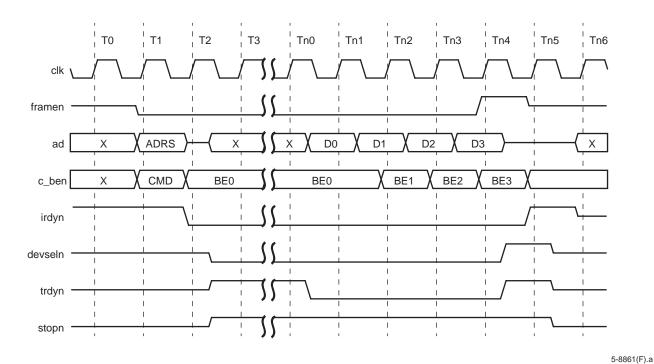

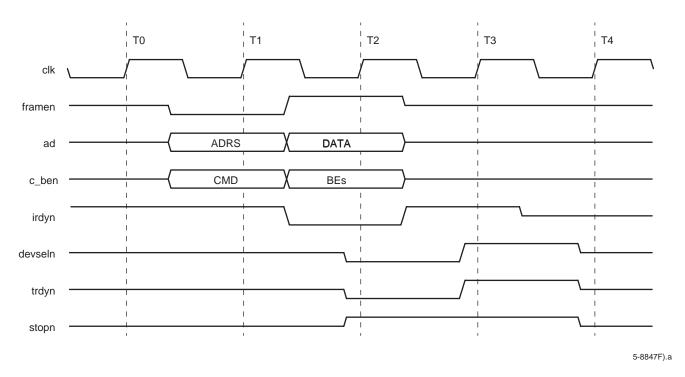

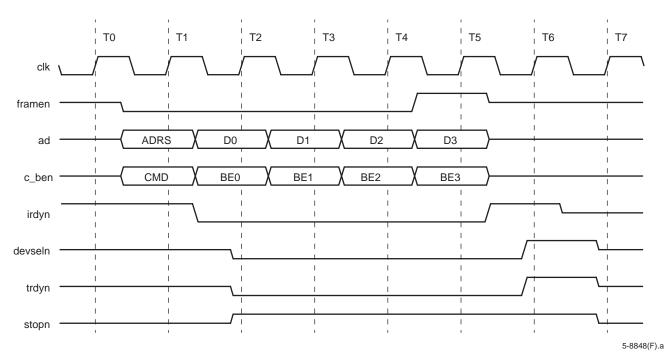

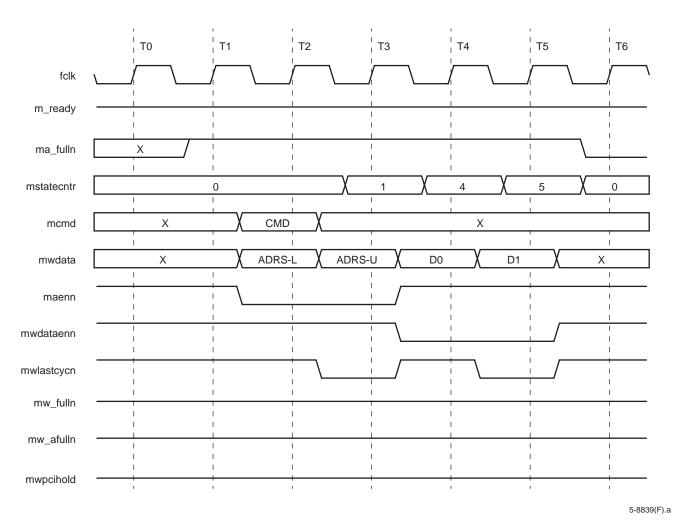

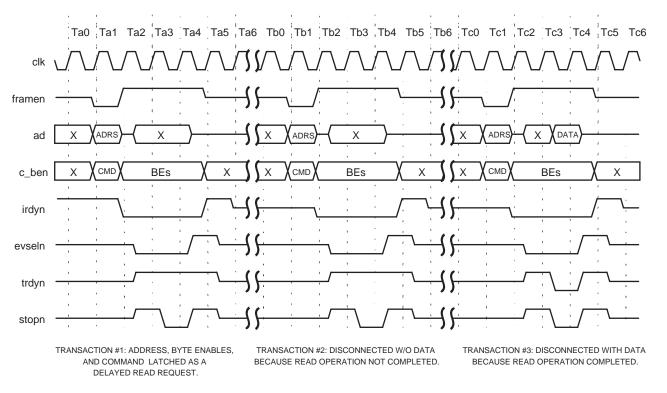

| enumn                   | 0        | Active-low open drain signal that notifies the system host that the card has been freshly inserted or is about to be extracted. The system host can then either install (for insertion) or quiesce (for extraction) the card's driver to adjust for the change in system configuration.                                                                                                   |