# ORCA® ORT4622 Field-Programmable System Chip (FPSC) Four-Channel x 622 Mbits/s Backplane Transceiver

#### Introduction

Lattice has developed a solution for designers who need the many advantages of FPGA-based design implementation, coupled with high-speed serial backplane data transfer. The 622 Mbits/s backplane transceiver offers a clockless, high-speed interface for interdevice communication on a board or across a backplane. The built-in clock recovery of the ORT4622 allows for higher system performance, easier-to-design clock domains in a multiboard system, and fewer signals on the backplane. Network designers will benefit from the backplane transceiver as a network termination device. The backplane transceiver offers SONET scrambling/descrambling of data and streamlined SONET framing, pointer moving, and transport overhead handling, plus the programmable logic to terminate the network into proprietary systems. For non-SONET applications, all SONET functionality is hidden from the user and no prior networking knowledge is required.

#### **Embedded Core Features**

- Implemented in an ORCA Series 3 FPGA array.

- Allows wide range of applications for SONET network termination application as well as generic data moving for high-speed backplane data transfer.

- No knowledge of SONET/SDH needed in generic applications. Simply supply data, 78 MHz clock, and a frame pulse.

- High-speed interface (HSI) function for clock/data recovery serial backplane data transfer without external clocks.

- HSI function uses Lattice's proven 622 Mbits/s serial interface core.

- Four-channel HSI function provides 622 Mbits/s serial interface per channel for a total chip bandwidth of 2.5 Gbits/s (full duplex).

- LVDS I/Os compliant with *EIA*\*-644, support hot insertion.

- 8:1 data multiplexing/demultiplexing for 77.76 MHz byte-wide data processing in FPGA logic.

- On-chip phase-lock loop (PLL) clock meets B jitter tolerance specification of ITU-T Recommendation G.958 (0.6 UIP-P at 250 kHz).

- Powerdown option of HSI receiver on a perchannel basis.

- Highly efficient implementation with only 3% overhead vs. 25% for 8B10B coding.

- In-Band management and configuration.

- Streamlined pointer processor (pointer mover) for 8 kHz frame alignment to system clocks.

- Built-in boundry scan (*IEEE*<sup>†</sup> 1149.1 JTAG).

- FIFOs align incoming data across all four channels for STS-48 (2.5 Gbits/s) operation (in quad STS-12 format).

- 1 + 1 protection supports STS-12/STS-48 redundancy by either software or hardware control for protection switching applications.

- \* EIA is a registered trademark of Electronic Industries Association.

- † IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

Table 1. ORCA ORT4622—Available FPGA Logic

| Device  | Usable<br>System<br>Gates <sup>‡</sup> | Number of<br>LUTs | Number of<br>Registers | Max User<br>RAM | Max User<br>I/Os | Array Size | Number of PFUs |

|---------|----------------------------------------|-------------------|------------------------|-----------------|------------------|------------|----------------|

| ORT4622 | 60K—120K                               | 4032              | 5304                   | 64K             | 259              | 18 x 28    | 504            |

<sup>‡</sup>The embedded core and interface are not included in the above gate counts. The usable gate count range from a logic-only gate count to a gate count assuming 30% of the PFUs/SLICs being used as RAMs. The logic-only gate count includes each PFU/SLIC (counted as 108 gates per PFU/SLIC), including 12 gates pre-LUT/FF pair (eight per PFU), and 12 gates per SLC/FF pair (one per PFU). Each of the four PIOs per PIC is counted as 16 gates (two FFs, fast-capture latch, output logic, CLK drivers, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32 x 4 RAM (or 512 gates) per PFU.

## **Table of Contents**

| Contents F                                      | age |

|-------------------------------------------------|-----|

| Introduction                                    | 1   |

| Embedded Core Features                          | 1   |

| FPSC Highlights                                 | 3   |

| Software Support                                | 3   |

| Description                                     | 4   |

| What Is an FPSC?                                | 4   |

| FPSC Overview                                   |     |

| FPSC Gate Counting                              | 4   |

| FPGA/Embedded Core Interface                    |     |

| ORCA Foundry Development System                 |     |

| FPSC Design Kit                                 |     |

| FPGA Logic Overview                             |     |

| PLC Logic                                       |     |

| PIC Logic                                       |     |

| System FeaturesRouting                          |     |

| Configuration                                   |     |

| More Series 3 Information                       | 6   |

| ORT4622 Overview                                |     |

| Device Layout                                   |     |

| Backplane Transceiver Interface                 |     |

| HSI Interface                                   |     |

| STM Macrocell                                   |     |

| CPU Interface                                   |     |

| FPGA Interface                                  | 9   |

| FPSC Configuration                              | 11  |

| Generic Backplane Transceiver                   |     |

| Application                                     |     |

| Backplane Transceiver Core Detailed Description |     |

| HSI Macro                                       |     |

| STM Transmitter (FPGA -> Backplane)             |     |

| STM Receiver (Backplane -> FPGA)                |     |

| Powerdown Mode                                  |     |

| Redundancy and Protection Switching  Memory Map |     |

| Definition of Register Types                    |     |

| Memory Map Overview                             |     |

| Powerup Sequencing for ORT4622 Device           | 20  |

| FPGA Configuration Data Format                  |     |

| Using ORCA Foundry to Generate Configurati      |     |

| RAM Data                                        |     |

| FPGA Configuration Data Frame                   |     |

| Bit Stream Error Checking                       |     |

| FPGA Configuration Modes                        | 37  |

| Absolute Maximum Ratings                        |     |

| Recommend Operating Conditions                  |     |

| Electrical Characteristics                      |     |

| HSI Circuit Specifications                      |     |

| Input Data                                      |     |

| Jitter Tolerance                                |     |

| Generated Output Jitter                         |     |

| PLL                                             |     |

| Input Reference Clock                           | 40  |

| Contents                                   | Page |

|--------------------------------------------|------|

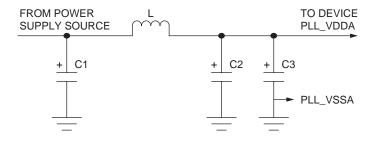

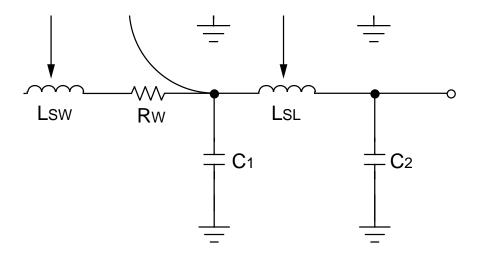

| Power Supply Decoupling LC Circuit         | 41   |

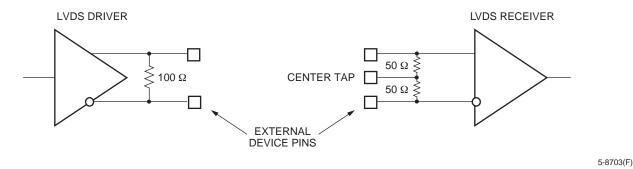

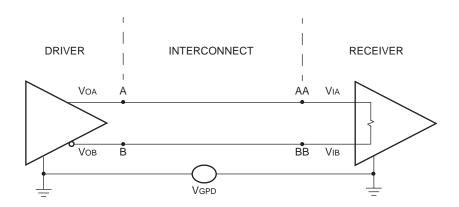

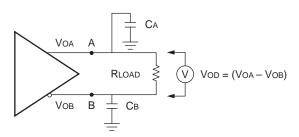

| LVDS I/O                                   |      |

| LVDS Receiver Buffer Requirements          | 43   |

| Timing Characteristics                     | 44   |

| Description                                |      |

| PFU Timing                                 | 45   |

| PLC Timing                                 | 45   |

| SLIC Timing                                | 45   |

| PIO Timing                                 | 45   |

| Special Function Timing                    | 45   |

| Clock Timing                               | 45   |

| Configuration Timing                       | 45   |

| Readback Timing                            | 45   |

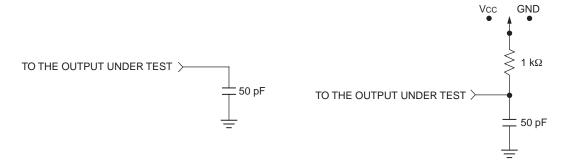

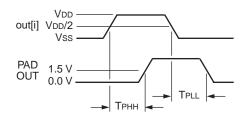

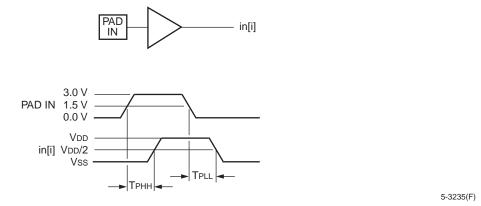

| Input/Output Buffer Measurement Conditions |      |

| (on-LVDS Buffer)                           | 55   |

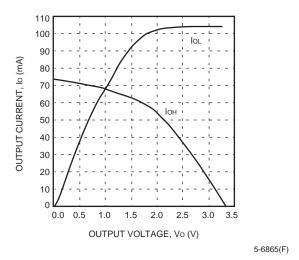

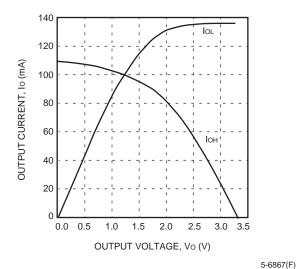

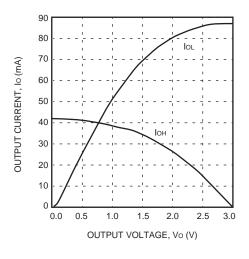

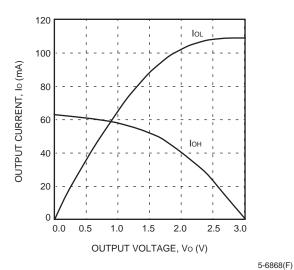

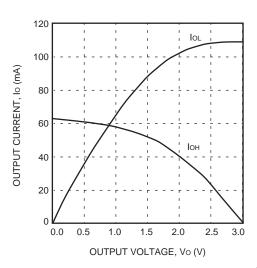

| FPGA Output Buffer Characteristics         |      |

| LVDS Buffer Characteristics                | 57   |

| Termination Resistor                       |      |

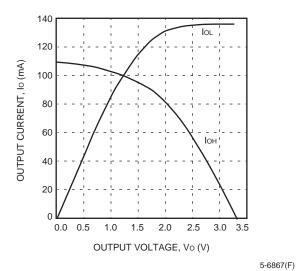

| LVDS Driver Buffer Capabilities            | 57   |

| Estimating Power Dissipation               |      |

| ORT4622 Clock Power                        | 58   |

| Pin Information                            |      |

| Package Thermal Characteristics Summary    | 82   |

| ΘJA                                        | 82   |

| ψJC                                        | 82   |

| ΘJC                                        | 82   |

| ΘJB                                        |      |

| FPGA Maximum Junction Temperature          |      |

| Package Thermal Characteristics            |      |

| Package Coplanarity                        |      |

| Package Parasitics                         |      |

| Package Outline Diagrams                   |      |

| Terms and Definitions                      |      |

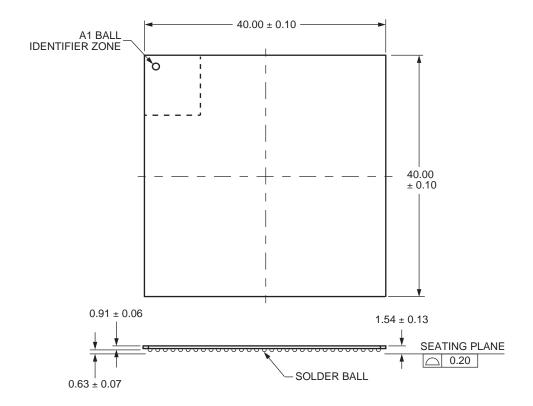

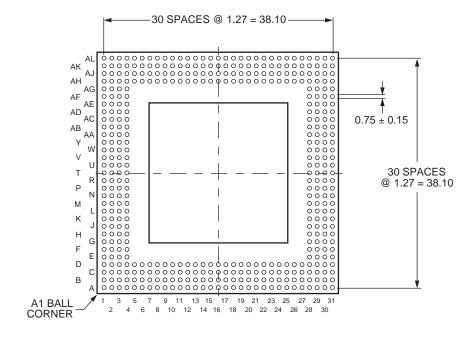

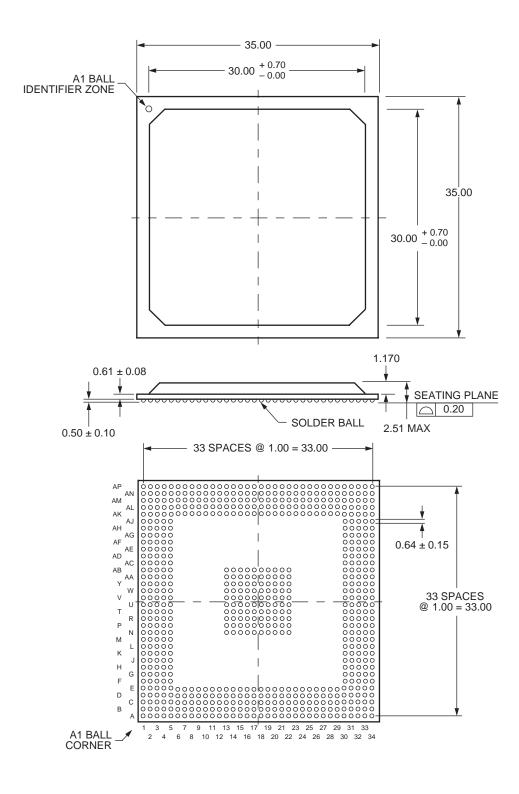

| 432-Pin EBGA                               | 86   |

| 680-Pin PBGAM                              | 87   |

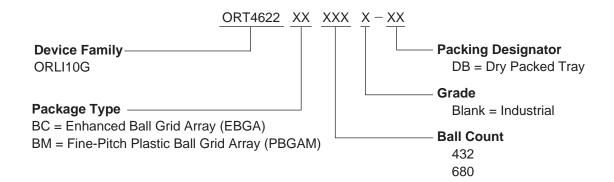

| Ordering Information                       | 88   |

#### **Embedded Core Features** (continued)

- Pseudo-SONET protocol including A1/A2 framing.

- SONET scrambling and descrambling for required ones density (optional).

- Selected transport overhead (TOH) bytes insertion and extraction for interdevice communication via the TOH serial link.

## **FPSC Highlights**

- Implemented as an embedded core in the ORCA Series 3+ FPSC architecture.

- Allows the user to integrate the core with up to 120K gates of programmable logic (all in one device) and provides up to 242 user I/Os in addition to the embedded core I/O pins.

- FPGA portion retains all of the features of the ORCA Series 3 FPGA architecture:

- High-performance, cost-effective, 0.25 μm, 5-level metal technology.

- Twin-quad programmable function unit (PFU)

architecture with eight 16-bit look-up tables

(LUTs) per PFU, organized in two nibbles for use

in nibble- or byte-wide functions. Allows for mixed

arithmetic and logic functions in a single PFU.

- Softwired LUTs (SWL) allow fast cascading of up to three levels of LUT logic in a single PFU.

- Supplemental logic and interconnect cell (SLIC) provides 3-statable buffers, up to 10-bit decoder, and PAL\*-like AND-OR-INVERT (AOI) in each programmable logic cell (PLC).

- Up to three ExpressCLK inputs allow extremely fast clocking of signals on- and off-chip plus access to internal general clock routing.

- Dual-use microprocessor interface (MPI) can be used for configuration, as well as for a generalpurpose interface to the FPGA. Glueless interface to i960<sup>†</sup> and PowerPC<sup>‡</sup> processors with userconfigurable address space provided.

- Programmable clock manager (PCM) adjusts clock phase and duty cycle for input clock rates from 5 MHz to 120 MHz. The PCM may be com-

- bined with FPGA logic to create complex functions, such as digital phase-locked loops, frequency counters, and frequency synthesizers or clock doublers. Two PCMs are provided per device.

- True internal 3-state, bidirectional buses with simple control provided by the SLIC.

- 32 x 4 RAM per PFU, configurable as single or dual port. Create large, fast RAM/ROM blocks (128 x 8 in only eight PFUs) using the SLIC decoders as bank drivers.

- Built-in boundary scan (*IEEE* 1149.1 JTAG) and TS\_ALL testability function to 3-state all I/O pins.

- High-speed, on-chip interface provided between FPGA logic and embedded core to reduce bottlenecks typically found when interfacing off-chip.

## **Software Support**

- Supported by ORCA Foundry software and thirdparty CAE tools for implementing ORCA Series 3+ devices and simulation/timing analysis with the embedded core functions.

- Embedded core configuration options and simulation netlists generated by FPSC Configuration Manager utility.

- \* PAL is a trademark of Advanced Micro Devices, Inc.

- † *i960* is a registered trademark of Intel Corporation.

- ‡ PowerPC is a registered trademark of International Business Machines Corporation.

### **Description**

#### What Is an FPSC?

FPSCs, or field-programmable system chips, are devices that combine field-programmable logic with ASIC or mask-programmed logic on a single device. FPSCs provide the time to market and flexibility of FPGAs, the design effort savings of using soft intellectual property (IP) cores, and the speed, design density, and economy of ASICs.

#### **FPSC Overview**

Lattice's Series 3+ FPSCs are created from Series 3 ORCA FPGAs. To create a Series 3+ FPSC, several rows of programmable logic cells (see FPGA Logic Overview section for FPGA logic details) are removed from a Series 3 ORCA FPGA, and the area is replaced with an embedded logic core. Other than replacing some FPGA gates with ASIC gates, at greater than 10:1 efficiency, none of the FPGA functionality is changed—all of the Series 3 FPGA capability is retained: MPI, PCMs, boundary scan, etc. The rows of programmable logic are replaced at the bottom of the device, allowing pins on the bottom and sides of the replaced rows to be used as I/O pins for the embedded core. The remainder of the device pins retain their FPGA functionality as do special function FPGA pins within the embedded core area.

#### **FPSC Gate Counting**

The total gate count for an FPSC is the sum of its embedded core (standard-cell/ASIC gates) and its FPGA gates. Because FPGA gates are generally expressed as a usable range with a nominal value, the total FPSC gate count is sometimes expressed in the same manner. Standard-cell ASIC gates are, however, 10 to 25 times more silicon area efficient than FPGA gates. Therefore, an FPSC with an embedded function is gate equivalent to an FPGA with a much larger gate count.

#### FPGA/Embedded Core Interface

The interface between the FPGA logic and the embedded core is designed to look like FPGA I/Os from the FPGA side, simplifying interface signal routing and providing a unified approach with general FPGA design. Effectively, the FPGA is designed as if signals were going off of the device to the embedded core, but the on-chip interface is much faster than going off-chip and requires less power. All of the delays for the interface are precharacterized and accounted for in the *ORCA* Foundry Development System.

Clock spines also can pass across the FPGA/embedded core boundary. This allows for fast, low-skew clocking between the FPGA and the embedded core. Many of the special signals from the FPGA, such as DONE and global set/reset, are also available to the embedded core, making it possible to fully integrate the embedded core with the FPGA as a system.

For even greater system flexibility, FPGA configuration RAMs are available for use by the embedded core. This allows for user-programmable options in the embedded core, in turn allowing for greater flexibility. Multiple embedded core configurations may be designed into a single device with user-programmable control over which configurations are implemented, as well as the capability to change core functionality simply by reconfiguring the device.

#### **ORCA** Foundry Development System

The *ORCA* Foundry Development System is used to process a design from a netlist to a configured FPSC. This system is used to map a design onto the *ORCA* architecture and then place and route it using *ORCA* Foundry's timing-driven tools. The development system also includes interfaces to, and libraries for, other popular CAE tools for design entry, synthesis, simulation, and timing analysis.

The ORCA Foundry Development System interfaces to front-end design entry tools and provides the tools to produce a configured FPSC. In the design flow, the user defines the functionality of the FPGA portion of the FPSC and embedded core settings at two points in the design flow: at design entry and at the bit stream generation stage. Following design entry, the development system's map, place, and route tools translate the netlist into a routed FPSC. A static timing analysis tool is provided to determine device speed, and a backannotated netlist can be created to allow simulation.

## **Description** (continued)

Timing and simulation output files from *ORCA* Foundry are also compatible with many third-party analysis tools. Its bit stream generator is then used to generate the configuration data which is loaded into the FPSC's internal configuration RAM.

When using the bit stream generator, the user selects options that affect the functionality of the FPSC. Combined with the front-end tools, *ORCA* Foundry produces configuration data that implements the various logic and routing options discussed in this data sheet.

#### **FPSC Design Kit**

Development is facilitated by an FPSC design kit which, together with *ORCA* Foundry and third-party synthesis and simulation engines, provides all software and documentation required to design and verify an FPSC implementation. Included in the kit are the FPSC configuration manager, HDL gate-level structural netlists, all necessary synthesis libraries, and complete online documentation. The kit's software couples with *ORCA* Foundry, providing a seamless FPSC design environment. More information can be obtained by visiting the *ORCA* website or contacting a local sales office, both listed on the last page of this document.

#### **FPGA Logic Overview**

ORCA Series 3 FPGA logic is a new generation of SRAM-based FPGA logic built on the successful Series 2 FPGA line, with enhancements and innovations geared toward today's high-speed designs on a single chip. Designed from the start to be synthesis friendly and to reduce place and route times while maintaining the complete routability of the ORCA Series 2 devices, the Series 3 more than doubles the logic available in each logic block and incorporates system-level features that can further reduce logic requirements and increase system speed. ORCA Series 3 devices contain many new patented enhancements and are offered in a variety of packages, speed grades, and temperature ranges.

ORCA Series 3 FPGA logic consists of three basic elements: programmable logic cells (PLCs), programmable input/output cells (PICs), and system-level features. An array of PLCs is surrounded by PICs. Each PLC contains a programmable function unit (PFU), a supplemental logic and interconnect cell (SLIC), local routing resources, and configuration RAM. Most of the FPGA logic is performed in the PFU, but decoders, PAL-like functions, and 3-state buffering can be performed in the SLIC. The PICs provide device inputs and outputs and can be used to register signals and to perform input demultiplexing, output multiplexing, and other functions on two output signals. Some of the system-level functions include the new microprocessor interface (MPI) and the programmable clock manager (PCM).

### **PLC Logic**

Each PFU within a PLC contains eight 4-input (16-bit) look-up tables (LUTs), eight latches/flip-flops (FFs), and one additional flip-flop that may be used independently or with arithmetic functions.

The PFU is organized in a twin-quad fashion: two sets of four LUTs and FFs that can be controlled independently. LUTs may also be combined for use in arithmetic functions using fast-carry chain logic in either 4-bit or 8-bit modes. The carry-out of either mode may be registered in the ninth FF for pipelining. Each PFU may also be configured as a synchronous 32 x 4 single- or dual-port RAM or ROM. The FFs (or latches) may obtain input from LUT outputs or directly from invertible PFU inputs, or they can be tied high or tied low. The FFs also have programmable clock polarity, clock enables, and local set/reset.

The SLIC is connected to PLC routing resources and to the outputs of the PFU. It contains 3-state, bidirectional buffers and logic to perform up to a 10-bit AND function for decoding, or an AND-OR with optional INVERT (AOI) to perform *PAL*-like functions. The 3-state drivers in the SLIC and their direct connections to the PFU outputs make fast, true 3-state buses possible within the FPGA logic, reducing required routing and allowing for real-world system performance.

#### **Description** (continued)

#### **PIC Logic**

The Series 3 PIC addresses the demand for everincreasing system clock speeds. Each PIC contains four programmable inputs/outputs (PIOs) and routing resources. On the input side, each PIO contains a fast-capture latch that is clocked by an ExpressCLK. This latch is followed by a latch/FF that is clocked by a system clock from the internal general clock routing. The combination provides for very low setup requirements and zero hold times for signals coming on-chip. It may also be used to demultiplex an input signal, such as a multiplexed address/data signal, and register the signals without explicitly building a demultiplexer. Two input signals are available to the PLC array from each PIO, and the ORCA Series 2 capability to use any input pin as a clock or other global input is maintained.

On the output side of each PIO, two outputs from the PLC array can be routed to each output flip-flop, and logic can be associated with each I/O pad. The output logic associated with each pad allows for multiplexing of output signals and other functions of two output signals.

The output FF, in combination with output signal multiplexing, is particularly useful for registering address signals to be multiplexed with data, allowing a full clock cycle for the data to propagate to the output. The I/O buffer associated with each pad is the same as the *ORCA* Series 3 buffer.

#### **System Features**

The Series 3 also provides system-level functionality by means of its dual-use microprocessor interface (MPI) and its innovative programmable clock manager (PCM). These functional blocks allow for easy glueless system interfacing and the capability to adjust to varying conditions in today's high-speed systems. Since these and all other Series 3 features are available in every Series 3+ FPSC, they can also interface to the embedded core providing for easier system integration.

#### Routing

The abundant routing resources of *ORCA* Series 3 FPGA logic are organized to route signals individually or as buses with related control signals. Clocks are routed on a low-skew, high-speed distribution network and may be sourced from PLC logic, externally from any I/O pad, or from the very fast ExpressCLK pins. ExpressCLKs may be glitchlessly and independently enabled and disabled with a programmable control signal using the StopCLK feature. The improved PIC routing resources are now similar to the patented intra-PLC routing resources and provide great flexibility in moving signals to and from the PIOs. This flexibility translates into an improved capability to route designs at the required speeds when the I/O signals have been locked to specific pins.

#### Configuration

The FPGA logic's functionality is determined by internal configuration RAM. The FPGA logic's internal initialization/configuration circuitry loads the configuration data at powerup or under system control. The RAM is loaded by using one of several configuration modes, including serial EEPROM, the microprocessor interface, or the embedded function core.

#### **More Series 3 Information**

For more information on Series 3 FPGAs, please refer to the Series 3 FPGA data sheet, available on the Lattice website.

#### **ORT4622 Overview**

#### **Device Layout**

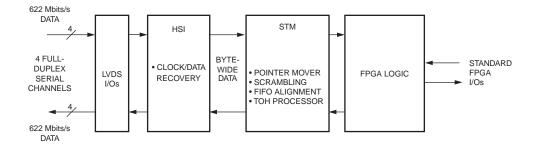

The ORT4622 FPSC provides a high-speed backplane transceiver combined with FPGA logic. The device is based on a 2.5 V 3.3 V I/O OR3L125B FPGA. The OR3L125B has a 28 x 28 array of programmable logic cells (PLCs). For the ORT4622, the bottom ten rows of PLCs in the array were replaced with the embedded backplane transceiver core. The ORT4622 embedded core comprises the HSI macrocell, the synchronous transport module (STM) macrocell, a CPU interface, and LVDS I/Os. The four full-duplex channels perform data transfer, scrambling/descrambling and framing at the rate of 622 Mbits/s. Figure 1 shows the ORT4622 block diagram.

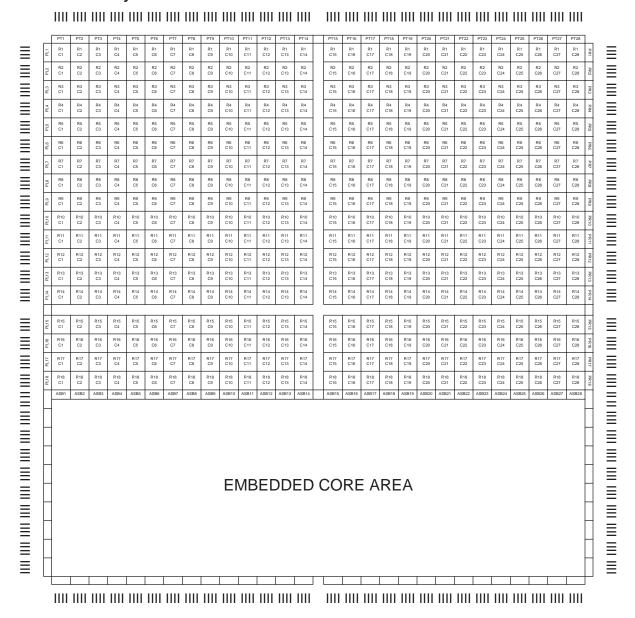

Table 2 shows a schematic view of the ORT4622. The upper portion of the device is an 18 x 28 array of PLCs surrounded on the left, top, and right by programmable input/output cells (PICs). At the bottom of the PLC array are the core interface cells (CICs) connecting to the embedded core region. The embedded core region contains the backplane transceiver functionality of the device. It is surrounded on the left, bottom, and right by backplane transceiver dedicated I/Os as well as power and special function FPGA pins. Also shown are the interquad routing blocks (hIQ, vIQ) present in the Series 3 FPGA devices. System-level functions (located in the corners of the PLC array), routing resources, and configuration RAM are not shown in Table 2.

#### **Backplane Transceiver Interface**

The advantage of the ORT4622 FPSC is to bring specific networking functions to an early market presence with programmable logic in FPGA system.

The 622 Mbits/s backplane transceiver core allows the ORT4622 to communicate across a backplane or on a given board at an aggregate speed of 2.5 Gbits/s, providing a physical medium for high-speed asynchronous serial data transfer between system devices. This device is intended for, but not limited to, connecting terminal equipment in SONET/SDH and ATM systems.

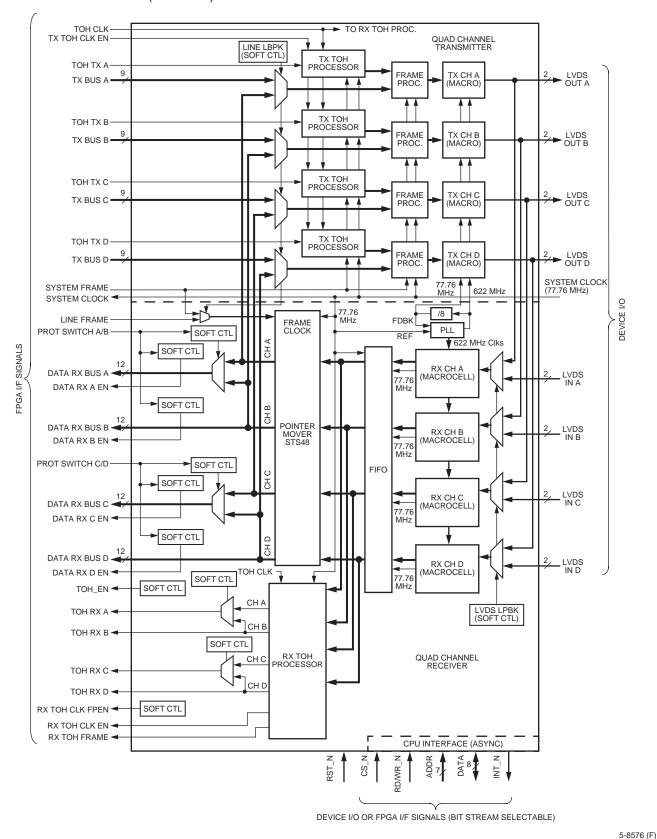

For networking applications, the ORT4622 offers a pseudo SONET framer and scrambler/descrambler interface capable of frame synchronization and insertion/extraction of selectable transport overhead bytes and SONET scrambling and descrambling for four STS-12 (622 Mbits/s) channels. The channels are synchronized to each other by a user-provided 8 kHz frame pulse. The ORT4622 also provides STS-48 (2.5 Gbits/s) operation across all four channels where each channel is in STS-12 format. The pseudo-SONET framer of OR4622 is designed with a reduced set of the SONET framing algorithm. The pointer processing capability is more suitable for low error rate intersystem data communication, particular for backplane transceiver applications. Figure 2 shows the architecture of the ORT4622 backplane transceiver core.

5-8113(F)

Figure 1. ORCA ORT4622 Block Diagram

Table 2. ORT4622 Array

#### **HSI** Interface

The high-speed interconnect (HSI) macrocell is used for clock/data recovery and MUX/deMUX between 77.76 MHz byte-wide internal data buses and 622 Mbits/s external serial links.

The HSI interface receives four 622 Mbits/s serial input data streams from the LVDS inputs and provides four independent 77.76 MHz byte-wide data streams and recovered clock to the STM macro. There is no requirement for bit alignment since SONET type framing will take place inside the ORT4622 core. For transmit, the HSI converts four byte-wide 77.76 MHz data streams to serial streams at 622 Mbits/s at the LVDS outputs.

#### **STM Macrocell**

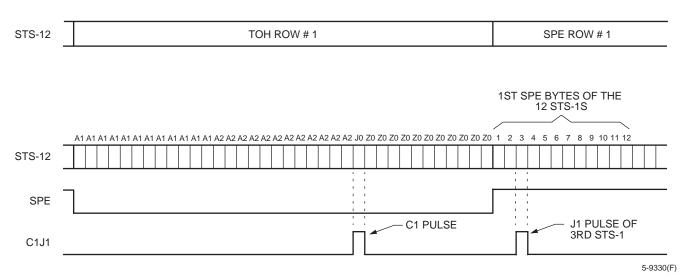

The STM portion of the embedded core consists of transmitter (Tx) and receiver (Rx) sections. The receiver receives four byte-wide data streams at 77.76 MHz and the associated clocks from the HSI. In the Rx section, the incoming streams are SONET framed and descrambled before they are written into a FIFO which absorbs phase and delay variations and allows the shift to the system clock. The TOH is then extracted and sent out on the four serial ports. The pointer Mover consists of three blocks: pointer interpreter, elastic store, and pointer generator. The pointer interpreter finds the synchronous transport signal (STS) synchronous payload envelopes (SPE) and places it into a small elastic store from which the pointer generator will produce four byte-wide STS-12 streams of data that are aligned to the system timing pulse.

In the Tx section, transmitted data for each channel is received through a parallel bus and a serial port from the FPGA circuit. TOH bytes are received from the serial input port and can be optionally inserted from programmable registers or serial inputs to the STS-12 frame via the TOH processor. Each of the four parallel input buses is synchronized to a free-running system clock. Then the SPE and TOH data is transferred to the HSI.

The STM macrocell also has a scrambler/descrambler disable feature, allowing the user to disable the scrambler of the transmitter and the descrambler of the receiver. Also, unused channels can be disabled to reduce power dissipation.

#### **CPU Interface**

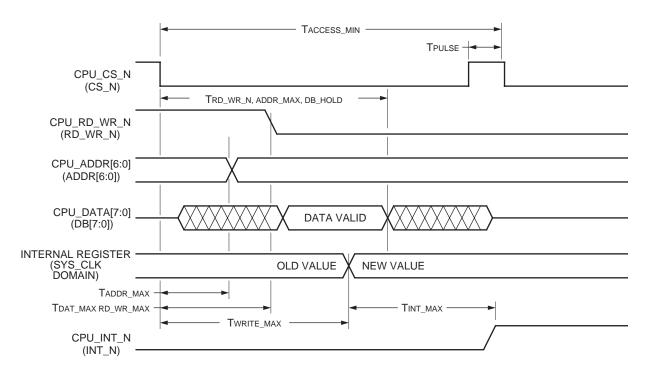

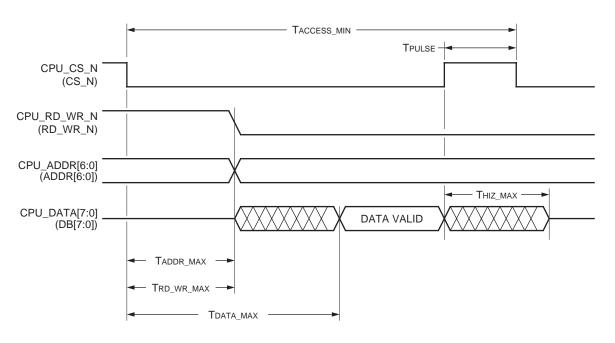

The embedded core has a dedicated, asynchronous, MPC860 compatible, CPU interface that is used for device setup, control, and monitoring. Dual sets of I/O pins of this CPU interface with a bit stream configurable scheme provide designers a convenient and flexible option for configuration. One set of CPU I/O pins goes off chip allowing direct connection with an onboard CPU. Another set of CPU I/O pins is available to the FPGA logic allowing for a stand-alone system free of an external CPU interface, or for itegration into the Series 3 FPGA MPI interface.

The CPU interface is composed of an 8-bit data bus, a 7-bit address bus, a chip select signal, a read/write signal, and an interrupt signal.

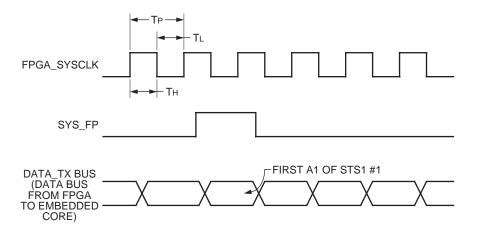

#### **FPGA Interface**

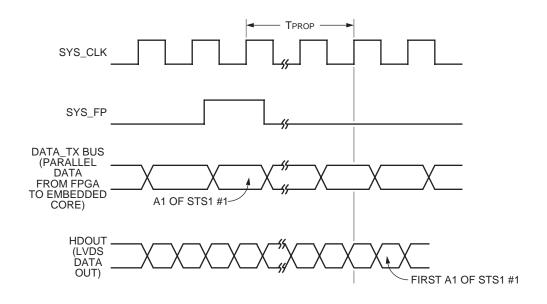

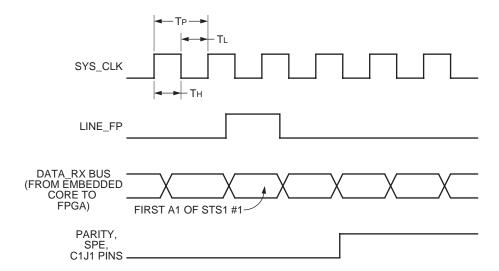

The FPGA logic will receive/transmit frame-aligned streams of 77.76 MHz data (maximum of four streams in each direction) from/to the backplane transceiver embedded core. All frames transmitted to the FPGA will be aligned to the FPGA frame pulse which will be provided by the FPGA user's logic to the STM macro. All frames received from the FPGA logic will be aligned to the system frame pulse that will be supplied to the STM macro from the FPGA user's logic.

Figure 2. Architecture of ORT4622 Backplane Transceiver

#### **FPSC Configuration**

Configuration of the ORT4622 occurs in two stages, FPGA bit stream configuration and embedded core setup.

#### **FPGA Configuration**

Prior to becoming operational, the FPGA goes through a sequence of states, including powerup initialization, configuration, start-up, and operation. The FPGA logic is configured by standard FPGA bit stream configuration means as discussed in the Series 3 FPGA data sheet. Additionally, for the ORT4622, the location of the CPU interface to the embedded core, either on the device pins or at the FPGA/embedded core boundary, is configured via FPGA configuration and is defined via the ORT4622 design kit. The default configuration sets the CPU interface pins to be active. A simple microprocessor emulation soft Intellectual Property (IP) core that uses very small FPGA logic is available from Lattice. This microprocessor core sets up the embedded core via a state machine and allows the ORT4622 to work in an independent system without an external microprocessor interface.

#### **Embedded Core Setup**

The embedded core operation is set up via the embedded core CPU interface. All options for the operation of the core are configured according to the device register map presented in the detailed description section of this data sheet.

During the powerup sequence, the ORT4622 device (FPGA programmable circuit and the core) is held in reset. All the LVDS output buffers and other output buffers are held in 3-state. All flip-flops in core area are in reset state, with the exception of the boundry scan shift registers, which can only be reset by Boundary Scan Reset. After powerup reset, the FPGA can start configuration. During FPGA configuration, the ORT4622 core will be held in reset and all the local bus interface signals are forced high, but the following active-high signals (PROT\_SWITCH\_A, PROT\_SWITCH\_C, TX\_TOH\_CK\_EN, SYS\_FP, LINE\_FP) are forced low. The CORE\_READY signal sent from the embedded core to FPGA is held low, indicating core is not ready to

interact with FPGA logic. At the end of the FPGA configuration sequence, the CORE\_READY signal will be held low for six SYS\_CLK cycles after DONE, TRI\_IO and RST\_N (core global reset) are high. Then it will go active-high, indicating the embedded core is ready to function and interact with FPGA programmable circuit. During FPGA reconfiguration when DONE and TRI\_IO are low, the CORE\_READY signal sent from the core to FPGA will be held low again to indicate the embedded core is not ready to interact with FPGA logic. During FPGA partial configuration, CORE\_READY stays active. The same FPGA configuration sequence described previously will repeat again.

The initialization of the embedded core consists of two steps: register configuration and synchronization of the alignment FIFO. In order to configure the embedded core, the registers need to be unlocked by writing 0xA0 to address 0x04 and writing 0x01 to address 0x05. Control registers 0x04 and 0x05 are lock registers. If the output bus of the data, serial TOH port, and TOH clock and TOH frame pulse are controlled by 3-state registers (the use of the registers for 3-state output control is optional; these output 3-state enable signals are brought across the local bus interface and available to the FPGA side), the next step is to activate the 3state output bus and signals by taking them to functional state from high-impedance state. This can be done by writing 0x01 to correspond bits of the channel registers 0x20, 0x38, 0x50, and 0x68. If the 3-state control is done in FPGA logic or external logic instead of in the embedded core registers, this step should be done in that particular control logic also.

In addition, the synchronization of selected streams is recommended for some networking systems applications. This is a resync of the alignment FIFO after the enabled channels have a valid frame pulse. Here are the procedures: Put all of the streams to be aligned, including disabled streams, into their required alignment mode. Force AIS-L in all streams to be synchronized (refer to register map, write 0x01 to DB1 of register 0x20, 0x38, 0x50, 0x68). Wait four frames. Write a 0x01 to the FIFO alignment resync register, bit DB1 of register 0x06. Wait four frames. Release the AIS-L in all streams (write 1 to DB1 of register 0x20, 0x38, 0x50, 0x68). This procedures allows normal data flow through the embedded core.

# Generic Backplane Transceiver Application

The combination of ORT4622 and soft IP cores provides a generic data moving solution for non-SONET applications. There is no requirement for SONET knowledge to the users. All that is needed is to supply the embedded core interface with data, clock, and a 8 kHz frame pulse. The provision registers may also need to be set up, and this can be done through either the FPGA MPI or in a state machine in the FPGA section (VHDL code available from Lattice).

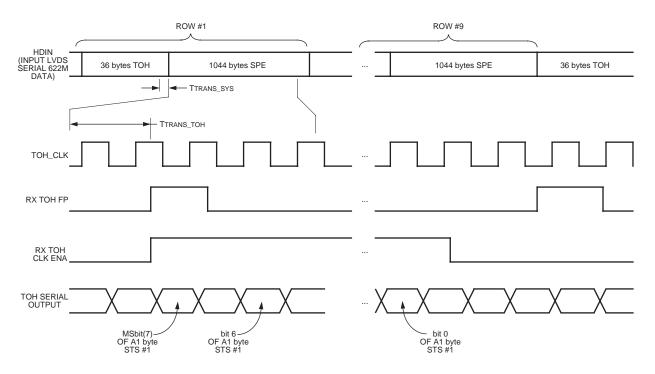

The 8 kHz frame pulse must be supplied to the SYS\_FP signal. For generic applications, the frame pulse can be created in FPGA logic from the 77.76 MHz SYS CLK using a simple resettable counter (the frame pulse should only be high for one cycle of the SYS CLK). A VHDL core that automatically provides the 8 kHz frame pulse is available from Lattice. Byte-wide data is then sent to each of the transmit channels as follows: the first 36 bytes transferred will be invalid data (replaced by overhead), where the first byte is sent on the rising edge of SYS\_CLK when SYS\_FP is high. The next 1044 byte positions can be filled with valid data. This will repeat a total of nine times (36 invalid bytes followed by 1044 valid bytes) at which time the next 8 kHz frame pulse will be found. Thus, 87 out of 90 (96.7%) of the data bytes sent are valid user data.

On the receive side, an 8 kHz pulse must again be supplied to SYS\_FP. In this case, however, only the signal DATA\_RX\*\_SPE must be monitored for each channel, where a high value on this signal means valid data. Again 87 out 90 bytes received (96.7%) will be valid data.

In order to provide an easy user interface to transfer arbitrary data streams through the ORT4622, Lattice provides a soft Intellectual Property (IP) core called the protocol independent framer, or PI-Framer. This block transfers user format to the one described above and allows for smoothing/rate transfer of this user data. This framer works with a single channel at 622 Mbits/s, two channels at 1.25 Gbits/s, or across four channels at 2.5 Gbits/s.

## Backplane Transceiver Core Detailed Description

#### **HSI Macro**

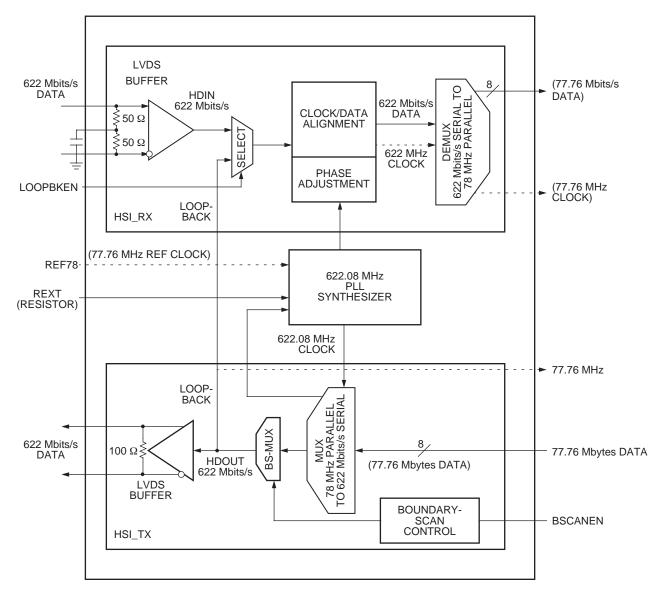

The high-speed interface (HSI) provides a physical medium for high-speed asynchronous serial data transfer between the ORT4622 and other devices. The devices can be mounted on the same board or mounted on different boards and connected through the shelf backplane. The 622 Mbits/s CDR macro is a four-channel clock phase select (CPS) and data retime function with serial-to-parallel demultiplexing for the incoming data stream and parallel-to-serial multiplexing for outgoing data. The HSI macro consists of three functionally independent blocks: receiver, transmitter, and PLL synthesizer as shown in Figure 3.

The PLL synthesizer block receives a 77.76 MHz reference clock at its input, and provides a phase-locked 622.08 MHz clock to the transmitter block and phase control signal to the receiver block. The PLL synthesizer block is a common asset shared by four receive and transmit channels.

The HSI receiver receives four channels of differential 622.08 Mbits/s serial data without clock at its LVDS receive inputs. The received data must be scrambled, conforming to SONET STS-12 and SDH STM-4 data formats using either a PN7 or PN9 sequence. The PN7 characteristic polynomial is  $1 + x^6 + x^7$ , and PN9 characteristic polynomial is  $1 + x^4 + x^9$ . The ORT4622 supplies a default scrambler using the PN7 sequence. The clock phase select and data retime (CPS/DR) module performs a clock recovery and data retiming function by using phase control information. The resultant 622.08 Mbits/s data and clock are then passed to the deserializer module, which performs serial-to-parallel conversion and provides a 77.76 Mbits/s parallel data and clock at its output.

The HSI transmitter receives four channels of 77.76 Mbits/s parallel data that is synchronous to the reference clock at its inputs. The serializer performs a parallel-to-serial conversion using a 622.08 MHz clock provided by the PLL/synthesizer block. The 622 Mbits/s serial data streams are then transmitted through the LVDS drivers.

5-8592 (F)

Figure 3. HSI Functional Block Diagram

#### **STM Transmitter (FPGA -> Backplane)**

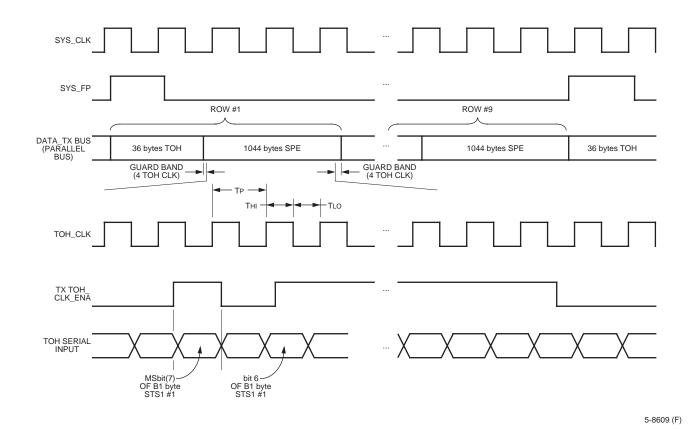

The STM has four STS-12 transmit channels which can be treated as a single STS-48 channel. In general, the transmitter circuit receives four byte-wide 77.76 MHz data from the FPGA, which nominally represents four STS-12 streams (A, B, C, and D). This data is synchronized to the system (reference) clock, and an 8 kHz system frame pulse from the FPGA logic. Transport overhead bytes are then optionally inserted into these streams, and the streams are forwarded to the HSI. All byte timing pulses required to isolate individual overhead bytes (e.g., A1, A2, B1, D1—D3, etc.) are generated internally based on the system frame pulse (SYS FP) received from the FPGA logic. All streams operate byte-wide at 77.76 MHz in all modes. The TOH processor operates from 25 MHz to 77.76 MHz and supports the following TOH signals: A1 and A2 insertion and optional corruption; H1, H2, and H3 pass transparently; BIP-8 parity calculation (after scrambling) and B1 byte insertion and optional corruption (before scrambling); optional K1 and K2 insert; optional S1/M0 insert; optional E1/F1/E2 insert; optional section data communication channel (DCC, D1—D3) and line data communication channel (DCC, D4—D12) insertion (for intercard communications channel); scrambling of outgoing data stream with optional scrambler disabling; and optional stream disabling.

When the ORT4622 is used in nonnetworking applications as a generic high-speed backplane data mover, the TOH serial ports are unused or can be used for slow-speed off-channel communication between devices.

Data received on the parallel bus is optionally scrambled and transferred to LVDS outputs.

#### **Byte Ordering Information**

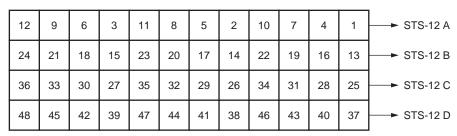

The core supports quad STS-12 mode of operation on the input/output ports. STS-48 is also supported when received in quad STS-12 format. When operating in quad STS-12 mode, each of the independent byte streams carries an entire STS-12 within it. Figure 4 reveals the byte ordering of the individual STS-12 streams and for STS-48 operation. Note that the recovered data will always continue to be in the same order as transmitted.

STS-48 IN QUAD STS-12 FORMAT

QUAD STS-12

5-8574 (F)

Figure 4. Byte Ordering of Input/Output Interface in STS-12 Mode

#### Transport Overhead for In Band Communication

The TOH byte can be used for In Band configuration, service, and management since it is carried along the same channel as data. In ORT4622, In Band signaling can be efficiently utilized, since the total cost of overhead is only 3.3%.

#### **Transport Overhead Insertion (Serial Link)**

The TOH serial links are used to insert TOH bytes into the transmit data. The transmit TOH data and TOH\_CLK\_EN get retimed by TOH\_CLK in order to meet setup and hold specifications of the device.

The retimed TOH data is shifted into a 288-bit (36-byte by 8-bit) shift register and then multiplexed as an 8-bit bus to be inserted into the byte-wide data stream. Insertion from these serial links or pass-through of TOH from the byte-wide data is under software control.

## Transport Overhead Byte Ordering (FPGA to Backplane)

In the transparent mode, SPE and TOH data received on parallel input bus is transferred, unaltered, to the serial LVDS output. However, B1 byte of STS#1 is always replaced with a new calculated value (the 11 bytes following B1 are replaced with all zeros). Also, A1 and A2 bytes of all STS-1s are always regenerated. TOH serial port in not used in the transparent mode of operation.

In the TOH insert mode, SPE bytes are transferred, unaltered, from the input parallel bus to the serial LVDS output. On the other hand, TOH bytes are received from the serial input port and are inserted in the STS-12 frame before being sent to the LVDS output. Although all TOH bytes from the 12 STS-1s are transferred into the device from each serial port, not all of them get inserted in the frame. There are three hard-coded exceptions to the TOH byte insertion:

- Framing bytes (A1/A2 of all STS-1s) are not inserted from the serial input bus. Instead, they can always be regenerated.

- Parity byte (B1 of STS#1) is not inserted from the serial input bus. Instead, it is always recalculated (the 11 bytes following B1 are replaced with all zeros).

- Pointer bytes (H1/H2/H3 of all STS-1s) are not inserted from the serial input bus. Instead, they always flow transparently from parallel input to LVDS output.

In addition to the above hard-coded exceptions, the source of some TOH bytes can be further controlled by software. When configured to be in pass-through mode, the specific bytes must flow transparently from the parallel input. Note that blocks of 12 STS-1 bytes forming an STS-12 are controlled as a whole. There are 15 software controls per channel, as listed below:

- Source of K1 and K2 bytes of the 12 STS-1s (24 bytes) is specified by a control bit (per channel control).

- Source of S1 and M0 bytes of the 12 STS-1s (24 bytes) is specified by a control bit (per channel control).

- Source of E1, F1, E2 bytes of the STS-1s (36 bytes) is specified by a control it (per channel control).

- Source of D1 bytes of the STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D2 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D3 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D4 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D5 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D6 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D7 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D8 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D9 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D10 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D11 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

- Source of D12 bytes of the 12 STS-1s (12 bytes) is specified by a control bit (per channel control).

TOH reconstruction is dependent on the transmitter mode of operation. In the transparent mode of operation, TOH bytes on LVDS output are as shown in Table 3.

Table 3. Transmitter TOH on LVDS Output (Transparent Mode)

| A1  | A1    | A1     | A1    | A1      | A1        | A1                             | A1                               | A1                                   | A1                  | A1                                       | A2                                           | A2                                         | A2                                           | A2                                           | A2                                           | A2                                           | A2                                           | A2                                             | A2                                             | A2                                             | A2                                             | A2                                                 |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|-----|-------|--------|-------|---------|-----------|--------------------------------|----------------------------------|--------------------------------------|---------------------|------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|--------------------------------------------------------|

| 0   | 0     | 0      | 0     | 0       | 0         | 0                              | 0                                | 0                                    | 0                   | 0                                        |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|     |       |        |       |         |           |                                |                                  |                                      |                     |                                          |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|     |       |        |       |         |           |                                |                                  |                                      |                     |                                          |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|     |       |        |       |         |           |                                |                                  |                                      |                     |                                          |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|     |       |        |       |         |           |                                |                                  |                                      |                     |                                          |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|     |       |        |       |         |           |                                |                                  |                                      |                     |                                          |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

| Reg | enera | ated b | ytes. |         |           |                                |                                  |                                      |                     |                                          |                                              |                                            |                                              |                                              |                                              |                                              |                                              |                                                |                                                |                                                |                                                |                                                    |                                                    |                                                    |                                                  |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                       |                                                        |

|     | Reg   | 0 0    | 0 0 0 | 0 0 0 0 | 0 0 0 0 0 | 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Regenerated bytes. |

Transparent bytes from parallel input port.

In the TOH Insert mode of operation, TOH bytes on LVDS output are shown in the following Table. This also shows the order in which data is transferred to the serial TOH interface, starting with the must significant bit of the first A1 byte. The first bit of the first byte is replaced by an even parity check bit over all TOH bytes from the previous TOH frame.

Table 4. Transmitter TOH on LVDS Output (TOH Insert Mode)

| A1  | <b>A</b> 1 | A1  | A1  | <b>A</b> 1 | A1  | A2  |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|------------|-----|-----|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| B1  | 0          | 0   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | E1  | F1  |

| D1  | D1         | D1  | D1  | D1         | D1  | D1  | D1  | D1  | D1  | D1  | D1  | D2  | D3  |

| H1  | H1         | H1  | H1  | H1         | H1  | H1  | H1  | H1  | H1  | H1  | H1  | H2  | Н3  | Н3  | НЗ  | Н3  | НЗ  | Н3  | Н3  | НЗ  | Н3  | Н3  | НЗ  | Н3  |

|     |            |     |     |            |     |     |     |     |     |     |     | K1  | K2  |

| D4  | D4         | D4  | D4  | D4         | D4  | D4  | D4  | D4  | D4  | D4  | D4  | D5  | D6  |

| D7  | D7         | D7  | D7  | D7         | D7  | D7  | D7  | D7  | D7  | D7  | D7  | D8  | D9  |

| D10 | D10        | D10 | D10 | D10        | D10 | D10 | D10 | D10 | D10 | D10 | D10 | D11 | D12 |

| S1  | S1         | S1  | S1  | S1         | S1  | S1  | S1  | S1  | S1  | S1  | S1  | M0  | MO  | M0  | MO  | MO  | E2  |

Regenerated bytes.

Inserted or transparent bytes. Blocks of 12 STS-1 bytes are controlled as a whole. There are 15 controls/channel: K1/K2, S1/M0, E1/F1/E2, D1, D2, D3, D4, D5, D6, D7, D8, D9, D10, D11, D12

Transparent bytes (from parallel input port).

Inserted bytes from TOH serial input port.

#### A1/A2 Frame Insert and Testing

The A1 and A2 bytes provide a special framing pattern that indicates where a STS-1 begins in a bit stream. All 12 A1 bytes of each STS-12 are set to 0xF6, and all 12 A2 bytes of the STS-12 are set to 0x28 when not overridden with an user-specified value for testing.

A1/A2 testing (corruption) is controlled per stream by the A1/A2 error insert register. When A1/A2 corruption detection is set for a particular stream, the A1/A2 values in the corrupted A1/A2 value registers are sent for the number of frames defined in the corrupted A1/A2 frame count register. When the corrupted A1/A2 frame count register is set to zero, A1/A2 corruption will continue until the A1/A2 error insert register is cleared.

On a per-device basis, the A1 and A2 byte values are set, as well as the number of frames of corruption. Then, to insert the specified A1/A2 values, each channel has an enable register. When the enable register is set, the A1/A2 values are corrupted for the number specified in the number of frames to corrupt. To insert errors again, the per-channel fault insert register must be cleared, and set again. Only the last A1 and the first A2 are corrupted.

#### **B1 Calculation and Insertion**

A bit interleaved parity –8 (BIP-8) error check set for even parity over all the bits of an STS-1 frame. B1 is defined for the first STS-1 in an STS-N only. The B1 calculation block computes a BIP-8 code, using even parity over all bits of the previous STS-12 frame after scrambling and is inserted in the B1 byte of the current STS-12 frame before scrambling. Per-bit B1 corruption is controlled by the force BIP-8 corruption register (register address 0F). For any bit set in this register, the corresponding bit in the calculated BIP-8 is inverted before insertion into the B1 byte position. Each stream has an independent fault insert register that enables the inversion of the B1 bytes. B1 bytes in all other STS-1s in the stream are filled with zeros.

#### Stream Disable

When disabled via the appropriate bit in the stream enable register, the prescrambled data for a stream is set to all ones, feeding the HSI. The HSI macro is powered down on a per-stream basis, as are its LVDS outputs.

#### Scrambler

The data stream is scrambled using a frame synchronous scrambler of sequence length 127. The scrambling function can be disabled by software. The generating polynomial for the scrambler is  $1 + x^6 + x^7$ . This polynomial conforms to the standard SONET STS-12 data format. The scrambler is reset to 1111111 on the first byte of the SPE (byte following the Z0 byte in the twelfth STS-1). That byte and all subsequent bytes to be scrambled are exclusive-ORed, with the output from the byte-wise scrambler. The scrambler runs continuously from that byte on throughout the remainder of the frame. A1, A2, J0, and Z0 bytes are not scrambled.

#### System Frame Pulse and Line Frame Pulse

System frame pulse (for transmitter) and line frame pulse (for receiver) are generated in FPGA logic. A1/A2 framing is used on the link for locating the 8 kHz frame location. All frames sent to the FPGA are aligned to the FPGA frame pulse LINE\_FP which is provided by the FPGA to the STM macro. All frames sent from the FPGA to the STM will be aligned to the frame pulse SYS\_FP that is supplied to the STM macro. In either directions, system frame pulse and line frame pulse are active for one system clock cycle, indicating the location of A1 byte of STS#1. They are common to all four channels.

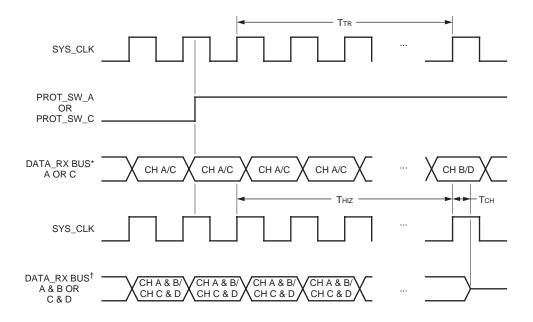

#### STM Receiver (Backplane -> FPGA)

The ORT4622 has four receiving channels that can be treated as one STS-48 stream, or treated as independent channels. Incoming data is received through LVDS serial ports at the data rate of 622 Mbits/s. The receiver can handle the data streams with frame offsets of up to ±12 bytes which would be due to timing skews between cards and along backplane traces. The received data streams are processed in the HSI and the STM, and then passed through the CIC boundary to the FPGA logic.

#### **Framer Block**

The framer block, in Figure 5, takes byte-wide data from the HSI, and outputs a byte-aligned, byte-wide data stream and 8 kHz sync pulse. The framer algorithm determines the out-of-frame/in-frame status of the incoming data and will cause interrupts on both an errored frame and an out-of-frame (OOF) state. The framer detects the A1/A2 framing pattern and generates the 8 kHz frame pulse. When the framer detects OOF, it will generate an interrupt. Also, the framer detects an errored frame and increments an A1/A2 frame error counter. The counter can be monitored by a processor to compile performance status on the quality of the backplane.

Because the ORT4622 is intended for use between it and another ORT4622 or other devices via a backplane, there is only one errored frame state. Thus after two transitions are missed, the state machine goes into the OOF state and there is no severely errored frame (SEF) or loss-of-frame (LOF) indication.

#### **B1 Calculate and Descramble (Backplane -> FPGA)**

Each Rx block receives byte-wide scrambled 77.76 MHz data and a frame sync from the framer. Since each HSI is independently clocked, the Rx block operates on individual streams. Timing signals required to locate overhead bytes to be extracted are generated internally based on the frame sync. The Rx block produces byte-wide (optionally) descrambled data and an output frame sync for the alignment FIFO block.

The B1 calculation block computes a BIP-8 (Bit Interleaved Parity 8-bits) code, using even parity over all bits of the previous STS-12 frame before descrambling; this value is checked against the B1 byte of the current frame after descrambling. A per-stream B1 error counter is incremented for each bit that is in error. The error counter may be read via the CPU interface.

**Descrambling.** The streams are descrambled using a frame synchronous descrambler of sequence length 127 with a generating polynomial of  $1 + x^6 + x^7$ . The A1/A2 framing bytes, the section trace byte (J0) and the growth bytes (Z0) are not descrambled. The descrambling function can be disabled by software.

AlS-L Insertion. Alarm indication signal (AIS) is a continuous stream of unframed 1s sent to alert downstream equipment that the near-end terminal has failed, lost its signal source, or has been temporarily taken out of service. If enabled in the AIS\_L force register, AIS-L is inserted into the received frame by writing all ones for all bytes of the descrambled stream.

**AIS-L Insertion on Out-of-Frame.** If enabled via a register, AIS-L is inserted into the received frame by writing all ones for all bytes of the descrambled stream when the framer indicates that an out-of-frame condition exists.

#### **Internal Parity Generation**

Even parity is generated on all data bytes and is routed in parallel with the data to be checked before the protection switch MUX at the parallel output.

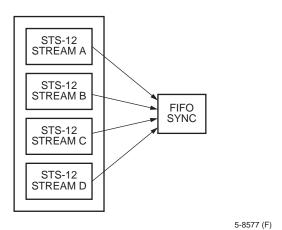

### FIFO Alignment (Backplane -> FPGA)

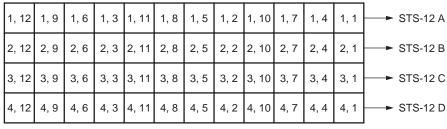

The alignment FIFO allows the transfer of all data to the system clock. The FIFO sync block (Figure 5) allows the system to be configured to allow the frame alignment of multiple slightly varying data streams. This optional alignment ensures that matching STS-12 streams will arrive at the FPGA end in perfect data sync. The frame alignment is configurable to allow for the possibility of fully independent (i.e., total frame misalignment) STS-12s.

Figure 5. Interconnect of Streams for FIFO Alignment

The incoming data from the clock and data recovery can be separated into four STS-12 channels (A, B, C, and D). These streams can be frame aligned in the patterns shown in Figure 6.

Figure 6. Alignment of Four STS-12 Streams

There is also a provision to allow certain streams to be disabled (i.e., not producing interrupts or affecting synchronization). These streams can be enabled at a later time without disrupting other streams.

The FIFO block consists of a 24 by 10-bit FIFO per link. This FIFO is used to align up to ±154.3 ns of interlink skew and to transfer to the system clock. The FIFO sync circuit takes metastable hardened frame pulses from the write control blocks and produces sync signals that indicate when the read control blocks should begin reading from the first FIFO location. On top of the sync signals, this block produces an error indicator which indicates that the signals to be aligned are too far apart for alignment (i.e., greater than 18 clocks apart). Sync and error signals are sent to read control block for

alignment. The read control block is synched only once on start-up; any further synchronization is software controlled. The action of resynching a read control block will always cause loss of data. A register allows the read control block to be resynched.

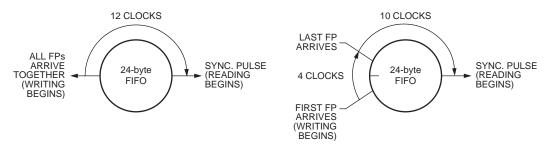

**Link Alignment.** The general operation of the link alignment algorithm is to wait 12 clocks (i.e., half the FIFO) from the arriving frame pulse and then signal the read control block to begin reading. For perfectly aligned frame pulses across the links, it is simply a matter of counting down 12 and then signaling the read control block.

The algorithm down counts by one until all of the frame pulses have arrived and then by two when they are all present. For example (Figure 7), if all pulses arrive together, then alignment algorithm would count 24 (12 clocks); if, however, the arriving pulses are spread out over four clocks, then it would count one for the first four pulses and then two per clock afterward, which gives a total of 14 clocks between first frame pulse and the first read. This puts the center of arriving frame pulses at the halfway point in the buffer. This is the extent of the algorithm, and it has no facility for actively correcting problems once they occur.

The write control block receives byte-wide data at 77.76 MHz and a frame pulse two clocks before the first A1 byte of the STS-12 frame. It generates the write address for the FIFO block. The first A1 in every STS-12 stream is written in the same location (address 0) in the FIFO. Also, a frame bit is passed through the FIFO along with the first byte before the first A1 of the STS-12. The read control block synchronizes the reading of the FIFO for streams that are to be aligned. Reading begins when the FIFO sync signals that all of the applicable A1s and the appropriate margin have been written to the FIFO. All of the read blocks to be synchronized begin reading at the same time and same location in memory (address 0).

The alignment algorithm takes the difference between read address and write address to indicate the relative clock alignments between STS-12 streams. If this depth indication exceeds certain limits (12 clocks), then an interrupt is given to the microprocessor (alignment overflow). Each STS-12 stream can be realigned by software if it gets too far out of line (this would cause a loss of data). For background applications that have less than 154.3 ns of interlink skew, misalignment will not occur.

PERFECTLY ALIGNED FRAMES

4-byte SPREAD IN ARRIVING FRAMES

5-8584 (F)

Figure 7. Examples of Link Alignment

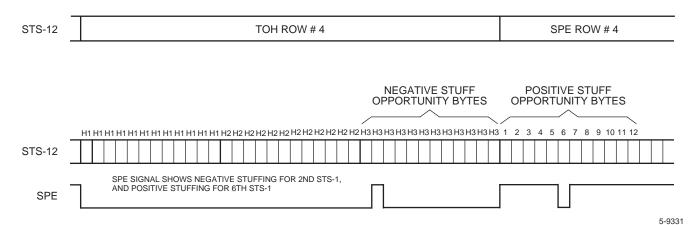

#### Pointer Mover Block (Backplane -> FPGA)

The pointer mover maps incoming frames to the line framing that is supplied by the FPGA logic. The K1/K2 bytes and H1-SS bits are also passed through to the pointer generator so that the FPGA can receive them. The pointer mover handles both concatenations inside the STS-12, and to other STS-12s inside the core.

The pointer mover block can correctly process any length of concatenation of STS frames (multiple of three) as long as it begins on an STS-3 boundary (i.e., STS-1 number one, four, seven, ten, etc.) and is contained within the smaller of STS-3, 12, or 48. See details in Table 5.

Table 5. Valid Starting Positions for an STS-Mc

| STS-1<br>Number | STS-3cSPE | STS-6cSPE | STS-9cSPE | STS-12cSPE | STS-15cSPE | STS-18c to<br>STS-48c<br>SPEs |

|-----------------|-----------|-----------|-----------|------------|------------|-------------------------------|

| 1               | YES       | YES       | YES       | YES        | YES        | YES                           |

| 4               | YES       | YES       | YES       | NO         | YES        | _                             |

| 7               | YES       | YES       | NO        | NO         | YES        | _                             |

| 10              | YES       | NO        | NO        | NO         | YES        | _                             |

| 13              | YES       | YES       | YES       | YES        | YES        | _                             |

| 16              | YES       | YES       | YES       | NO         | YES        | _                             |

| 19              | YES       | YES       | NO        | NO         | YES        | _                             |

| 22              | YES       | NO        | NO        | NO         | YES        | _                             |

| 25              | YES       | YES       | YES       | YES        | YES        | _                             |

| 28              | YES       | YES       | YES       | NO         | YES        | _                             |

| 31              | YES       | YES       | NO        | NO         | YES        | _                             |

| 34              | YES       | NO        | NO        | NO         | YES        | NO                            |

| 37              | YES       | YES       | YES       | YES        | NO         | NO                            |

| 40              | YES       | YES       | YES       | NO         | NO         | NO                            |

| 43              | YES       | YES       | NO        | NO         | NO         | NO                            |

| 46              | YES       | NO        | NO        | NO         | NO         | NO                            |

Note: YES = STS-Mc SPE can start in that STS-1.

NO = STS-Mc SPE cannot start in that STS-1.

<sup>— =</sup> YES or NO, depending on the particular value of M.

Pointer Interpreter State Machine. The pointer interpreter's highest priority is to maintain accurate data flow (i.e., valid SPE only) into the elastic store. This will ensure that any errors in the pointer value will be corrected by a standard, fully SONET compliant, pointer interpreter without any data hits. This means that error checking for increment, decrement, and new data flag (NDF) (i.e., eight of 10) is maintained in order to ensure accurate data flow. A single valid pointer (i.e., 0—782) that differs from the current pointer will be ignored. Two consecutive incoming valid pointers that differ from the current pointer will cause a reset of the J1 location to the latest pointer value (the generator will then produce an NDF). This block is designed to handle single bit errors without affecting data flow or changing state.

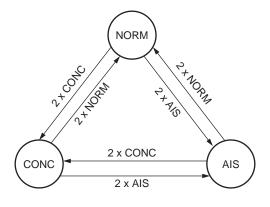

The pointer interpreter has only three states (NORM, AIS, and CONC). NORM state will begin whenever two consecutive NORM pointers are received. If two consecutive NORM pointers are received that both differ from the current offset, then the current offset will be reset to the last received NORM pointer. When the pointer interpreter changes its offset, it causes the pointer generator to receive a J1 value in a new position. When the pointer generator gets an unexpected J1, it resets its offset value to the new location and declares an NDF. The interpreter is only looking for two consecutive pointers that are different from the current value. These two consecutive NORM pointers do not have to have the same value. For example, if the current pointer is ten and a NORM pointer with offset of 15 and a second NORM pointer with offset of 25 are received, then the interpreter will change the current pointer to 25. The receipt of two consecutive CONC pointers causes CONC state to be entered. Once in this state, offset values from the head of the concatenation chain are used to determine the location of the STS SPE for each STS in the chain. Two consecutive AIS pointers cause the AIS state to occur. Any two consecutive normal or concatenation pointers will end this AIS state. This state will cause the data leaving the pointer generator to be overwritten with 0xFF.

5-8589 (F)

Figure 8. Pointer Mover State Machine

**Pointer Generator.** The pointer generator maps the corresponding bytes into their appropriate location in the outgoing byte stream. The generator also creates offset pointers based on the location of the J1 byte as indicated by the pointer interpreter. The generator will signal NDFs when the interpreter signals that it is coming out of AIS state. The pointer generator resets the pointer value and generates NDF every time a byte marked J1 is read from the elastic store that doesn't match the previous offset.

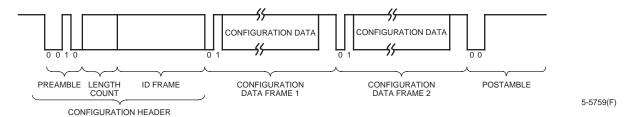

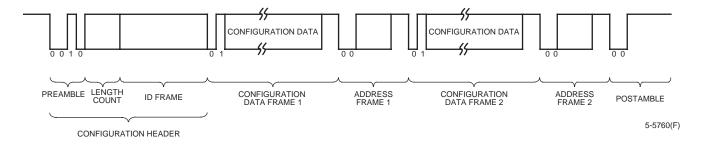

Increment and decrement signals from the pointer interpreter are latched once per frame on either the F1 or E2 byte times (depending on collisions); this ensures constant values during the H1 through H3 times. The choice of which byte time to do the latching on is made once when the relative frame phases (i.e., received and system) are determined. This latch point is then stable unless the relative framing changes and the received H byte times collide with the system F1 or E2 times, in which case the latch point would be switched to the collision-free byte time.