# ORCA® Series 4 MPI/System Bus

March 2002 Technical Note TN1017

## Introduction

The Lattice Semiconductor ORCA Series 4 devices contain an embedded microprocessor interface (MPI) that can be used to interface any Series 4 field-programmable gate array (FPGA) or field-programmable system chip (FPSC) to any MPC860/MPC8260 PowerPC microprocessor or compatible interface.

The MPI is available prior to and optionally after configuration of the programmable logic in the FPGA/FPSC. The MPI can be used prior to device configuration to identify, test, initialize, and download configuration data into the device. After configuration of the programmable logic, the MPI can be used to read back the configuration and internal status data, write or read the contents of the embedded random access memory (RAM) blocks, control parameters in the phase-locked loops (PLL), access status and control registers for an embedded FPSC block (if present), and interact with the users design configured in programmable logic.

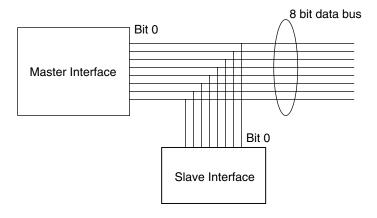

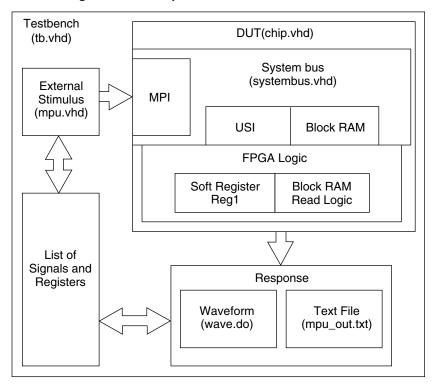

The MPI is one element on the embedded system bus illustrated in Figure 1. The system bus provides multi-master/multi-slave communication between the MPI and the status and configuration interface, the embedded RAM interfaces (RAMT, RAMB), the PLLs, the user logic interface (ULI), and one or more FPSC interface blocks as needed in each specific FPGA/FPSC device.

MPI System Bus Status and Config Embedded Block RAM (top) **PPLL** PPLL HPI I PII1 **ORCA Series 4 FPSC FPGA Array** Block PPLL PPLL **HPLL** PLL2 USI UMI EBR (bottom)

Figure 1. ORCA Series 4 Embedded System Bus Elements

This document describes the operation of each element on the embedded system bus and illustrates how to use these embedded features in conjunction with programmable logic in the device.

#### Terms used:

- MSB Most Significant Byte

- · MSb Most Significant Bit

- · LSB Least Significant Byte

- · LSb Least Significant Bit

- MPI Microprocessor Interface

- · UMI User Master Interface

- · USI User Slave Interface

· PLL - Phase-Lock Loop

· EBR - Embedded Block RAM

# **System Bus**

The embedded system bus on the ORCA Series 4 ties all of the programmable elements together in a bus framework. There are two types of interfaces on the system bus; master and slave. A master interface has the ability to perform actions on the bus such as writes and reads to and from a specific address. A slave interface responds to the actions of a master by accepting data and address on a write and providing data on read. The system bus has a memory map which describes each of the slave peripherals that is connected on the bus. Using the addresses listed in the memory map a master interface can access each of the slave peripherals on the system bus. Any and all peripherals on the system bus can be used at the same time. Table 1 lists all of the available user peripherals on the system bus.

Table 1. System Bus User Peripherals

| Peripheral            | Interface Type                       |

|-----------------------|--------------------------------------|

| MPI                   | Master                               |

| User Master Interface | Master                               |

| User Slave Interface  | Slave                                |

| PLLs                  | Slave                                |

| Embedded Block RAMs   | Slave                                |

| FPSC                  | Master or Slave (Specific to Device) |

The system bus decodes 18 bits (256k addresses) in the device address space. The address space is divided into eight address ranges as shown in Table 1. The contents of some address ranges will vary slightly from device to device. For example, the number of block RAMs implemented in RAM banktop (RAMT) and RAM bankbottom (RAMB) will be different from one device to another based on the size of the device. Likewise, generic Series 4 FPGAs do not implement any registers in the FPSC address range, while each FPSC device implements various functions consistent with the requirements of a specific embedded core.

Table 2. System Bus Address Ranges

| Start Address | End Address | Size | Description                                        |

|---------------|-------------|------|----------------------------------------------------|

| 0x00000       | 0x001FF     | 1k   | Status and control registers (STAT)                |

| 0x00200       | 0x07FFF     | 31k  | Reserved                                           |

| 0x08000       | 0x0FFFF     | 32k  | User logic slave interface (ULI)                   |

| 0x10000       | 0x17FFF     | 32k  | RAM banktop (up to 16 banks of data and parity)    |

| 0x18000       | 0x1FFFF     | 32k  | Reserved for parity bit storage                    |

| 0x20000       | 0x27FFF     | 32k  | RAM bankbottom (up to 16 banks of data and parity) |

| 0x28000       | 0x2FFFF     | 32k  | Reserved for parity bit storage                    |

| 0x30000       | 0x3FFFF     | 64k  | FPSC slave interface (FPSC)                        |

#### Multi Master

The system bus is a multiple master bus meaning that there can be more than one bus master present on the bus at the same time. A single bus arbiter controls the traffic on the bus by ensuring only one master has access to the bus at any time. This bus arbiter monitors a number of different requests to use the bus and decides which request is currently the highest priority. The configuration logic has the highest priority and overrides all normal user interfaces. By default, all master interfaces have equal priority when requesting the embedded system bus, and a fair round robin scheme is used to rotate arbitration priority. Optionally, you can specify a priority of low=1, medium=2, or high=3 for each master interface in SCUBA® (discussed later). As a result, if all three master interfaces are waiting for the system bus, an interface with higher priority will be granted the bus over one with a lower priority. If two requesting interfaces share the same priority, the round robin scheme will rotate arbitration priority.

# System Bus Clock (HCLK)

The system bus is a synchronous element that has an internal clock. This clock is sometimes referred to as the HCLK. Each of the peripherals on the system are also synchronous and have an interface clock. This peripheral clock is the clock that the FPGA designer sources to the peripheral to clock data in and out of the user interface and eventually onto the system bus. The system bus itself needs to be sourced by a clock (HCLK). This main system bus clock is the clock on which all of the traffic will run through the system bus. As traffic is passed to and from each peripheral a domain change will occur from the system bus clock domain to the peripheral domain. For burst and single transfers this domain change is taken care of inside the system bus.

The system bus clock can be driven from several sources; CCLK, JTAG TCK, MPI, FPSC, User, or Oscillator. Before the bitstream is loaded into the FPGA (pre-configuration) the system bus clock is selected via the mode pins. After the bitstream has been successfully loaded into the FPGA the system bus clock is selected by the bitstream programming in the FPGA design.

#### **CCLK**

Before a bitstream is loaded and during device configuration and reconfiguration the system bus clock is defaulted to the configuration clock (CCLK). The CCLK is either an input or output of the FPGA depending on the configuration mode pins state. The CCLK is driven internally on the system bus from the configuration logic block. There will be no input or output pin associated on the system bus module for the CCLK. Using the CCLK is for pre-configuration only and can not be simulated.

#### **JTAG TCK**

If the user interrupts the configuration cycle with a JTAG program the TCK clock will then drive the system bus clock and configuration logic. The JTAG TCK clock is also selected during a readback via the built-in JTAG test access port during device operation. The JTAG TCK clock is driven internally on the system bus from the configuration logic block. There will be no input or output pin associated on the system bus module for the JTAG TCK. Using the JTAG TCK is for pre-configuration and readback only and can not be simulated.

#### MPI

If the user has selected to program the device via the MPI then the microprocessor clock will drive the system bus during configuration. In post configuration the MPI option is set via the bitstream and will select the clock on the MPI to drive the system bus. The MPI clock corresponds to the input mpi\_clk on the system bus module. This is most often selected since the MPI is the master most often used to access the system bus and its peripherals. Using the MPI clock the system bus clock can be driven up to speeds of 66MHz.

#### **FPSC**

The FPSC option allows the embedded ASIC block of the FPGA to drive the system bus clock. The FPSC Configuration Wizard will connect the FPSC to the system bus module in the FPSC template. The FPSC clock will be connected to the correct module pin on the system bus for this mode.

#### User

The User clock allows the FPGA design to source a clock to drive the system bus clock. This user clock input port is provided on the usr\_clk port of the system bus. The user clock can be used to create a synchronous interface

between the user interfaces (master and slave) and the system bus. To create a synchronous interface between the interfaces simply use the same clock source for the usr\_clk and interface clocks um\_clk and us\_clk.

The user clock is driven from the FPGA design and thus can be driven by any signal in the user's design. If the user clock is derived in any way from the output of a PLL, changing the PLL control register will not be allowed. When changing the PLL control register the output clock from the PLL will stop for a period of time. If this clock stops the user clock will stop and thus the HCLK will stop. If the HCLK stops the system bus will lock. The PLL control register will not be able to be changed and the FPGA will lock. To prevent this condition do not drive this signal with a PLL output or do not change the PLL control register for this PLL.

#### Oscillator

The Oscillator option allows the internal configuration oscillator to drive the system bus clock. The internal oscillator drives the CCLK during master mode pre-configuration. This is a valid option to select for the system bus clock driver, but does not have a practical application after configuration.

# **System Bus Interrupts**

The system bus has the ability to generate and accept interrupt signals from several peripherals. These interrupts can then be used to alert either on chip modules or external modules. An internal interrupt can be generated from the FPGA design, the configuration block during device configuration, or from the embedded ASIC block of an FPSC. The interrupt cause register (0x00010) contains a bit for each source of an interrupt. When one of the peripherals sets an interrupt the particular bit in the cause register will bet set to a 1. To clear the interrupt cause bit a master interface will need to write a 1 to clear the bit.

Some peripherals on the system bus can pass interrupts found in the interrupt cause register through their interface. For a peripheral to pass interrupts through the interface the interrupt enable register must be properly provisioned. There is an interrupt enable register for each possible master interface; MPI (active low mpi\_irq), User (active hi user\_irq), and FPSC. When a bit is set to a 1 in the interrupt enable register (0x00011 - 0x00013), this corresponding interrupt will be passed through the peripheral. When the interrupt signal for the peripheral indicates an interrupt was created, a master should read the interrupt cause register to determine the source of the interrupt.

For example, to pass interrupts created by device configuration to the MPI the interrupt enable register (0x00013) must set the CFG\_IRQ and CFG\_ERR bits. When the configuration logic throws an interrupt CFG\_IRQ and CFG\_ERR in the interrupt cause register will go to a 1. These interrupts will then drive the mpi\_irq pin low to indicate an interrupt to the microprocessor. The microprocessor should then read the interrupt cause register to determine that the interrupt came from the configuration block.

For more information on the interrupt cause register and interrupt enable register refer to the system bus memory map.

# **Address and Data Bus Ordering**

The system bus handles bus transfers of address and data at all of its interfaces. The orientation of the address bus and the data bus may be different depending on which peripheral is accessed. Internally on the bus the address bus is always oriented the same, where the data bus is dependent on the driving master/slave interface.

There are 18 address bits (17:0) on the system bus. These address lines can be driven by any of the master interfaces on the system bus. The address bus on a slave interface will always be provided to the slave with bit 0 as the LSb. For the master interfaces (MPI, User, and FPSC) the address bus is dependent on the master. The user interface will use the same orientation as the slaves, bit 17 as the MSb and bit 0 as the LSB. The FPSC interface will be dependent on the FPSC implementation. The MPI will match the PowerPC address bus orientation which is bit 0 MSb and bit 31 the LSb. More information on this address bus and its connections are found in the MPI section of this document.

The data bus on the system bus is 36 bits wide, 32 bits for data and 4 bits for optional parity. On the system bus the data bits are passed unchanged through the peripherals. So the orientation of the data on the system bus and is dependent on the data driving master/slave interface. This means that bit 0 on the master interface will be bit 0 on

the slave interface, bit 1 will be bit 1, etc. So if bit 0 is the LSb on the master interface then bit 0 will be the LSb on the slave interface as shown in Figure 2. Care must be taken by the user when accessing an address location to make sure data bits are used properly in terms of LSb and MSb.

Figure 2. System Bus Data Bus Bit Mapping

#### **Internal Data Bus**

The internal data bus is labeled d(35:0). Bits d(31:0) are used to carry the data between peripherals. Bits d(35:32) are used to carry parity to the peripherals. Parity is not checked internally by any of the peripherals on the system bus. If parity is enabled (SCUBA), internal non-user defined registers will generate parity for read operations. User parity is only passed through the system bus and its interfaces. Parity is mapped to byte lanes as shown in Table 3. The orientation of the data bus d(31:0) depends on the master interface driving the data bus, but the parity bits are always stored on d(35:32).

Table 3. Internal Data Bus Bit Mapping

| Internal<br>Data Bus | MPI                                           | User<br>Master Interface | Description                                                                                          |

|----------------------|-----------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------|

| D(35)                | Mpi_parity(4)                                 | Um_w/rdata(35)           | Parity bit for d(31:24)                                                                              |

| D(34)                | Mpi_parity(3)                                 | Um_w/rdata(34)           | Parity bit for d(23:16)                                                                              |

| D(33)                | Mpi_parity(2)                                 | Um_w/rdata(33)           | Parity bit for d(15:8)                                                                               |

| D(32)                | Mpi_parity(1)                                 | Um_w/rdata(32)           | Parity bit for d(7:0)                                                                                |

| D(31:24)             | Mpi_data(31:23) 32-bit LSB, bit 31 = LSb      | Um_w/rdata(31:24)        | Data byte 31:24 - LSB of the MPI in 32-bit mode.                                                     |

| D(23:16)             | Mpi_data(23:16), bit 23 = LSb                 | Um_w/rdata(23:16)        | Data byte 23:16                                                                                      |

| D(15:8)              | Mpi_data(15:8), 16-bit LSB, bit 15 = LSb      | Um_w/rdata(15:8)         | Data byte 15:8, LSB of the MPI in 16-bit mode                                                        |

| D(7:0)               | Mpi_data(7:0), 8-bit LSb=7, 16-bit/32-bit MSB | Um_w/rdata(7:0)          | Data byte 7:0, MSB of the MPI in 16/32-bit mode. In MPI 8-bit mode bit 0 is MSb and bit 7 is the LSb |

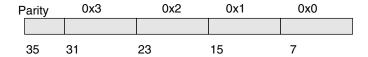

### 32-bit Data Bus

When a master interface is configured for 32-bit operation all 32 bits (d(31:0)) are used to carry the data. If the master interface is using parity, then the four parity bits will be carried on d(35:32) using the parity byte mapping previously described. Again, the orientation (MSb,LSb) of the data bus depends on which master/slave interface drives data onto the system bus. When using a 32-bit data bus the address resolution will be limited to 32-bit boundaries. Data will be carried on the bus such that the lowest address maps to byte lane d(31:24) and the highest address maps to byte d(7:0).

For example a 32-bit read at address 0x00000 will read addresses 0x00000 - 0x00003. Address 0x00000 data will be on d(7:0), address 0x00001 data will be on d(15:8), address 0x00002 data will be on d(23:16), and address 0x00003 data will be on d(31:24) as shown in Figure 3.

Figure 3. 32-bit Data Bus

## 16-Bit Data Bus

For 16-bit operation of a master interface the data will be carried on d(15:0). The slave interface will only need to read data from d(15:0). The MSB and LSB of the data will be determined by how the data was driven onto the bus by the master/slave interface. When using a 16-bit data bus the address resolution will be limited to 16-bit boundaries. Data will be carried on the bus such that the lowest address maps to byte lane d(15:8) and the highest address maps to byte d(7:0). The same data will also be replicated on d(31:16) along with parity(3:2).

For example a 16-bit read at address 0x00000 will read addresses 0x00000 - 0x00001. Address 0x00000 data will be on d(7:0) and address 0x00001 data will be on d(15:8) as shown in Figure 4.

Figure 4. 16-bit Data Bus

| Parity | 0x1 | 0x0 | 0x1 | 0x0 |  |

|--------|-----|-----|-----|-----|--|

|        |     |     |     |     |  |

| 35     | 31  | 23  | 15  | 7   |  |

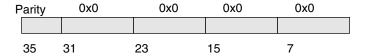

#### 8-Bit Data Bus

For 8-bit operation of a master interface the data will be carried on d(7:0). The slave interface will only need to read and write data on d(7:0). The same data will also be replicated on d(31:24), d(23:16), and d(15:8) along with parity(3:1) as shown in Figure 5. The MSb and LSb of the data will be determined by the master/slave interface.

Figure 5. 8-Bit Data Bus

## **MPI Data/Address Ordering**

When using the MPI, the external chip data bus is labeled  $mpi_d(0:31)$  for a 32 bit bus. For the PowerPC  $mpi_d(0)$  is the MSb while  $mpi_d(31)$  is the LSb. The internal system bus data is d(35:0). The data bus on the system is a one to one mapping of bits. So  $mpi_d(0)$  connects to internal data bus bit d(0) as the MSb of the PowerPC. The resulting slave interface will see d(0) as the MSb.

Example: PowerPC writes an 8-bit value of 0x01 to a USI address.

Table 4. Example of MPI to USI

| Data Bus | MPI     | Internal | Us_rdata |

|----------|---------|----------|----------|

| Bit 0    | 0 (MSb) | 0        | 0        |

| Bit 1    | 0       | 0        | 0        |

| Bit 2    | 0       | 0        | 0        |

| Bit 3    | 0       | 0        | 0        |

| Bit 4    | 0       | 0        | 0        |

| Bit 5    | 0       | 0        | 0        |

| Bit 6    | 0       | 0        | 0        |

| Bit 7    | 1       | 1        | 1        |

For the PowerPC a value of 0x01 will have bit 7 '1' with 0:6 bits '0'. On the internal data bus the bits map directly and on the resulting USI the data bits map directly as shown in Table 4. If the designer wants a value of 0x01 to be pulled off the us\_rdata bus the orientation will need to be the same as the MPI with bit 0 as the MSb.

Mydata <= us\_rdata(0:7)

# **User Master Data Ordering**

The user master interface on the system bus is defined by the FPGA design. The data bus orientation designed for the user master interface should match the targets of the user master interface. If the user master interface is targeting specific status and control registers, the orientation of the status and control registers will dictate the MSb and LSb of the data bus.

# **FPSC Master Interface Data Ordering**

The FPSC master interface on the system bus is defined by the FPSC block. The FPSC block design will dictate the data bus orientation on the slave interfaces the master references. The FPSC master interface is very specific to the FPSC device being used. More information on specific interfaces are provided in the FPSC data sheets.

# **System Bus Peripherals**

The following section discusses each of the peripherals on the system bus in detail. Some of the peripherals on the system bus do not have FPGA design user ports and are fully contained inside the system bus. These peripherals' registers will be described in the memory map and do not have any user inputs or outputs on the system bus.

#### PowerPC MPI

The microprocessor interface (MPI) acts as a bridge between an external PowerPC processor and the embedded system bus. Externally the MPI acts as a slave peripheral interface through which a PowerPC can access the embedded features of the device. Internally the MPI acts as a master peripheral interface on the system bus to initiate data transfers as directed by the external processor.

The PowerPC interface built into the Series 4 ORCA devices is based on the PowerPC Big Endian mode of operation. Series 4 ORCA devices will bolt up gluelessly to a PowerPC in this mode only.

## **MPI Interface**

Table 5 shows the MPI signals used by the PowerPC to perform transactions with the ORCA device. The MPI is a fixed block on the FPGA array and the interface signals are mapped to dedicated pins on the ORCA device. PowerPC pins to ORCA pins mapping can be found in the appendix of this application note.

Externally the MPI implements a 36-bit PowerPC bus slave which internally drives the system bus as a master. data bus width is selectable among 8 bits, 16 bits, and 32 bits with parity of 1, 2, or 4 bits, respectively (one parity

bit for each active byte). Note that the MPI does not check or generate parity, but simply passes it from the PowerPC bus to the system bus and vice versa. It is left to the other peripherals on the system bus to check or generate correct parity.

Table 5. MPI Signals to PowerPC Bus

| Name            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPI_CLK         | I   | This is the clock from the PowerPC (CLKOUT). This clock input will clock the MPI. This clock may optionally clock the main system bus clock if selected. The MPI clock can be driven up to 66Mhz operation.                                                                                                                                                                                                                                                                                                                                                                          |

| MPI_TSZ(0:1)    | I   | Transfer size (00-double word, 10-word, 01-byte). The MPI_TSZ pins connect directly up to the PowerPC TSIZ1 and TSIZ0. These pins select the size of the PowerPC data transaction. This is the transfer size of the data transaction from the microprocessor's perspective. This is different from the MODE pin selected size discussed later.                                                                                                                                                                                                                                       |

| MPI_RDWR_N      | I   | Transfer type (0-write, 1-read). This signal indicates to the MPI whether the transaction initiated by the microprocessor is a read or a write. If the transaction is a read data will be provided to the microprocessor from the address specified. If the transaction is a write data will be written to the address specified by the microprocessor inside the ORCA device. This signal connects to the PowerPC RD//WR signal.                                                                                                                                                    |

| MPI_BURST       | I   | Indicates that a burst transfer is in progress when low. This signal informs the MPI that the PowerPC is performing a burst transaction using the PowerPC burst pin.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MPI_BDIP        | I   | Burst Data In Progress. This signal from the PowerPC will go low on the first clock of data during a burst and go high on the last clock of data of the burst transfer.                                                                                                                                                                                                                                                                                                                                                                                                              |

| MPI_STRBn       | I   | This active low signal indicates the start of a transactions or the strobe. This pin is connected to the TS pin of the PowerPC.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CS0n/CS1        | I   | Chip selects for active high (CS1) and active low (CS0n). Both of these chip selects must be active for the ORCA device to be selected. Typically CS1 is connected to logic 1 and CS0n is connected to a PowerPC CS pin.                                                                                                                                                                                                                                                                                                                                                             |

| MPI_ADDR[14:31] | I   | The PowerPC address bus is 32 bits wide. The Series 4 ORCA devices only support 18 bits of address space. The ORCA uses the least significant bits of the PowerPC address space using address bits 14:31.                                                                                                                                                                                                                                                                                                                                                                            |

| MPI_DATA[0:31]  | I/O | The PowerPC data bus can be up to 32 bits wide. Bit 0 is the MSb and bit 31 is the LSb. For multibyte transfers, the most significant byte has the lowest address. The PowerPC data pins D[0:31] connect directly to the ORCA pins mpi_data(0:31). Data pins not used by virtue of selecting 8-bit or 16-bit data widths are available as general-purpose user I/O.                                                                                                                                                                                                                  |

| MPI_PARITY[0:3] | I/O | Parity can be up to 4 bits wide depending on the data bus size. Parity connects directly to the PowerPC DP[0:3] pins. Parity pins not used by virtue of selecting 8-bit or 16-bit data widths are available as general-purpose user I/O.                                                                                                                                                                                                                                                                                                                                             |

| MPI_TA          | 0   | This active low signal indicates the transfer acknowledge from the ORCA device. This pin is connected to the TA pin of the PowerPC. For a MPI write transaction the mpi_ta will come back on the next clock. See Consecutive Writes section. For a MPI read transaction the mpi_ta will come back after the target slave responds. The result is a difference in time it takes to complete a transaction depending on the slave that is accessed. Other dependencies are the clock rate of the system bus (HCLK), clock rate of the slave interface, and slave acknowledge protocol. |

| MPI_TEA         | 0   | This active low signal indicates a transfer error acknowledge during the current transaction. More information on cause of this error can be found under MPI exceptions.                                                                                                                                                                                                                                                                                                                                                                                                             |

| MPI_IRQ         | 0   | Active-low interrupt request from the ORCA device. See system bus interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MPI_RETRY       | 0   | Active-low request for processor to relinquish the bus and retry the cycle. Exception signal indicating the ORCA device is not ready to accept the requested transaction. More information on the cause of this error can be found under MPI exceptions.                                                                                                                                                                                                                                                                                                                             |

| MODE[3:0]       | I   | MPI data width (1010, 1011, 1110 => 8, 16, 32-bits, respectively). The MODE pins are used to select the type of bitstream configuration the ORCA device will utilize. More information on the MODE pins can be found under the MPI configuration section.                                                                                                                                                                                                                                                                                                                            |

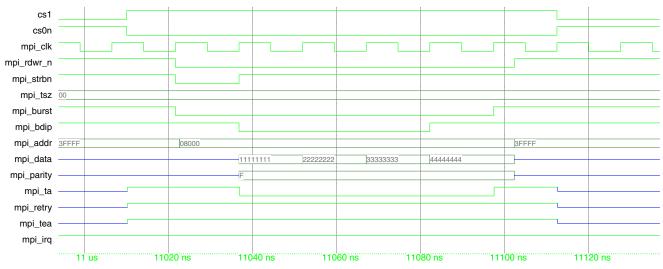

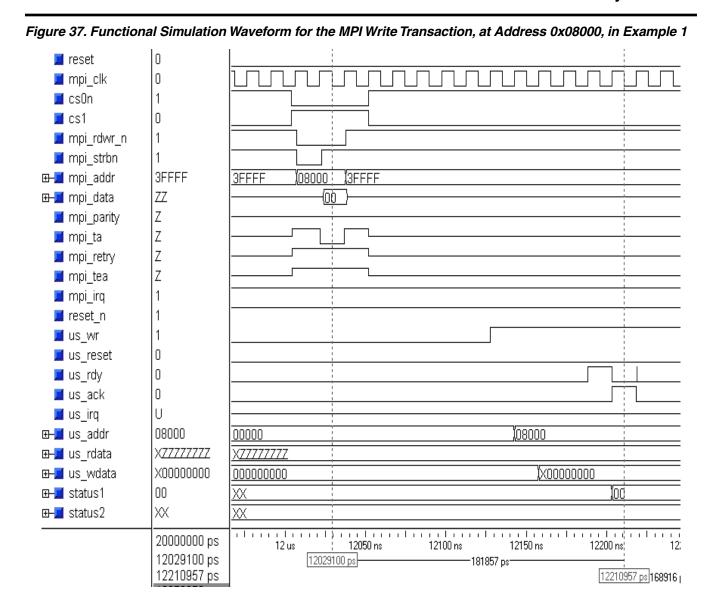

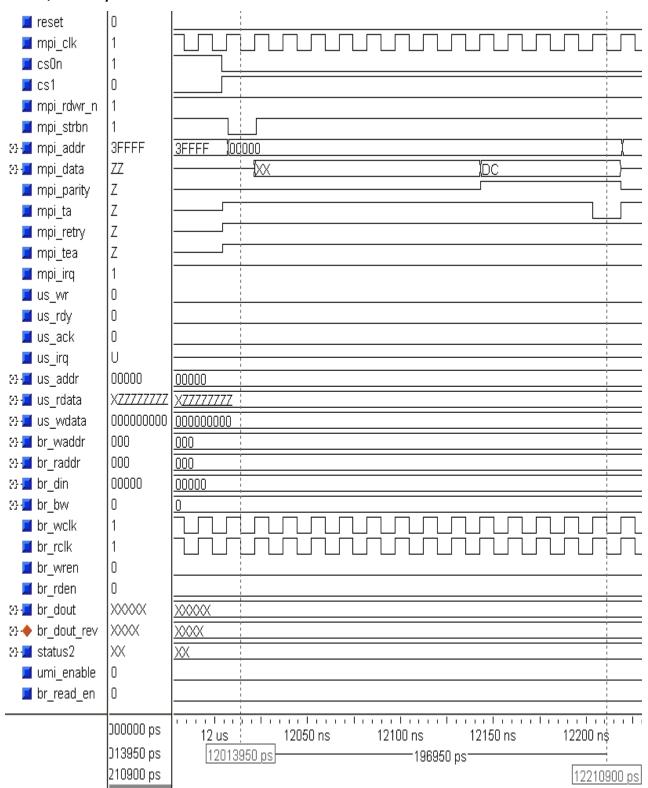

cs0n cs1 mpi\_clk mpi\_rdwr\_n mpi\_strbn mpi\_tsz mpi\_burst mpi\_bdip 3FFFF mpi addr OFFFFFF mpi\_data XXXXXXXX mpi\_parity mpi ta mpi\_retry mpi\_tea mpi\_irq 11050 ns 11100 ns 11250 ns 11300 ns 11350 ns Entity:tb Architecture:behave Date: Wed Mar 06 08:54:03 Central Daylight Time 2002 Row: 1 Page: 1

Figure 6. MPI Single Beat Data Transfer Timing

#### **MPI Burst Transfers**

The MPI will support burst transfers of 4 beats (32-bit width), 8 beats (16-bit width), or 16 beats (8-bit width), depending upon the selected data bus width. Burst transfers can be of any size that is compatible with the selected data bus width given the limitation that the MPI will handle 4, 8, or 16 beats as indicated.

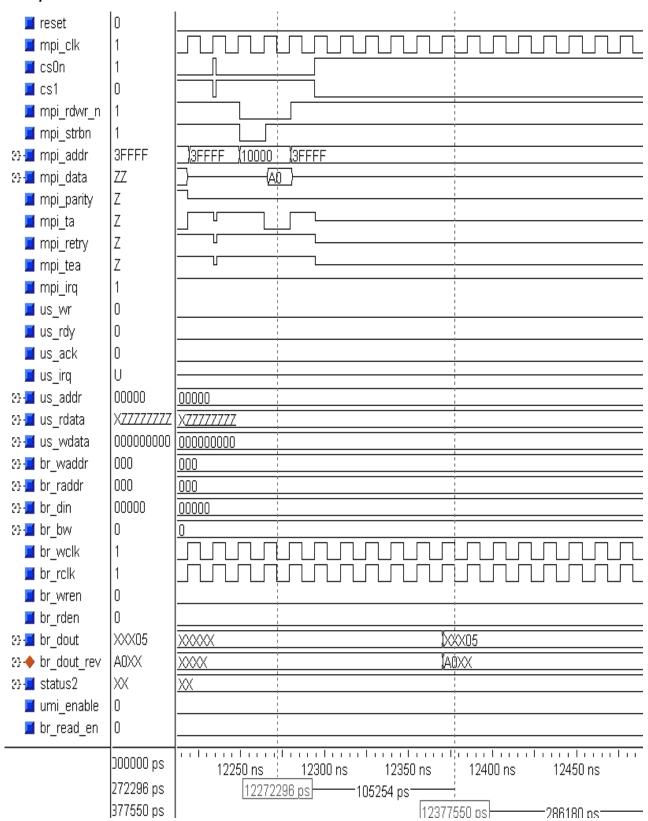

The burst mechanism uses MPI\_BURST to indicate that the transfer is a burst transfer and MPI\_BDIP to indicate the duration of the burst. Figure 7 shows the signal timing for a 4-beat burst write. Figure 8 shows the signal timing for a 4-beat burst read.

Figure 7. MPI Burst Write Transfer Timing

Entity: Architecture: Date: Wed Mar 06 09:32:20 Central Daylight Time 2002 Row: 1 Page: 1

cs0n mpi\_clk mpi\_rdwr\_n mpi strbn mpi tsz od mpi burst mpi bdip mpi\_addr 3FFFF mpi\_data mpi\_parity mpi ta mpi\_retry mpi\_tea mpi\_irq 11800 ns 11900 ns 12050 ns

Figure 8. MPI Burst Read Transfer Timing

Entity: Architecture: Date: Wed Mar 06 09:32:51 Central Daylight Time 2002 Row: 1 Page: 1

Along with the address and transfer control signals, the PowerPC asserts MPI\_BURST during the address phase of the transfer. In the data phase, the microprocessor asserts MPI\_BDIP until the next to the last word is received. The MPI continues to send/receive data until it detects MPI\_BDIP deasserted at the rising edge of MPI\_CLK while MPI\_TA is asserted.

## **Consecutive Writes with the MPI**

The MPI uses a single write post buffer implementation. This means that on each MPI write, the MPI\_TA comes back on the next clock cycle to terminate the PowerPC transaction. Internally on the MPI and system bus the data is not yet transmitted to the target. It will take several HCLK clock cycles before the target receives the data and terminates the transaction. Until this termination takes place any additional writes from the MPI will issue a retry (MPI\_RETRY).

The number of PowerPC clock cycles (MPI\_CLK) it takes until the next write can take place without a retry is variable. The variables include the source of the HCLK, the target being accessed, and the target's termination protocol and clock. The user should add appropriate delay based on their board and system behavior.

## **MPI Exceptions**

Three signals, MPI\_TEA, MPI\_RETRY, and MPI\_TA are monitored during the termination phase of a transfer. A normal termination is indicated when MPI\_TA is asserted and both MPI\_TEA and MPI\_RETRY are deasserted. If either MPI\_TEA or MPI\_RETRY are asserted, a MPI bus exception is indicated.

MPI\_TEA is asserted for one MPI\_CLK cycle to indicate either an internal system bus error, or a transfer with MPI\_TSZ larger than the data port size, or physical data size selected by the MODE[3:0] inputs.

MPI\_RETRY is asserted for one MPI\_CLK cycle when the MPI is busy to request that the PowerPC relinquish the bus and reissue the current transfer. A retry is issued when the following occurs:

- 1. The MPI gets a read transaction while its write FIFOs are not empty.

- 2. The MPI gets a write transfer while its write FIFOs are full.

- 3. The MPI receives a retry indication from the embedded system bus during a read transfer.

For burst transfers, the MPI will issue retry before acknowledging the first data phase; if MPI\_RETRY is asserted after the first data phase of a burst transfer, it should be treated as a transfer error (MPI\_TEA).

## **Enabling the MPI**

To enable the MPI at power-up, prior to device configuration, the external MODE pins (Table 6) must be set to specify one of the three MPI configuration modes as specified in the ORCA Series 4 data sheet. If the MPI is not used all of the MPI pins (mpi\_ta, mpi\_data, etc.) are tristated during configuration.

Table 6. ORCA Device Configuration Modes

| М3 | M2 | M1 | МО | Description                          |

|----|----|----|----|--------------------------------------|

| 0  | 0  | 0  | 0  | Serial master (high-speed)           |

| 0  | 1  | 0  | 0  | Parallel master (high-speed)         |

| 0  | 1  | 0  | 1  | Asynchronous peripheral (high-speed) |

| 0  | 1  | 1  | 1  | Reserved                             |

| 1  | 0  | 0  | 0  | Serial master (low-speed)            |

| 1  | 0  | 0  | 1  | Parallel slave                       |

| 1  | 0  | 1  | 0  | MPC860 8-bit                         |

| 1  | 0  | 1  | 1  | MPC860 16-bit                        |

| 1  | 1  | 0  | 0  | Parallel master (low-speed)          |

| 1  | 1  | 0  | 1  | Asynchronous peripheral (low-speed)  |

| 1  | 1  | 1  | 0  | MPC860 32-bit                        |

| 1  | 1  | 1  | 1  | Serial slave                         |

Data port width is determined at power-up by the value presented on the MODE pins during the low-to-high transition of the INIT signal. The MODE pins select the data size of the transaction including the parity bits. MPC860 8-bit mode will also use mpi\_parity(0) along with the data. MPC860 16-bit will use mpi\_parity(0:1) and MPC860 32-bit will use mpi\_parity(0:4). Unused mpi\_parity bits will be tristated during configuration. All of the other MPI signals connect directly to the PowerPC bus. Pad locations vary depending upon device type, size, and package.

The data port width selected by the MODE[3:0] pins is not related to the transfer size specified by MPI\_TSZ[0:1]. The port width selected by the MODE[3:0] pins determines how many data pins are used by the MPI, while the transfer size is determined by the master interface on the PowerPC bus. The transfer size used by an external master must not exceed the selected data port width; otherwise, the higher-order data bits will be lost and a bus exception is issued by the MPI.

To enable the MPI for use after device configuration and during normal operation, the user must instantiate the system bus with an MPI peripheral in the FPGA design. The system bus element along with the MPI is created using SCUBA and is discussed later in this document.

A third option of enabling the MPI is also available that is good for debugging purposes. The MPI can be enabled during normal operation by setting the MPI\_USR\_ENABLE bit in the command register (0x08 bit 2). This is done either by writing to the control register prior to device configuration (if the MPI is enabled via the MODE pins). If the MPI\_USR\_ENABLE bit is not set, MPI signal pins revert to general purpose I/O pins once the configuration process is completed. Using this bit the user can utilize the MPI in the design without having to modify the HDL code to instantiate the system bus. This aids in debugging by now allowing visibility into the control and status registers.

If the MPI is not utilized at all in the FPGA design the dedicated MPI pins can be used as general I/O pins for the user's design. More information on MPI configuration of the ORCA Series 4 devices can be found in technical note number TN1013, ORCA Series 4 FPGA Configuration.

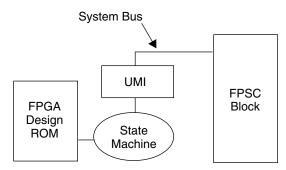

## **User Master Interface (UMI)**

The user logic master interface (UMI) allows the FPGA design to perform transactions on the system bus. Through the UMI the FPGA design has access to any and all of the slave peripherals on the system bus. Signals for the user logic master interface are listed in Table 7.

Table 7. User Logic Master Interface Signals

| Signal         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| um_clk         | I    | The main clock for the user master interface. This clock only clocks the interface registers. A domain change is made from the um_clk domain to the system bus clock domain. The user master interface and the system bus can be made synchronous by using the same clock for the um_clk and usr_clk and selecting User as the HCLK. A frequency preference on this signal will constrain all of the inputs and outputs of the UMI.                    |

| um_reset       | I    | This active-high reset resets all of the controls in the user master interface. This should be pulsed once before any transactions can occur on the UMI. This is typically connected to the same reset as the GSR and pulsed at power-up.                                                                                                                                                                                                              |

| um_wdata[35:0] | I    | 36-bit write data bus to system bus. This data bus is oriented with bits 35:32 used for parity while bits 31:0 are used for data. Parity is not calculated or checked by any of the peripherals on the system bus, it is only carried. The MSB and LSB must be selected based on the peripheral target and application.                                                                                                                                |

| um_rdata[35:0] | 0    | 36-bit read data bus to system bus. This data bus is oriented with bits 35:32 used for parity while bits 31:0 are used for data. Parity is not calculated or checked by any of the peripherals on the system bus, it is only carried. The MSB and LSB must be selected based on the peripheral target and application.                                                                                                                                 |

| um_addr[17:0]  | I    | This 18 bit address bus is used to select the address where a user master transaction will target. Bit 17 of the um_addr bus is the MSB while bit 0 is the LSB.                                                                                                                                                                                                                                                                                        |

| um_read        | I    | Active-high read request indicates the current transaction is a read. Data will be expected to be found on the um_rdata bus.                                                                                                                                                                                                                                                                                                                           |

| um_write       | I    | Active-high write request indicates the current transaction is a write. Data will be expected to be driven onto um_wdata bus.                                                                                                                                                                                                                                                                                                                          |

| um_lock        | I    | This active-high signal will be used to request ownership of the system bus.                                                                                                                                                                                                                                                                                                                                                                           |

| um_granted     | 0    | If the system bus arbiter grants ownership to the UMI the um_granted signal will go high indicating the system bus is locked to the UMI. The um_granted signal is clocked off the HCLK, not the um_clk. This is used for debugging purposes only. The user should use um_ack as the signal to indicate the UMI is ready for transactions                                                                                                               |

| um_burst       | 1    | Indicates this operation is a burst transfer.                                                                                                                                                                                                                                                                                                                                                                                                          |

| um_size[1:0]   | I    | Data width for transfer (10-double word, 01-word, 00-byte, 11-invalid). Selects the size of the data transfer being done on the UMI. For 32-bit transactions all bits 31:0 will carry valid data. For 16-bit transactions only bits 15:0 will carry valid data. For 8-bit transactions only bits 7:0 will carry valid data. It is recommend for smaller than 32-bit transactions the remaining unused data bits are driven to 0 for a write operation. |

| um_ready       | I    | Data strobe indicates address and data ready. Should be driven high when valid address is provided for read and valid address and data is present for write.                                                                                                                                                                                                                                                                                           |

| um_ack         | 0    | Acknowledge from master interface to indicate that it is ready for another operation.                                                                                                                                                                                                                                                                                                                                                                  |

| um_retry       | 0    | Asserted for one um_clk cycle when the UMI is busy to request that the master relinquish the bus and reissue the current transfer. A retry is issued when the following occurs:  1.The UMI gets a read transaction while its write FIFOs are not empty.  2.The UMI gets a write transfer while its write FIFOs are full.  3.The UMI receives a retry indication from the embedded system bus.                                                          |

| um_err         | 0    | Bus error response is asserted for one clock cycle when um_ready is asserted. Indicates an internal system bus error.                                                                                                                                                                                                                                                                                                                                  |

| um_irq         | I    | User logic master interface interrupt request. Active-high signal to indicate an interrupt to the system bus. This signal will map to the interrupt cause register USER_MSTR bit.                                                                                                                                                                                                                                                                      |

# **Locking the UMI**

The system bus is a multi master bus and the um\_lock signal will request ownership of the bus. In a multi master system bus application the UMI must be locked to guarantee uninterrupted multiple transactions through the UMI. Ownership of the bus is granted based on the priority of the master interface. If two masters request the bus at the same time the interface with higher priority will obtain the bus. Once the UMI has locked the bus the um\_granted signal along with um\_ack will go high indicating the interface is ready for a transaction. Um\_granted is for debug only and should not be used in the user's design.

To release the lock on the system bus a um\_ready pulse must be given after um\_lock is driven low. The um\_ready pulse will allow the system bus to sample um\_lock and release the bus lock.

For a single UMI transaction um\_lock is not required.

# **UMI Single Access**

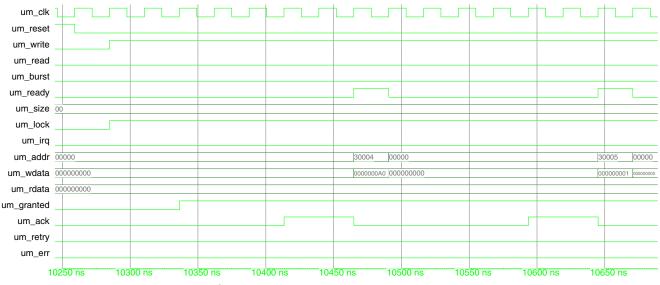

A typical operation of a single access write transactions are as follows. For this description the um\_lock signal will be used to lock the system bus and guarantee uninterrupted multiple transactions.

Figure 9. Single Access Write from USER Master Interface

Entity: Architecture: Date: Wed Mar 06 09:38:59 Central Daylight Time 2002 Row: 1 Page: 1

A single write access is initiated with the assertion of um\_lock and um\_write. This in turn requests ownership of the system bus. When granted ownership (um\_granted), the UMI returns with um\_ack. The user then asserts um\_ready with valid data and address on um\_addr and um\_wdata. Um\_ready is the gating signal for valid data and address and is to be asserted for every single access write transaction. When the write transaction is complete, um\_ack is asserted by the UMI. Um\_ack is a synchronous signal and stays asserted after the single write is completed.

Consecutive single writes may be performed with the assertion of um\_ready along with new data and address. Um\_write is to be asserted for the entire period of the transaction. System bus lock requests are not made for subsequent back-to-back write operations. Um\_ack gets deasserted on the clock cycle after um\_ready and gets asserted when the transaction is complete and ready for the next transaction.

A typical operation of a single access read transaction is as follows. Again the um\_lock signal will be used to lock the system bus.

um reset um\_write um\_read um burst um ready um\_size o um lock um\_irq um\_addr 00000 00001 um\_wdata 000000000 um rdata F3B3B3B3E um\_granted um ack um\_retry um err 10350 ns 10400 ns 10450 ns 10500 ns

Figure 10. Single Access Read from USER Master Interface

Entity: Architecture: Date: Wed Mar 06 09:36:36 Central Daylight Time 2002 Row: 1 Page: 1

A single access read is initiated with the assertion of um\_lock and um\_read. This in turn requests ownership of the system bus. When granted ownership (um\_granted), the UMI returns with um\_ack. The user then asserts um\_ready with a valid read address on um\_addr. Um\_ready is the gating signal for valid address and is to be asserted for only one um\_clk cycle for every single read transaction. When the read data is ready at the um\_rdata ports, um\_ack is asserted by the UMI. Um\_ack is a synchronous signal and stays asserted after the single read is completed. Consecutive signal reads may be performed with the assertion of um\_ready along with the new address. Um\_read is to be asserted for the entire period of the transaction. System bus lock requests are not made for subsequent back-to-back write operations. On the next um\_clk with um\_ready high, um\_ack is deasserted and is re-asserted when the transaction is complete and ready for the next transaction. Signal um\_ready should only be high for 1 um\_clk cycle.

## **UMI Burst Access**

Burst access is initiated by asserting the um\_burst signal along with um\_lock and um\_write/um\_read. The UMI handles bursts that are four beats deep. It employs a four beat deep FIFO that is 36 bits wide. It handles and generates burst writes and reads that are four deep regardless of the size of the bus chosen by um\_size. All address and data mapping is retained across the master interface.

A typical burst write operation is as follows: a burst access write is initiated with the assertion of um\_lock, um\_burst and um\_write. This in turn requests ownership of the system bus. When granted ownership (um\_granted), the UMI returns with um\_ack.

The user then asserts um\_ready with valid data address on um\_addr and um\_wdata, respectively, for four consecutive cycles. There is no address FIFO in the UMI, so the address on um\_addr qualified by the first um\_ready phase is incremented internally for the next three data words on um\_wdata. Internal incrementing of the address depends on the size specified by um\_size. When the write transaction is complete, um\_ack is asserted by the UMI. Signal um\_ack is a synchronous signal and stays asserted after the burst write is completed. Consecutive burst writes may be performed with the assertion of um\_ready along with new data and address. Signal um\_write is to be asserted for the entire period of the transaction. System bus lock requests are not made for subsequent back-to-back write operations. On the next um\_clk with um\_ready high, um\_ack is deasserted and is re-asserted when the transaction is complete and ready for the next transaction. Signal um\_ready should only be high for 1 um\_clk cycle.

A typical burst read operation is as follows: a burst access read is initiated with the assertion of um\_lock, um\_burst, and um\_read. This in turn requests ownership of the system bus. When granted ownership (um\_granted), the UMI returns with um\_ack.

The user then asserts um\_ready with valid address on um\_addr. There is no address FIFO in the user master interface, so the address on um\_addr is qualified when the um\_ready phase is incremented internally for a total of four addresses. Internal incrementing of the address depends on the size specified by um\_size. when the read transaction is complete, um\_ack is asserted by the umi. um\_ack is a synchronous signal and stays asserted for four clock cycles after the burst read is completed. in this case, the um\_ack qualifies the availability of valid data on um\_rdata. Consecutive burst reads may be performed with the assertion of um\_ready along with a new address. Signal um\_read is to be asserted for the entire period of the transaction. System bus lock requests are not made for subsequent back-to-back read operations. The valid data on um\_rdata is available on the first four clocks of um\_ack. Signal um\_ack gets deasserted only on the clock cycle after um\_ready. Signal um\_ack get asserted again when a new transaction is complete and ready for the next transaction.

# **User Slave Interface (USI)**

The user logic slave interface includes the signals listed in Table 8.

Table 8. User Logic Slave Interface Signals

| Signal         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| us_clk         | I    | User slave interface clock. This clock will only clock the USI. A domain transfer will occur from the USI to the system bus (HCLK). The user slave interface and the system bus can be made synchronous by using the same clock for the us_clk and usr_clk and selecting User as the HCLK. A frequency preference on this signal will constrain all of the inputs and outputs of the USI.                                                                                                                                                                                                       |

| us_reset       | I    | This active-high reset resets all of the controls in the user slave interface. This should be pulsed once before any transactions can occur to the USI. This is typically connected to the same reset as the GSR and pulsed at power-up.                                                                                                                                                                                                                                                                                                                                                        |

| us_wdata[35:0] | 0    | 36-bit write data from the system bus. This data bus is oriented with bits 35:32 used for parity while bits 31:0 are used for data. Parity is not calculated or checked by any of the peripherals on the system bus; it is only carried. The MSb and LSb will be based on the driving master. For 32-bit access bits (31:0) are used. For 16-bit access bits 15:0 are used. The same data on 15:0 will be present as well on 31:16 as well. For 8-bit access bits 7:0 are used and the same data will be present on d(31:24), d(23:16), and d(15:8) as well.                                    |

| us_rdata[35:0] | I    | 36-bit read data bus to system bus. This data bus is oriented with bits 35:32 used for parity while bits 31:0 are used for data. Parity is not calculated or checked by any of the peripherals on the system bus, it is only carried. The MSB and LSB must be selected based on the accepting master and application. For 32-bit access bits (31:0) are used. For smaller than 32-bit transfers the data must be replicated on all byte lanes. For 16-bit access bits 15:0 and 31:16 are used. For 8-bit access bits 7:0, 15:8, 23:16, and 31:24 are used with the same read data on all bytes. |

| us_addr[17:0]  | 0    | This 18 bit address bus is provides the address where a slave transaction will operate. Bit 17 of the um_addr bus is the MSB while bit 0 is the LSB. The user only needs to decode the address bits that make up the application. Since the USI always resides at address offset 0x8000, bit 15 will always be 1 during a USI access.                                                                                                                                                                                                                                                           |

| us_wr          | 0    | Indicates whether the current transaction is a read or a write. 1 indicates a write transaction and the us_wdata should be captured. 0 indicates a read transaction and data should be placed on us_rdata.                                                                                                                                                                                                                                                                                                                                                                                      |

| us_size[1:0]   | 0    | Transfer size (10-double word, 10-word, 00-byte, 11-invalid). Indicates the size of the current transaction. For a 32-bit transaction all of the data bits 31:0 will be valid. For 16-bit transaction only bits 15:0 will be valid. For 8-bit data only bits 7:0 will be valid. For smaller than 32-bit transactions the remaining unused data bits should driven to 0 for a read operation.                                                                                                                                                                                                    |

| us_burst       | 0    | Transfer is a burst (high) or single beat (low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| us_err         | I    | Active-high error response from the user to the USI when data size is not consistent with us_size, or the address on the us_addr is out of range for the application.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| us_ack         | I    | Active-high acknowledge for read operations. User drives us_ack high to terminate the transaction. Signal us_ack is passed through the system bus to eventually terminate the transaction from the driving master.                                                                                                                                                                                                                                                                                                                                                                              |

## Table 8. User Logic Slave Interface Signals (Continued)

| Signal   | Type | Description                                                                                                                                                 |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| us_rdy   | 0    | Active-high ready response from the USI for either read or write transactions. Signal us_rdy goes high when an address is ready on us_addr.                 |

| us_retry | I    | Signal available for the user to drive when a transaction is not ready to be processed. This retry signal is then sent to the originating master interface. |

| us_irq   | I    | Active-high interrupt pin to indicate an interrupt to the system bus. This signal will map to the interrupt cause register USER_SLAVE bit (0x00010 bit 6).  |

#### **User Slave Transfer Errors**

The user logic slave interface responds with a transfer error to the system bus under the following circumstances. This is an internally generated error from the USI and is separate from the us\_err signal. The resulting error to the master interface will be either a mpi\_retry or um\_retry for the MPI and UMI. For the FPSC this will be specific to the FPSC master interface and will be covered in the FPSC data sheet.

- 1. us\_reset is high during the transaction

- 2. us\_err is high during the transaction

- 3. The device is in bitstream configuration.

- 4. The address does not conform to the us\_size specified. The setting for us\_size will dictate the granularity of the address available from the USI. If us\_size is selected for 8-bit mode, then all address can be selected. If us\_size is selected for 16-bit (word) mode, then only addresses on word boundaries can be selected.

For example address 0x0, 0x2, 0x4, etc. are valid addresses. 0x1, 0x3, 0x5, etc. are not valid addresses for word accesses. The same holds true for 32-bit (double word) mode; 0x0, 0x4, 0x8, etc. are valid while 0x1, 0x2, 0x3, 0x5, 0x6, 0x7, 0x9, etc. are not valid.

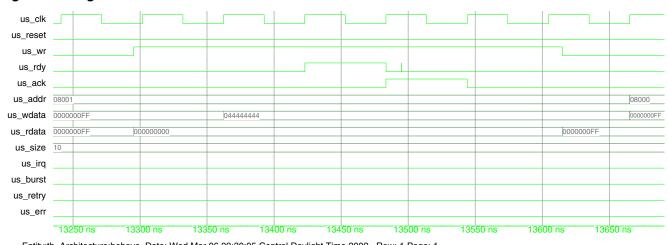

## **USI Single Access**

A typical operation of a single access write transaction is as follows. The us\_wr signal goes high to indicate that a write is taking place. The synchronous signal us\_rdy signal indicates the availability of valid address and data on the us\_addr and us\_wdata ports, respectively. The USI inserts additional wait states until the us\_ack signal is asserted by the user. For write operations, if the data received by the slave interface can be accepted by the user slave in one cycle, it is acceptable to leave us\_ack asserted continuously during us\_wr (write operation). If the USI takes more than one us\_clk cycle to terminate the transaction then us\_ack should be driven high when the transaction is complete.

um reset um write um\_read um burst um ready um size 0 um\_lock um\_irq um\_addr 00000 00000 30004 30005 um\_wdata 000000000 um rdata um\_granted um\_ack um\_retry um err 10350 ns 104<mark>00 ns</mark> 10550 ns 106<mark>00 ns</mark> 106<mark>50 ns</mark>

Figure 11. Single Access Write at USER Slave Interface

Entity: Architecture: Date: Wed Mar 06 09:38:59 Central Daylight Time 2002 Row: 1 Page: 1

A typical operation of a single access read transaction is as follows. the us\_wr signal is low to indicate that a read is taking place. The synchronous us\_rdy signal indicates the availability of valid address on the us\_addr. The user must then respond with read data on the us\_rdata bus and assert us\_ack. The USI inserts additional wait states until the us\_ack signal is asserted by the user.

Figure 12. Single Access Read at USI

Entity:tb Architecture:behave Date: Wed Mar 06 09:30:05 Central Daylight Time 2002 Row: 1 Page: 1

#### **USI Burst Access**

A burst access to the USI is indicated by the us\_burst signal. However, burst accesses are treated similar to single accesses. There is no FIFO in the USI and thus all burst accesses are handled as back-to-back signal accesses with wait states. It is possible for the slave to handle bursts of user design defined lengths. During a burst access the us\_addr bus will increment on each us\_clk during the burst transfer.

#### **FPSC Master/Slave Interface**

The FPSC system bus interface can be either a master or a slave interface. The details and protocol of the FPSC interface are specific to the FPSC being used. The connections from the system bus to the FPSC block are main-

tained by the FPSC software and are fixed in the actual device. Therefore this interface is not covered in this document. The FPSC template from the FPSC Configuration Wizard makes all of the HDL connections for the user.

The FPSC memory map resides at address offset 0x30000. When referencing the FPSC data sheet, all addresses begin at base address 0x30000.

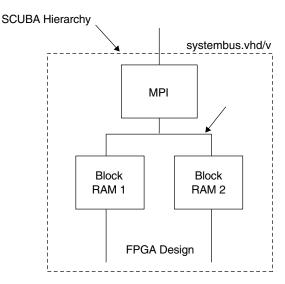

## System Bus Embedded Block RAMs

Embedded block RAMs (EBR) in an ORCA Series 4 device are quad-port 512-bit x 18-bit static random access memories (SRAM). The embedded memory blocks may be configured in either quad port (two user write ports and two user read ports), or system bus mode (one pair of read/write ports available to FPGA logic, one pair of read/write ports dedicated to embedded system bus access). Prior to device configuration, all of the embedded memory blocks operate in system bus mode to facilitate bitstream or microprocessor initialization of the memory contents. After configuration, embedded memory blocks are not accessible from the system bus unless the user specifically includes the system bus element and associated block memories in system bus mode in their FPGA design.

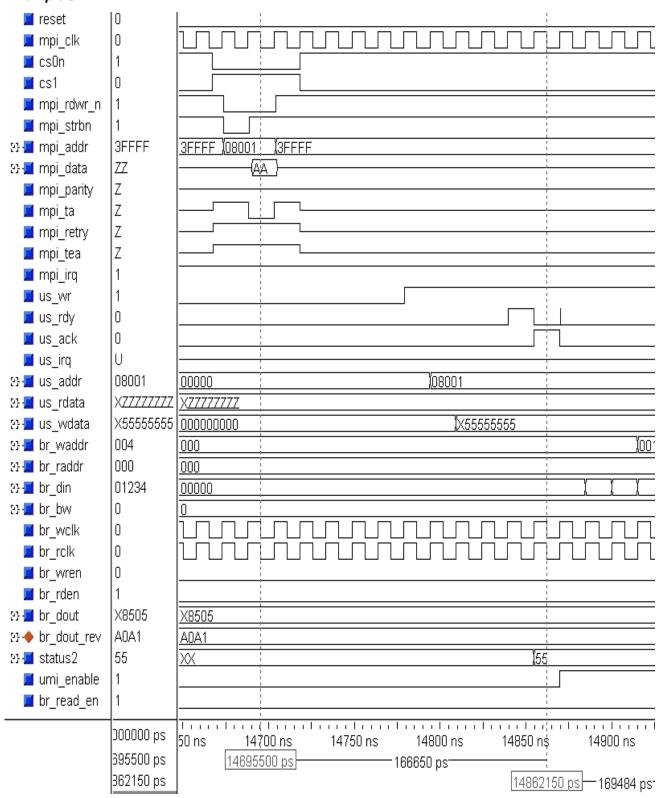

If an EBR is used on the system bus the EBR cannot be used in any other mode (FIFO, CAM, or Multiplier) in the FPGA design. Figure 13 shows how system bus EBRs are connected to the system bus and represented in SCUBA. One of the read/write ports of the quad port EBR is connected to the system bus and the other is available for the FPGA design. The read/write ports for the user will be found on the system bus element when creating the system bus and EBR using SCUBA. EBR memories that do not require a connection to the system bus are created separately from the system bus and have no connection in the HDL to the system bus.

Figure 13. SCUBA HDL for System Bus EBRs

# **EBR Memory Mapping**

The embedded system bus provides two memory spaces for accessing the contents of the embedded memory blocks. The first (0x10000 to 0x17FFF) provides access to embedded memory blocks along the top edge of the device. The second (0x20000 to 0x27FFF) provides access to embedded memory blocks along the bottom edge of the device. Adjacent memory blocks are paired to form a single 512-bit x 32-bit data structure that is accessed via the embedded system bus. Table 9 illustrates the address mapping of the first double word of each embedded memory block as well as device location, availability and SCUBA location designator.

Table 9. Memory Block Address Mapping

| Address         | Bits    | RAM Block      | Device Location | SCUBA Location<br>Name | Device      |

|-----------------|---------|----------------|-----------------|------------------------|-------------|

| 0x10001:0x10000 | [0:15]  | BLOCK0 [0:15]  | Top Left        | 1024_0                 | 4e2,4e4,4e6 |

| 0x10003:0x10002 | [16:31] | BLOCK1 [0:15]  | Тор             | 1024_0                 | 4e2,4e4,4e6 |

| 0x10801:0x10800 | [0:15]  | BLOCK2 [0:15]  | Тор             | 1024_1                 | 4e2,4e4,4e6 |

| 0x10803:0x10802 | [16:31] | BLOCK3 [0:15]  | Тор             | 1024_1                 | 4e2,4e4,4e6 |

| 0x11001:0x11000 | [0:15]  | BLOCK4 [0:15]  | Тор             | 1024_2                 | 4e4,4e6     |

| 0x11003:0x11002 | [16:31] | BLOCK5 [0:15]  | Тор             | 1024_2                 | 4e4,4e6     |

| 0x11801:0x11800 | [0:15]  | BLOCK6 [0:15]  | Тор             | 1024_3                 | 4e6         |

| 0x11803:0x11802 | [16:31] | BLOCK7 [0:15]  | Top Right       | 1024_3                 | 4e6         |

| 0x20001:0x20000 | [0:15]  | BLOCK32 [0:15] | Bottom Left     | 1024_16                | 4e2,4e4,4e6 |

| 0x20003:0x20002 | [16:31] | BLOCK33 [0:15] | Bottom          | 1024_16                | 4e2,4e4,4e6 |

| 0x20801:0x20800 | [0:15]  | BLOCK34 [0:15] | Bottom          | 1024_17                | 4e2,4e4,4e6 |

| 0x20803:0x20802 | [16:31] | BLOCK35 [0:15] | Bottom          | 1024_17                | 4e2,4e4,4e6 |

| 0x21001:0x21000 | [0:15]  | BLOCK36 [0:15] | Bottom          | 1024_18                | 4e4,4e6     |

| 0x21003:0x21002 | [16:31] | BLOCK37 [0:15] | Bottom          | 1024_18                | 4e4,4e6     |

| 0x21801:0x21800 | [0:15]  | BLOCK38 [0:15] | Bottom          | 1024_19                | 4e6         |

| 0x21803:0x21802 | [16:31] | BLOCK39 [0:15] | Bottom Right    | 1024_19                | 4e6         |

If enabled, parity for each byte is provided via the data bus parity bits. Parity is stored in the most significant bit of the byte mapped 32k addresses above the related data byte. This space is reserved in the memory map shown in Table 9. If parity is enabled, the parity bits are recombined with the data to form 36-bit data on the embedded system bus, and 18-bit data on the user ports of the embedded memory block.

## **EBR User Ports**

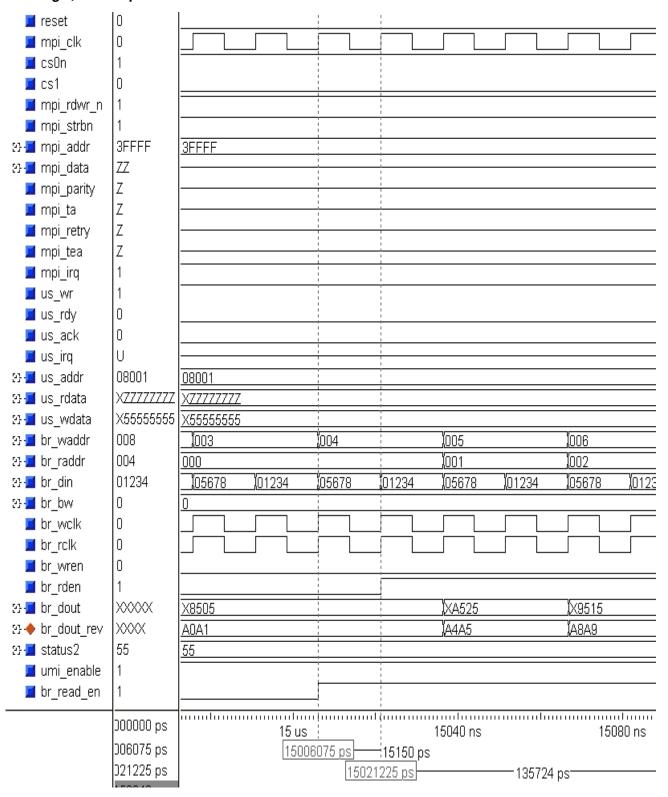

When using an EBR in the system bus one read/write port is connected to the system bus while the other port is available to the user FPGA design. Table 10 shows the user ports and their description. These ports will exist on the system bus element if a system bus block RAM is utilized.

Table 10. Block RAM User Logic Interface Signals

| Signal     | Туре | Description                                                                                                                                                                                                      |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Waddr[N:0] | Į    | Write port address (N: 8 = 512, 9 = 1024).                                                                                                                                                                       |

| Din[17:0]  | I    | Write port data. Parity is carried on 17:16, data on 15:0. Parity is mapped that bit 17 is used for 15:8 and bit 16 is used for 7:0.                                                                             |

| BW[1:0]    | I    | Active-high, byte lane write enables. 00 - Both byte lanes are disabled 01 - Byte lane with bits 16,7:0 is enabled 10 - Byte lane with bits 17,15:8 is enabled 11 - Both byte lanes are enabled for 18-bit write |

| WREN       | ı    | Active-high, write enable.                                                                                                                                                                                       |

| WCLK       | I    | Write port clock input.                                                                                                                                                                                          |

| RADDR[N:0] | I    | Read port address (N: 8 = 512, 9 = 1024).                                                                                                                                                                        |

| RDEN       | I    | Active-high, read enable.                                                                                                                                                                                        |

| RCLK       | Į    | Read port clock input.                                                                                                                                                                                           |

| DOUT[17:0] | 0    | Read port data. Parity is carried on 17:16, data on 15:0. Parity is mapped that bit 17 is used for 15:8 and bit 16 is used for 7:0.                                                                              |

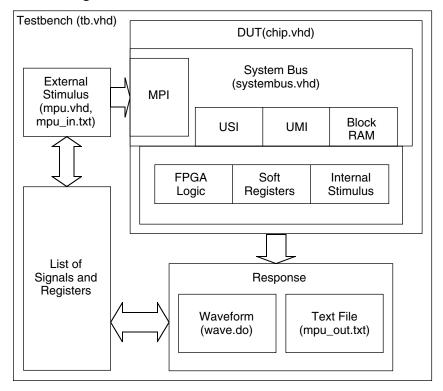

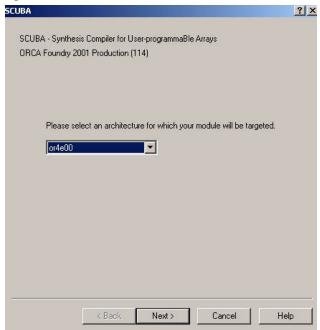

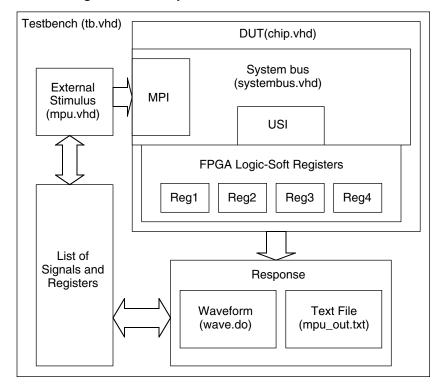

# Creating the System Bus in HDL

The system bus is a very large element that is contained in the ORCA Foundry VHDL and Verilog libraries for Series 4 ORCA devices. In order to facilitate the use of this large block, SCUBA is used to create a custom system bus for a user's FPGA design and application. The SCUBA Wizard will guide the user through the different interfaces of the system bus and allow them to tailor the system bus for the specific application. SCUBA will create an HDL file output that includes a module with only the system bus peripheral interfaces specified in SCUBA. This new module instantiates the library element for the system bus and disables all of the unused interfaces.

SCUBA is used to create the system bus and all connected EBRs. System Bus EBRs are accessed as 512-bit x 36-bit on the system bus. Designers have the choice of accessing the EBR as a single 1024-bit x 18-bit or two 512-bit x 18-bit interfaces. A checkbox for arbiter mode is available in SCUBA to use the arbiter to perform arbitration between two EBRs. SCUBA also allows the designer to choose whether to use EBR input and output registers. These registers pipeline the address and/or data across the FPGA boundary in and out of the EBR. A memory file is also available to initialize the EBR to any value. This memory file is used to initialize the EBR to values other than 0x0. Be default the EBR will be initialized to 0x0 at power-up. However, when utilizing the EBR memories using the MPI to perform bitstream configuration, the MPI will be required to initialize the EBR.

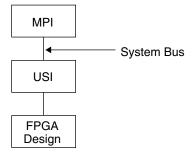

# **Applications of the System Bus**

# **MPI** and User Slave

A common application using the system bus involves the use of the MPI and user slave interface to create soft control and status registers inside of the FPGA design. Using the system bus with a MPI and a user slave interface can be accomplished with an 8, 16, and 32-bit data bus and using up to all 18 bits of address in the FPGA design. As an example application we will use an 8-bit data bus using two address bits to create four registers in the FPGA. Two registers will be used as R/W control registers and two registers will be used as read only status registers. We will also use an interrupt generated from the FPGA design to signal the processor via the MPI. Figure 14 shows a block level diagram of the FPGA design.

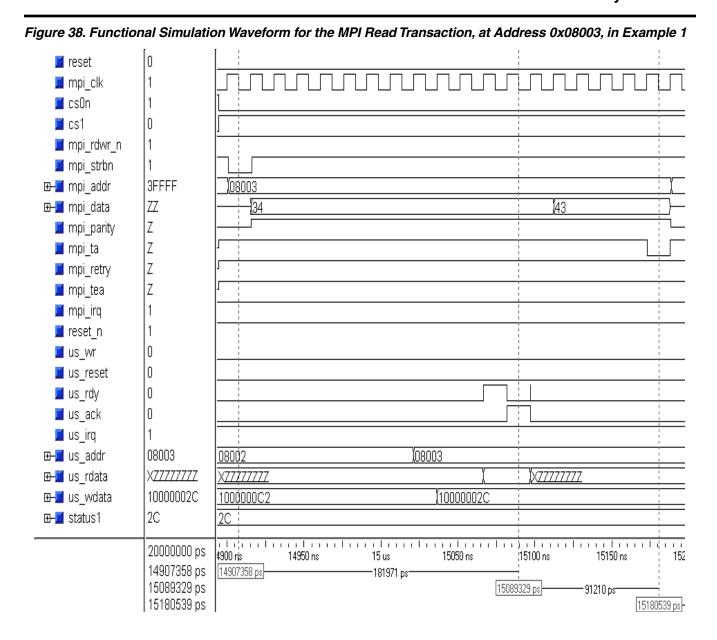

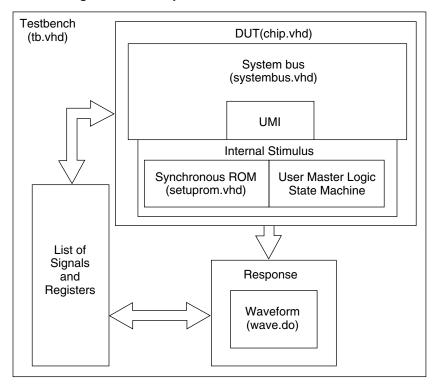

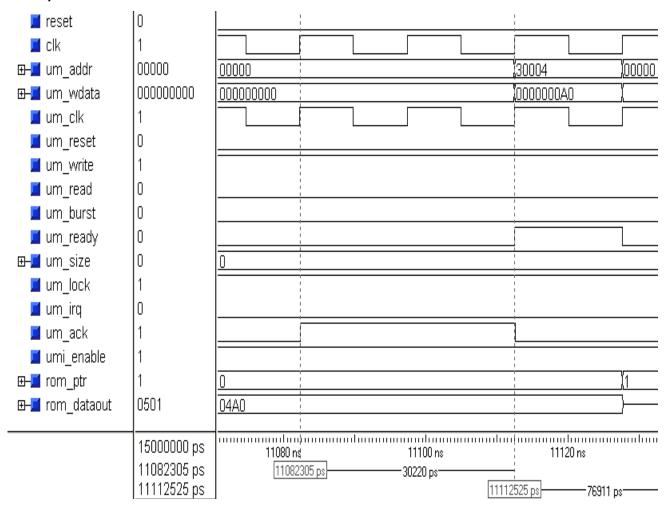

Figure 14. MPI and User Slave Application Diagram