# OTC-045

# 35-BIT LED DISPLAY DRIVER

DATE: December 5, 2001

#### FEATURES

- CMOS technology

- Continuous brightness control

- Serial data input

- No load signal required

- Optional external data enable and reset

- Wide power supply operation (3.5V to 12V)

- TTL compatibility

- 34 or 35 outputs, 20mA sink capability

- Alphanumeric capability

#### APPLICATIONS

- Products with alphanumeric LED displays such as digital clock, counter, radio, multimeter, etc.

- Industrial control indicator or instrumentation readout

- Relay driver

#### ORDERING INFORMATION

| PART NO. | PACKAGE     | NOTE      |  |  |

|----------|-------------|-----------|--|--|

| OTC-045  | -           | CHIP FORM |  |  |

| OTC-045Q | 44-PIN LQFP | -         |  |  |

#### ABSOLUTE MAXIMUM RATINGS

| Ta=+25°C, UNLESS OTHERWISE SPECIFIED |        |                |                        |  |  |  |  |

|--------------------------------------|--------|----------------|------------------------|--|--|--|--|

| CHARACTERISTICS                      | SYMBOL | RATING         | UNIT                   |  |  |  |  |

| Supply Voltage                       | VDD    | +3.5 ~ +12     | V                      |  |  |  |  |

| Clock Frequency                      | Fclk   | 4M             | Hz                     |  |  |  |  |

| Input Voltage                        | VIN    | -0.3 ~ VDD+0.3 | V                      |  |  |  |  |

| Input B.C. Current                   | IBC    | 700            | μΑ                     |  |  |  |  |

| Output Sustaining Voltage            | Vds    | 10             | V                      |  |  |  |  |

| Output Continuous Current            | Iout   | 25             | mA                     |  |  |  |  |

| Power Dissipation Per Output         | Pdiss  | 25             | mW                     |  |  |  |  |

| Operating Temperature                | Topr   | -40 ~ +85      | $^{\circ}\!\mathbb{C}$ |  |  |  |  |

| Storage Temperature                  | Tstr   | -60 ~ +150     | $^{\circ}\!\mathbb{C}$ |  |  |  |  |

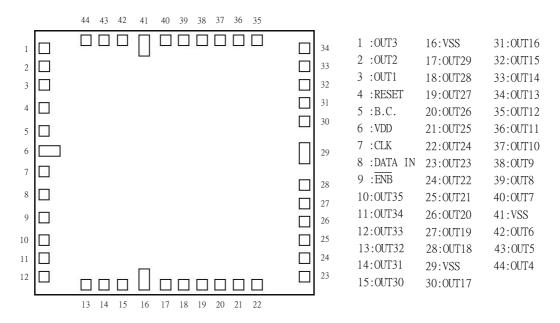

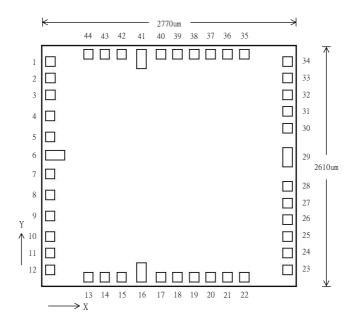

#### PAD/PIN ASSIGNMENT (TOP VIEW)

— Pad Assignment (Chip Form)

Die Size:  $2770 \text{um} \times 2610 \text{um} (W \times H)$

# — Pin Assignment (LQFP)

# ■ PAD/PIN DESCRIPTIONS

| PIN NO.     | PAD/PIN NAME | TYPE   | DESCRIPTION                                 |

|-------------|--------------|--------|---------------------------------------------|

| 6           | VDD          | Power  | Power                                       |

| 16,29,41    | VSS          | Ground | Ground                                      |

| 4           | RESET        | Input  | Reset signal input, (Normally grounded)     |

| 5           | B.C.         | Input  | DC current input for LED brightness control |

| 7           | CLK          | Input  | Clock input                                 |

| 8           | DATA IN      | Input  | Serial data input                           |

| 9           | ENB          | Input  | Data input enable, (Normally grounded)      |

| 1,2,3;10~15 | OUT1~OUT35   | Output | Open-drain NMOS output drivers              |

| 17~28;30~40 |              |        |                                             |

| 42,43,44    |              |        |                                             |

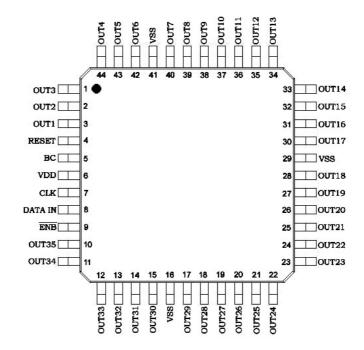

#### FUNCTION DESCRIPTIONS

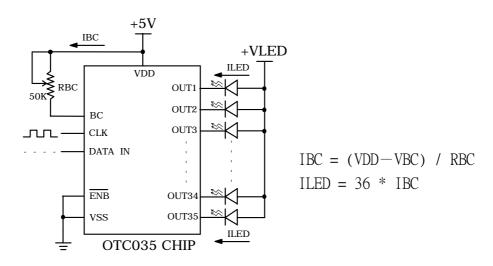

The OTC-045 is designed to drive either 4 or 5-digit, common anode alphanumeric LED displays with the added benefit of requiring minimal interface with the display or data source.

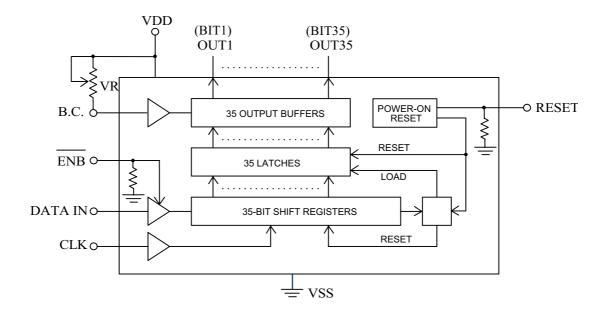

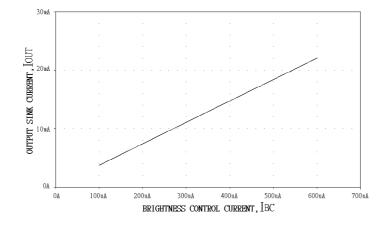

Data is transferred serially via 2 signals: clock and serial data. Data transfer without the added inconvenience of an external load signal is accomplished by using a format of a leading "1" followed by the allowed 35 data bits. These 35 data bits are latched after the 36th clock has been transferred. This scheme provides non-multiplexed, direct drive to the LED display. Characters currently displayed (thus, data output) changes only if the serial data bits differ from those previously transferred. Display brightness is determined by control of the output current for LED displays. This control function can be achieved by varying the current flowing into B.C. terminal. A simple way is to set an external variable resistor illustrated in the block diagram. Typically, the output current is 36 times greater that current into B.C. terminal.

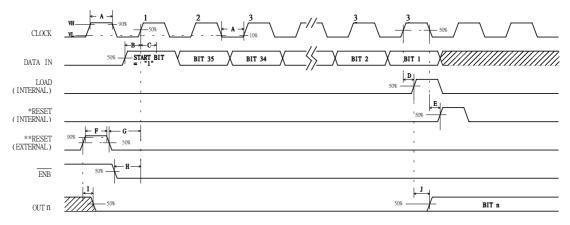

Figure 1 shows the input data format. A leading "1" is followed by 35 bits of data. After the 36th had been transferred, a load signal is generated synchronously with the clock high state. This loads the 35 bits of data into the latches. A reset signal is generated consecutively with the clock low, which clears all shift registers for the next set of data. All shift registers are static master-slave, with no clear for the master portion of the first register, allowing continuous operation. There must be a complete 36 clocks or the shift registers will not clear.

When the chip first powers on an transient high state of internal power on reset signal is generated which clears all shift registers and latches. The start bit and the first clock return the chip to its normal operation. The 'RESET' input terminal is also available for an option to clear all shift registers and latches by an external pulse.

### TYPICAL APPLICATION CIRCUIT

### RECOMMENDED OPERATING CONDITIONS

| VDD=+5V, Ta=+25℃, UNLESS OTHERWISE SPECIFIED |        |     |      |     |         |  |  |  |  |

|----------------------------------------------|--------|-----|------|-----|---------|--|--|--|--|

| CHARACTERISTICS                              | SYMBOL | MIN | TYP  | MAX | UNIT    |  |  |  |  |

| Supply Voltage                               | VDD    | 4.5 | 5    | 9   | V       |  |  |  |  |

| Clock Frequency                              | FCLK   | -   | 500K | 2M  | Hz      |  |  |  |  |

| Input B.C. Current                           | IBC    | 0   | -    | 550 | $\mu$ A |  |  |  |  |

| Output Sustaining Voltage                    | VDS    | -   | -    | 9   | V       |  |  |  |  |

| Output Continuous Current                    | IOUT   | -   | -    | 20  | mA      |  |  |  |  |

| Power Dissipation Per Output                 | PDISS  | -   | -    | 20  | mW      |  |  |  |  |

# DC ELECTRICAL CHARACTERISTICS

| VDD=+5V, Ta=+25℃, UNLESS OTHERWISE SPECIFIED |                           |         |      |         |         |  |  |  |

|----------------------------------------------|---------------------------|---------|------|---------|---------|--|--|--|

| PARAMETER                                    | CONDITIONS                | MIN     | TYP  | MAX     | UNIT    |  |  |  |

| Power Supply,VDD                             |                           | 3.5     | -    | 12      | V       |  |  |  |

| Power Supply Current                         | VDD=5V, Excluding output  | -       | -    | 5       | mA      |  |  |  |

| Logic Input Voltages,VIH                     | VDD=5V                    | 0.8VDD  | VDD  | VDD+0.3 | V       |  |  |  |

| VIL                                          | VDD=5V                    | VSS-0.3 | VSS  | 0.2VDD  | V       |  |  |  |

| Brightness Input,IBC                         |                           | 0       | -    | 550     | $\mu$ A |  |  |  |

| Brightness Input Voltage                     | Input Current, IBC=550 μA | 3.0     | 3.2  | 4.0     | V       |  |  |  |

| Output Current, IouT(OFF)                    | VOUT=3.0V                 | -       | -    | <0.5    | $\mu$ A |  |  |  |

| Output Current, Iout(ON)                     | VOUT=1.0V                 | 0       | -    | 22      | mA      |  |  |  |

|                                              | Brightness Input=0μA      | 0       | -    | <0.5    | $\mu$ A |  |  |  |

|                                              | Brightness Input=100μA    | 3.5     | 3.6  | 3.7     | mA      |  |  |  |

|                                              | Brightness Input=550μA    | 20      | 21   | 22      | mA      |  |  |  |

| Output Matching                              |                           | -       | -    | 5       | %       |  |  |  |

| Clock Input Frequency, Fak                   |                           | -       | 500K | 2M      | Hz      |  |  |  |

NOTE 1: Output matching is calculated as the percent variation of each IOUT(ON)

to IOUT(AVG), where

$$IOUT(AVG) = \{\sum_{n=1}^{35} IOUT(ON)[BITn]\} \div 35$$

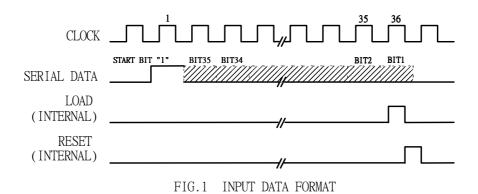

### TIMING CHART AND TIMING CONDITIONS

# — TIMING CHART

- \* THE INTERNAL RESET ONLY CLEARS ALL INTERNAL SHIFT REGISTERS.

- \*\* THE EXTERNAL RESET CLEARS ALL INTERNAL SHIFT REGISTERS AND LATCHES.

### — TIMING CONDITIONS

| ITEM | DESCRIPTION                                   | MIN | TYP | MAX | UNIT |

|------|-----------------------------------------------|-----|-----|-----|------|

| A    | Clock pulse width                             | 250 | -   | -   | nS   |

| В    | Serial data setup time                        | 30  | -   | -   | nS   |

| С    | Serial data hold time                         | 30  | -   | -   | nS   |

| D    | Time between clock activation & internal load | 35  | -   | -   | nS   |

|      | pulse activation                              |     |     |     |      |

| Е    | Time between clock falling & internal reset   | 35  | -   | -   | nS   |

|      | pulse activation                              |     |     |     |      |

| F    | External reset pulse duration                 | 25  | ı   | -   | nS   |

| G    | External reset inactive setup time            | 120 | -   | -   | nS   |

| Н    | Data enable setup time                        | 70  | -   | -   | nS   |

| I    | Time between external reset activation & the  | 25  | -   | -   | nS   |

|      | output off                                    |     |     |     |      |

| J    | Time between internal load activation & new   | 30  | -   | -   | nS   |

|      | output states arising                         |     |     |     |      |

# TRUTH TABLE

| EXTERNAL |        |                      | SERIAL   | SHIFT   | REGISTER CON | TENTS | INTERNAL | INTERNAL | LATCH CONTENTS          |

|----------|--------|----------------------|----------|---------|--------------|-------|----------|----------|-------------------------|

| RESET    | ENB    | CLK                  | DATA IN  | I35 I34 | I33 • • • I2 | I1 I0 | LOAD     | RESET    | I35 I34 I33 · · · I2 I1 |

|          |        | _                    | Н        | H R35   | R34 · · · R3 | R2 L  | L        | L        | NO CHANGE               |

|          |        | 4                    | L        | L R35   | R34 · · · R3 | R2 L  | L        | L        | NO CHANGE               |

| L or F   | L or F | الم                  | X        | R35 R34 | R33 • • • R2 | Rı L  | L        | L        | NO CHANGE               |

|          |        |                      | (1)<br>X | P35 P34 | P33 · · · P2 | Pı H  | Н        | L        | P35 P34 P33 • • • P2 P1 |

|          |        | (1) (3)<br>11<br>(2) | (2)<br>X | L L     | L L          | L L   | L        | Н        | P35 P34 P33 • • • P2 P1 |

|          |        |                      | (3)<br>H | H L     | L L          | L L   | L        | L        | P35 P34 P33 · · · P2 P1 |

|          |        |                      | (3)<br>L | L L     | L L          | L L   | L        | L        | P35 P34 P33 · · · P2 P1 |

|          |        |                      | X        | L R35   | R34 • • • R3 | R2 L  | L        | L        | NO CHANGE               |

|          |        | ٦                    | X        | R35 R34 | R33 • • • R3 | R2 L  | L        | L        | NO CHANGE               |

| L or F   | Н      |                      | (1)<br>X | P35 P34 | P33 · · · P2 | Pı H  | Н        | L        | P35 P34 P33 • • • P2 P1 |

|          |        | (1) (3)              | (2)<br>X | L L     | L L          | L L   | L        | Н        | P35 P34 P33 • • • P2 P1 |

|          |        |                      | (3)<br>X | L L     | L L          | L L   | L        | L        | P35 P34 P33 • • • P2 P1 |

| Н        | X      | X                    | X        | L L     | L L          | L L   | L        | L        | L L L · · · · L L       |

H = HIGH LOGIC LEVEL

R = PREVIOUS STATE

X = IRRELEVANT

L = LOW LOGIC LEVEL

P = PRESENT STATE

F = FLOATING

# ■ TYPICAL CHARACTERISTIC CURVES (VDD=5V, VOUT=1V)

# PAD LOCATIONS AND PAD SIZE

|         | COORDINATE | S REFERENCE | E TO CENTER | OF PAD AND F | PAD SIZE / | ORIGION ( | ),0) AT CENT | TER OF PAD# | 12           |

|---------|------------|-------------|-------------|--------------|------------|-----------|--------------|-------------|--------------|

| Pad No. | Name       | X           | Y           | Pad Size     | Pad No.    | Name      | X            | Y           | Pad Size     |

| 1       | OUT3       | 0           | +2184       |              | 23         | OUT23     | +2495        | 0           |              |

| 2       | OUT2       | 0           | +2009       |              | 24         | OUT22     | +2495        | +175        |              |

| 3       | OUT1       | 0           | +1834       | 100X BY 100Y | 25         | OUT21     | +2495        | +350        |              |

| 4       | RESET      | 0           | +1616       |              | 26         | OUT20     | +2495        | +526        | 100X BY 100Y |

| 5       | B.C.       | 0           | +1396       |              | 27         | OUT19     | +2495        | +702        |              |

| 6       | VDD        | +50         | +1202       | 200X BY 100Y | 28         | OUT18     | +2495        | +876        |              |

| 7       | CLK        | 0           | +1004       |              | 29         | VSS       | +2495        | +1180       | 100X BY 200Y |

| 8       | DATA IN    | 0           | +784        |              | 30         | OUT17     | +2495        | +1485       |              |

| 9       | ENB        | 0           | +564        |              | 31         | OUT16     | +2495        | +1660       |              |

| 10      | OUT35      | 0           | +350        |              | 32         | OUT15     | +2495        | +1834       |              |

| 11      | OUT34      | 0           | +175        | 100X BY 100Y | 33         | OUT14     | +2495        | +2010       |              |

| 12      | OUT33      | 0           | 0           |              | 34         | OUT13     | +2495        | +2185       |              |

| 13      | OUT32      | +400        | -76         |              | 35         | OUT12     | +2040        | +2260       | 100X BY 100Y |

| 14      | OUT31      | +576        | -76         |              | 36         | OUT11     | +1865        | +2260       |              |

| 15      | OUT30      | +751        | -76         |              | 37         | OUT10     | +1690        | +2260       |              |

| 16      | VSS        | +957        | -26         | 100X BY 200Y | 38         | OUT9      | +1514        | +2260       |              |

| 17      | OUT29      | +1164       | -76         |              | 39         | OUT8      | +1340        | +2260       |              |

| 18      | OUT28      | +1340       | -76         |              | 40         | OUT7      | +1164        | +2260       |              |

| 19      | OUT27      | +1515       | -76         | 100X BY 100Y | 41         | VSS       | +957         | +2210       | 100X BY 200Y |

| 20      | OUT26      | +1690       | -76         | 100% DI 1001 | 42         | OUT6      | +750         | +2260       |              |

| 21      | OUT25      | +1865       | -76         |              | 43         | OUT5      | +576         | +2260       | 100X BY 100Y |

| 22      | OUT24      | +2040       | -76         |              | 44         | OUT4      | +400         | +2260       |              |

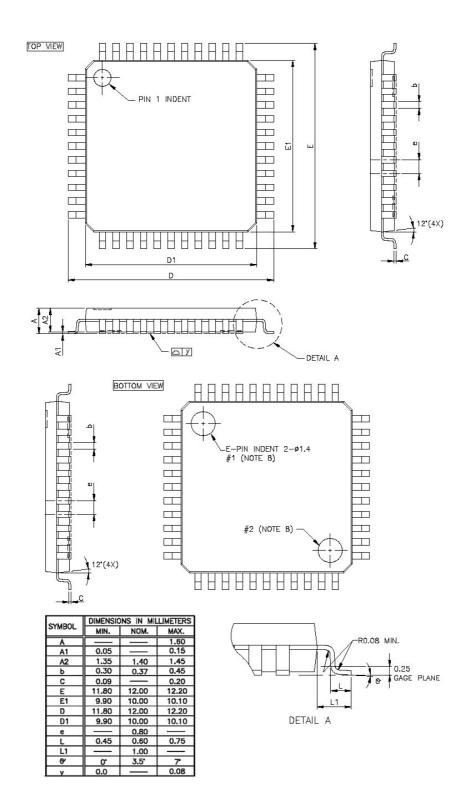

# PACKAGE INFORMATION

# OPTO TECH CORPORATION

NO.8 INNOVATION ROAD 1, HSINCHU SCIENCE-BASED INDUSTRIAL PARK, HSINCHU 30077, TAIWAN, R. O. C.