# **OX16PCI954**

Integrated Quad UART with PCI interface.

# **APPLICATION NOTES**

This application note presents guidelines for hardware implementation and configuration of the Oxford Semiconductor OX16PCI954 Quad UART with PCI interface in various PC add-in card configurations.

**Version 1.2 (11 January 2000)**

# **CONTENTS**

| 1  | INTRODUCTION                                    | 4  |

|----|-------------------------------------------------|----|

| 2  | DEVICE OVERVIEW                                 | 5  |

|    |                                                 |    |

| 3  | CONFIGURATION AND OPERATION                     |    |

| _  | .1 Mode selection                               |    |

|    | .2 ACCESSING LOGICAL FUNCTIONS                  |    |

| 3. | PCI INTERRUPTS                                  | 9  |

| ļ  | INTERFACING THE OX16PCI954                      | 10 |

| 4. | .1 Pin descriptions                             | 10 |

|    | 4.1.1 Power supply pins                         |    |

|    | 4.1.2 PCI pins                                  |    |

|    | 4.1.3 Serial port pins                          | 11 |

|    | 4.1.4 Local Bus Pins                            |    |

|    | 4.1.5 Parallel port pins                        | 12 |

|    | 4.1.6 Subsystem ID and Subsystem Vendor ID pins |    |

|    | 4.1.7 Multi-purpose Input and output pins       |    |

|    | 4.1.8 Serial EEPROM pins                        |    |

|    | 4.1.9 Miscellaneous pins                        |    |

| 4. | 2 Standard Connectivity                         |    |

|    | 4.2.1 Common connectivity example               |    |

|    | 4.2.2 Serial port interfacing                   |    |

|    | 4.2.3 Local bus examples                        |    |

|    | 4.2.4 Local bus addressing                      |    |

| 4. | 3 UART CLOCK OPTIONS                            |    |

|    | 4.3.1 TTL Clock Module                          |    |

|    | 4.3.2 Crystal Oscillator Circuit                |    |

|    | 4.3.3 Suggested Clock Frequencies               |    |

|    | 4.3.4 High speed operation                      |    |

|    | 4.3.5 Isochronous Clock Mode                    |    |

| -  | .4 MULTI-PURPOSE INPUT / OUTPUT PINS (MIO)      |    |

| 4. | .5 EXTERNAL CONNECTIONS                         |    |

|    | 4.5.1 Serial ports                              |    |

|    | 4.5.2 RS-232 Loopback Connector                 |    |

| 1  | 4.5.3 PC Parallel Port Connections              |    |

| 4. | .6 POWER MANAGEMENT                             |    |

|    | TYPICAL APPLICATIONS                            | 26 |

| 5. | .1 Low cost four-port serial card.              | 26 |

|    | 5.1.1 Interfacing                               | 26 |

|    | 5.1.2 Operation                                 | 27 |

| 5. | COMBO FOUR-PORT SERIAL, ONE-PORT PARALLEL CARD  |    |

|    | 5.2.1 Interfacing                               |    |

|    | 5.2.2 Operation                                 |    |

| 5. | 8-PORT SERIAL CARD                              |    |

|    | 5.3.1 Operation                                 |    |

| 5. | .4 12,16,20-port cards                          |    |

|    | 5.4.1 Operation                                 | 33 |

|    | PCB LAYOUT TESTING                              | 34 |

|    |                                                 |    |

|    | PROGRAMMING THE OX16C95X UART FAMILY            | 35 |

| 7.1 Ft | UNDAMENTAL I/O OPERATIONS                           | 35 |

|--------|-----------------------------------------------------|----|

| 7.1.1  | Standard Register Access                            | 36 |

| 7.1.2  | 650 Compatible Register Access                      |    |

| 7.1.3  | 950 Specific Register Access                        |    |

| 7.1.4  | 950 Indexed Control Register Set Access             |    |

| 7.2 Gi | ETTING STARTED                                      |    |

| 7.2.1  | Identifying the OX16C950 UART                       |    |

| 7.2.2  | Mode Selection                                      |    |

| 7.2.3  | Basic Operation & Configuration                     |    |

| 7.2.4  | Modem Control and Status                            |    |

| 7.2.5  | Interrupts                                          | 52 |

| 7.2.6  | Standard FIFO Trigger Levels                        |    |

| 7.3 U  | SING ENHANCED FEATURES                              |    |

| 7.3.1  | Flexible Baud Rate Generation (Using TCR and CPR)   |    |

| 7.3.2  | Using 950 Trigger Levels                            |    |

| 7.3.3  | Enabling and Disabling the Transmitter and Receiver |    |

| 7.3.4  | Using Automated Out-of-band Flow Control            |    |

| 7.3.5  | Using Automated In-band Flow Control                |    |

| 7.3.6  | Using Special Character Detection                   |    |

| 7.3.7  | Transmitting and Receiving Nine-bit Data            |    |

| 7.3.8  | Data Transfer Using an Isochronous Clock            |    |

| 7.3.9  | Configuring Automatic RS-485 Buffer Enabling        |    |

| 7.3.10 | Enabling Sleep-Mode                                 |    |

| 8 ENHA | NCED FEATURES                                       | 68 |

| 8.1 PC | CI Power Management                                 | 68 |

| 8.2 Er | NHANCED PERFORMANCE FEATURES                        | 68 |

| 8.2.1  | Use of GIS registers                                | 68 |

| 8.2.2  | Use of shadowed fill levels and Good-data status    |    |

| 8.3 SI | ERIAL EEPROM                                        |    |

| 8.3.1  | Operation                                           |    |

| 8.3.2  | Example program                                     |    |

| 8.4 C1 | LOCK REFERENCE SIGNALS                              |    |

| 9 PERF | ORMANCE ENHANCEMENTS                                | 71 |

| 10 CON | NTACT INFORMATION                                   | 72 |

| 11 DIS | CLAIMER                                             | 72 |

|        | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~              |    |

#### 1 INTRODUCTION

This document describes example applications for the OX16PCI954 Integrated Quad UART and PCI interface. It provides design engineers with sufficient information and examples to integrate the device into a serial/parallel peripheral application such as a PC add-in card. Examples are given of all aspects of interfacing and using the device, however for detailed specifications the reader should refer to the data sheet.

In the sample applications, some basic knowledge of serial communications and PCI architecture is assumed, but any features particular to the OX16PCI954 are explained in detail.

The document is structured in such a way as to build up familiarity with the device, and provide a useful reference manual for electronic design engineers. In Section 2, a brief overview of the device is given. Section 3 continues with a description of how to access the various functions of the chip via the PCI interface. Section 4 provides examples of how to interface the device with associated interconnects and components, and then Section 4.6 provides whole application examples for many typical applications using this chip. Section 6 deals with programming the four OX16C950 UARTs which comprise the device's major function, and finally, Section 8 describes programming of the advanced PCI-specific features available.

#### 2 Device Overview

The OX16PCI954 is a single chip solution for PCI-based serial and parallel expansion cards. It has various modes of operation, which can provide a combination of four high-performance serial ports, a bidirectional parallel port, and an 8/32 bit Local expansion Bus, operated from a multifunction PCI interface. The device provides a simple means of designing PCI serial boards with up to 20 serial ports, low-cost 4-port PCI serial boards, or combo serial/parallel boards.

The device is a dual-function PCI target, where function 0 offers four high-peformance OX16C950 UARTs, and function 1 is configurable to offer either an 8/32 bit pass-through Local Bus or a bi-directional parallel port. The desired functions are selected via two 'Mode' pins, and then operation is performed through standard I/O or memory mapping on the PCI interface. For many applications, the OX16PCI954 and serial line drivers will be the only components necessary; however for more complex solutions many of the device default registers are reconfigurable from an optional serial EEPROM.

Therefore, to design a combo parallel / four-port serial card, the designer need to enable the four UARTs and the parallel port, and make the necessary connections to the PCI bus and line drivers. If the parallel port is not required, the pins can be reconfigured to assign the PCI Subsystem ID and Subsystem Vendor ID.

Alternatively, boards with up to 20 serial ports can be produced using the local bus function. In this case the designer should enable the four internal UARTs, and then add external UART devices onto the local bus, which can be configured to either Intel or Motorola-type operation.

In one further mode of operation, the internal UARTs can be disabled to allow their pins to be reconfigured to provide a full 32-bit pass through interface.

## 3 Configuration and Operation

#### 3.1 Mode selection

The Mode[1:0] pins are used to select which of the logical functions are enabled behind the PCI interface. Table 1 describes the configuration mapping used.

| Mode [1:0] | Configuration                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------|

| 00         | Function 0 is Quad UART, Function 1 is 8-bit Local Bus                                                    |

| 01         | Function 0 is Quad UART, Function 1 is bidirectional parallel port                                        |

| 10         | Function 0 is Quad UART, Function 1 is unusable as the local bus pins are used to assign Subsystem ID and |

|            | Subsystem Vendor ID to Function 0.                                                                        |

| 11         | Function 0 is unusable, Function 1 is 32-bit Local Bus                                                    |

**Table 1: Mode configuration**

## 3.2 Accessing logical functions

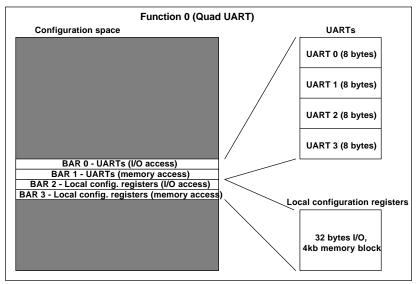

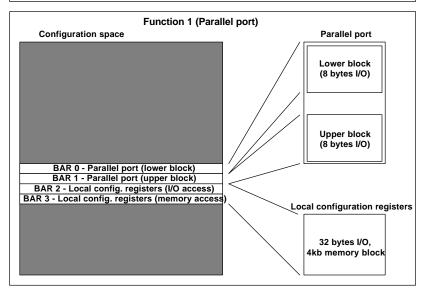

Operation of the UARTs, local bus and parallel port is implemented through standard I/O and memory address mapping. The configuration space for each function contains a number of Base Address Registers (BARs), which will be initialized by the system BIOS or Plug and Play operating system. Figure 1 (on page 8) shows the BAR mapping for the UARTs, 8-bit local bus and parallel port. The Plug and Play architecture automatically sets up the BARs in all PCI devices so that no address ranges overlap. Once they are set up, PCI I/O or memory reads to the specified locations will be directed to the respective function. Drivers need to read the value from configuration space (or the interface in the operating system) and direct accesses to the correct address.

Each function has its own unique address, however the local configuration registers can be accessed through either function. This enables multi-port drivers to easily snoop accesses and/or adjust the parameters for either function.

Mapping for the local bus can be reconfigured to suit the external devices connected. The size of the block is variable between 4 and 256 bytes of I/O space. The number of active address lines (maximum 8) depends on the block size selected. For 8-bit local bus, the memory block size is fixed at 4kb, however this can be increased to 16kb in 32-bit mode, where more address lines are available.

Table 2 shows which functions accept byte, word and dword accesses via I/O and memory mapping.

| PCI Function           | I/O accesses |      | Memory accesses |             |      |       |

|------------------------|--------------|------|-----------------|-------------|------|-------|

|                        | Byte         | Word | Dword           | Byte        | Word | dword |

| UARTs                  | ~            | Х    | Х               | <b>&gt;</b> | Х    | Х     |

| 8-bit Local Bus        | ~            | Х    | Х               | >           | Х    | Х     |

| 32-bit Local Bus       | ~            | ~    | ~               | >           | ~    | ~     |

| Parallel port          | ~            | Χ    | Х               | N/A         | N/A  | N/A   |

| Local config registers | ~            | Х    | Х               | <b>&gt;</b> | ~    | ~     |

**Table 2: Accessing logical functions**

Complete examples of applications and device register mapping are given in Section 4.6, since access to the local bus devices will vary between applications. Access to the local configuration registers is constant with application and which logical function is used, so a register map is given overleaf in Table 3.

| Register | Offset from Base Address 2 in I/O space (hex) | Offset from Base Address 3 in memory space (hex) |

|----------|-----------------------------------------------|--------------------------------------------------|

| LCC      | 0x00                                          | 0x00                                             |

| MIC      | 0x04                                          | 0x04                                             |

| LT1      | 0x08                                          | 0x08                                             |

| LT2      | 0x0C                                          | 0x0C                                             |

| URL      | 0x10                                          | 0x10                                             |

| UTL      | 0x14                                          | 0x14                                             |

| UIS      | 0x18                                          | 0x18                                             |

| GIS      | 0x1C                                          | 0x1C                                             |

Table 3: Accessing local configuration registers

Figure 1: Base address mapping

### 3.3 PCI interrupts

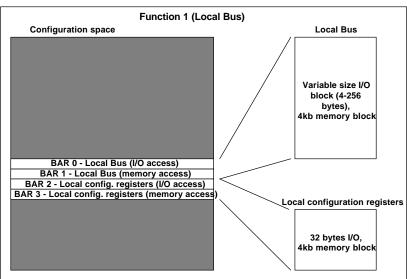

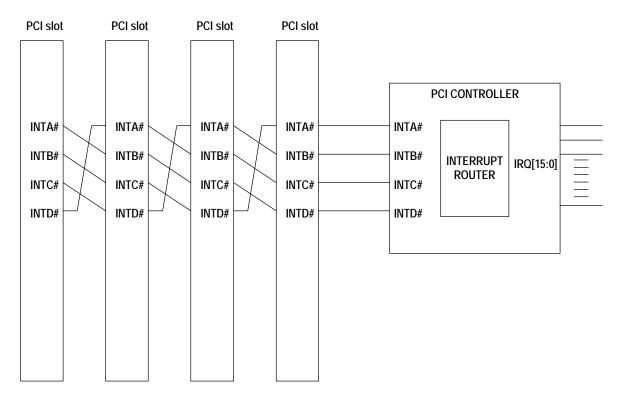

PCI interrupts are level-sensitive and can therefore be shared. One PCI add-in card is permitted to use all four interrupt pins, but if it uses fewer than this it must take INTA# first, then INTB#, INTC#, INTD# in order. A PCI platform with expansion slots usually has the form of interrupt layout shown in . Using this architecture, if all the add-in cards require only their INTA#, all card will have their own interrupt. Sharing will occur if a device uses more than one interrupt, or there are more than four devices on the bus.

To assert an interrupt, the device drives the signal low. To deassert, it allows it to float (open-drain connection). The pull-up is located on the system board.

Figure 2: PCI interrupt routing in PC systems

The OX16PCI954 can make use of one or two interrupts (INTA# and INTB#). The default routing is for Function 0 to assert interrupts on INTA# and Function 1 to assert interrupts on INTB#. This can be changed using the serial EEPROM; the only other permissible configuration is for both functions to use INTA#.

# **Interfacing the OX16PCI954**

#### 4.1 Pin descriptions

This section gives a functional description of each of the OX16PCI954 device pins. Device pin listings are given in Sections 3 and 4 of the data sheet; the information given below serves as an extension to the data sheet descriptions.

#### 4.1.1 Power supply pins

VDD and GND

Supply power to the device. When devices have multiple power and ground pins, all instances of VDD should be connected to +5V DC and all instances of GND should be connected to the 0V rail. Attention should also be given to local high-frequency decoupling due to the high-frequency switching that occurs in the device during normal operation. Note that there are two separate power and ground rails in the device, AC and DC. The DC rails supply power to all elements in steady state, while the AC rails supply current in switching state. This precaution reduces the effects of simultaneous sitching outputs and undesirable EMI interference.

### 4.1.2 PCI pins

AD[31:0] 32-bit multiplexed PCI address/data bus.

C/BE[3:0]# 4-bit bus command during PCI address phase, byte enable during data phase. The command encoding is as described

in the PCI specification. Since addressing is always DWORD aligned, the Byte Enables ensure that only the correct

bytes in an addressed DWORD are accessed.

CLK PCI system clock – speeds up to 33MHz are supported by the OX16PCI954.

FRAME# Signifies the start of a PCI transaction

DEVSEL# Output by the target device to acknowledge that it is the recipient of the current transaction. The OX16PCI954 supports

medium-speed decoding, ie it will assert DEVSEL# two clock cycles after FRAME# is activated if the address matches

any of its BARs.

IRDY# Output from the Bus Master (Initiator) to signify that it is ready to complete the data transfer.

TRDY# Output from the target to signify that it is ready to complete the data transfer

STOP# Target stop request. Output from the target to terminate the data transfer. The OX16PCI954 asserts this with TRDY# to

signify disconnect-with-data on every transfer. Therefore burst accesses are not supported.

PAR PCI transfer parity pin.

SERR# System error – output by the OX16PCI954 to report an error that may jeopardize system or data integrity.

PERR# Parity error – output by any PCI device to report a parity error

**IDSEL** Used by the PCI controller to select a device for a configuratin access.

RST# Active-low PCI device reset

INTA#, INTB# PCI interrupts. These are active-low, level sensitive, shared interrupts. They should always be connected to the INTA#

and INTB# pins respectively on the connector finger. The system board will then map these pins to any of the four PCI

interrupts.

PME# Power Management Event – used by the OX16PCI954 to report a power management event. Used to request that the

device driver wake-up the device from a low-power state. If Power Management functionality is required, use of an

isolator is recommended to prevent the OX16PCI954 activating PME# when powered down (see p25).

### 4.1.3 Serial port pins

FIFO Size Select input (common to all UART channels). This input determines the power up FIFO size. If it is tied low,

the default FIFO size is 16 bytes. If it is tied high, the default is 128 bytes. The FIFO size is also settable in software,

overriding the state of this pin. (See Section 7.2.2)

SOUT[3:0] Serial data output pin (for the respective UART channel). This pin also provides modulated IrDA output when IrDA mode

is enabled

SIN[3:0] Serial data input pin (for the respective UART channel). This pin is also a modulated IrDA signal input when IrDA mode

is enabled

CTS[3:0]# Clear to send input (for the respective UART channel). This pin's state is reflected in bit 4 of the Modem Status

Register. It is generally used for hardware flow control handshaking and is connected to the RTS# signal of the remote receiver. When automatic CTS flow control is enabled and this pin is de-asserted, the transmitter will be disabled after completion of the current character. This allows the remote receiver to moderate the flow of data from the transmitter and hence prevent FIFO overrun. A change of state of this pin will cause bit 0 of MSR to be set (delta CTS) and can be

configured to generate an interrupt. This pin may also be used as a general-purpose input.

DSR# Data Set Ready input (for the respective UART channel). This pin's state is reflected in bit 5 of the Modem Status

Register. Similar to CTS# It is generally used for hardware flow control handshaking and is connected to the DTR# signal of the remote receiver. When automatic DSR flow control is enabled, de-asserting this pin has the same affect as de-asserting CTS described above. A change of state of this pin will cause bit 1 of MSR to be set (delta DSR) and can

be configured to generate an interrupt. This pin may also be used as a general-purpose input.

RI[3:0]# Ring Indicator input (for the respective UART channel). This pin's state is reflected in bit 6 of the Modem Status

Register. This pin is generally connected to the RI output of a modem. This goes low when the modem is called from a remote device. A falling edge on this pin will cause bit 2 of MSR to be set (trailing edge RI) and can be configured to

generate an interrupt. This pin may also be used as a general-purpose input.

The RI pin may be configured as a receiver 1x clock source for isochronous operation. See Sections 4.3.5 and 7.3.8.

DCD[3:0]# Data Carrier Detect input (for the respective UART channel). This pins state is reflected in bit 7 of the Modem Status Register. This pin is generally connected to the DCD output of a modem, which is asserted when a valid data carrier

signal is present on the line. A change of state of this pin will cause bit 3 of MSR to be set (delta DCD) and can be

configured to generate an interrupt. This pin may also be used as a general-purpose input.

RTS[3:0]# Ready to send output (for the respective UART channel). This pin's state is set by bit 1 of the Modem Control Register.

It is generally used for hardware flow control handshaking and is connected to the CTS# input of the remote transmitter. When automatic RTS flow control is enabled this pin is de-asserted and asserted in accordance with pre-defined flow control trigger levels in the receiver FIFO. This allows the receiver to disable and enable the remote transmitter according to how much data is held in the receiver FIFO (as long as it is also using CTS/RTS flow control) and hence

prevents FIFO overrun. This pin may also be used as a general-purpose output.

DTR[3:0]# Data Terminal Ready output (for the respective UART channel). This pin's state is set by bit 0 of the Modem Control

Register. It is generally used for hardware flow control handshaking and is connected to the DSR# input of the remote transmitter. When automatic DTR flow control is enabled this pin is de-asserted and asserted in accordance with predefined flow control trigger levels in the receiver FIFO, as with RTS. This pin may also be used as a general-purpose

output.

DTR may also be configured as an RS-485 buffer enable pin (see Section 4.2.2.1) or a 1x clock source (Section 4.3.5).

XTLO This pin provides an output driver for a crystal oscillator circuit (see Section 4.3). It is not used when an alternative TTL

level clock input is applied to XTLI, and can be left unconnected.

XTLI Main system clock input. This pin is used as a direct TTL level clock input or in conjunction with XTLO in a crystal

oscillator circuit configuration (see Section 4.3).

#### 4.1.4 Local Bus Pins

LBA[7:0] Local Bus address signals. In 32-bit mode the UART's pins are redefined to provide LBA[11:0]

LBD[7:0] Local Bus Data signals. In 32-bit mode the UART's pins are redefined to provide LBD[31:0]

LBCS[3:0] Local Bus chip-select signals. The local bus address block can be subdivided into one, two or four chip-select regions. If

it is defined as one whole block, LBCS0# will be activated on all accesses. If there are two regions, the lower half will be controlled by LBCS0# and the upper half by LBCS1#. If four regions, the block is split equally between the four chip-select signals. See Section 4.2.4 for information on defining chip-select regions. In motorola-type mode these pins are

redefined as Data strobe (LBDS#) pins.

LBWR# Local Bus write strobe. In Intel-type mode this initiates a write access to local bus peripherals. In Motorola-type mode

this pin is redefined to Read-not-Write control (LBRDWR#).

LBRD# Local Bus read strobe. In Intel-type mode this initiates a read access to local bus peripherals. In Motorola-type mode

this pin is redefined to permanent high impedance.

**LBRST** Local Bus active-high reset

**LBRST#** Local Bus active-low reset.

**LBDOUT** Local Bus data-out enable. This pin can be used by optional external transceivers; it is high when LBD[7:0] are in output

mode and low when they are in input mode. This pin also applies to the parallel port.

**UART CIK Out** Buffered UART oscillator output. This clock is a buffered version of the signal present on the XTLI pin. It can be used to

drive external oscillators from one single oscillator circuit. See Section 8.4 for information on this pin.

**LBCLK** Buffered PCI Clock. Local bus operation is synchronised to this clock. See Section 8.4 for information on this pin.

## 4.1.5 Parallel port pins

#### STANDARD PARALLEL PORT (SPP) MODE:

PD[7:0] Bi-directional 8-bit parallel data, bits 7 (MSB) to 0 (LSB).

**INIT#** Active-Low Initialise input/output. This pin is used to send an initialisation signal to a peripheral. The pins state is set

using 'Peripheral Control Register' PCR[2]. PCR[2] = 0 sets the output low (active) PCR[2] = 1 sets it high.

**ERR#** Peripheral Error Input. This pin is held low by a peripheral to assert an error condition. The state of this pin is reflected

in bit 3 of the 'Peripheral Status Register' PSR. This is a user defined pin in EPP mode.

SLCT# Peripheral Selected Input. This pin is held low by a peripheral when it is selected. The state of this pin is reflected in bit

4 of the 'Peripheral Status Register' PSR. This is a user defined pin in EPP mode.

PE Paper Empty input. This pin is held high by a peripheral to assert an 'out of paper' condition. The state of this pin is

reflected in bit 5 of the 'Peripheral Status Register' PSR. This is a user defined pin in EPP mode.

ACK# Peripheral Acknowledge Input. PSR[6] PSR[2] (INT#) cleared on rising edge of this pin

AFD# Auto Feed input/output. The state of this pin is set and read using bit 1 of the 'Peripheral Control Register' PCR bit 1

(0 = inactive, 1 = active).

**BUSY** Peripheral Busy Input. This pin is set high by a peripheral when it is not ready to receive data. Its state is reflected in

'Peripheral Status Register' PSR bit 7.

SLIN# Peripheral Select input/output. This output is asserted to attempt to select a peripheral. The state of this pin is set by

Peripheral Control Register' PCR bit 3 (0 = inactive, 1 = active). The input state of the pin is also readable from this bit.

STB# Data Strobe input/output. The peripheral uses this line to latch the data currently available on the PD[7:0] data lines.

The state of this pin is set by 'Peripheral Control Register' PCR bit 0 (0 = inactive, 1 = active). The input state of the pin

is also readable from this bit.

#### ENHANCED PARALLEL PORT (EPP) MODE:

For more information on EPP parallel port signals, refer to the IEEE 1284 EPP specification. Most pins remain the same as defined for SPP mode, however the following pins are redefined:

Functionality is the same as SPP-mode ACK#. INTR# (ACK#)

WAIT# (BUSY#) Active-low handshake output. This pin is driven by the internal EPP controller.

DATASTB# (AFD#) Active-low Data Strobe output. This pin is driven by the internal EPP controller and provides data read/write data strobe signals.

ADDRSTB# (SLIN#) Active-low address strobe output. This pin is driven by the internal EPP controller, and provides the address read / write strobe signals.

WRITE# (STB#) Write / not read output. This pin is driven by the internal EPP controller, identifying write cycles when low and read cycles when high.

### 4.1.6 Subsystem ID and Subsystem Vendor ID pins

Sub\_ID[15:0] In Mode '10', these pins are provided to hard-wire the Subsystem ID of Function 0

Sub\_V\_ID[15:0] In Mode '10', these pins are provided to hard-wire the Subsystem Vendor ID of Function 0

## 4.1.7 Multi-purpose Input and output pins

MIO[11:3] These pins can drive high or low, or be used as inputs to generate a PCI interrupt.

MIO<sub>2</sub> The function of this pin is dependent on the setting of LCC[7] in the local configuration registers. When LCC[7]=0, this

pin has the same MIO function as MIO[11:3]. When LCC[7] is set, it is used as an input to generate a Power

management event for function 1.

MIO<sub>1</sub> The function of this pin is dependent on the setting of LCC[6:5]. When LCC[6:5]=00, it has the same MIO function as

MIO[11:3]. When LCC[6:5]≠00, this pin is defined as permanent high-impedance.

The function of this pin is dependent on the mode of operation of the OX16PCI954. When in Mode '01' this pin is MIO0

defined as permanent high-impedance. In other modes it has the same MIO function as MIO[11:3].

#### 4.1.8 Serial EEPROM pins

EE CK EEPROM clock. If the optional serial EEPROM is used, this pin should be connected to CK. This pin drives high or low depending on the setting of LCC[24] in the Local Configuration Registers

EEPROM active-high chip-select. If the optional serial EEPROM is used, this pin should be connected to CS. This pin EE CS

drives high or low depending on the setting of LCC[25] in the Local Configuration Registers.

EE\_DI EEPROM data in. If the optional serial EEPROM is used, this pin should be connected to DO, and pulled high with an

external resistor (value 1k-10k).

**EE\_DO**EEPROM data out. If the optional serial EEPROM is used, this pin should be connected to DI. This pin drives high or low depending on the setting of LCC[26] in the Local Configuration Registers.

Note: after a reset, these pins are controlled by the EEPROM interface controller, and will download any valid memory contents to the OX16PCI954.

#### 4.1.9 Miscellaneous pins

**TEST** This pin must be connected to GND.

**MODE[1:0]** These pins select the mode of operation of the device. See Section 3.1.

## 4.2 Standard Connectivity

This section describes briefly how to interface the OX16PCI954 modules to other components of a serial / parallel port application. Table 4 provides a quick reference, and each module is described seperately in more detail below.

| Pin                                                                                                               | Mode     | Description                                | Action when used                                            | Action when not used |

|-------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------|-------------------------------------------------------------|----------------------|

| VDD                                                                                                               | All      | Power supply                               | Connect directly to +5V DC                                  | N/A                  |

| GND                                                                                                               | All      | Power supply                               | Connect directly to 0V DC                                   | N/A                  |

| TEST                                                                                                              | All      | Manufacturing test                         | Connect directly to 0V DC                                   | N/A                  |

| Mode[1:0]                                                                                                         | All      | Mode selector                              | Select mode as per Table 1 (p6).                            | N/A                  |

| AD[31:0]                                                                                                          | All      | PCI Multiplexed<br>Address / Data pins     | Connect to AD[31:0] on the PCI bus                          | N/A                  |

| C/BE[3:0]#                                                                                                        | All      | PCI Command / byte enable                  | Connect to C/BE[3:0] on the PCI bus                         | N/A                  |

| CLK, FRAME#,<br>DEVSEL#,<br>IRDY#, TRDY#,<br>STOP#, PAR,<br>SERR#, PERR#,<br>IDSEL, RST#<br>INTA#, INTB#,<br>PME# | All      | PCI Control signals                        | Connect to respective signals on the PCI bus                | N/A                  |

| FIFOSEL                                                                                                           | 00,01,10 | FIFO select                                | Connect to GND for 16-deep FIFOs, to VDD for 128-deep FIFOs | Tie high or low      |

| SOUT                                                                                                              | 00,01,10 | Serial data output                         | Connect to a suitable line driver (See Section 4.2.2)       | Leave unconnected    |

| SIN                                                                                                               | 00,01,10 | Serial data input                          | Connect to a suitable line receiver (See Section 4.2.2)     | Tie high             |

| RTS#                                                                                                              | 00,01,10 | Request-To-Send<br>Modem signal output     | Connect to a suitable line driver (See Section 4.2.2)       | Leave unconnected    |

| CTS#                                                                                                              | 00,01,10 | Clear-To-Send<br>Modem signal input        | Connect to a suitable line receiver (See Section 4.2.2)     | Tie high             |

| DTR#                                                                                                              | 00,01,10 | Data-Terminal-Ready<br>Modem signal output | Connect to a suitable line driver (See Section 4.2.2)       | Leave unconnected    |

| DSR#                                                                                                              | 00,01,10 | Data-Set-Ready<br>Modem signal input       | Connect to a suitable line receiver (See Section 4.2.2)     | Tie high             |

| DCD#                                                                                                              | 00,01,10 | Data-Carrier-Detect<br>Modem signal input  | Connect to a suitable line receiver (See Section 4.2.2)     | Tie high             |

| RI#                                                                                                               | 00,01,10 | Ring-Indicator<br>Modem signal input       | Connect to a suitable line receiver (See Section 4.2.2)     | Tie high             |

| Pin                                                              | Mode      | Description                          | Action when used                                                               | Action when not used                                                 |

|------------------------------------------------------------------|-----------|--------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| UART_Clk_Out                                                     | All       | Buffered UART clock                  | Connect to XTLI on external UARTs                                              | Leave unconnected                                                    |

| LBRST                                                            | 00,11     | Local Bus reset                      | Connect to active-high reset on external UARTs                                 | Leave unconnected                                                    |

| LBRST#                                                           | 00,11     | Local Bus reset                      | Connect to active-low reset on external UARTs                                  | Leave unconnected                                                    |

| LBDOUT                                                           | 00,01,11  | Local Bus Data out enable            | Connect to direction pin of external transceiver                               | Leave unconnected                                                    |

| LBCLK                                                            | 00,11     | Buffered PCI clock                   | Connect to clock reference on external devices                                 | Leave unconnected                                                    |

| LBCS#                                                            | 00,11 (I) | Local Bus chip-select                | Connect to chip-select on external Intel-mode devices                          | Leave unconnected                                                    |

| LBDS#                                                            | 00,11 (M) | Local Bus Data strobe                | Connect to data-strobe on external Motorola-mode devices                       |                                                                      |

| LBWR#                                                            | 00,11 (I) | Local Bus write strobe               | Connect to WR# on external Intel-<br>mode devices                              | Leave unconnected                                                    |

| LBRDWR#                                                          | 00,11 (M) | Local Bus Read-not-<br>write control | Connect to RD/WR# on external Motorola-mode devices                            |                                                                      |

| LBRD#                                                            | 00,11 (I) | Local Bus read strobe                | Connect to RD# on external Intel-<br>mode devices                              | Leave unconnected<br>(always N/C when local<br>bus is Motorola-type) |

| LBA[7:0]<br>LBA[11:0]                                            | 00<br>11  | Local Bus address                    | Connect to address pins on external devices or to decode logic                 | Leave unconnected                                                    |

| LBD[7:0]<br>LBD[31:0]                                            | 00<br>11  | Local Bus data                       | Connect to data pins on external devices                                       | Leave unconnected                                                    |

| ACK#, PE,<br>BUSY, SLCT,<br>ERR#, SLIN#,<br>INIT#, AFD#,<br>STB# | 01        | Parallel port control signals        | Connect to parallel port connector and pull up with external resistor (1k-10k) | Leave unconnected                                                    |

| PD[7:0]                                                          | 01        | Parallel port data signals           | Connect to data transceiver or parallel port connector.                        | Leave unconnected                                                    |

| Sub_ID[15:0]                                                     | 10        | Subsystem ID                         | Tie pins to VDD or GND as per required subsystem ID                            | N/A                                                                  |

| Sub_V_ID[15:0]                                                   | 10        | Subsystem Vendor ID                  | Tie pins to VDD or GND as per required subsystem Vendor ID                     | N/A                                                                  |

| MIO[11:0]                                                        | All       | Multi-purpose<br>Input/Output        | Configure function in Local configuration registers, connect as required       | Tie low (or high as<br>required) with 10k<br>resistor                |

| EE_CS                                                            | All       | EEPROM chip select                   | Connect to EEPROM CS pin                                                       | Leave unconnected                                                    |

| EE_CK                                                            | All       | EEPROM clock                         | Connect to EEPROM CK pin                                                       | Leave unconnected                                                    |

| EE_DI                                                            | All       | EEPROM Data in                       | Connect to EEPROM DO pin and pull up with external resistor (1k-10k)           | Leave unconnected                                                    |

| EE_DO                                                            | All       | EEPROM Data out                      | Connect to EEPROM DI pin                                                       | Leave unconnected                                                    |

**Table 4: Device Pins**

#### 4.2.1 Common connectivity example

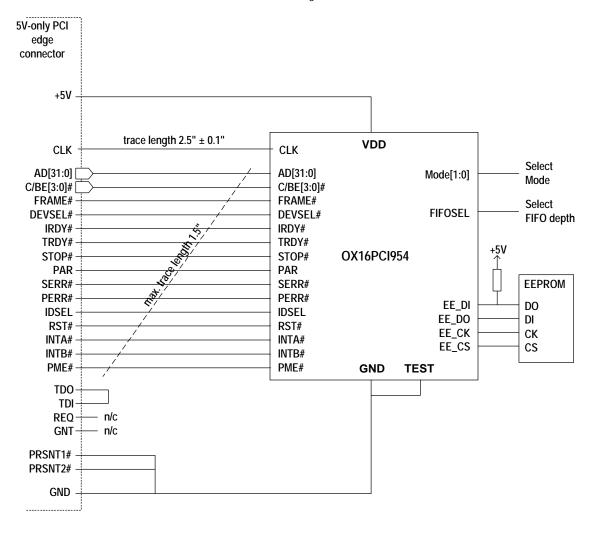

Figure 3 shows how to interface the common elements of a solution using the OX16PCI954.

Figure 3: Interfacing the OX16PCI954

Note: All PCI pins should be connected to their respective signals on the PCI bus / edge connector, in strict adherence to the layout guidelines provided in the PCI specification.

#### 4.2.2 Serial port interfacing

#### 4.2.2.1 Connectivity examples

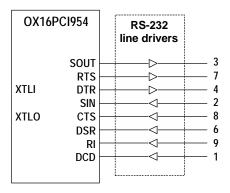

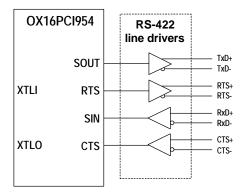

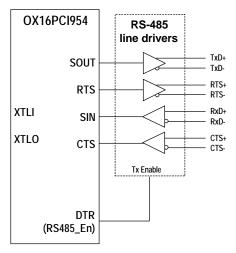

The examples below show how to interface any of the serial ports to RS232, RS422 and RS485 half-duplex line drivers/receivers. Either clock option is valid; use a crystal with suitable passive components, or connect directly to a clock source.

Figure 4: Interfacing an RS-232 port

Figure 5: Interfacing an RS-422 port

Figure 6: Interfacing an RS-485 port for half-duplex operation

#### 4.2.2.2 RS-232 Line Drivers

RS-232 is the industry standard for PC serial communications. It employs single ended line driving at +/- 12V logic levels and can cover distances of up to 30 metres. Most standard RS-232 line drivers are capable of speeds up to 115.2 Kbps and can be used in conjunction with cost effective bundled multi-wire cables. Some high-speed line drivers are also available, capable of speeds up to 1Mbps.

#### 4.2.2.3 RS-422 Line Drivers

RS-422 allows a single transmitter to communicate with up to 10 separate receivers. Differential signals are used requiring the use of a twisted pair cable over long distances. Each signal requires a pair of cables instead of the single cable used for RS-232.

Data rates of up to 10 Mbps per second are achievable over short distances (around 10 metres), with lower rates, up to 100 Kbps, being possible over distances as high as 1.2 Km.

#### 4.2.2.4 RS-485 Line Drivers

RS-485 is similar to RS-422. It allows up to 32 transmitters to communicate with up to 32 receivers on a common data bus. One device will transmit data at any given time, while the remaining devices are able to simultaneously receive it. RS-485 line drivers are equipped with drive enable inputs that allow them to either drive the bus, or to switch into a high impedance tri-state mode.

This standard operates under the same distance / speed restrictions as RS-422 and has the same cable requirements.

#### 4.2.2.5 Suggested Line Drivers

The following table gives a suggested line transceiver for each of the above standards. Suitable parts mentioned are available from  $MAXIM^{TM}$  (see Table 5), although there are a wide variety of line drivers and receivers available from a range of other manufacturers, such as National Semiconductor<sup>TM</sup>, Analog Devices<sup>TM</sup>, Linear Technology<sup>TM</sup> and many others.

| Protocol     | Maximum Speed | Line Driver Description                        | MAXIM ™ Part No. |

|--------------|---------------|------------------------------------------------|------------------|

| RS-232       | 115.2 Kbps    | 4 Drivers / 5 Receivers, 28-pin surface mount  | MAX241           |

| RS-232       | 1 Mbps        | 2 Drivers / 2 Receivers, 20-pin surface mount  | MAX3225          |

| RS-422 / 485 | 10 Mbps       | Single Driver / Receiver, 10-pin surface mount | MAX1484          |

Table 5: Suggested Line Transceiver IC's

#### 4.2.3 Local bus examples

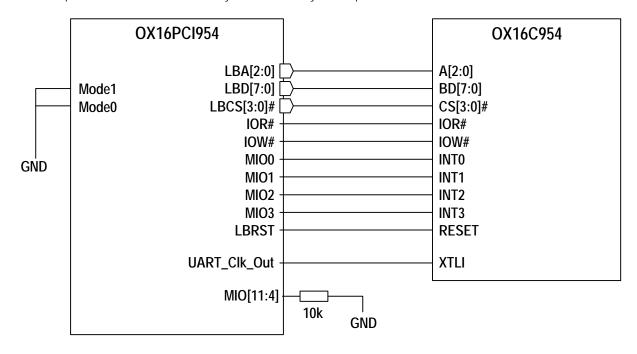

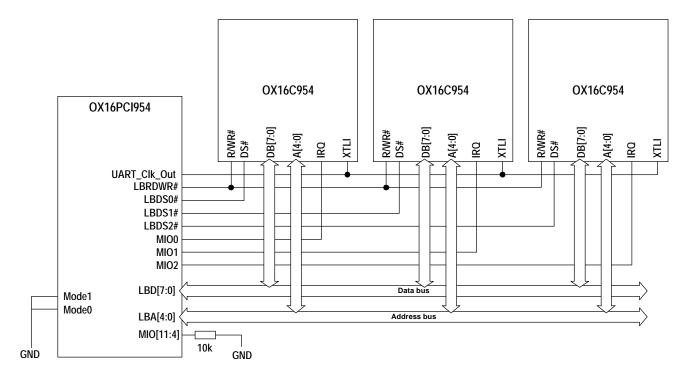

Figure 7 shows an example of a Quad UART device connected to the local bus in Intel mode (to make an 8-port serial card). Figure 8 shows 3 devices connected in Motorola mode; this would comprise a 16-port serial card. Note, for glueless implementation of serial cards with more than 8 ports Motorola mode is necessary as there are only four chip selects available.

Figure 7: Interfacing the local bus in Intel Mode

Figure 8: Interfacing the local bus in Motorola Mode

#### 4.2.4 Local bus addressing

The local bus address space can be set in the region of 4 bytes – 256 bytes of I/O space, and 4K bytes of memory space (can be increased to 16K bytes in 32-bit bridge mode). In memory space, the addressable block is always divided into four chip-select regions, however in I/O space it can be divided into one, two or four regions according to the requirements of the peripheral devices connected.

The block size is defined by LT2[22:20] in the local configuration registers, as described in the data sheet. For block sizes less than 256 bytes, the upper address lines which are not needed will always be zero; for example if the default size of 32 bytes is used, this requires Local Bus address pins LBA[4:0], therefore LBA[7:5] will be zero.

The chip-select regions are defined using LT2[26:23]. This bits are named "Lower-Address-CS-Decode" and define which of the LBA[7:0] pins represents a chip-select region boundary. Shows the value which must be programmed into LT2[26:23] to select the required number of chip-select regions.

| Number of chip- | I/O sp | I/O space block size (bytes) |    |            |            |            |     |

|-----------------|--------|------------------------------|----|------------|------------|------------|-----|

| select regions  | 4      | 8                            | 16 | 32         | 64         | 128        | 256 |

| One             | A2     | A3                           | A4 | <b>A</b> 5 | A6         | A7         | A8  |

| Two             |        | A2                           | A3 | A4         | <b>A</b> 5 | A6         | A7  |

| Four            |        |                              | A2 | A3         | A4         | <b>A</b> 5 | A6  |

Table 6: Lower-address-Chip-select decode values

### 4.3 UART clock options

If the UARTs are required in the application, a clock signal must be applied to the XTLI pin. The speed of this clock determines the maximum baud rate at which the device can receive and transmit serial data. This maximum baud rate is equal to one sixteenth of the frequency of the system clock (Increasing to one guarter of this value if TCR=4 is used, see Section 7.3.1).

The industry standard system clock for PC COM ports is 1.8432 MHz, limiting the maximum baud rate to 115.2 Kbps. The OX16PCI954 supports system clocks up to 60MHz, and its flexible baud rate generation hardware means that almost any frequency can be optionally scaled down for compatibility with standard devices.

Designers have the option of using either TTL clock modules or crystal oscillator circuits for system clock input, with minimal additional components. The following two sections describe how each can be connected.

NOTE: For very low power applications, use of a low power TTL clock module is recommended

NOTE: Please see Section 4.3.4 on high speed operation when considering applications requiring baud rates in excess of 1Mbps.

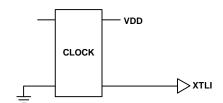

#### 4.3.1 TTL Clock Module

Using a TTL module for the system clock simply requires the module to be supplied with +5v power and GND connections. The clock output can then be connected directly to XTLI. XTLO should be left unconnected.

Figure 9: TTL Clock Module Connectivity

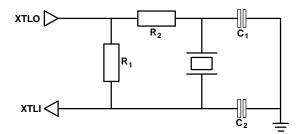

#### 4.3.2 Crystal Oscillator Circuit

The OX16PCI954 provides the XTLO output pin to drive a crystal oscillator circuit. The circuit is shown below with suggested component values. Owing to the nature of such circuits, some variation in these values may be required to ensure stable oscillation at different frequencies. The total load capacitance (C1 and C2 in series) however, should be approximately that stated by the crystal manufacturer (nominally 16pF).

Figure 10: Crystal Oscillator Circuit

| Frequency Range (MHz) | C1 (pF) | C2 (pF) | R1 (Ω)     | R2 (Ω) |

|-----------------------|---------|---------|------------|--------|

| 1-8                   | 68      | 22      | 220K       | 470R   |

| 8-60                  | 33 – 68 | 33 - 68 | 220K – 2M2 | 470R   |

#### 4.3.3 Suggested Clock Frequencies

Table 7 below shows a range of standard serial communication clock frequencies, starting at 1.8432 MHz, the standard used in almost all PC COM ports. With each frequency is given a pair of maximum baud rates. One using the standard 16x over-sampling clock (i.e. where the maximum baud rate is restricted to 1/16 of the input clock frequency), and one using a 4x over-sampling clock (configured by writing to the TCR register). All baud rates assume that the prescaler is bypassed and hence no pre-division of the input clock is used. See Section 7.3.1 for more information on TCR and the prescaler.

| Input Clock Frequency | Maximum standard baud rate | Maximum baud rate with<br>4x over-sampling clock |

|-----------------------|----------------------------|--------------------------------------------------|

| 1.8432 MHz            | 115.2 Kbps                 | 460.8 Kbps                                       |

| 3.6864 MHz            | 230.4 Kbps                 | 921.6 Kbps                                       |

| 4.9152 MHz            | 307.2 Kbps                 | 1.23 Mbps                                        |

| 7.3728 MHz            | 460.8 Kbps                 | 1.843 Mbps                                       |

| 8.192 MHz             | 512 Kbps                   | 2.048 Mbps                                       |

| 14.7456 MHz           | 921.6 Kbps                 | 3.686 Mbps                                       |

| 18.432 MHz            | 1.152 Mbps                 | 4.608 Mbps                                       |

| 32.768 MHz            | 2.048 Mbps                 | 8.192 Mbps                                       |

Table 7: Example maximum baud rates for various input clock frequencies

The standard baud rate divisor word registers allow any divisor of these maximum values in the range 1 to 65535 (0x0001 to 0xFFFF).

#### 4.3.4 High speed operation

Designers using these devices in high speed applications (UART System clock > 10MHz) are advised to follow the guidelines for high speed digital design, paying particular attention to the following:

- Keeping PCB tracks carrying high speed signals and return currents as short and direct as possible

- Correct termination of high-speed traces

- Use of mutli-layered PCB with separate power and ground planes

- Adequate decoupling as near as possible to all high-frequency components

#### 4.3.5 Isochronous Clock Mode

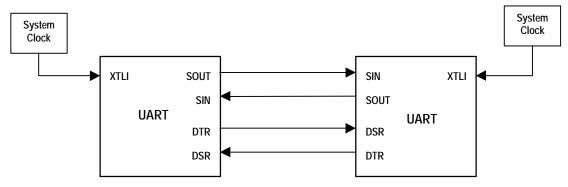

Figure 11 below illustrates the clock configuration required to operate OX16C95x devices in Isochronous mode. The 950 can be configured to output its own 1x clock on the DTR pin and accept a receiver clock on the DSR pin. In the configuration shown, it is therefore possible to receive and transmit at different baud rates if different system clocks are employed at either end. Note that this figure does not apply to OX16C952 and OX16C954 devices – see relevant application notes for information.

Figure 11: 950 Isochronous Configuration

For information on configuring Isochronous mode operation in the UART, see Section 7.3.8.

### 4.4 Multi-purpose input / output pins (MIO)

Twelve MIO pins are provided (MIO[11:0]). These can be used to provide drive high or low signals, or can be used to pass external sources of interrupts to the PCI INTA#/INTB# pins. The function of the pins is controlled using the MIC register. Each pin can be reconfigured seperately. When configured as an input, an active signal present on the MIO pin will be passed through to the PCI interrupt pin if the interrupt mask in the GIS register is set.

If there are unused MIO pins in the application, care should be taken that these do not cause spurious interrupts. Therefore they should either be masked off in the GIS register, or tied inactive using pull-down (or pull-up resistors). A direct connection to VDD or GND is sufficient; however there is risk of the user inadvertently configuring the pin to drive high or low.

#### 4.5 External connections

#### 4.5.1 Serial ports

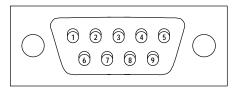

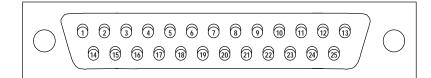

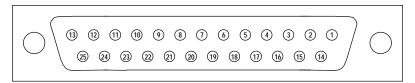

Standard PC COM ports operate using the RS232 standard and use either a 9-Pin or a 25-Pin male D-Type connector. The pin numbering for these connectors is given in the following diagram. Note that normally, only 9 pins on the 25 pin connector are actually used. It is used for compatibility with other devices such as modems, which also have 25 pin connectors.

Table 8 details the signal pin out for both of these connectors

9-Pin D Type Connector

25-Pin D Type Connector

Figure 12: D Type connector pin numbering (Front view)

| Signal              |     | 9-PIN<br>CONNECTO<br>R | 25-Pin<br>Connector |

|---------------------|-----|------------------------|---------------------|

| Data Carrier Detect | DCD | 1                      | 8                   |

| Received Data       | RxD | 2                      | 3                   |

| Transmitted Data    | TxD | 3                      | 2                   |

| Data Terminal Ready | DTR | 4                      | 22                  |

| Ground              | GND | 5                      | 7                   |

| Data Set Ready      | DSR | 6                      | 6                   |

| Request To Send     | RTS | 7                      | 4                   |

| Clear To Send       | CTS | 8                      | 5                   |

| Ring Indicator      | RI  | 9                      | 20                  |

Table 8: Serial port D Type connector pin-outs

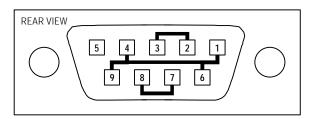

#### 4.5.2 RS-232 Loopback Connector

Serial loopback connectors are often used for testing serial ports. Such connectors simply feed the output signals and data back in to their corresponding inputs on the same port. The diagram below illustrates the connectivity of an RS-232 loopback plug for a standard 9-Pin PC COM port. This is the rear view (solder side) of a female 9-pin D connector. It connects TxD to RxD, RTS to CTS and DTR to DSR, RI & DCD. The ground pin has no connection.

9-Pin RS-232 Serial Loopback Connector

#### 4.5.3 PC Parallel Port Connections

The diagram below illustrates the pin numbering of the standard PC parallel port. This is a standard 25 pin D-Type connector and is shown here as if from the rear of the PC. The following table lists the standard simple parallel port pin-out for this connector.

Figure 13: Standard SPP PC Parallel port connector

| Pin # | Signal  |

|-------|---------|

| 1     | STB#    |

| 2-9   | PD0 – 7 |

| 10    | ACK#    |

| 11    | BUSY    |

| 12    | PE      |

| 13    | SLCT    |

| 14    | AFD#    |

| 15    | ERR#    |

| 16    | INIT    |

| 17    | SLIN    |

| 18-25 | GND     |

Table 9: Parallel port connector pinout

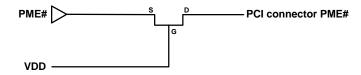

#### 4.6 Power Management

The OX16PCI954 support PCI Power Management states D0, D2 and D3. However, when in power state  $D3_{cold}$ , the device is powered down, and in this condition the PME# line presents a low-impedance path to GND through clamping diodes. In some cases this can cause the PC to wake up from Power State  $D3_{cold}$ . Therefore, care should be taken when designing an add-in card to be used in fully-ACPI compliant systems.

If Power Management functionality is not required, the PME# should be treated as no-connect

If Power management will be used, use of an isolator FET is recommended so that the PME# pin remains Hi-Z even when the OX16PCI954 is powered down. A suitable circuit is shown in Figure 14.

Figure 14: PME# isolator circuit

# 5 Typical applications

This section provides examples of typical serial / parallel applications using the OX16PCI954 device. Several typical application examples are given; for each one a description is given of the components required, connectivity needed and register/logical function mapping across the PCI interface. Detail is only given for connections particular to the application; it is assumed that the PCI interface, TEST etc. are connected as described in Section 4.

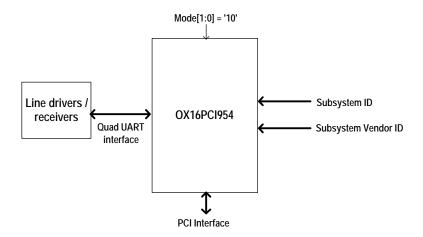

#### 5.1 Low cost four-port serial card.

This application uses the device in Mode '10'; because neither the local bus or parallel port are required the pins can be used to assign the Subsystem Vendor ID and Subsystem ID of function 0.

#### 5.1.1 Interfacing

The only components needed are the OX16PCI954 and RS232/422 line drivers. A block diagram is given in Figure 15.

Figure 15: Low-cost four-port serial card

| OX16PCI954 pins         | Connection                 |

|-------------------------|----------------------------|

| Mode[1:0]               | 10                         |

| PCI control / data pins | PCI interface connections  |

| UART signals            | RS232/422/485 Line drivers |

| Sub_V_ID[15:0]          | 16-bit Subsystem Vendor ID |

| Sub_ID[15:0]            | 16-bit Subsystem ID        |

**Table 10: Connections required**

# 5.1.2 Operation

The UARTs are accessed through BAR0 and BAR1 of function 0, as shown in Table 11. Note that since the memory space occupies a 4kb block, there are a number of aliases of the UARTs in the allocated region. The local configuration registers can be accessed as described in Section 3.2.

| UART<br>address | Offset from Base Address 0 in I/O space (hex) |       |       | Offset from Base Address 1 in memory space (hex) |       |       |       |       |

|-----------------|-----------------------------------------------|-------|-------|--------------------------------------------------|-------|-------|-------|-------|

| (bin)           | UART0                                         | UART1 | UART2 | UART3                                            | UART0 | UART1 | UART2 | UART3 |

| 000             | 00                                            | 80    | 10    | 18                                               | 00    | 20    | 40    | 60    |

| 001             | 01                                            | 09    | 11    | 19                                               | 04    | 24    | 44    | 64    |

| 010             | 02                                            | 0A    | 12    | 1A                                               | 08    | 28    | 48    | 68    |

| 011             | 03                                            | 0B    | 13    | 1B                                               | 0C    | 2C    | 4C    | 6C    |

| 100             | 04                                            | 0C    | 14    | 1C                                               | 10    | 30    | 50    | 70    |

| 101             | 05                                            | 0D    | 15    | 1D                                               | 14    | 34    | 54    | 74    |

| 110             | 06                                            | 0E    | 16    | 1E                                               | 18    | 38    | 58    | 78    |

| 111             | 07                                            | 0F    | 17    | 1F                                               | 1C    | 3C    | 5C    | 7C    |

Table 11: Access to UARTs in I/O and memory space

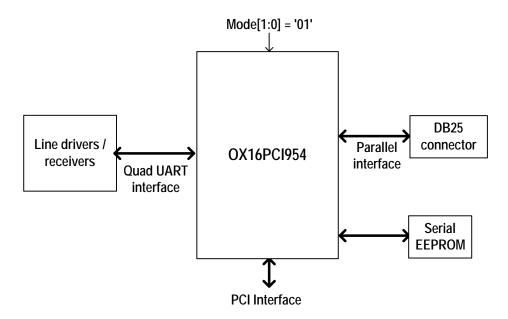

## 5.2 Combo four-port serial, one-port parallel card.

This application uses the device in Mode '01'. Note that the serial EEPROM is not necessary for operation; however it is necessary to set Subsystem IDs to non-zero values for full PCI 2.2 compliance.

## 5.2.1 Interfacing

The only components needed are the OX16PCI954 and RS232/422 line drivers. A block diagram is given in Figure 16.

Figure 16: Four-port serial plus parallel port card

| OX16PCI954 pins                   | Connection                 |

|-----------------------------------|----------------------------|

| Mode[1:0]                         | 01                         |

| PCI control / data pins           | PCI interface connection   |

| UART signals                      | RS232/422/485 Line drivers |

| EEPROM signals                    | Serial EEPROM              |

| MIO[11:0]                         | GND (via 10k resistor)     |

| Parallel port control / data pins | Parallel port connector    |

**Table 12: Connections required**

## 5.2.2 Operation

The UARTs are accessed through BAR0 and BAR1 of function 0, in the same fashion as for the previous example (see Table 11). The parallel port register map is divided into two block, lower and upper. In legacy parallel ports the upper block is always placed at an address 400h above the lower block. If this relationship is set in the BARs for the OX16PCI954, generic drivers can be used for SPP and EPP mode operation. A register map for the parallel port is shown in Table 13, with the assumption that the 400h relationship is present.

| Parallel port address (hex) | Offset from Base<br>Address 0 (hex) | Offset from Base<br>Address 1 (hex) |

|-----------------------------|-------------------------------------|-------------------------------------|

| 000                         | 00                                  | N/A                                 |

| 001                         | 01                                  | N/A                                 |

| 002                         | 02                                  | N/A                                 |

| 003                         | 03                                  | N/A                                 |

| 004                         | 04                                  | N/A                                 |

| 005                         | 05                                  | N/A                                 |

| 006                         | 06                                  | N/A                                 |

| 007                         | 07                                  | N/A                                 |

| 400                         | N/A                                 | 00                                  |

| 401                         | N/A                                 | 01                                  |

| 402                         | N/A                                 | 02                                  |

| 403                         | N/A                                 | 03                                  |

Table 13: Access to Parallel Port in I/O space

# 5.3 8-port serial card

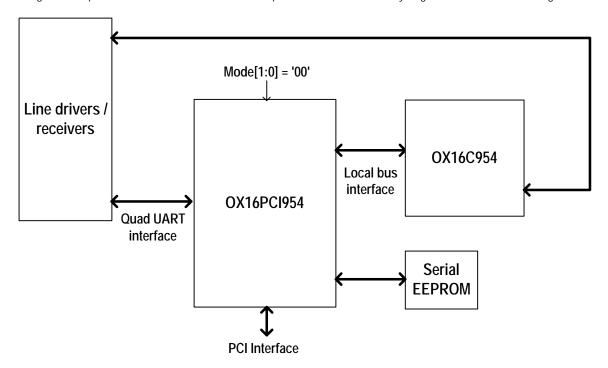

In this configuration, the card designer requires a combination of OX16PCI954, an external Quad UART (recommended OX16C954) and line drivers. Again, the optional EEPROM is recommended to provide maximum flexibility. Figure 17 shows a block diagram.

Figure 17: 8-port serial card.

| OX16PCI954 pins                   | Connection                             |

|-----------------------------------|----------------------------------------|

| Mode[1:0]                         | 00                                     |

| PCI control / data pins           | PCI interface connection               |

| UART signals                      | RS232/422/485 Line drivers             |

| EEPROM signals                    | Serial EEPROM                          |

| LBD[7:0]                          | OX16C954 DB[7:0]                       |

| LBA[2:0]                          | OX16C954 A[2:0]                        |

| LBRD#                             | OX16C954 RD#                           |

| LBWR#                             | OX16C954 WR#                           |

| LBCS[3:0]#                        | OX16C954 CS[3:0]#                      |

| MIO[3:0]                          | OX16C954 INT[3:0] + pull-down resistor |

| MIO[11:4]                         | GND (via 10k resistor)                 |

| Parallel port control / data pins | Parallel port connector                |

**Table 14: Connections required**

## 5.3.1 Operation

The internal UARTs are accessed through BAR0 and BAR1 of function 0, in the same fashion as for the example in Section 5.1.2 (see Table 11). Similarly, the local bus UARTs are accessed through BAR0 and BAR1 of function 1. When the 8-bit local bus is accessed in memory space, AD[9:2] is asserted on LBA[7:0], and the 4kb block is always divided into four chip-select regions. Table 15 shows a register map for the local bus UARTs in I/O and memory space. Note that since the memory space occupies a 4kb block, there are a number of aliases of the UARTs in the allocated region.

| UART<br>address | Offset from Base Address 0 in I/O space (hex) |       |       | Offset from Base Address 1 in memory space (hex) |       |       | y space (hex) |       |

|-----------------|-----------------------------------------------|-------|-------|--------------------------------------------------|-------|-------|---------------|-------|

| (bin)           | UART0                                         | UART1 | UART2 | UART3                                            | UART0 | UART1 | UART2         | UART3 |

| 000             | 00                                            | 80    | 10    | 18                                               | 00    | 400   | 800           | C00   |

| 001             | 01                                            | 09    | 11    | 19                                               | 04    | 404   | 804           | C04   |

| 010             | 02                                            | 0A    | 12    | 1A                                               | 08    | 408   | 808           | C08   |

| 011             | 03                                            | 0B    | 13    | 1B                                               | 0C    | 40C   | 80C           | COC   |

| 100             | 04                                            | 0C    | 14    | 1C                                               | 10    | 410   | 810           | C10   |

| 101             | 05                                            | 0D    | 15    | 1D                                               | 14    | 414   | 814           | C14   |

| 110             | 06                                            | 0E    | 16    | 1E                                               | 18    | 418   | 818           | C18   |

| 111             | 07                                            | 0F    | 17    | 1F                                               | 1C    | 41C   | 81C           | C1C   |

Table 15: Access to Local Bus UARTs in I/O and memory space

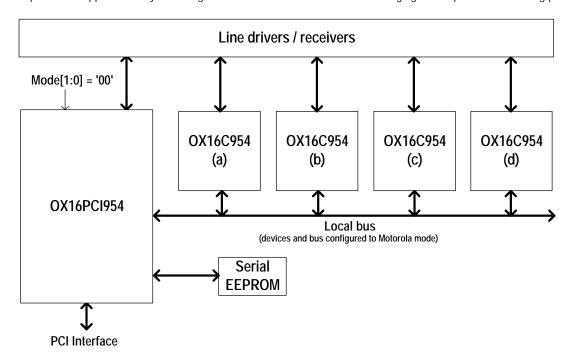

#### 5.4 12,16,20-port cards

Up to four external Quad UARTs can be addressed from the 8-bit local bus, however for glueless implementation of serial cards with port counts higher than 8, the local bus should be configured to operate in Motorola mode; there are only four chip-selects available hence only one can be used for each peripheral device. The I/O space block size will also have to be changed; therefore for these reasons the serial EEPROM is mandatory for these applications. Figure 18 shows a block diagram for a 20-port card, although the example can easily be altered to lower port-count applications by removing the extra OX16C954 devices and changing the respective addressing parameters.

Figure 18: 20-port serial card

| OX16PCI954 pins                   | Connection                          |

|-----------------------------------|-------------------------------------|

| Mode[1:0]                         | 00                                  |

| PCI control / data pins           | PCI interface connection            |

| UART signals                      | RS232/422/485 Line drivers          |

| EEPROM signals                    | Serial EEPROM                       |

| UART_Clk_Out                      | OX16C954 XTLI                       |

| LBD[7:0]                          | OX16C954 DB[7:0]                    |

| LBA[4:0]                          | OX16C954 A[4:0]                     |

| LBRDWR#                           | OX16C954 R/W#                       |

| LBDS0#                            | OX16C954(a) DS#                     |

| LBDS1#                            | OX16C954(b) DS#                     |

| LBDS2#                            | OX16C954(c) DS#                     |

| LBDS3#                            | OX16C954(d) DS#                     |

| MIO0                              | OX16C954(a) IRQ# + pull-up resistor |

| MIO1                              | OX16C954(b) IRQ# + pull-up resistor |

| MIO2                              | OX16C954(c) IRQ# + pull-up resistor |

| MIO3                              | OX16C954(d) IRQ# + pull-up resistor |

| MIO[11:4]                         | GND (via 10k resistor)              |

| Parallel port control / data pins | Parallel port connector             |

**Table 16: Connections required**

Table 17 shows the necessary fields that will need to be reprogrammed by the EEPROM. Other values, such as identification registers, class codes etc. may also be desired.

| OX16PCI954 register | Value | Description                                                         |

|---------------------|-------|---------------------------------------------------------------------|

| LČC[2]              | 1     | Enable UART_CIk_Out                                                 |

| MIC[7:0]            | 55h   | MIO[3:0] = inverting inputs                                         |

| LT1[15:12]          | 4h    | Write-cycle Read-not-Write deassertion = 4 cycles                   |

| LT1[19:16]          | 1h    | Read-cycle Data-strobe assertion = 1 cycle                          |

| LT1[23:20]          | 3h    | Read-cycle Data-strobe deassertion = 3 cycles                       |

| LT1[27:24]          | 1h    | Write-cycle Data-strobe assertion = 1 cycle                         |

| LT1[31:28]          | 3h    | Write-cycle Data-strobe deassertion = 3 cycles                      |

| LT2[22:20]          | 110   | Function 1 I/O space block size= 128 bytes                          |

| LT2[26:23]          | 0011  | Divide into four chip-select regions (Lower-address-CS-decode = A5) |

| LT2[31]             | 1     | Set to Motorola mode                                                |

**Table 17: EEPROM configuration**

### 5.4.1 Operation

The internal UARTs are accessed through BAR0 and BAR1 of function 0, in the same fashion as for the example in Section 5.1.2 (see Table 11). Similarly, the local bus UARTs are accessed through BAR0 and BAR1 of function 1. In this example, the I/O space block size is 128 bytes; for similar applications with fewer ports it simply needs to be large enough to address the requisite number of UARTs. The CS-decode parameter will also need to be adusted to divide up the I/O space block into the correct number of Chip-select regions (one for each external UART chip). When the 8-bit local bus is accessed in memory space, AD[9:2] is asserted on LBA[7:0], and the 4kb block is always divided into four chip-select regions. Table 15 shows a register map for the serial ports in I/O and memory space. Note that since the memory space occupies a 4kb block, there are a number of aliases of the UARTs in the allocated region.

| Port number | Physical device | PCI<br>function | I/O space addressing (hex offset from BAR0) | Memory space addressing (hex offset from BAR1, DWORD aligned) |

|-------------|-----------------|-----------------|---------------------------------------------|---------------------------------------------------------------|

| 0           | Internal UART0  | 0               | 00-07                                       | 00-1C                                                         |

| 1           | Internal UART1  | 0               | 08-0F                                       | 20-3C                                                         |

| 2           | Internal UART2  | 0               | 10-17                                       | 40-5C                                                         |

| 3           | Internal UART3  | 0               | 18-1F                                       | 60-7C                                                         |

| 4           | LB Chip1, UARTO | 1               | 00-07                                       | 00-1C                                                         |

| 5           | LB Chip1, UART1 | 1               | 08-0F                                       | 20-3C                                                         |

| 6           | LB Chip1, UART2 | 1               | 10-17                                       | 40-5C                                                         |

| 7           | LB Chip1, UART3 | 1               | 18-1F                                       | 60-7C                                                         |

| 8           | LB Chip2, UART0 | 1               | 20-27                                       | 400-41C                                                       |

| 9           | LB Chip2, UART1 | 1               | 28-2F                                       | 420-43C                                                       |

| 10          | LB Chip2, UART2 | 1               | 30-37                                       | 440-45C                                                       |

| 11          | LB Chip2, UART3 | 1               | 38-3F                                       | 460-47C                                                       |

| 12          | LB Chip3, UART0 | 1               | 40-47                                       | 800-81C                                                       |

| 13          | LB Chip3, UART1 | 1               | 48-4F                                       | 820-83C                                                       |

| 14          | LB Chip3, UART2 | 1               | 50-57                                       | 840-85C                                                       |

| 15          | LB Chip3, UART3 | 1               | 58-5F                                       | 860-87C                                                       |

| 16          | LB Chip4, UART0 | 1               | 60-67                                       | C00-C1C                                                       |

| 17          | LB Chip4, UART1 | 1               | 68-6F                                       | C20-C3C                                                       |

| 18          | LB Chip4, UART2 | 1               | 70-77                                       | C40-C5C                                                       |

| 19          | LB Chip4, UART3 | 1               | 78-7F                                       | C60-C7C                                                       |

Table 18: Access to serial ports in I/O and memory space

# 6 PCB layout testing

Most pins on the OX16PCl954 can be placed into tristate or input mode, to facilitate PCB testing. This extra function is enabled by applying the following vectors to the pins:

```

Hold TEST=1, MODE[1:0]='10', RST#=0

Sequence 0-1-0 on PCI_CLK and hold 0

```

This application will place all the device's pins in tristate/input mode with the following exceptions:

| Number | Name         | State            |

|--------|--------------|------------------|

| 64     | XTLO         | PERMANENT OUTPUT |

| 71     | UART_CLK_OUT | PERMANENT OUTPUT |

| 123    | LBRST#       | PERMANENT OUTPUT |

| 102    | LBDOUT       | PERMANENT OUTPUT |

| 109    | LBCLK        | PERMANENT OUTPUT |

| 112    | LBWR#        | PERMANENT OUTPUT |

| 113    | LBRD#        | PERMANENT OUTPUT |

| 41     | EE_CK        | PERMANENT OUTPUT |

| 39     | EE_CS        | PERMANENT OUTPUT |

| 40     | EE_DO        | PERMANENT OUTPUT |

# 7 Programming the OX16C95x UART family

The aim of this section is to build up a library of simple functions (written in C) for accessing the internal OX16C950 UARTs and configuring the various features. All the source code presented in this document is available on disk; please see Section 10 at the end of this document for contact information.

## 7.1 Fundamental I/O Operations