# Quad Precision, High-Speed Operational Amplifier

**OP467**

#### **FEATURES**

High Slew Rate – 170 V/ $\mu$ s Wide Bandwidth – 28 MHz Fast Settling Time – <200 ns to 0.01% Low Offset Voltage – <500  $\mu$ V Unity-Gain Stable Low Voltage Operation  $\pm 5$  V to  $\pm 15$  V Low Supply Current – <10 mA Drives Capacitive Loads

#### **APPLICATIONS**

High-Speed Image Display Drivers High Frequency Active Filters Fast Instrumentation Amplifiers High-Speed Detectors Integrators Photo Diode Preamps

#### **GENERAL DESCRIPTION**

The OP467 is a quad, high-speed, precision operational amplifier. It offers the performance of a high-speed op amp combined with the advantages of a precision operational amplifier all in a single package. The OP467 is an ideal choice for applications where, traditionally, more than one op amp was used to achieve this level of speed and precision.

The OP467's internal compensation ensures stable unity-gain operation, and it can drive large capacitive loads without oscillation. With a gain bandwidth product of 28 MHz driving a 30 pF load, output slew rate in excess of 170 V/ $\mu$ s, and settling time to 0.01% in less than 200 ns, the OP467 provides excellent dynamic accuracy in high-speed data-acquisition systems. The channel-to-channel separation is typically 60 dB at 10 MHz.

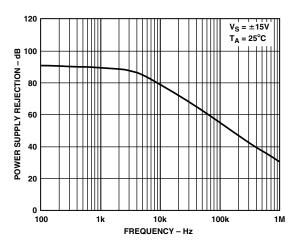

The dc performance of OP467 includes less than 0.5 mV of offset, voltage noise density below 6 nV/ $\sqrt{\text{Hz}}$  and total supply current under 10 mA. Common-mode rejection and power supply rejection ratios are typically 85 dB. PSRR is maintained to better than 40 dB with input frequencies as high as 1 MHz. The low offset and drift plus high speed and low noise, make the OP467 usable in applications such as high-speed detectors and instrumentation.

The OP467 is specified for operation from  $\pm 5$  V to  $\pm 15$  V over the extended industrial temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C) and is available in 14-lead plastic and ceramic DIP, plus 16-lead SOIC and 20-terminal LCC surface mount packages.

Contact your local sales office for MIL-STD-883 data sheet and availability.

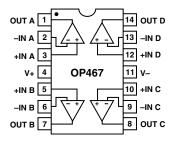

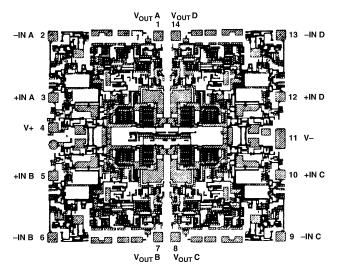

#### PIN CONNECTIONS

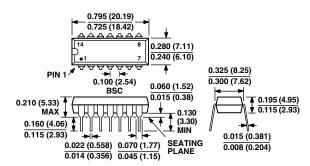

14-Lead Ceramic DIP (Y Suffix) and 14-Lead Plastic DIP (P Suffix)

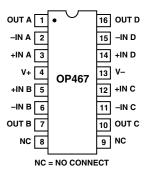

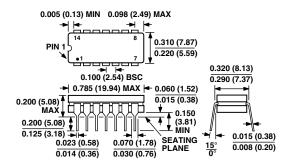

### 16-Lead SOIC (S Suffix)

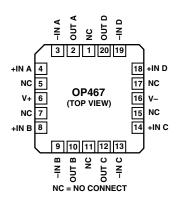

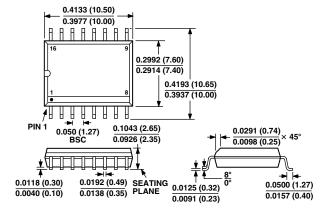

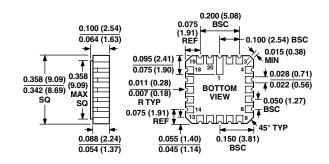

# 20-Terminal LCC (RC Suffix)

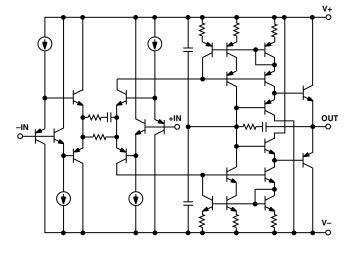

Figure 1. Simplified Schematic

### REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# **OP467—SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS** (@ $V_S = \pm 15.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                                                                    | Symbol                                                                                                   | Conditions                                                                                                                              | Min            | Тур                     | Max             | Unit                                        |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------|-----------------|---------------------------------------------|

| INPUT CHARACTERISTICS Offset Voltage                                         | V <sub>OS</sub>                                                                                          | 400G 4TF 410F0G                                                                                                                         |                | 0.2                     | 0.5             | mV                                          |

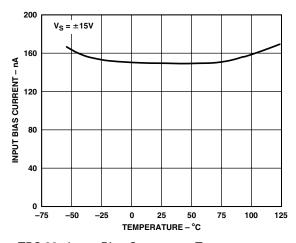

| Input Bias Current                                                           | $I_{B}$                                                                                                  |                                                                                                                                         |                | 150<br>150              | 1<br>600<br>700 | mV<br>nA<br>nA                              |

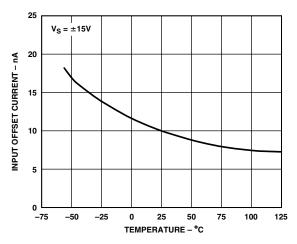

| Input Offset Current                                                         | I <sub>OS</sub>                                                                                          | $V_{CM} = 0 \text{ V}$<br>$V_{CM} = 0 \text{ V}$<br>$V_{CM} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$       |                | 10<br>10                | 100<br>150      | nA<br>nA                                    |

| Common-Mode Rejection                                                        | CMR<br>CMR                                                                                               | $V_{CM} = \pm 12 \text{ V}$<br>$V_{CM} = \pm 12 \text{ V}$ , $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$             | 80<br>80       | 90<br>88                | 130             | dB<br>dB                                    |

| Large Signal Voltage Gain                                                    | A <sub>VO</sub>                                                                                          | $R_{L} = 2 \text{ k}\Omega$<br>$R_{L} = 2 \text{ k}\Omega$ , $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                    | 83<br>77.5     | 86                      |                 | dB<br>dB                                    |

| Offset Voltage Drift<br>Bias Current Drift<br>Long Term Offset Voltage Drift | $\begin{array}{c c} \Delta V_{OS}/\Delta T \\ \Delta I_B/\Delta T \\ \Delta V_{OS}/\Delta T \end{array}$ | Note 1                                                                                                                                  |                | 3.5<br>0.2              | 750             | μV/°C<br>pA/°C<br>μV                        |

| OUTPUT CHARACTERISTICS Output Voltage Swing                                  | Vo                                                                                                       | $R_{L} = 2 \text{ k}\Omega$ $R_{L} = 2 \text{ k}\Omega, -40^{\circ}\text{C} \leq T_{A} \leq +85^{\circ}\text{C}$                        | ±13.0<br>±12.9 | ±13.5<br>±13.12         |                 | V<br>V                                      |

| POWER SUPPLY <sup>2</sup> Power Supply Rejection Ratio                       | PSRR                                                                                                     | $\pm 4.5 \text{ V} \le \text{V}_{\text{S}} = \pm 18 \text{ V}$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ | 96<br>86       | 120<br>115              |                 | dB<br>dB                                    |

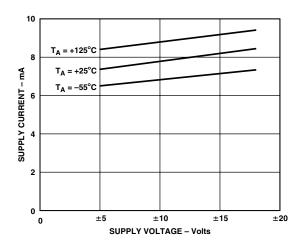

| Supply Current                                                               | $I_{SY}$                                                                                                 | $V_{O} = 0 \text{ V}$<br>$V_{O} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   |                | 8                       | 10<br>13        | mA<br>mA                                    |

| Supply Voltage Range                                                         | $V_S$                                                                                                    |                                                                                                                                         | ±4.5           |                         | ±18             | V                                           |

| DYNAMIC PERFORMANCE<br>Gain Bandwidth Product<br>Slew Rate                   | GBP<br>SR                                                                                                | $A_V = +1, C_L = 30 \text{ pF}$<br>$V_{IN} = 10 \text{ V Step}, R_L = 2 \text{ k}\Omega, C_L = 30 \text{ pF}$<br>$A_V = +1$             | 125            | 28<br>170               |                 | MHz<br>V/μs                                 |

| Full-Power Bandwidth Settling Time Phase Margin                              | $\begin{bmatrix} BW_{\rho} \\ t_{S} \\ \theta_{0} \end{bmatrix}$                                         | $A_{V} = -1$<br>$V_{IN} = 10 \text{ V Step}$<br>To 0.01%, $V_{IN} = 10 \text{ V Step}$                                                  |                | 350<br>2.7<br>200<br>45 |                 | V/µs<br>MHz<br>ns<br>Degrees                |

| Input Capacitance<br>Common Mode<br>Differential                             |                                                                                                          |                                                                                                                                         |                | 2.0<br>1.0              |                 | pF<br>pF                                    |

| NOISE PERFORMANCE Voltage Noise Voltage Noise Density Current Noise Density  | $egin{array}{c} e_{\mathrm{N}} \ \mathrm{p-p} \ e_{\mathrm{N}} \ \mathrm{i}_{\mathrm{N}} \end{array}$    | f = 0.1 Hz to 10 Hz<br>f = 1 kHz<br>f = 1 kHz                                                                                           |                | 0.15<br>6<br>8          |                 | $\mu V p-p \\ nV/\sqrt{Hz} \\ pA/\sqrt{Hz}$ |

Specifications subject to change without notice.

-2-REV. D

NOTES <sup>1</sup>Long-Term Offset Voltage Drift is guaranteed by 1000 hrs. Life test performed on three independent wafer lots at 125 °C, with an LTPD of 1.3.

<sup>&</sup>lt;sup>2</sup>For proper operation the positive supply must be sequenced ON before the negative supply.

# **ELECTRICAL CHARACTERISTICS** (@ $V_s = \pm 5.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                    | Symbol                                           | Conditions                                                                                                           | Min       | Тур   | Max | Unit           |

|------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------|-------|-----|----------------|

| INPUT CHARACTERISTICS        |                                                  |                                                                                                                      |           |       |     |                |

| Offset Voltage               | Vos                                              |                                                                                                                      |           | 0.3   | 0.5 | mV             |

| Ç                            |                                                  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                                                |           |       | 1   | mV             |

| Input Bias Current           | I <sub>B</sub>                                   | $V_{CM} = 0 \text{ V}$                                                                                               |           | 125   | 600 | nA             |

| -                            |                                                  | $V_{CM} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                        |           | 150   | 700 | nA             |

| Input Offset Current         | I <sub>OS</sub>                                  | $V_{CM} = 0 \text{ V}$                                                                                               |           | 20    | 100 | nA             |

| -                            |                                                  | $V_{CM} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                        |           |       | 150 | nA             |

| Common-Mode Rejection        | CMR                                              | $V_{CM} = \pm 2.0 \text{ V}$                                                                                         | 76        | 85    |     | dB             |

| •                            | CMR                                              | $V_{CM} = \pm 2.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                  | 76        | 80    |     | dB             |

| Large Signal Voltage Gain    | A <sub>VO</sub>                                  | $R_L = 2 k\Omega$                                                                                                    | 80        | 83    |     | dB             |

|                              | "0                                               | $R_{L} = 2 \text{ k}\Omega, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   | 74        |       |     | dB             |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$                         |                                                                                                                      |           | 3 5   |     | μV/°C          |

| Bias Current Drift           | $\Delta I_B/\Delta T$                            |                                                                                                                      |           | 0.2   |     | pA/°C          |

| OUTPUT CHARACTERISTICS       | _                                                |                                                                                                                      |           |       |     |                |

| Output Voltage Swing         | $V_{0}$                                          | $R_{\rm L} = 2 \text{ k}\Omega$                                                                                      | ±3.0      | ±3.5  |     | V              |

| Output voltage 5wing         | <b>V</b> O                                       | $R_{L} = 2 \text{ k}\Omega$<br>$R_{L} = 2 \text{ k}\Omega$ , $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ | $\pm 3.0$ | ±3.20 |     | V              |

|                              |                                                  | N <sub>L</sub> = 2 R22, -40 C ≤ 1 <sub>A</sub> ≤ +83 C                                                               | 13.0      | 15.20 |     | V              |

| POWER SUPPLY                 |                                                  |                                                                                                                      |           |       |     |                |

| Power Supply Rejection Ratio | PSRR                                             | $\pm 4.5 \text{ V} \le \text{V}_{\text{S}} = \pm 5.5 \text{ V}$                                                      | 92        | 107   |     | dB             |

|                              |                                                  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                                                | 83        | 105   |     | dB             |

| Supply Current               | $I_{SY}$                                         | $V_O = 0 V$                                                                                                          |           | 8     | 10  | mA             |

|                              |                                                  | $V_{O} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                         |           |       | 12  | mA             |

| DYNAMIC PERFORMANCE          |                                                  |                                                                                                                      |           |       |     |                |

| Gain Bandwidth Product       | GBP                                              | $A_V = +1$                                                                                                           |           | 22    |     | MHz            |

| Slew Rate                    | SR                                               | $V_{IN} = 5 \text{ V Step}, R_L = 2 \text{ k}\Omega, C_L = 39 \text{ pF}$                                            |           | 22    |     | 11112          |

| olew Rate                    |                                                  | $A_{V} = +1$                                                                                                         |           | 90    |     | V/µs           |

|                              |                                                  | $A_{V} = -1$                                                                                                         |           | 90    |     | V/μs           |

| Full-Power Bandwidth         | $BW_0$                                           | $V_{IN} = 5 \text{ V Step}$                                                                                          |           | 2.5   |     | MHz            |

| Settling Time                | r                                                | $V_{IN} = 3 \text{ V Step}$<br>To 0.01%, $V_{IN} = 5 \text{ V Step}$                                                 |           | 280   |     | ns             |

| Phase Margin                 | $\begin{array}{c c} t_S \\ \theta_0 \end{array}$ | 10 0.0170; V <sub>IN</sub> = 3 V Step                                                                                |           | 45    |     | Degrees        |

|                              | 00                                               |                                                                                                                      |           | - IJ  |     | Degrees        |

| NOISE PERFORMANCE            |                                                  |                                                                                                                      |           |       |     |                |

| Voltage Noise                | e <sub>N</sub> p-p                               | f = 0.1  Hz to  10  Hz                                                                                               |           | 0.15  |     | μV p <u>-p</u> |

| Voltage Noise Density        | $e_N$                                            | f = 1  kHz                                                                                                           |           | 7     |     | $nV/\sqrt{Hz}$ |

| Current Noise Density        | $i_N$                                            | f = 1  kHz                                                                                                           |           | 8     |     | pA/√Hz         |

Specifications subject to change without notice.

REV. D –3–

# WAFER TEST LIMITS<sup>1</sup> (@ $V_S = \pm 15.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                        | Symbol      | Conditions                                   | Limit | Unit      |

|----------------------------------|-------------|----------------------------------------------|-------|-----------|

| Offset Voltage                   | Vos         |                                              | ±0.5  | mV max    |

| Input Bias Current               | $I_{\rm B}$ | $V_{CM} = 0 V$                               | 600   | nA max    |

| Input Offset Current             | $I_{OS}$    | $V_{CM} = 0 \text{ V}$                       | 100   | nA max    |

| Input Voltage Range <sup>2</sup> |             |                                              | ±12   | V min/max |

| Common-Mode Rejection Ratio      | CMRR        | $V_{CM} = \pm 12 \text{ V}$                  | 80    | dB min    |

| Power Supply Rejection Ratio     | PSRR        | $V = \pm 4.5 \text{ V to } \pm 18 \text{ V}$ | 96    | dB min    |

| Large Signal Voltage Gain        | $A_{VO}$    | $R_{L} = 2 k\Omega$                          | 83    | dB min    |

| Output Voltage Range             | Vo          | $R_L = 2 k\Omega$                            | ±13.0 | V min     |

| Supply Current                   | $I_{SY}$    | $V_O = 0 \text{ V}, R_L = \infty$            | 10    | mA max    |

#### NOTES

<sup>1</sup>Electrical tests and wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

<sup>2</sup>Guaranteed by CMR test.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage <sup>2</sup> ±18 V               |

|-------------------------------------------------|

| Input Voltage <sup>3</sup> ±18 V                |

| Differential Input Voltage <sup>3</sup> ±26 V   |

| Output Short-Circuit DurationLimited            |

| Storage Temperature Range                       |

| Y, RC Packages65°C to +175°C                    |

| P, S Packages65°C to +150°C                     |

| Operating Temperature Range                     |

| OP467A55°C to +125°C                            |

| OP467G                                          |

| Junction Temperature Range                      |

| Y, RC Packages65°C to +175°C                    |

| P, S Packages65°C to +150°C                     |

| Lead Temperature Range (Soldering, 60 sec)300°C |

| Package Type            | $\theta_A^{-4}$ | $\theta_{ m JC}$ | Unit |

|-------------------------|-----------------|------------------|------|

| 14-Lead Cerdip (Y)      | 94              | 10               | °C/W |

| 14-Lead Plastic DIP (P) | 76              | 33               | °C/W |

| 16-Lead SOIC (S)        | 88              | 23               | °C/W |

| 20-Terminal LCC (RC)    | 78              | 33               | °C/W |

### NOTES

### ORDERING GUIDE

| Model         | Temperature<br>Ranges | Package<br>Descriptions | Package<br>Options |

|---------------|-----------------------|-------------------------|--------------------|

| OP467ARC/883C | –55°C to +125°C       | 20-Terminal LCC         | E-20A              |

| OP467AY/883C  | –55°C to +125°C       | 14-Lead Cerdip          | Q-14               |

| OP467GBC      |                       | DIE                     |                    |

| OP467GP       | –40°C to +85°C        | 14-Lead Plastic DIP     | N-14               |

| OP467GS       | –40°C to +85°C        | 16-Lead SOIC            | R-16               |

| OP467GS-REEL  | –40°C to +85°C        | 16-Lead SOIC            | R-16               |

### DICE CHARACTERISTICS

OP467 Die Size 0.111  $\times$  0.100 inch, 11,100 sq. mils Substrate is Connected to V+, Number of Transistors 165

REV. D

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$<sup>^2\</sup>mbox{For proper operation}$  the positive supply must be sequenced ON before the negative supply.

$<sup>^3</sup>$ For supply voltages less than  $\pm 18$  V, the absolute maximum input voltage is equal to the supply voltage.

$<sup>^4\</sup>theta_{JA}$  is specified for the worst-case conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for cerdip, P-DIP, and LCC packages;  $\theta_{JA}$  is specified for device soldered in circuit board for SOIC package.

# **Typical Performance Characteristics—0P467**

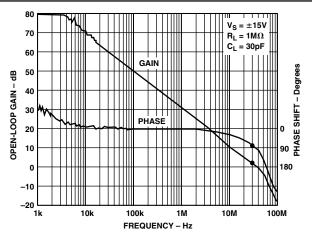

TPC 1. Open-Loop Gain, Phase vs. Frequency

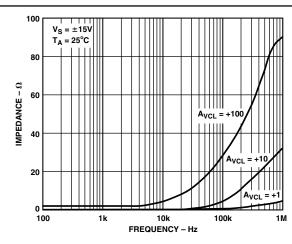

TPC 4. Closed-Loop Output Impedance vs. Frequency

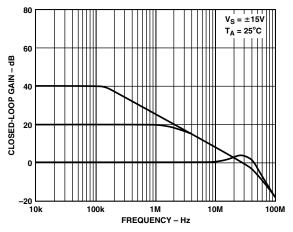

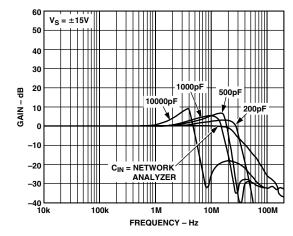

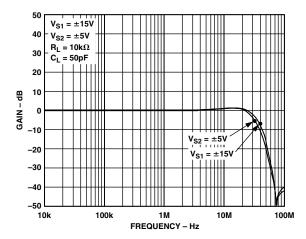

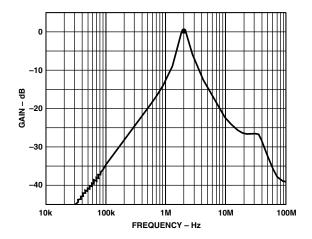

TPC 2. Closed-Loop Gain vs. Frequency

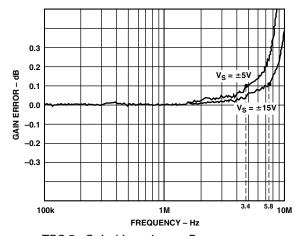

TPC 5. Gain Linearity vs. Frequency

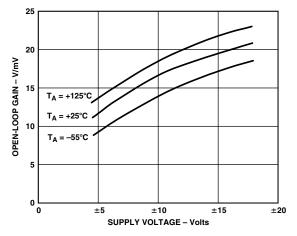

TPC 3. Open-Loop Gain vs. Supply Voltage

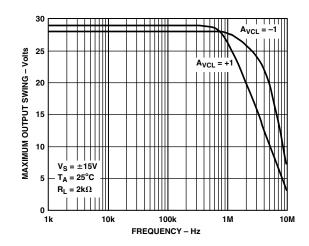

TPC 6. Max  $V_{OUT}$  Swing vs. Frequency

REV. D –5–

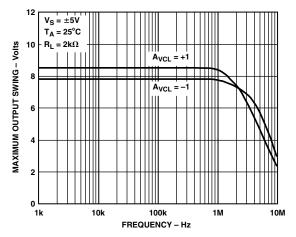

TPC 7. Max  $V_{OUT}$  Swing vs. Frequency

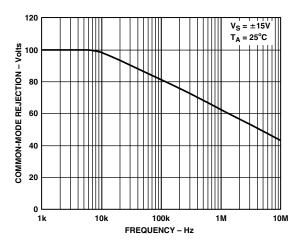

TPC 8. Common-Mode Rejection vs. Frequency

TPC 9. Power-Supply Rejection vs. Frequency

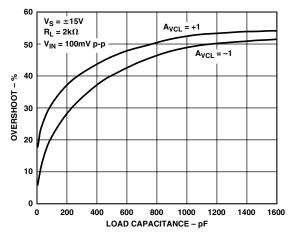

TPC 10. Small Signal Overshoot vs. Load Capacitance

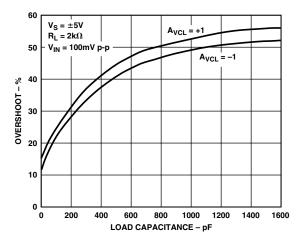

TPC 11. Small Signal Overshoot vs. Load Capacitance

TPC 12. Noninverting Gain vs. Capacitive Loads

–6– REV. D

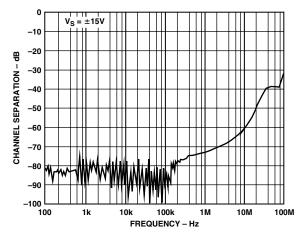

TPC 13. Channel Separation vs. Frequency

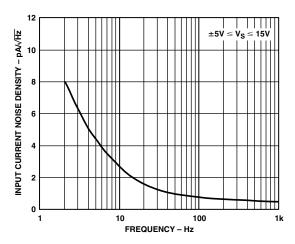

TPC 14. Input Current Noise Density vs. Frequency

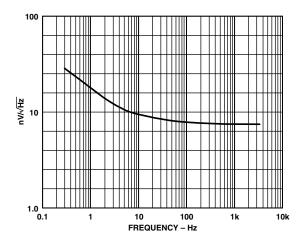

TPC 15. Voltage Noise Density vs. Frequency

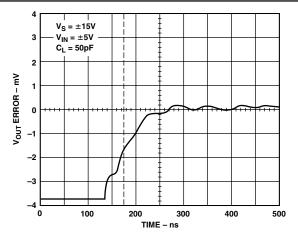

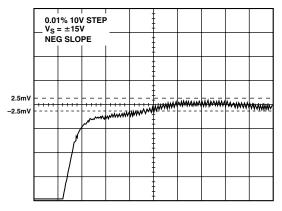

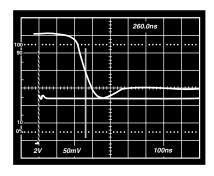

TPC 16. Settling Time, Negative Edge

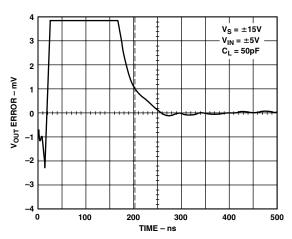

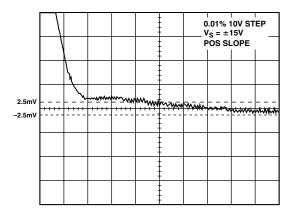

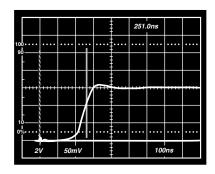

TPC 17. Settling Time, Positive Edge

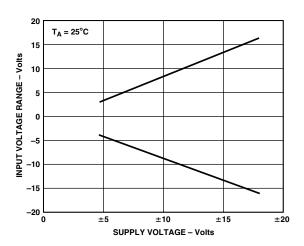

TPC 18. Input Voltage Range vs. Supply Voltage

REV. D -7-

TPC 19. Noninverting Gain vs. Supply Voltage

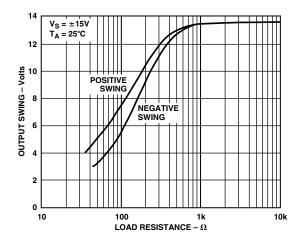

TPC 20. Output Swing vs. Load Resistance

TPC 21. Output Swing vs. Load Resistance

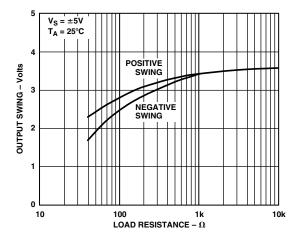

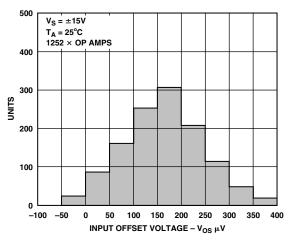

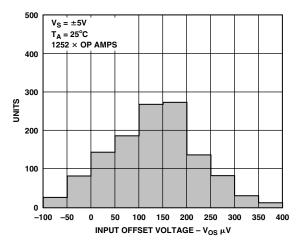

TPC 22. Input Offset Voltage Distribution

TPC 23. Input Offset Voltage Distribution

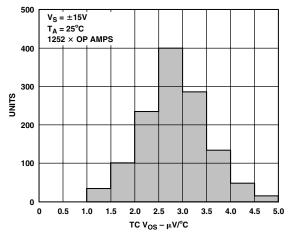

TPC 24. TC V<sub>OS</sub> Distribution

–8– REV. D

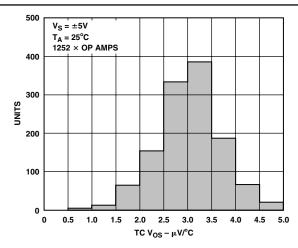

TPC 25. TC V<sub>OS</sub> Distribution

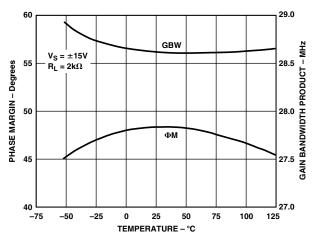

TPC 26. Phase Margin and Gain Bandwidth vs. Temperature

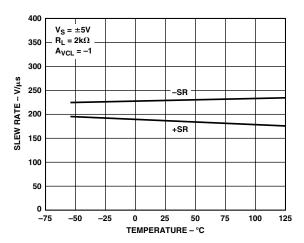

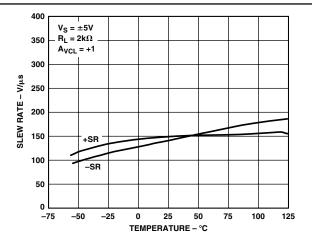

TPC 27. Slew Rate vs. Temperature

TPC 28. Slew Rate vs. Temperature

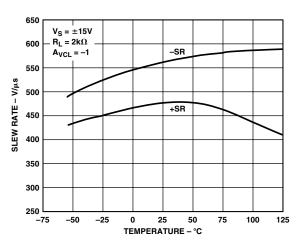

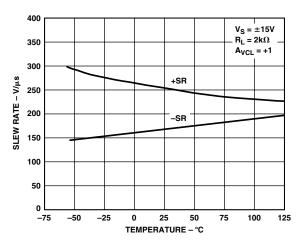

TPC 29. Slew Rate vs. Temperature

TPC 30. Slew Rate vs. Temperature

REV. D –9–

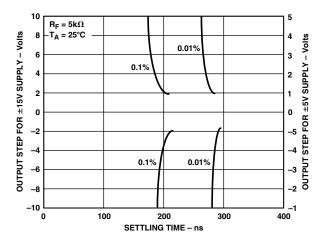

TPC 31. Settling Time vs. Output Step

TPC 32. Supply Current vs. Supply Voltage

TPC 33. Input Bias Current vs. Temperature

TPC 34. Input Offset Current vs. Temperature

# APPLICATIONS INFORMATION OUTPUT SHORT-CIRCUIT PERFORMANCE

To achieve a wide bandwidth and high slew rate, the OP467 output is *not* short circuit protected. Shorting the output to ground or to the supplies may destroy the device.

For safe operation, the output load current should be limited so that the junction temperature does not exceed the absolute maximum junction temperature.

To calculate the maximum internal power dissipation, the following formula can be used:

$$P_D = \frac{T_{J \text{ max}} - T_{A}}{\theta_{JA}}$$

where  $T_J$  and  $T_A$  are junction and ambient temperatures respectively,  $P_D$  is device internal power dissipation, and  $\theta_{JA}$  is packaged device thermal resistance given in the data sheet.

#### **UNUSED AMPLIFIERS**

It is recommended that any unused amplifiers in a quad package be connected as a unity gain follower with a 1 k $\Omega$  feedback resistor with noninverting input tied to the ground plain.

### PRINTED CIRCUIT BOARD LAYOUT CONSIDERATIONS

Satisfactory performance of a high-speed op amp largely depends on a good PC layout. To achieve the best dynamic performance, following high frequency layout technique is recommended.

### **GROUNDING**

A good ground plain is essential to achieve the optimum performance in high-speed applications. It can significantly reduce the undesirable effects of ground loops and IR drops by providing a low impedance reference point. Best results are obtained with a multilayer board design with one layer assigned to ground plain. To maintain a continuous and low impedance ground, avoid running any traces on this layer.

### POWER SUPPLY CONSIDERATIONS

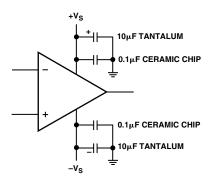

For proper operation the positive supply must be sequenced ON before the negative supply. All users should take steps to ensure this. In high frequency circuits, device lead length introduces an inductance in series with the circuit. This inductance, combined with stray capacitance, forms a high frequency resonance circuit. Poles generated by these circuits will cause gain peaking and additional phase shift, reducing the op amp's phase margin and leading to an unstable operation.

A practical solution to this problem is to reduce the resonance frequency low enough to take advantage of the amplifier's power supply rejection.

This is easily done by placing capacitors across the supply line and the ground plain as close as possible to the device pin. Since capacitors also have internal parasitic components, such as stray inductance, selecting the right capacitor is important. To be effective, they should have low impedance over the frequency range of interest. Tantalum capacitors are an excellent choice for their high capacitance/size ratio, but their ESR (Effective Series Resistance) increases with frequency making them less

effective. On the other hand, ceramic chip capacitors have excellent ESR and ESL (Effective Series Inductance) performance at higher frequencies, and because of their small size, they can be placed very close to the device pin, further reducing the stray inductance. Best results are achieved by using a combination of these two capacitors. A 5  $\mu F$ –10  $\mu F$  tantalum parallel with a 0.1  $\mu F$  ceramic chip caps are recommended. If additional isolation from high frequency resonances of the power supply is needed, a ferrite bead should be placed in series with the supply lines between the bypass caps and the power supply. A word of caution, addition of the ferrite bead will introduce a new pole and zero to frequency response of the circuit and could cause unstable operation if it is not selected properly.

Figure 2. Recommended Power Supply Bypass

#### SIGNAL CONSIDERATIONS

Input and output traces need special attention to assure a minimum stray capacitance. Input nodes are very sensitive to capacitive reactance, particularly when connected to a high impedance circuit. Stray capacitance can inject undesirable signals from a noisy line into a high impedance input. Protect high impedance input traces by providing guard traces around them. This will also improve the channel separation significantly.

Additionally, any stray capacitance in parallel with the op amp's input capacitance generates a pole in the frequency response of the circuit. The additional phase shift caused by this pole will reduce the circuit's gain margin. If this pole is within the gain range of the op amp, it will cause unstable performance. To reduce these undesirable effects, use the lowest impedance where possible. Lowering the impedance at this node places the poles at a higher frequency, far above the gain range of the amplifier. Stray capacitance on the PC board can be reduced by making the traces narrow and as short as possible. Further reduction can be realized by choosing smaller pad size, increasing the spacing between the traces, and using PC board material with a low dielectric constant insulator (Dielectric Constant of some common insulators: air = 1, Teflon® = 2.2, and FR4 = 4.7; with air being an ideal insulator).

Removing segments of the ground plain directly under the input and output pads is recommended.

Outputs of high-speed amplifiers are very sensitive to capacitive loads. A capacitive load will introduce a pair of pole and zero to the circuit's frequency response, reducing the phase margin, leading to unstable operation or oscillation.

REV. D –11–

Generally, it is a good design practice to isolate the amplifier's output from any capacitive load by placing a resistor between the amplifier's output and the rest of the circuits. A series resistor of  $10~\Omega$  to  $100~\Omega$  is normally sufficient to isolate the output from a capacitive load.

The OP467 is internally compensated to provide stable operation, and is capable of driving large capacitive loads without oscillation.

Sockets are not recommended since they increase the lead inductance/capacitance and reduce the power dissipation of the package by increasing the leads' thermal resistance. If sockets must be used, use Teflon or pin sockets with the shortest possible leads.

### PHASE REVERSAL

The OP467 is immune to phase reversal; its inputs can exceed the supply rails by a diode drop without any phase reversal.

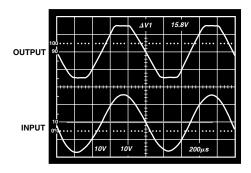

Figure 3. No Phase Reversal  $(A_V = +1)$

### **SATURATION RECOVERY TIME**

The OP467 has a fast and symmetrical recovery time from either rail. This feature is very useful in applications such as high-speed instrumentation and measurement circuits, where the amplifier is frequently exposed to large signals that overload the amplifier.

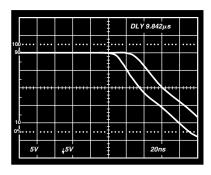

Figure 4. Saturation Recovery Time, Positive Rail

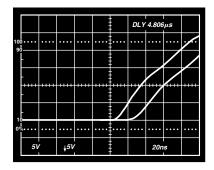

Figure 5. Saturation Recovery Time, Negative Rail

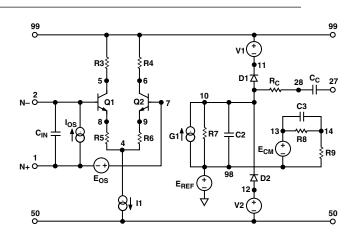

#### **HIGH-SPEED INSTRUMENTATION AMPLIFIER**

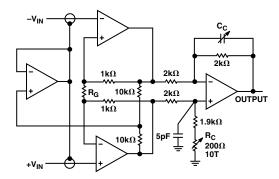

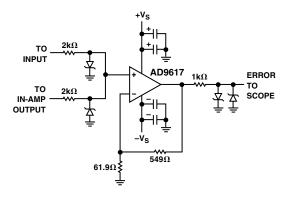

The OP467 performance lends itself to a variety of high-speed applications, including high-speed precision instrumentation amplifiers. Figure 6 represents a circuit commonly used for data acquisition, CCD imaging, and other high-speed applications.

Circuit gain is set by  $R_G$ . A 2  $k\Omega$  resistor will set the circuit gain to 2; for unity gain, remove  $R_G$ . For any other gain settings use the following formula:

$$G = 2/R_G$$

Resistor Value is in  $k\Omega$

$R_{\rm C}$  is used for adjusting the dc common-mode rejection, and  $C_{\rm C}$  is used for ac common-mode rejection adjustments.

Figure 6. A High-Speed Instrumentation Amplifier

Figure 7. Instrumentation Amplifier Settling Time to 0.01% for a 10 V Step Input (Negative Slope)

–12– REV. D

Figure 8. Instrumentation Amplifier Settling Time to 0.01% for a 10 V Step Input (Positive Slope)

Figure 9. Settling Time Measurement Circuit

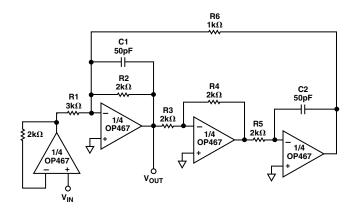

### 2 MHz BIQUAD BANDPASS FILTER

The circuit in Figure 10 is commonly used in medical imaging ultrasound receivers. The 30 MHz bandwidth is sufficient to accurately produce the 2 MHz center frequency, as the measured response shows in Figure 11. When the op amp's bandwidth is too close to the filter's center frequency, the amplifier's internal phase shift causes excess phase shift at 2 MHz, which alters the filter's response. In fact, if the chosen op amp has a bandwidth close to 2 MHz, the combined phase shift of the three op amps will cause the loop to oscillate.

Careful consideration must be given to the layout of this circuit as with any other high-speed circuit.

If the phase shift introduced by the layout is large enough, it could alter the circuit performance, or worse, it will oscillate.

Figure 10. 2 MHz Biquad Filter

Figure 11. Biquad Filter Response

REV. D –13–

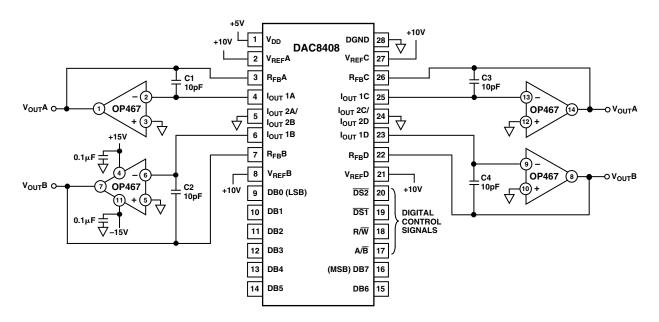

Figure 12. Quad DAC Unipolar Operation

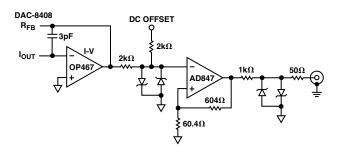

#### **FAST I-TO-V CONVERTER**

The fast slew rate and fast settling time of the OP467 are well suited to the fast buffers and I-to-V converters used in variety of applications. The circuit in Figure 12 is a unipolar quad D/A converter consisting of only two ICs. The current output of the DAC8408 is converted to a voltage by the OP467 configured as an I-to-V converter. This circuit is capable of settling to 0.1% within 200 ns. Figures 13 and 14 show the full-scale settling time of the outputs. To obtain reliable circuit performance, keep the traces from the DAC's I<sub>OUT</sub> to the inverting inputs of the OP467 short to minimize parasitic capacitance.

Figure 13. Voltage Output Settling Time

Figure 14. Voltage Output Settling Time

Figure 15. DAC V<sub>OUT</sub> Settling Time Circuit

–14– REV. D

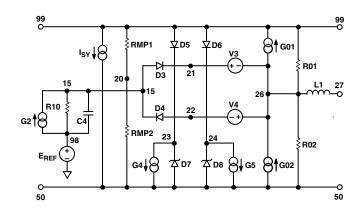

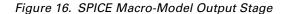

#### **OP467 SPICE MACRO-MODEL** \* COMMON-MODE STAGE WITH ZERO AT 1.26 kHz \* Node assignments noninverting input inverting input **ECM** 98 POLY (2) (1,20) (2,20) 0 0 . 5 0 . 5 13 R8 13 14 positive supply 1E6 negative supply R9 14 98 25.119 output C3 13 14 126.721E-12 . SUBCKT OP467 99 50 27 2 \* POLE AT 400E6 \* INPUT STAGE R10 15 98 1E6 C4 15 98 0.398E-15 Ι1 10E-3 G2 98 4 50 15 (10,20) 1E-6 CIN 1 2 1E-12 IOS 1 2 5E-9 \* OUTPUT STAGE 5 2 8 QN Q1 7 Q2 6 9 QN **ISY** 99 50 -8.183E-3 99 R3 5 185.681 99 96.429E3 RMP1 20 R4 99 6 185.681 RMP2 20 96.429E3 50 R5 8 4 180.508 99 200 RO1 26 9 R6 4 180.508 RO2 26 200 50 7 **EOS** POLY (1) (14,20) 50E-6 1 1 L1 26 27 1E-798 **EREF** 0 (20,0) 1 GO<sub>1</sub> 26 99 (99,15) 5E-3 GO<sub>2</sub> 50 26 (15,50) 5E-3 \* GAIN STAGE AND DOMINANT POLE AT 1.5 kHz G4 23 50 (15,26) 5E-3 G5 24 50 (26,15) 5E-3 R7 21 10 98 3.714E6 V3 26 50 C2 10 98 28.571E-12 V426 22 50 (5,6) 5.386E-3 G1 98 10 D3 15 21 DX V1 99 D4 22 DX 11 1.6 15 V2 12 50 D5 99 23 DX1.6 99 10 24 DX D111 DX D6 D2 12 DX D750 23 DY 10 RC 10 28 1.4E3 D8 50 24 DY CC 28 27 12E-12 \* MODELS USED . MODEL QN NPN (BF=33.333E3) . MODEL DX D . MODEL DY D (BV=50)

. ENDS OP467

Figure 17. SPICE Macro-Model Input and Gain Stage

REV. D –15–

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### 14-Lead Plastic DIP (P Suffix) (N-14)

### 14-Lead Cerdip (Y Suffix) (Q-14)

### 16-Lead SOIC (S Suffix) (R-16)

### 20-Terminal Leadless Ceramic Chip Carrier (RC Suffix) (E-20A)

## **OP467**—Revision History

| Location                                     | Page |

|----------------------------------------------|------|

| Data Sheet changed from REV. C to REV. D.    |      |

| Footnote added to POWER SUPPLY               | 2    |

| Footnote added to MAX RATINGS                | 4    |

| Edits to POWER SUPPLY CONSIDERATIONS section | 11   |

-16-