## Description

The OV8610 (color) and OV8110 (black and white) CMOS Image sensors are single-chip video/imaging camera devices designed to provide a high level of functionality in a single, small-footprint package. The devices incorporate an 800 x 600 image array capable of operating at up to 60 frames per second. Proprietary sensor technology utilizes advanced algorithms to cancel Fixed Pattern Noise (FPN), eliminate smearing, and drastically reduce blooming. All required camera functions including exposure control, gamma, gain, white balance, color matrix, color saturation, hue control, windowing, and more, are programmable through the serial SCCB interface. The device can be programmed to provide image output in different 8-bit or 16-bit digital formats.

#### **Features**

- 480,000 pixels, 1/3" lens, SVGA/QSVGA format

- Data output formats include ITU-601 and ITU-656

- Choice of progressive scan/interlaced read

- Wide dynamic range, anti-blooming, zero smearing

- Electronic exposure/gain/white balance control

- Image Controls brightness, contrast, gamma, saturation, sharpness, windowing, hue, etc.

- Internal & external synchronization

- Line exposure option

- 3.3-Volt operation, low power dissipation

- < 30 mA active power at 30FPS with 10 mA load

- < 10 μA in power-down mode

- Built in Gamma correction (0.45/0.55/1.00)

- SCCB programmable:

- Color saturation, brightness, hue, white balance, exposure time, gain, etc.

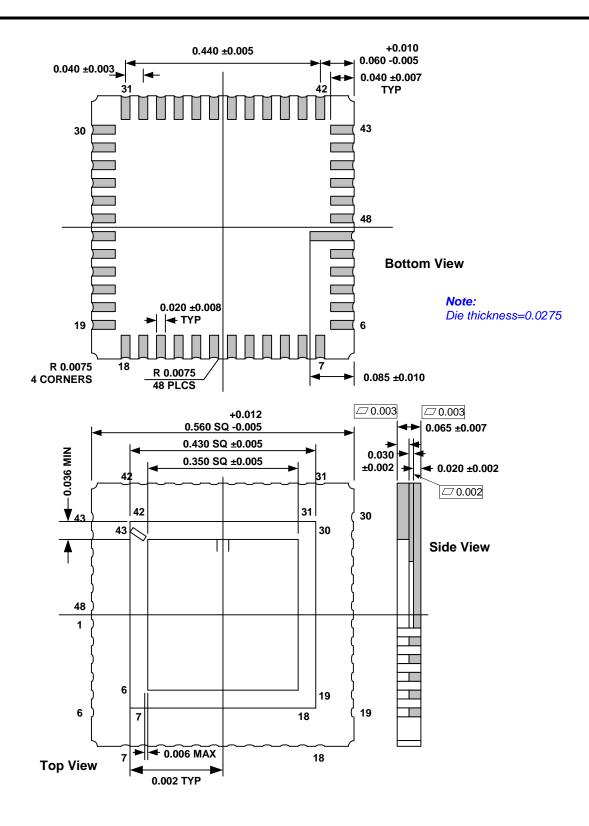

## **Ordering Information**

| Product | Package                         | Description                                               |

|---------|---------------------------------|-----------------------------------------------------------|

| OV8610  | 48 LCC<br>0.560 in <sup>2</sup> | COLOR, SVGA,<br>QSVGA, QCIF<br>Digital, SCCB<br>interface |

| OV8110  | 48 LCC<br>0.560 in <sup>2</sup> | SVGA, QSVGA,<br>QCIF, Digital,<br>SCCB interface          |

## **Applications**

- . Cell Phone

- . Digital Still Camera

- . PC Multimedia

- . PDAs

- . Machine Vision

## **Key Specifications**

| Active Array Element |                                |

|----------------------|--------------------------------|

| (SVGA)               | 800x600                        |

| (QSVGA)              | (400x300)                      |

| Pixel Size           | 6.2μm x 6.2μm                  |

| Image Area           | 4.96mm x 3.72mm                |

| Max Frames/Sec       | Up to 120 FPS for QSVGA        |

| Electronics Exposure | Up to 648:1 (for selected FPS) |

| Scan Mode            | Progressive or Interlace       |

| Gamma Correction     | 0.45/0.55/1.0                  |

| Min. Illumination    | OV8610 < 3 lux @ f1.2          |

| (3000K)              | OV8110 < 0.8 lux @ f1.2        |

| S/N Ratio            | > 48 dB                        |

|                      | (AGC off, Gamma=1)             |

| FPN                  | < 0.03% V <sub>PP</sub>        |

| Dark Current         | < .2 nA/cm <sup>2</sup>        |

| Dynamic Range        | > 72 dB                        |

| Power Supply         | 3.0-3.6VDC                     |

| Power Requirements   | < 30mA Active (w/10mA load)    |

| •                    | < 10μA Standby                 |

| Package              | 48 pin LCC                     |

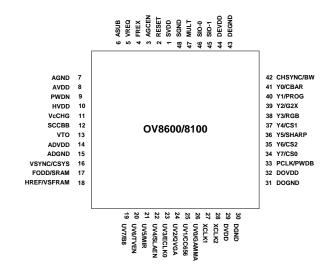

Figure 1. OV8610/OV8110 Pin Diagram

# **Pin Description**

## **Table 1. Pin Description**

| Pin No. | Name                 | Pin Type                | Function/Description                                                                                                                                                                                                              |

|---------|----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01      | SVDD                 | V <sub>IN</sub>         | Array power (+3.3VDC). Bypass to ground with a 0.1μF capacitor.                                                                                                                                                                   |

| 02      | RESET                | Function<br>(Default=0) | Chip reset, active high. Resets all control registers to factory defaults.                                                                                                                                                        |

| 03      | AGCEN                | Function<br>(Default=0) | Automatic Gain Control (AGC) selection  "0" – Disable AGC  "1" – Enable AGC  Note: This function is disabled when OV8610/OV8110 sensor is configured in SCCB low mode. In SCCB low mode this pin is an SCCB chip select function. |

| 04      | FREX                 | Function<br>(Default=0) | Frame exposure control "0" – Disables frame exposure control "1" – Enables frame exposure control                                                                                                                                 |

| 05      | VREQ                 | V <sub>REF</sub> (1.5V) | Array reference. Connect to ground with a 0.1μF (min.) capacitor.                                                                                                                                                                 |

| 06      | ASUB                 | V <sub>IN</sub>         | Analog substrate voltage                                                                                                                                                                                                          |

| 07      | AGND                 | V <sub>IN</sub>         | Analog ground                                                                                                                                                                                                                     |

| 08      | AVDD                 | V <sub>IN</sub>         | Analog power supply (+3.3VDC). Bypass to ground with a 0.1µF capacitor.                                                                                                                                                           |

| 09      | PWDN                 | Function<br>(Default=0) | Power-down mode selection.  "0" – Operating mode  "1" – Power-down mode                                                                                                                                                           |

| 10      | HVDD                 | V <sub>REF</sub> (5.0V) | Charge pump out voltage. Doubler must be enabled.                                                                                                                                                                                 |

| 11      | V <sub>C</sub> CHG   | V <sub>REF</sub> (2.7V) | Internal voltage reference. Bypass to ground with a 0.1µF capacitor.                                                                                                                                                              |

| 12      | SCCBB                | Function<br>(Default=0) | SCCB enable selection.  "0" – Selects internal register setting control and enables SCCB interface "1" – Enables I/O input pin power on latch setting control                                                                     |

| 13      | VTO                  | 0                       | B&W CCIR analog composite signal output—for test purposes only                                                                                                                                                                    |

| 14      | ADVDD                | V <sub>IN</sub>         | Analog power supply (+3.3VDC). Bypass to ground with a 0.1μF capacitor.                                                                                                                                                           |

| 15      | ADGND                | V <sub>IN</sub>         | Analog signal ground                                                                                                                                                                                                              |

| 16      | VSYNC/CSYS           | 0                       | Vertical sync output. At power-up, read as CSYS.                                                                                                                                                                                  |

| 17      | FODD/SRAM            | 0                       | Field ID FODD output. At power-up, read as SRAM.                                                                                                                                                                                  |

| 18      | HREF/VSFRAM          | 0                       | HREF output. At power-up, read as VSFRAM                                                                                                                                                                                          |

| 19      | *UV7/B8              | 0                       | Bit 7 of U video component output. At power-up, sampled as B8.                                                                                                                                                                    |

| 20      | *UV6/TVEN            | 0                       | Bit 6 of U video component output. At power-up, sampled as TVEN.                                                                                                                                                                  |

| 21      | <sup>*</sup> UV5/MIR | 0                       | Bit 5 of U video component output. At power-up, sampled as MIR.                                                                                                                                                                   |

| 22      | *UV4/SLAEN           | 0                       | Bit 4 of U video component output. At power-up, sampled as SLAEN.                                                                                                                                                                 |

| 23      | *UV3/ECLK0           | 0                       | Bit 3 of U video component output. At power-up, samples as ECLKO.                                                                                                                                                                 |

| 24      | *UV2/QSVGA           | 0                       | Bit 2 of U video component output. At power-up, sampled as QSVGA.                                                                                                                                                                 |

| 25      | *UV1/CC656           | 0                       | Bit 1 of U video component output. At power-up, sampled as CC656.                                                                                                                                                                 |

| 26      | *UV0/GAMMA           | 0                       | Bit 0 of U video component output. At power-up, sampled as GAMMA.                                                                                                                                                                 |

| 27      | XCLK1                | 1                       | Crystal clock input                                                                                                                                                                                                               |

| 28      | XCLK2                | 0                       | Crystal clock output                                                                                                                                                                                                              |

| 29      | DVDD                 | V <sub>IN</sub>         | Digital power supply (+3.3VDC). Bypass to ground with a 0.1μF capacitor.                                                                                                                                                          |

| 30      | DGND                 | V <sub>IN</sub>         | Digital ground                                                                                                                                                                                                                    |

| 31      | DOGND                | V <sub>IN</sub>         | Digital interface output buffer ground                                                                                                                                                                                            |

| 32      | DOVDD                | V <sub>IN</sub>         | Digital output buffer supply (+3.3VDC). Bypass to ground with a 0.1μF capacitor.                                                                                                                                                  |

| 33      | PCLK/PWDB            | 0                       | PCLK output. At power-up sampled as charge pump enable.                                                                                                                                                                           |

| 34      | Y7                   | 0                       | Bit 7 of Y video component output                                                                                                                                                                                                 |

| 35      | Y6                   | 0                       | Bit 6 of Y video component output                                                                                                                                                                                                 |

| 36      | Y5/SHARP             | 0                       | Bit 5 of Y video component output. At power-up, sampled as SHARP.                                                                                                                                                                 |

| 37      | Y4                   | 0                       | Bit 4 of Y video component output                                                                                                                                                                                                 |

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A.

Tel: (408) 733-3030 Fax: (408) 733-3061

# Advanced Information Preliminary OV8610/OV8110

# OV8610 SINGLE-CHIP CMOS VGA COLOR DIGITAL CAMERA OV8110 SINGLE-CHIP CMOS VGA B&W DIGITAL CAMERA

| Pin No. | Name      | Pin Type        | Function/Description                                                     |

|---------|-----------|-----------------|--------------------------------------------------------------------------|

| 38      | Y3/RGB    | 0               | Bit 3 of Y video component output. At power-up, sampled as RGB.          |

| 39      | Y2/G2X    | 0               | Bit 2 of Y video component output. At power-up, sampled as G2X.          |

| 40      | Y1/PROG   | 0               | Bit 1 of Y video component output. At power-up, samples as PROG          |

| 41      | Y0/CBAR   | 0               | Bit 0 of Y video component output. At power-up, sampled as CBAR.         |

| 42      | CHSYNC/BW | 0               | CHSYNC output. At power-up, sampled as BW.                               |

| 43      | DEGND     | V <sub>IN</sub> | Decoder ground                                                           |

| 44      | DEVDD     | V <sub>IN</sub> | Decoder power supply (+3.3VDC). Bypass to ground with a 0.1μF capacitor. |

| 45      | SIO-1     | I               | SCCB serial interface clock input                                        |

| 46      | SIO-0     | I/O             | SCCB serial interface data input and output                              |

| 47      | Reserved  | Function        |                                                                          |

|         |           | (Default=0)     |                                                                          |

| 48      | SGND      | V <sub>IN</sub> | Array ground                                                             |

<sup>\*</sup> Note: Output is not available on the OV8110 sensor and one-port mode for OV8610.

All I/O latch input pins are effective only when SCCB pin is high, otherwise all pin functions are regulated by the register settings.

Legend: (I=Input), (O=Output), (I/O=Bi-directional), (P=Power), (A=Analog)

## **Electrical and Mechanical Characteristics**

#### **Table 2. General Characteristics**

| Descriptions          | Min | Max | Units |

|-----------------------|-----|-----|-------|

| Operating temperature | 0   | 40  | °C    |

| Storage temperature   | -40 | 125 | °C    |

| Operating humidity    | TBD | TBD |       |

| Storage humidity      | TBD | TBD |       |

## Table 3. DC Characteristics (0°C ≤ TA ≤ 85°C, Voltages referenced to GND)

| Symbol           | Descriptions                                                                                        | Max                  | Тур | Min  | Units |

|------------------|-----------------------------------------------------------------------------------------------------|----------------------|-----|------|-------|

| Supply           |                                                                                                     | -                    |     | -    | -     |

| $V_{DD1}$        | Supply voltage (DEVDD, ADVDD, AVDD, DVDD, DOVDD)                                                    | 3.6                  | 3.3 | 3.0  | V     |

| I <sub>DD1</sub> | Supply current<br>(@ 30 fps and 3.3V digital I/O with 25pF plus ITTL loading on<br>16-bit data bus) | 35                   | 30  |      | mA    |

| $I_{DD3}$        | Standby supply current                                                                              | 10                   | 8   |      | μΑ    |

| Digital Inp      | uts                                                                                                 |                      |     |      |       |

| V <sub>IL</sub>  | Input voltage LOW                                                                                   | 0.8                  |     |      | V     |

| $V_{IH}$         | Input voltage HIGH                                                                                  |                      |     | 2    | V     |

| C <sub>IN</sub>  | Input capacitance                                                                                   | 10                   |     |      | PF    |

| Digital Out      | puts (standard loading 25pF, 1.2KΩ to 3V)                                                           |                      |     |      |       |

| V <sub>OH</sub>  | Output voltage HIGH                                                                                 |                      |     | 2.4  | V     |

| V <sub>OL</sub>  | Output voltage LOW                                                                                  | 0.6                  |     |      | V     |

| SCCB Inpu        | it                                                                                                  |                      |     |      |       |

| V <sub>IL</sub>  | SIO-0 and SIO-1 (V <sub>DD2</sub> =5V)                                                              | 1.5                  |     | -0.5 | V     |

| V <sub>IH</sub>  | SIO-0 and SIO-1 (V <sub>DD2</sub> =5V)                                                              | V <sub>DD</sub> +0.5 | 3.3 | 3.0  | V     |

| V <sub>IL</sub>  | SIO-0 and SIO-1 (V <sub>DD2</sub> =3V)                                                              | 1                    | 0   | -0.5 | V     |

| V <sub>IH</sub>  | SIO-0 and SIO-1 (V <sub>DD2</sub> =3V)                                                              | V <sub>DD</sub> +0.5 | 3   | 2.5  | V     |

## Table 4. AC Characteristics (T<sub>A</sub>=25°C, V<sub>DD</sub>=3V)

| Symbol           | Descriptions                                  | Max | Тур | Min | Units |  |  |

|------------------|-----------------------------------------------|-----|-----|-----|-------|--|--|

| RGB/YCrCb Output |                                               |     |     |     |       |  |  |

| I <sub>SO</sub>  | Maximum sourcing current                      |     | 15  |     | mA    |  |  |

| $V_{Y}$          | DC level at zero signal                       |     | 1.2 |     | V     |  |  |

|                  | Y <sub>PP</sub> 100% amplitude (without sync) |     | 1   |     |       |  |  |

|                  | Sync amplitude                                |     | 0.4 |     |       |  |  |

| ADC Parar        | neters                                        |     |     |     |       |  |  |

| В                | Analog bandwidth                              |     | TBD |     | MHz   |  |  |

| $\Phi_{DIFF}$    |                                               |     |     |     |       |  |  |

| DLE              | DC differential linearity error               |     | 0.5 |     | LSB   |  |  |

| ILE              | DC integral linearity error                   |     | 1   |     | LSB   |  |  |

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A.

Tel: (408) 733-3030 Fax: (408) 733-3061

## **Table 5. Timing Characteristics**

| Symbol                          | Descriptions                         | Max      | Тур | Min | Units |

|---------------------------------|--------------------------------------|----------|-----|-----|-------|

| Oscillator                      | and Clock Input                      |          |     |     |       |

| fosc                            | Frequency (XCLK1)                    | 40       | 20  | 10  | MHz   |

| t <sub>r</sub> , t <sub>f</sub> | Clock input rise/fall time           | 5        |     |     | ns    |

|                                 | Clock input duty cycle               | 55       | 50  | 45  | %     |

| SCCB Tim                        | ing (400Kbit/s)                      | <u> </u> |     |     |       |

| t <sub>BUF</sub>                | Bus free time between STOP and START |          |     | 1.3 | ms    |

| t <sub>HD:SAT</sub>             | SIO-D change after START status      |          |     | 0.6 | μs    |

| t <sub>LOW</sub>                | SIO-D low period                     |          |     | 1.3 | μs    |

| t <sub>HIGH</sub>               | SIO-D high period                    |          |     | 0.6 | μs    |

| t <sub>HD:DAT</sub>             | Data hold time                       |          |     | 0   | μs    |

| t <sub>SU:DAT</sub>             | Data setup time                      |          |     | 0.1 | μs    |

| t <sub>SU:STP</sub>             | Setup time for STOP status           |          |     | 0.6 | μs    |

| Digital Tin                     | ning                                 |          |     |     | •     |

| t <sub>PCLK</sub>               | PCLK period (16-bit operation)       |          | 50  |     | ns    |

| t <sub>PCLK</sub>               | PCLK period (8-bit operation)        |          | 50  |     | ns    |

| t <sub>r</sub> , t <sub>f</sub> | PCLK rise/fall time                  | 5        |     |     | ns    |

| t <sub>PDD</sub>                | PCLK to data valid                   | 5        |     |     | ns    |

| $t_{PHD}$                       | PCLK to HREF delay                   | 20       | 10  | 5   | ns    |

| Zoom Vide                       | eo Port AC Parameters                |          |     |     |       |

| t1                              | PCLK fall time                       | 8        |     | 4   | ns    |

| t2                              | PCLK low time                        |          |     | 21  | ns    |

| t3                              | PCLK rise time                       | 8        |     | 4   | ns    |

| t4                              | PCLK high time                       |          |     | 21  | ns    |

| t5                              | PCLK period                          |          |     | 50  | ns    |

| t6                              | Y/UV/HREF setup time                 |          |     | 5   | ns    |

| t7                              | Y/UV/HREF hold time                  |          |     | 20  | ns    |

| t8                              | VSYNC setup/hold time to HREF        |          |     | 1   | μs    |

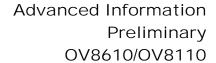

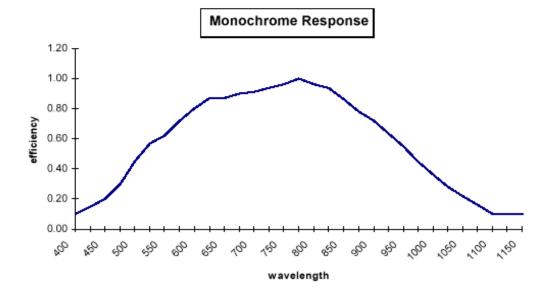

## Normalized Spectrum Response

Figure 2. OV8610/8110 Light Response

## **Function Description**

## Overview

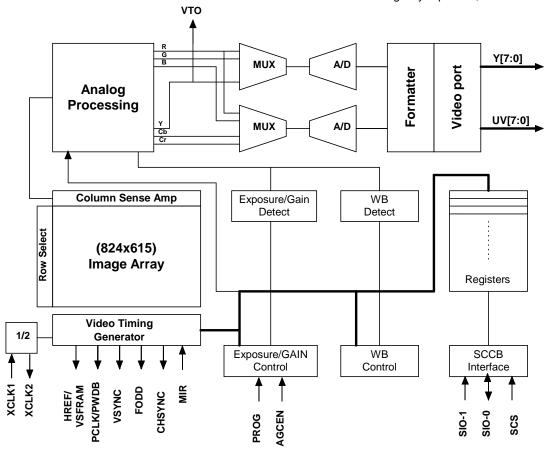

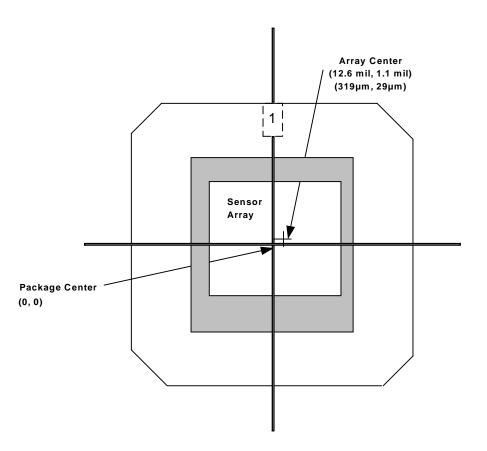

Referring to Figure 3 below, the OV8610/OV8110 sensor includes a 824 x 615 pixel image array, an analog signal processor, dual 10-bit A/D converters, analog video multiplexer, digital data formatter, video port, SCCB interface and control registers to control the timing block, exposure time, black level, white balance and a number of other parameters.

The OV8610/OV8110 sensor is a 1/3" CMOS imaging device. The sensor contains a total of 506,760 pixels (824x615). Its design is based on a field integration readout system with line-by-line transfer and an electronic rolling shutter with a synchronous pixel readout scheme. The color filter of the sensor consists of primary red, green, and blue filters arranged in the line-alternating Bayer pattern, RGRG/GBGB.

Figure 3. OV8610/OV8110 CMOS Image Sensor Block Diagram

Tel: (408) 733-3030 Fax: (408) 733-3061

## **Analog Processing Circuits**

#### Overview

The image is captured by the 824 x 615 pixel image array and routed to the analog processing section where the majority of signal processing occurs. This block contains the circuitry that performs color separation, color correction, automatic gain control (AGC), gamma correction, color balance, black level calibration, "knee" smoothing, aperture correction, controls for picture luminance and chrominance, and hue control for color. The analog video signals are based on the following formula:

Y = 0.59G + 0.31R + 0.11B U = R - YV = B - Y

Where R,G,B are the equivalent color components in each pixel.

YCrCb format is also supported, based on the formula below:

Y = 0.59G + 0.31R + 0.11B Cr = 0.713 (R - Y)Cb = 0.564 (B - Y)

The YcrCb or RGB data signal from the analog processing section is fed to two on-chip 10-bit analog-to-digital (A/D) converters: one for the Y/G channel and one shared by the CrCb/BR channels. The converted data stream is further conditioned in the digital formatter. The processed signal is delivered to the digital video port through the video multiplexer which routes the user-selected 8-, or 10-bit video data to the correct output pins.

The on-chip 10-bit A/D operates at up to 20 MHz, and is fully synchronous to the pixel rate. Actual conversion rate is related to the frame rate. A/D black-level calibration circuitry ensures:

- The black level of Y/RGB is normalized to a value of 16

- The peak white level is limited to 240

- CrCb black level is 128

- CrCb Peak/bottom is 240/16

- RGB raw data output range is 16/240 (Note: Values 0 and 255 are reserved for sync flag)

#### **Image Processing**

The algorithm used for the electronic exposure control is based on the brightness of the full image. The exposure is optimized for a "normal" scene that assumes the subject is well lit relative to the background. In situations where the image is not well lit, the automatic exposure control (AEC) white/black ratio may be adjusted to suit the needs of the application.

Additional on-chip functions include:

- AGC that provides a gain boost of up to 24dB

- White balance control that enables setting of proper color temperature and can be programmed for automatic or manual operation.

- Separate saturation, brightness, hue, and sharpness adjustments allow for further fine-tuning of the picture quality and characteristics.

The OV8610/OV8110 image sensor also provides control over the White Balance ratio for increasing/decreasing the image field Red/Blue component ratio. The sensor provides a default setting that may be sufficient for many applications.

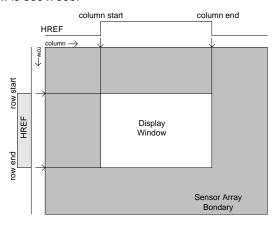

#### Windowing

The windowing feature of the OV8610/OV8110 image sensors allows user-definable window sizing as required by the application. Window size setting (in pixels) ranges from 2 x 2 to 800 x 600, and can be positioned anywhere inside the 824 x 615 boundary. Note that modifying window size and/or position does not change frame or data rate. The OV8610 imager alters the assertion of the HREF signal to be consistent with the programmed horizontal and vertical region. The default output window is 800 x 600.

Figure 4. Windowing

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A. Tel: (408) 733-3030 Fax: (408) 733-3061

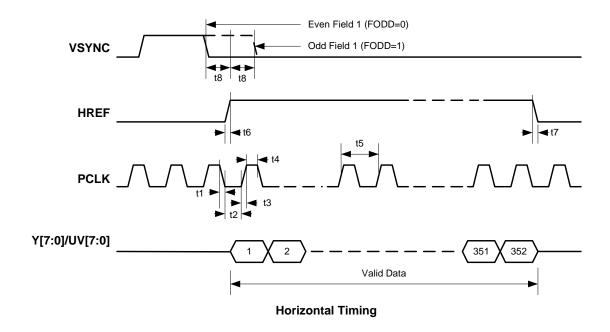

#### Zoom Video Port (ZV)

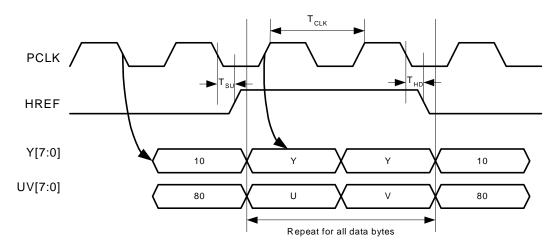

The OV8610/OV8110 image sensor includes a Zoom Video (ZV) function that supports standard ZV port interface timing. Signals available include VSYNC, CHSYNC, PCLK and 16-bit

data bus: Y[7:0] and UV[7:0]. The rising edge of PCLK clocks data into the ZV port. See Figure 5. Zoom Video Port Timing below.

**Vertical Timing**

## Figure 5. Zoom Video Port Timing

#### Note:

Zoom Video Port format output signal includes:

VSYNC: Vertical sync pulse.

HREF: Horizontal valid data output window.

PCLK: Pixel clock used to clock valid data and CHSYNC into Zoom V Port. Default frequency is 20MHz when use 20MHz as system clock plus 2X PLL implemented on chip. Rising edge of PCLK is used to clock the 16 Bit data.

Y[7:0]: 8 Bit luminance data bus.

UV[7:0]: 8 Bit chrominance data bus.

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A.

Tel: (408) 733-3030 Fax: (408) 733-3061

Advanced Information Preliminary OV8610/OV8110

OV8610 SINGLE-CHIP CMOS VGA COLOR DIGITAL CAMERA OV8110 SINGLE-CHIP CMOS VGA B&W DIGITAL CAMERA

#### **QSVGA**

A QSVGA mode is available for applications where higher resolution image capture is not required. Only half of the pixel rate is required when programmed in same frame rate with subsampling method. If you keep the same pixel rate with skip method, the maximum frame rate is 120. Default resolution is 400 x 300 pixels and can be programmed for other resolutions. Refer to Table 11. QSVGA Digital Output Format (YUV beginning of line) and Table 12. RGB Data Format for further information.

#### **QCIF**

A QCIF mode is available for further resolution decrease. Two method used to get this mode, sub-sampling and skip. The first one can get better quality than the second one and the second approach can have higher frame rate. The maximum frame rate is 240 for QCIF. The default resolution is 200 x 150.

#### **Video Output**

The video output port of the OV8610/OV8110 image sensors provides a number of output format/standard options to suit many different application requirements. Table 6, Digital Output Format indicates the output formats available. These formats are user-programmable through the SCCB interface.

#### **YUV Output**

The OV8610/OV8110 supports ITU-656 and ITU-601 output formats, providing VSYNC, HREF, and PCLK as standard output video timing signals.

#### ITU-601/ITU-656

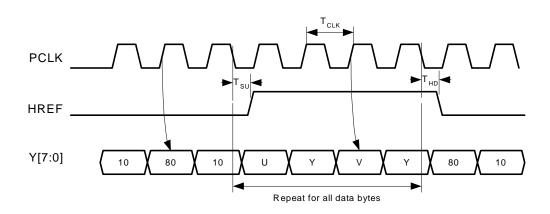

The OV8610/OV8110 imager supports both ITU-601 and ITU-656 output formats in the following configurations (See Table 7. 4:2:2 16-bit Format and Figure 6. Pixel Data Bus (YUV Output) for further details):

- 16-bit. 4:2:2 format

(This mode complies with the 60/50 Hz ITU-601 timing standard. See Table 7. 4:2:2 16-bit Format)

- 8-bit data mode

(In this mode, video information is output in Cb Y Cr Y order using the Y port only and running at twice the pixel rate during which the UV port is inactive. See Table 8. 4:2:2 8-bit Format).

The OV8610/OV8110 imager provides VSYNC, HREF, PCLK, FODD, and CHSYNC as standard video timing signals.

In ITU-656 modes, the OV8610/OV8110 imager asserts SAV (Start of Active Video) and EAV (End of Active Video) to indicate the beginning and the ending of the HREF window. As a result, SAV and EAV change with the active pixel window.

The OV8610/OV8110 imager offers flexibility in YUV output format. The device may be programmed to standard YUV 4:2:2. The device may also be configured to "swap" the UV sequence. When swapped, the UV channel output sequence in the 16-bit configuration becomes:

- V U V U....

The 8-bit configuration becomes:

- V Y U Y....

The third format available in the 8-bit configuration is the Y/UV sequence swap:

YUYV....

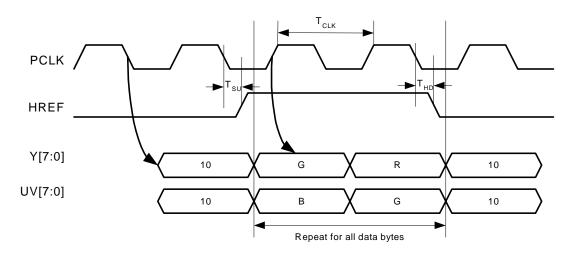

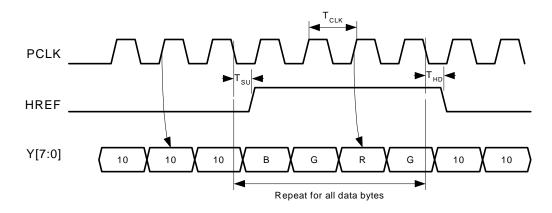

#### **RGB Raw Data Output**

The OV8610/OV8110 imager can also be programmed to provide 8-bit RGB raw data output. The output sequence is matched to the OV8610 color filter pattern.

The video output appears in Y channel only and the UV channel is disabled in 8-bit RGB raw data. The output sequence is B G R  $_{\odot}$

## **B/W Output**

The single-chip camera can be configured for use as a black and white image device. The vertical resolution is higher than in color mode. Video data output is provided at the Y port and the UV port is tri-stated. The data (Y/RGB) rate is equivalent to 16-bit in color mode.

The MSB and LSB of Y/UV or RGB output can be reversed. Y7 is MSB and Y0 is LSB in the default setting. Y7 becomes LSB and Y0 becomes MSB in the reverse order configuration. Y2-Y6 is also reversed appropriately.

Version 1.3, August 27, 2001

**Table 6. Digital Output Format**

| Resolution             | Pixel Clock          | 800 X 600 | 400 X 300 | 200 X 150 |

|------------------------|----------------------|-----------|-----------|-----------|

| YUV 4:2:2              | 16-bit               | Υ         | Υ         | Y         |

|                        | 8-bit                | Υ         | Y         | Y         |

|                        | ITU-656              | Υ         | Y         | Y         |

| RGB                    | 16-bit               | Υ         | Y         | Y         |

|                        | 8-bit                | Υ         | Y         | Y         |

|                        | ITU-656 <sup>1</sup> | Υ         | Y         | Y         |

| Y/UV swap <sup>2</sup> | 16-bit               |           |           |           |

|                        | 8-bit                | Υ         | Y         | Υ         |

| U/V swap               | YUV <sup>3</sup>     | Υ         | Y         | Y         |

|                        | RGB⁴                 | Υ         | Y         | Υ         |

| YG                     | 16-bit               | Υ         | Υ         | Υ         |

|                        | 8-bit                |           |           |           |

| Single-Line RGB        | 16-bit               |           |           |           |

| Raw Data               | 8-bit                | Υ         | Y         | Υ         |

| MSB/LSB swap           |                      | Υ         | Υ         | Y         |

#### Note:

("Y" indicates mode/combination is supported by OV8610/OV8110)

- 1. Output is 8-bit in RGB ITU-656 format. SAV and EAV are inserted at the beginning and ending of HREF, which synchronize the acquisition of VSYNC and HSYNC. 8-bit data bus configuration (without VSYNC and CHSYNC) can provide timing and data in this format.

- 2. Y/UV swap is valid in 8-bit only. Y channel output sequence is Y U Y V ...

- 3. U/V swap means UV channel output sequence swaps in YUV format, i.e., V U V U ... for 16 bit and V Y U Y ... for 8-bit.

- 4. U/V swap means neighbor row B R output sequence swap in RGB format. Refer to RGB raw data output format for further details.

Table 7. 4:2:2 16-bit Format

| Data Bus | Pixel Byte Sequence |       |     |     |     |     |  |

|----------|---------------------|-------|-----|-----|-----|-----|--|

| Y7       | Y7                  | Y7    | Y7  | Y7  | Y7  | Y7  |  |

| Y6       | Y6                  | Y6    | Y6  | Y6  | Y6  | Y6  |  |

| Y5       | Y5                  | Y5    | Y5  | Y5  | Y5  | Y5  |  |

| Y4       | Y4                  | Y4    | Y4  | Y4  | Y4  | Y4  |  |

| Y3       | Y3                  | Y3    | Y3  | Y3  | Y3  | Y3  |  |

| Y2       | Y2                  | Y2    | Y2  | Y2  | Y2  | Y2  |  |

| Y1       | Y1                  | Y1    | Y1  | Y1  | Y1  | Y1  |  |

| Y0       | Y0                  | Y0    | Y0  | Y0  | Y0  | Y0  |  |

| UV7      | UV7                 | UV7   | UV7 | UV7 | UV7 | UV7 |  |

| UV6      | UV6                 | UV6   | UV6 | UV6 | UV6 | UV6 |  |

| UV5      | UV5                 | UV5   | UV5 | UV5 | UV5 | UV5 |  |

| UV4      | UV4                 | UV4   | UV4 | UV4 | UV4 | UV4 |  |

| UV3      | UV3                 | UV3   | UV3 | UV3 | UV3 | UV3 |  |

| UV2      | UV2                 | UV2   | UV2 | UV2 | UV2 | UV2 |  |

| UV1      | UV1                 | UV1   | UV1 | UV1 | UV1 | UV1 |  |

| UV0      | UV0                 | UV0   | UV0 | UV0 | UV0 | UV0 |  |

| Y Frame  | 0                   | 1     | 2   | 3   | 4   | 5   |  |

| UV Frame | 0.                  | 01 23 |     |     | 4:  | 5   |  |

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A.

Tel: (408) 733-3030 Fax: (408) 733-3061

**Table 8. 4:2:2 8-bit Format**

| Data Bus |    | Pixel Byte Sequence |    |    |     |    |    |    |

|----------|----|---------------------|----|----|-----|----|----|----|

| Y7       | U7 | Y7                  | V7 | Y7 | U7  | Y7 | V7 | Y7 |

| Y6       | U6 | Y6                  | V6 | Y6 | U6  | Y6 | V6 | Y6 |

| Y5       | U5 | Y5                  | V5 | Y5 | U5  | Y5 | V5 | Y5 |

| Y4       | U4 | Y4                  | V4 | Y4 | U4  | Y4 | V4 | Y4 |

| Y3       | U3 | Y3                  | V3 | Y3 | U3  | Y3 | V3 | Y3 |

| Y2       | U2 | Y2                  | V2 | Y2 | U2  | Y2 | V2 | Y2 |

| Y1       | U1 | Y1                  | V1 | Y1 | U1  | Y1 | V1 | Y1 |

| Y0       | U0 | Y0                  | V0 | Y0 | U0  | Y0 | V0 | Y0 |

| Y Frame  | (  | 0 1                 |    | 1  | 2 3 |    |    | 3  |

| UV Frame |    | 01 23               |    |    |     |    |    |    |

Pixel Data 16-bit Timing (PCLK rising edge latches data bus)

Pixel Data 8-bit Timing (PCLK rising edge latches data bus)

**Note:**  $T_{CLK}$  is pixel clock period.  $T_{CLK}$ =50ns for 16-bit output and  $T_{CLK}$ =25ns for 8-bit output if the system clock is 20MHz with on chip 2X PLL.  $T_{SU}$  is the setup time of HREF. The maximum is 15ns.  $T_{HD}$  is the hold time of HREF. The maximum is 15ns.

Figure 6. Pixel Data Bus (YUV Output)

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A. Tel: (408) 733-3030 Fax: (408) 733-3061

Pixel Data 16-bit Timing (PCLK rising edge latches data bus)

Pixel Data 8-bit Timing (PCLK rising edge latches data bus)

**Note:**  $T_{\rm CLK}$  is pixel clock period.  $T_{\rm CLK}$ =50ns for 16-bit output and  $T_{\rm CLK}$ =25ns for 8-bit output if the system clock is 20MHz with on chip 2X PLL.  $T_{\rm SU}$  is the setup time of HREF. The maximum is 15ns.  $T_{\rm HD}$  is the hold time of HREF. The maximum is 15ns.

Figure 7. Pixel Data Bus (RGB Output)

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A. Tel: (408) 733-3030 Fax: (408) 733-3061

The default U/UV channel output port relation before an MSB/LSB swap:

#### **Table 9. Default Output Sequence**

|                      | MSB |    |    |    |    |    |    | LSB |

|----------------------|-----|----|----|----|----|----|----|-----|

| Output port          | Y7  | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0  |

| Internal output data | Y7  | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0  |

The relation after an MSB/LSB swap changes to:

## Table 10. Swapped MSB/LSB Output Sequence

|                      | MSB |    |    |    |    |    |    | LSB |

|----------------------|-----|----|----|----|----|----|----|-----|

| Output port          | Y7  | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0  |

| Internal output data | Y0  | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7  |

## Table 11. QSVGA Digital Output Format (YUV beginning of line)

| Pixel # | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Y       | Y0     | Y1     | Y2     | Y3     | Y4     | Y5     | Y6     | Y7     |

| UV      | U0, V0 | U1, V1 | U2, V2 | U3, V3 | U4, V4 | U5, V5 | U6, V6 | U7, V7 |

- Y channel output U2Y2V3 Y3U6 Y6V7 Y7 U10Y10 V11Y11 ...

- Every other (total 400) pixels and every other line (total 300 lines) is output in each frame.

#### **Table 12. RGB Data Format**

The pixel pattern is as following:

| R\C | 1                  | 2                  | 3                  | 4                  | <br>821              | 822                  | 823                  | 824                  |

|-----|--------------------|--------------------|--------------------|--------------------|----------------------|----------------------|----------------------|----------------------|

| 1   | B <sub>1,1</sub>   | G <sub>1,2</sub>   | B <sub>1,3</sub>   | G <sub>1,4</sub>   | B <sub>1,821</sub>   | G <sub>1,821</sub>   | B <sub>1,823</sub>   | G <sub>1,824</sub>   |

| 2   | G <sub>2,1</sub>   | R <sub>2,2</sub>   | G <sub>2,3</sub>   | R <sub>2,4</sub>   | G <sub>2,821</sub>   | R <sub>2,821</sub>   | G <sub>2,823</sub>   | R <sub>2, 824</sub>  |

| 3   | B <sub>3,1</sub>   | G <sub>3,2</sub>   | B <sub>3,3</sub>   | G <sub>3,4</sub>   | B <sub>3,821</sub>   | G <sub>3,642</sub>   | B <sub>3,823</sub>   | G <sub>3,824</sub>   |

| 4   | G <sub>4,1</sub>   | R <sub>4,2</sub>   | G <sub>4,3</sub>   | R <sub>4,4</sub>   | G <sub>4,821</sub>   | R <sub>4,642</sub>   | G <sub>4,823</sub>   | R <sub>4,824</sub>   |

|     |                    |                    |                    |                    |                      |                      |                      |                      |

| 613 | B <sub>613,1</sub> | G <sub>613,2</sub> | B <sub>613,3</sub> | G <sub>613,4</sub> | B <sub>613,821</sub> | G <sub>613,822</sub> | B <sub>613,823</sub> | G <sub>613,824</sub> |

| 614 | G <sub>614,1</sub> | R <sub>614,2</sub> | G <sub>614,3</sub> | R <sub>614,4</sub> | G <sub>614,821</sub> | R <sub>614,822</sub> | G <sub>614,823</sub> | R <sub>614,824</sub> |

- RGB full resolution progressive scan mode. (Total 614 HREFs)

- 1st HREF Y channel output unstable data

- 2nd HREF Y channel output  $B_{11}G_{21}\ R_{22}\ G_{12}\ B_{13}G_{23}\ R_{24}\ G_{14}\cdots$

- 3rd HREF Y channel output B<sub>31</sub> G<sub>21</sub> R<sub>22</sub> G<sub>32</sub> B<sub>33</sub> G<sub>23</sub> R<sub>24</sub> G<sub>34</sub>  $\cdots$

- Every line of data is output twice for each frame.

- PCLK is double

- RGB QSVGA resolution progressive scan mode. (Total 300 HREFs)

- 1st HREF Y channel output B<sub>11</sub>G<sub>21</sub> R<sub>22</sub> G<sub>12</sub> B<sub>15</sub>G<sub>25</sub> R<sub>26</sub> G<sub>16</sub>...

- 2nd HREF Y channel output  $B_{31}G_{41}$   $R_{42}$   $G_{32}$   $B_{35}G_{45}$   $R_{46}$   $G_{36}\cdots$

- 3rd HREF Y channel output B<sub>51</sub> G<sub>61</sub> R<sub>62</sub> G<sub>52</sub> B<sub>55</sub> G<sub>65</sub> R<sub>66</sub> G<sub>56</sub>  $\cdots$

- Every line of data is output once for each frame.

- Max frame rate is 60FPS

- RGB full resolution raw data one line format. (Total 600 HREFs)

- 1st HREF Y channel output B<sub>11</sub> G<sub>12</sub> B<sub>13</sub> G<sub>14</sub> ···

- 2nd HREF Y channel output G21 R22 G23 R24 ···

- 3rd HREF Y channel output  $B_{31}\ G_{32}\ B_{33}\ G_{34}\ \cdots$

- PCLK rising edge latch data bus.

- RGB QSVGA resolution raw data one line format. (Total 246 HREFs)

- 1st HREF Y channel output B<sub>11</sub> G<sub>12</sub> B<sub>15</sub> G<sub>16</sub> ···

- 2nd HREF Y channel output G21 R22 G25 R26 ···

- 3rd HREF Y channel output  $B_{51}$   $G_{52}$   $B_{55}$   $G_{56}$  ...

- 3rd HREF Y channel output G<sub>61</sub> R<sub>62</sub> G<sub>65</sub> R<sub>66</sub> ···

- PCLK rising edge latch data bus.

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A.

Tel: (408) 733-3030 Fax: (408) 733-3061

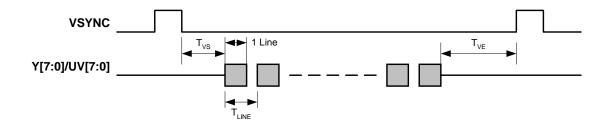

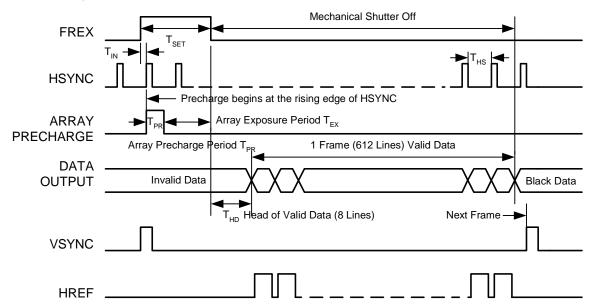

#### Frame Exposure Mode

OV8610/OV8110 supports frame exposure mode when FREX is set high. PWDN is asserted by an external master device to set exposure time at this mode. The pixel array is quickly precharged when PWDN is set to "1". OV8610/OV8110 captures the image in the time period when PWDN remains high. The video data stream is delivered to output port in a line-by-line manner after PWDN switches to "0".

It should be noted that PWDN must remain high long enough to ensure the entire image array has been pre-charged.

#### Reset

OV8610/8110 includes a RESET pin (pin 2) that forces a complete hardware reset when it is pulled high (VCC). OV8610/8110 clears all registers and resets to their default values when a hardware reset occurs. Reset can also be initiated through the SCCB interface.

#### **Power Down Mode**

Two methods are available to place OV8610 into power-down mode: hardware power-down and SCCB software power-down.

To initiate hardware power-down, the PWDN pin (9) must be tied to high (+3.3VDC). When this occurs, the OV8610 internal device clock is halted and all internal counters are reset. The current draw is less than 10µA in this standby mode.

Executing a software power-down through the SCCB interface suspends internal circuit activity, but does not halt the device clock. The current requirements drop to less than 1mA in this mode.

## Configure OV8610/OV8110

The method to configure OV8610/OV8110 is to use its on-chip SCCB register programming capability. The SCCB interface provides access to all of the device's programmable internal reaisters.

## Note:

- $T_{PR}$ =824 x 4 x  $T_{CLK}$  or  $T_{PR}$ =858x $T_{Clk}$  depends on mode selecton.  $T_{CLK}$  is internal pixel period.  $T_{CLK}$ =50ns if the system clock is 20MHz .  $T_{CLK}$  will increase with the clock divider CLK[5:0].  $T_{EX}$  is array exposure time which is decided by external master device.

- $T_{IN}^{EX}$  is uncertain time due to the using of HSYNC rising edge to synchronize FREX.  $T_{IN} < T_{HS}$

- There are 8 lines data output before valid data after FREX=0. T<sub>HD</sub>=4 THS. Valid data is output when

- $T_{\text{SET}} = T_{\text{IN}} + T_{\text{PR}} + T_{\text{EX}}$ ,  $T_{\text{SET}} > T_{\text{PR}} + T_{\text{IN}}$ . The exposure time setting resolution is  $T_{\text{HS}}$  (one line) due to the uncertainty of T<sub>IN</sub>.

Figure 8. Frame Exposure Timing

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A. Tel: (408) 733-3030 Fax: (408) 733-3061

# **Register Set**

The table below provides a list and description of available SCCB registers contained in the OV8610/8110 image sensor.

**Table 13. SCCB Registers**

| Sub-<br>address<br>(hex) | Register   | Default<br>(hex) | Read/<br>Write | Descriptions                                                                                                                                                                                          |

|--------------------------|------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                       | GAIN       | 00               | RW             | AGC gain control GC[7:6] – Unimplemented. GC[5:0] – The current gain setting.                                                                                                                         |

|                          |            |                  |                | This register is updated automatically if AGC is enabled. The internal controller stores the optimal gain value in this register. The current value is stored in this register if AGC is not enabled. |

| 01                       | BLUE       | 80               | RW             | Blue gain control BLU[7:0] – blue channel gain balance value. "FFh" is highest and "00h" is lowest  Note: This function is not available on the OV8110 image sensor.                                  |

| 02                       | RED        | 80               | RW             | Red gain control RED[7:0] – red channel balance value. "FFh" is highest and "00h" is lowest  Note: This function is not available on the OV8110 image sensor.                                         |

| 03                       | SAT        | 80               | RW             | Color saturation control SAT[7:4] – Saturation adjustment. "F8h" is highest and "00h" is lowest. SAT[3:0] – Unimplemented.  Note: This function is not available on the OV8110 image sensor.          |

| 04                       | HUE        | 10               | RW             | Color hue control HUE[7:6] – Unimplemented. HUE[5] – Enable HUE control HUE[4:0] – HUE control, range -30°~30°                                                                                        |

| 05                       | Rvsd       | XX               | -              | Reserved                                                                                                                                                                                              |

| 06                       | BRT        | 80               | RW             | Brightness control BRT[7:0] – Brightness adjustment. "FFh" is highest and "00h" is lowest.                                                                                                            |

| 07-09                    | Rsvd 07-09 | ××               | 1              | Reserved                                                                                                                                                                                              |

| 0A                       | PID        | 86               | R              | Product ID number read only                                                                                                                                                                           |

| 0B                       | VER        | B0               | R              | Product version number, read only                                                                                                                                                                     |

| 0C                       | ABLU       | 20               | RW             | White balance background: Blue channel ABLU[7:6] – Rsvd ABLU[5:0] - White balance blue ratio adjustment, "3Fh" is most blue.  Note: This function is not available on the OV8110 image sensor.        |

| 0D                       | ARED       | 20               | RW             | White balance background: Red channel ARED[7:6] – Rsvd ARED[4:0] - White balance red ratio adjustment, "3Fh" is most red.  Note: This function is not available on the OV8110 image sensor.           |

| 0E-0F                    | Rsvd 0E-0F | XX               | -              | Reserved                                                                                                                                                                                              |

| 10                       | AEC        | A2               | RW             | Automatic exposure control AEC[7:0] - Set exposure time $T_{EX} = 4 \times T_{LINE} \times AEC[7:0]$                                                                                                  |

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94085 U.S.A. Tel: (408) 733-3030 Fax: (408) 733-3061

| Sub-<br>address<br>(hex) | Register | Default (hex) | Read/<br>Write | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                       | CLKRC    | 00            | RW             | Clock rate control  CLKRC[7:6] - Sync output polarity selection  "00" - HSYNC=Neg, CHSYNC=Neg, VSYNC=Pos  "01" - HSYNC=Neg, CHSYNC=Neg, VSYNC=Neg  "10" - HSYNC=Pos, CHSYNC=Neg, VSYNC=Pos  "11" - HSYNC=Pos, CHSYNC=Pos, VSYNC=Pos  CLKRC[5:0] - Clock pre-scalar  CLK = (MAIN_CLOCK / ((CLKRC[5:0] + 1) × 2)) / n  Where n=1 if register [15], COMD[5] is set to "1" and n=2 otherwise.                                                                                                                                                                                                                                                                                                                                                                |

| 12                       | COMA     | 24            | RW             | Common control A  COMA[7] – SRST, "1" initiates soft reset. All registers are set to default values and chip is reset to known state and resumes normal operation.  COMA[6] – MIRR, "1" selects mirror image  COMA[5] – AGCEN, "1" enables AGC,  COMA[4] – Digital output format, "0" selects 8-bit: U Y V Y U Y V Y "1" selects 8-bit: Y U Y V Y U Y V V COMA[3] – Select video data output: "1" - select RGB, "0" - select YCrCb  COMA[2] – Auto white balance "1" - Enable AWB, "0" - Disable AWB  COMA[1] – Color bar test pattern: "1" - Enable color bar test pattern  COMA[0] – ADC BLC method: "1" – precise, "0" more stable but less precise                                                                                                   |

| 13                       | COMB     | 01            | RW             | Common control B  COMB[7] – VSYNC output selection, "1" – no VSYNC when no valid data, "0" –  VSYCN always output.  COMB[6] – AGC/AWB register SCCB update option. "1" – updated immediately after SCCB input, "0" – updated after VSYNC  COMB[5] - Select data format. "1" - select 8-bit format, Y/CrCb and RGB is multiplexed to 8-bit Y bus, UV bus is tri-stated, "0" - select 16-bit format COMB[4] – "1" - enable digital output in ITU-656 format  COMB[3] – CHSYNC output. "0" - horizontal sync, "1" - composite sync  COMB[2] – "1" – Tri-state Y and UV bus. "0" - enable both bus  COMB[1] – "1" - Initiate single frame transfer.  COMB[0] – "1" - Enable auto adjust mode.  Note: COMB[5] is not programmable on the OV8110 image sensor. |

| 14                       | COMC     | 00            | RW             | Common control C  COMC[7] – AWB threshold selection. "1" - More stable and less accurate, "0" – more accurate but less stable.  COMC[6] – UV option. "1" – UV always zero. "0" – normal color mode COMC[5] – QSVGA digital output format selection. "1" - 400x300; "0" - 800x 600.  COMC[4] – Field/Frame vertical sync output in VSYNC port selection: "1" - frame sync, only ODD field vertical sync; "0" - field vertical sync, effect in Interlaced mode  COMC[3] – HREF polarity selection: "0" - HREF positive effective, "1" - HREF negative.  COMC[2] – gamma selection: "1" - RGB Gamma on; "0" - RGB gamma is 1. COMC[1:0] – reserved                                                                                                          |

| Sub-<br>address | Register | Default<br>(hex) | Read/<br>Write | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|----------|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (hex)           |          |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15              | COMD     | 01               | RW             | Common Control D  COMD[7] – ADC clock 50% duty cycle selection. "1" – 50% duty cycle, "0" – non 50%.  COMD[6] – PCLK polarity selection. "0" - OV8610/OV8110 output data at PCLK falling edge and data bus will be stable at PCLK rising edge; "1" - rising edge output data and stable at PCLK falling edge.  COMD[5] – Digital 2x PLL disable. "1" – disable. "0" – enable.  COMD[4] – Array vertical 2 <sup>nd</sup> stage skip mode enable. Frame rate will double and only effective at progressive scan and 1 <sup>st</sup> stage sub-sampling disable.  COMD[3] – AGCEN pin option. "1" – AGCEN as data output enable/disable pin control, "0" – normal AGCEN pin.  COMD[2] – Reserved  COMD[1] – Enable NTSC timing. Only part of full resolution output.  COMD[0] – U V digital output sequence exchange control. 1 - UV UV ··· for 16- bit, U Y V Y ··· for 8-bit; 0 - V U V U ··· for 16-bit and V Y U Y ··· for 8-bit.  Note: COMD[0] is not programmable on the OV8110 image sensor.                                                                                                                                                                                                      |

| 16              | FSD      | 03               | RW             | Field slot division  FSD[7:2] – Field interval selection. It has functional in EVEN and ODD mode defined by FSD[1:0]. It is disabled in OFF and FRAME mode. The purpose of FSD[7:2] is to divide the video signal into programmed number of time slots, and allows HREF to be active only one field in every FSD[7:2] fields. It does not affect the video data or pixel rate. FSD[7:2]=1 outputs one field every field. FSD[7:2]=2 outputs one field every two fields. All other fields output black reference.  FSD[1:0] – field mode selection. Each frame consists of two fields: Odd and Even, FSD[1:0] define the assertion of HREF in relation to the two fields.  "00" – OFF mode; HREF is not asserted in both fields, one exception is the single frame transfer operation (see the description for the register 13)  "01" – Interlace mode: ODD mode; HREF is asserted in odd field only.  Progressive mode: HREF is asserted in frame according FD[7:2]  "10" – Interlace mode: EVEN mode; HREF is asserted in even field only.  Progressive mode: HREF is asserted in frame according FD[7:2].  "11" – FRAME mode; HREF is asserted in both odd field and even field.  FSD[7:2] disabled. |

| 17              | HREFST   | 38               | RW             | Horizontal HREF start  HS[7:0] – selects the starting point of HREF window, each LSB represents four pixels for SVGA resolution mode, two pixels for QVGA resolution mode, one pixel for QCIF mode. This value is set based on an internal column counter. The default value corresponds to 800 horizontal windows. Maximum window size is 824. HS[7:0] should be less than HE[7:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18              | HREFEND  | EA               | RW             | Horizontal HREF end  HE[7:0] – selects the ending point of HREF window, each LSB represents four pixels for full resolution and two pixels for QSVGA resolution, one pixel for QCIF mode. This value is set based on an internal column counter, the default value corresponds to the last available pixel. HE[7:0] should be larger than HS[7:0]. See window description below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19              | VSTRT    | 03               | RW             | Vertical line start VS[7:0] – selects the starting row of vertical window, in full resolution mode, each LSB represents 2 scan line in one field for Interlaced Scan Mode, 4 scan line in one frame for Progressive Scan Mode. In QSVGA mode, each LSB represents 1 scan line in one field for Interlaced Mode, 2 scan line in one frame for Progressive Scan Mode. See window description below. Min. is [02], max. is [98] and should less than VE[7:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Sub-             | Pogistor   | Default | Read/ | Dogarintiana                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|------------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address<br>(hex) | Register   | (hex)   | Write | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1A               | VEND       | 92      | RW    | Vertical line end VE[7:0] – selects the ending row of vertical window, in full resolution mode, each LSB represents 2 scan line in one field for Interlaced Scan Mode, 4 scan line in one frame for Progressive Scan Mode. In QSVGA mode, each LSB represents 1 scan line in one field for interlaced Mode, 2 scan line in one frame for Progressive Scan Mode. See window description below. Min. is [03], max. is [98] and should larger than VS[7:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1B               | PSHFT      | 00      | RW    | Pixel shift PS[7:0] – to provide a way to fine tune the output timing of the pixel data relative to that of HREF, it physically shifts the video data output time late in unit of pixel clock. This function is different from changing the size of the window as defined by HS[7:0] and HE[7:0] in registers 17 and 18. It just delays the output pixels relative tp HREF and does not change the window size. The highest number is "FF" and the maximum shift number is delay 256 pixels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1C               | MIDH       | 7F      | R     | Manufacture ID byte: High MIDH[7:0] – read only, always returns "7F" as manufacturer's ID no.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1D               | MIDL       | A2      | R     | Manufacture ID byte: Low MIDL[7:0] – read only, always returns "A2" as manufacturer's ID no.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1E-1F            | Rsvd 1E-1F | XX      | RW    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |