# 1 A Dual H-Bridge Driver

This dual full-bridge driver IC is intended for 14 V automotive stepper and DC motor applications. Its four half-bridge outputs are configured as two channels and are programmed by six TTL compatible inputs, allowing flexible control of bridge operation. The device operates in standby mode, run mode, or brake mode and typically consumes less than 1 µA while in standby. In run mode, each half-bridge output can deliver load current in either direction. Brake mode activates the low side transistors or high side transistors at the selected outputs. On-chip recirculation diodes are provided, and the IC has multiple fault protection modes. Overcurrent detection protects against shorted loads between outputs and shorts to supply or ground at each output. An overcurrent fault condition activates an internal timer, which modulates faulted outputs at low duty cycle. An overcurrent condition in one channel does not affect operation in the other. Overvoltage and overtemperature detection are also provided, and turn off all bridge outputs during these fault conditions. Recovery from all fault conditions is automatic; the IC will resume normal operation in its previously selected mode upon fault resolution. Diagnostic ability is provided by two open-collector STATUS outputs which report the fault status of each channel independently during overcurrent faults, and together during overvoltage or overtemperature faults.

#### **Features**

- Single 7 V-16 V Supply

- Low Standby Current:

- < 1.0 μA Typically

- 3.3 V / 5 V Compatible Inputs

- Independent Channel Enable

- Channels Configurable as:

- ◆ Full-Bridge Drive

- Half-Bridge, High Side or Low Side Drive

- On-Chip Recirculation Diodes

- Fault Protection with Automatic Recovery for:

- ♦ Overcurrent

- ♦ Overvoltage

- Overtemperature

- Fault Diagnostic STATUS Outputs

- Internally Fused Leads in SO-24L Package

## **Applications**

- Automotive and Industrial Driver for:

- DC or Stepper Motors

- Relays or Solenoids

- Unipolar or Bipolar Loads

# ON Semiconductor®

http://onsemi.com

SO-24L DW SUFFIX CASE 751E

#### MARKING DIAGRAM

A = Assembly Location

WL, L = Wafer Lot YY, Y = Year WW, W = Work Week

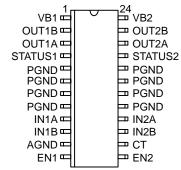

## **PIN CONNECTIONS**

## **ORDERING INFORMATION**

| Device      | Package | Shipping†        |  |  |

|-------------|---------|------------------|--|--|

| NCV7702DW   | SO-24L  | 31 Units/Rail    |  |  |

| NCV7702DWR2 | SO-24L  | 1000 Tape & Reel |  |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

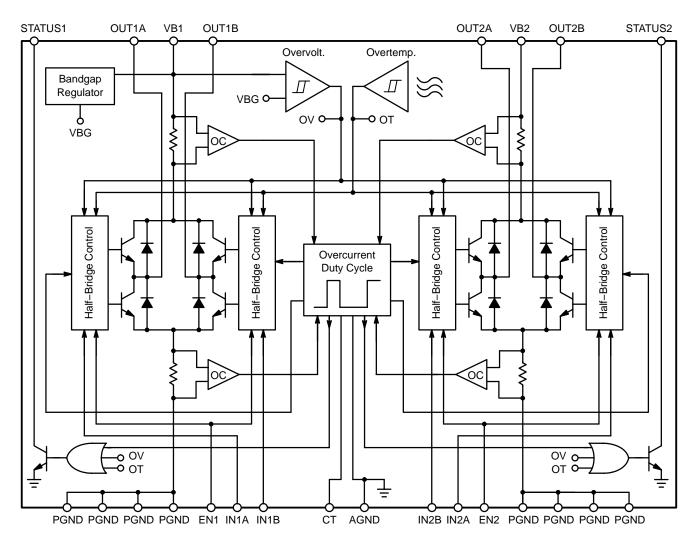

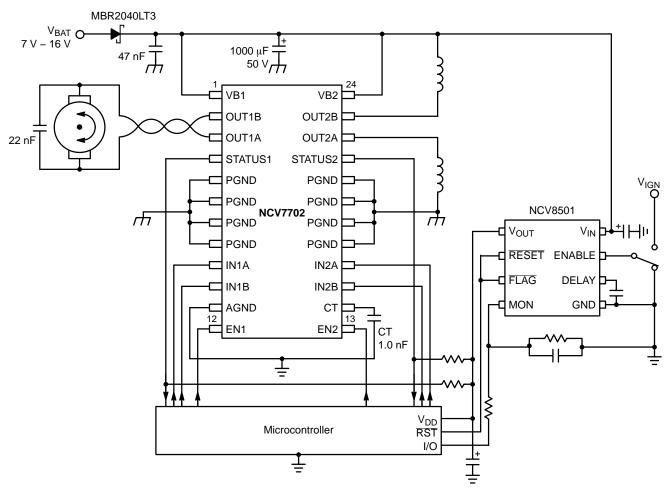

Figure 1. Block Diagram

# **MAXIMUM RATINGS**

|                                                                                                            | Value                                               | Unit       |         |  |  |  |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|---------|--|--|--|

| Power Supply Voltage, VB                                                                                   | -0.5 to 30                                          | V          |         |  |  |  |

| Peak Transient Voltage (46 V Loa                                                                           | Peak Transient Voltage (46 V Load Dump @ VB = 14 V) |            |         |  |  |  |

| Logic Inputs & Status Outputs                                                                              | Logic Inputs & Status Outputs                       |            |         |  |  |  |

| Junction Temperature, T <sub>J</sub>                                                                       | 150                                                 | °C         |         |  |  |  |

| Storage Temperature Range                                                                                  | -65 to 150                                          | °C         |         |  |  |  |

| Package Thermal Resistance:<br>Junction-to-Case, R <sub>θJC</sub><br>Junction-to-Ambient, R <sub>θJA</sub> |                                                     | 9<br>55    | °C/W    |  |  |  |

| ESD Capability                                                                                             | Human Body Model<br>Machine Model                   | 2.0<br>200 | kV<br>V |  |  |  |

| Soldering Temperature:                                                                                     | Reflow: (SMD styles only) (Note 1)                  | 230 peak   | °C      |  |  |  |

Maximum Ratings are those values beyond which damage (latent or otherwise) to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum–rated conditions is not implied. Voltages are with respect to device substrate.

1. 60 second maximum above 183°C.

**ELECTRICAL CHARACTERISTICS** (7.0 V  $\leq$  VB  $\leq$  16 V,  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  125°C; unless otherwise specified.) Notes 2 and 3.

| Characteristic                                                       | Test Conditions                                                                                                          | Min          | Тур           | Max         | Unit                     |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-------------|--------------------------|

| General Characteristics                                              |                                                                                                                          |              |               |             |                          |

| Quiescent Current                                                    | Standby Mode, VB ≤ 12.8 V                                                                                                | _            | 1.0           | 10          | μΑ                       |

|                                                                      | Run Mode, I <sub>OUT</sub> = 750 mA, Both Channels                                                                       | -            | -             | 40          | mA                       |

| Logic Inputs                                                         |                                                                                                                          |              |               |             |                          |

| High Level Input Voltage, V <sub>IH</sub>                            | -                                                                                                                        | 2.0          | -             | _           | V                        |

| Low Level Input Voltage, V <sub>IL</sub>                             | -                                                                                                                        | _            | -             | 8.0         | V                        |

| IN <sub>X</sub> Input Current                                        | V <sub>IN</sub> = 5.0 V<br>V <sub>IN</sub> = 0 V                                                                         | -<br>-5.0    | 0<br>0        | 5.0<br>-    | μ <b>Α</b><br>μ <b>Α</b> |

| EN <sub>X</sub> Input Current                                        | V <sub>IN</sub> = 5.0 V<br>V <sub>IN</sub> = 0 V                                                                         | -<br>-5.0    | 130<br>0      | 200<br>5.0  | μA<br>μA                 |

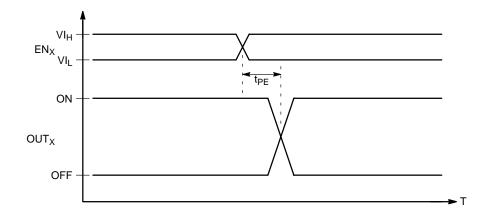

| EN <sub>X</sub> Delay, t <sub>PE</sub>                               | 50% of EN <sub>X</sub> to 50% of OUT <sub>X</sub> ; Note 4 Turn ON Turn Off                                              |              | -<br>-        | 25<br>60    | μs                       |

| Status Outputs                                                       |                                                                                                                          |              |               |             |                          |

| Saturation Voltage, V <sub>SL</sub>                                  | I <sub>STATUS</sub> = 4.0 mA                                                                                             | _            | _             | 0.4         | V                        |

| Leakage Current                                                      | V <sub>STATUS</sub> = 5.0 V                                                                                              | _            | -             | 10          | μΑ                       |

| Half-Bridge Driver Outputs                                           |                                                                                                                          |              |               |             | •                        |

| Total Output Saturation Voltage                                      | I <sub>OUT</sub> = 750 mA, Each Channel                                                                                  | -            | 2.5           | 3.0         | V                        |

| Output Saturation Voltage High                                       | I <sub>OUT</sub> = 750 mA, VB – V <sub>OUT</sub> , Each Driver                                                           | -            | 1.25          | 1.6         | V                        |

| Output Saturation Voltage Low                                        | I <sub>OUT</sub> = 750 mA, V <sub>OUT</sub> – V <sub>PGND</sub> , Each Driver                                            | _            | 1.25          | 1.6         | V                        |

| Output Leakage                                                       | V <sub>OUT</sub> = VB<br>V <sub>OUT</sub> = V <sub>PGND</sub>                                                            | -<br>-5.0    | 0             | 5.0<br>-    | μA<br>μA                 |

| Overcurrent Threshold, I <sub>OC</sub>                               | Low Side, Each Channel<br>High Side, Each Channel                                                                        | 0.9<br>0.775 | 1.25<br>0.900 | 1.6<br>1.10 | А                        |

| Overcurrent Duty Cycle                                               | 470 pF ≤ C <sub>T</sub> ≤ 1500 pF; Note 5                                                                                | 3.0          | 4.0           | 6.0         | %                        |

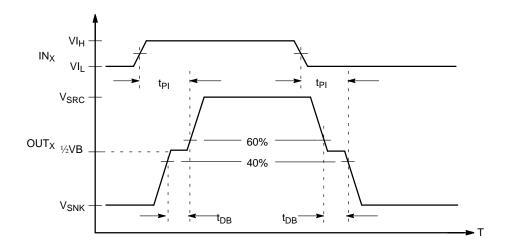

| Switching Delay, t <sub>Pl</sub><br>Sink to Source<br>Source to Sink | 50% of IN <sub>X</sub> to 60% of OUT <sub>X</sub> ; Note 6<br>50% of IN <sub>X</sub> to 40% of OUT <sub>X</sub> ; Note 6 | 0.20<br>0.20 | -<br>-        | 14<br>10    | μs                       |

| Dead Band Time, t <sub>DB</sub>                                      | Note 6                                                                                                                   | 0.10         | -             | 10          | μs                       |

| Recirculation Diode Forward Voltage                                  | I <sub>DIODE</sub> = 750 mA                                                                                              | _            | -             | 2.5         | V                        |

| Delay Timer                                                          |                                                                                                                          |              |               |             |                          |

| Charge Current, I <sub>CHG</sub>                                     | -                                                                                                                        | -85          | -65           | -45         | μΑ                       |

| Discharge Current, I <sub>DCH</sub>                                  | -                                                                                                                        | 1.25         | 2.0           | 3.25        | μΑ                       |

| Input Threshold High, V <sub>CH</sub>                                | -                                                                                                                        | 1.85         | 2.0           | 2.15        | V                        |

| Input Threshold Low, V <sub>DC</sub>                                 | -                                                                                                                        | 200          | 300           | 400         | mV                       |

| Global Fault Protection                                              |                                                                                                                          |              |               |             |                          |

| Overtemperature Detection Threshold                                  | Note 7                                                                                                                   | 150          | -             | 210         | °C                       |

| Overtemperature Hysteresis                                           | Note 7                                                                                                                   | _            | 15            | _           | °C                       |

| Overvoltage Detection Threshold                                      | Note 8                                                                                                                   | 26           | 28            | 30          | V                        |

| Overvoltage Hysteresis                                               | _                                                                                                                        | 500          | 850           | 1200        | mV                       |

- Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100% parametrically tested in production.

Operation is guaranteed down to VB = 6.0 V. Electrical characteristics may be outside the limits at that voltage.

See Figures 2 and 3; VB = 14 V, R = 100 Ω.

- C<sub>T</sub> must remain in this range to guarantee proper operation, and to ensure part integrity, during hard short conditions.

See Figures 2 and 4; VB = 14 V, R = 100 Ω.

Guaranteed by design.

- 8. Consult factory for no overvoltage detection or lower overvoltage detection threshold options.

# PACKAGE PIN DESCRIPTION

| PACKAGE PIN # | PIN SYMBOL | FUNCTION                                                                                 |

|---------------|------------|------------------------------------------------------------------------------------------|

| 1             | VB1        | Power supply input voltage; overvoltage detection occurs at this pin.                    |

| 2             | OUT1B      | Half-bridge output controlled by IN1B.                                                   |

| 3             | OUT1A      | Half-bridge output controlled by IN1A.                                                   |

| 4             | STATUS1    | Diagnostic output; reports channel #1 fault condition.                                   |

| 5             | PGND       | Power supply return.                                                                     |

| 6             | PGND       | Power supply return.                                                                     |

| 7             | PGND       | Power supply return.                                                                     |

| 8             | PGND       | Power supply return.                                                                     |

| 9             | IN1A       | Logic level input.                                                                       |

| 10            | IN1B       | Logic level input.                                                                       |

| 11            | AGND       | Analog supply return; reference for external C <sub>T</sub> capacitor, device substrate. |

| 12            | EN1        | Enable for OUT1A and OUT1B.                                                              |

| 13            | EN2        | Enable for OUT2A and OUT2B.                                                              |

| 14            | CT         | External capacitor; sets overcurrent delay time and duty cycle.                          |

| 15            | IN2B       | Logic level input.                                                                       |

| 16            | IN2A       | Logic level input.                                                                       |

| 17            | PGND       | Power supply return.                                                                     |

| 18            | PGND       | Power supply return.                                                                     |

| 19            | PGND       | Power supply return.                                                                     |

| 20            | PGND       | Power supply return.                                                                     |

| 21            | STATUS2    | Diagnostic output; reports channel #2 fault condition.                                   |

| 22            | OUT2A      | Half-bridge output controlled by IN2A.                                                   |

| 23            | OUT2B      | Half-bridge output controlled by IN2B.                                                   |

| 24            | VB2        | Power supply input voltage.                                                              |

# **INPUT LOGIC TABLE**

|     | EN1 = EN2 = 0 = Standby Mode |      |       |       |            |                                |   |   |      |      |            |

|-----|------------------------------|------|-------|-------|------------|--------------------------------|---|---|------|------|------------|

|     | Channel #1                   |      |       |       | Channel #2 |                                |   |   |      |      |            |

| EN1 | IN1A                         | IN1B | OUT1A | OUT1B | Mode       | EN2 IN2A IN2B OUT2A OUT2B Mode |   |   |      | Mode |            |

| 1   | 0                            | 0    | Low   | Low   | Brake Low  | 1                              | 0 | 0 | Low  | Low  | Brake Low  |

| 1   | 0                            | 1    | Low   | High  | Run        | 1                              | 0 | 1 | Low  | High | Run        |

| 1   | 1                            | 0    | High  | Low   | Run        | 1                              | 1 | 0 | High | Low  | Run        |

| 1   | 1                            | 1    | High  | High  | Brake High | 1                              | 1 | 1 | High | High | Brake High |

| 0   | Х                            | Х    | Z     | Z     | Off        | 0                              | Х | Х | Z    | Z    | Off        |

NOTE: X = Don't Care; |Z| = Output Off.

#### STATUS OUTPUT TABLE

| STATUS1 | STATUS2 | Fault Diagnostic                                                             |  |  |

|---------|---------|------------------------------------------------------------------------------|--|--|

| 1       | 1       | No Fault.                                                                    |  |  |

| 0       | 1       | Channel 1 Overcurrent; Note 9                                                |  |  |

| 1       | 0       | Channel 2 Overcurrent; Note 9                                                |  |  |

| 0       | 0       | Overvoltage, Overtemperature or Overcurrent in Both Channels; Notes 9 and 10 |  |  |

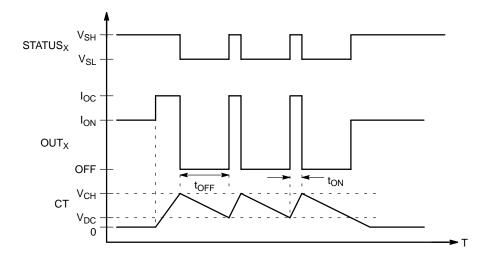

- 9. During overcurrent, the STATUS outputs will be modulated at the overcurrent duty cycle rate. See Figure 5. 10. During overtemperature, the STATUS outputs will be modulated by the thermal time constants.

Figure 2. Propagation Delay and Dead Band Timing Test Circuit

Figure 3. EN<sub>X</sub> Propagation Delay

Figure 4. OUT<sub>X</sub> Propagation Delay and Dead Band Timing

Figure 5. Overcurrent, Status and Duty Cycle Timing

#### **Functional Description**

The NCV7702 is arranged as four half–bridge drivers in two independent channels. Each channel can be operated as a full–bridge or half–bridge to drive multiple load configurations. Separate ENable inputs are used to control which channel is active. Each ENable input has a nominal 50 k $\Omega$  internal pull–down resistor to ensure that the outputs remain off during power–up. The four IN $_{\rm X}$  control inputs address each half–bridge output, and each output follows the state of its input. When IN $_{\rm X}$  is at logic one, OUT $_{\rm X}$  is sourcing current from the VB supply; when IN $_{\rm X}$  is at logic zero, OUT $_{\rm X}$  is sinking current to the PGND return.

# Half-Bridge Drivers

The half-bridge drivers of each  $OUT_X$  are comprised of an NPN Darlington driver on the low-side and a compound PNP-NPN driver on the high-side. Each half-bridge driver is capable of 1 A (min) peak current and is overcurrent protected against load and system faults. Cross conduction currents within each half-bridge are suppressed by the use of a dead-band timer. Each  $IN_X$  input contains an independent dead-band timer that is activated on either edge of the input transition.

Overcurrent detection circuitry is provided in both the low-side and high-side drivers of each half-bridge output. When activated, the overcurrent detectors trigger an internal timer which causes both half-bridge drivers in the same channel to be modulated at 4% (Typ.) duty cycle. The timer also activates the channel's STATUS output, causing it to be similarly modulated (see Figure 5.) Upon removal of the fault condition, the channel automatically resumes operation in its previously programmed mode and its STATUS output returns to a no-fault state.

Recirculation diodes at each  $OUT_X$  clamp load transients to either VB or PGND and help contain switching currents within each load loop.

# **Overcurrent Duty Cycle Timer**

A single timer for overcurrent duty cycle is common to both channels. The timer is triggered when a half-bridge in either channel has detected an overcurrent fault. An external capacitor connected to the NCV7702's C<sub>T</sub> pin is used to program the period of the timer, and the ratio of two internally fixed currents programs the timer's duty cycle. The capacitor voltage is normally kept at zero by discharge

current  $I_{DCH}$ . Upon detection of overcurrent, charging current  $I_{CHG}$  is switched on and the  $C_T$  capacitor begins charging from zero towards the timer's upper threshold  $(V_{DH})$ . When the capacitor voltage crosses  $V_{DH}$  the faulted channel's outputs are switched off and the channel's STATUS output is switched from  $V_{SH}$  to  $V_{SL}$  (see Figure 5.) The charging current is switched off, and the capacitor voltage decreases toward the timer's lower  $(V_{DL})$  threshold. Upon crossing the lower threshold, the channel's outputs are switched on and the channel's STATUS output returns to its  $V_{SH}$  voltage. This behavior continues until the fault condition is resolved. If the fault condition is resolved before  $V_{DH}$  is reached, the timer is reset and no modulation of the previously faulted channel's half—bridge or STATUS outputs occurs.

After the timer's initial charge cycle, the output off time is:  $t_{OFF} = C_T \; (V_{CH} - V_{Dc}) / \; I_{DCH}.$

The output on time is:  $t_{ON} = C_T (V_{CH} - V_{Dc}) / I_{CHG}$ .

The timer period is:  $T = t_{OFF} + t_{ON}$ .

The value of the  $C_T$  capacitor is required to be in the range of 470 to 1500 pF. Values below 470 pF may cause timer mis—operation due to internal delays, while values above 1500 pF may cause excessive power dissipation. Connecting the  $C_T$  pin to ground will prevent operation of the current limit function.

# Overvoltage and Overtemperature Protection

Overvoltage detection circuitry is intended to allow limited operation of the NCV7702 during double-battery conditions. Detection is via the VB1 pin and causes both channels of the IC to be switched off when the detection threshold is exceeded. Hysteresis is provided to improve noise immunity of the overvoltage function.

Overtemperature detection circuitry monitors the junction temperature internal to the IC and is intended to ensure reliability by preventing excessive power dissipation. The detection circuitry is centrally located on the IC and causes both channels of the IC to be switched off when the detection threshold is exceeded. Hysteresis is provided to improve noise immunity of the overtemperature function.

Both STATUS outputs are switched to the  $V_{SL}$  state during either overvoltage or overtemperature faults. Normal operation of the IC is resumed automatically upon resolution the fault, and the STATUS outputs return to the  $V_{SH}$  State.

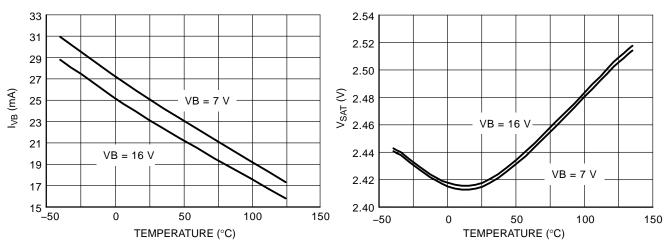

Figure 6. Run Mode Bias Current vs. Temperature

Figure 7. Total  $V_{\text{SAT}}$  vs. Temperature

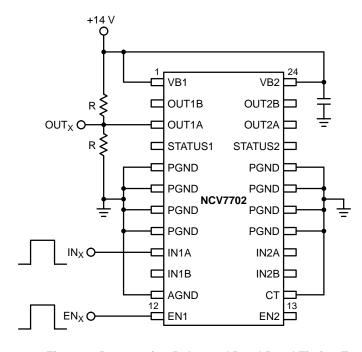

Figure 8. Application Diagram

NOTE: Both V<sub>B</sub> inputs must be connected to the power supply. All PGND pins must be connected to the power supply return (GND). For best thermal performance, the PGND pins should be connected to a thermal plane (heat sink) on the PC board.

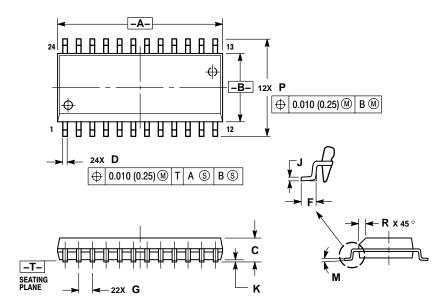

# **PACKAGE DIMENSIONS**

SO-24L **DW SUFFIX** CASE 751E-04 ISSUE E

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN   | IETERS | INCHES    |       |  |

|-----|----------|--------|-----------|-------|--|

| DIM | MIN      | MAX    | MIN       | MAX   |  |

| Α   | 15.25    | 15.54  | 0.601     | 0.612 |  |

| В   | 7.40     | 7.60   | 0.292     | 0.299 |  |

| С   | 2.35     | 2.65   | 0.093     | 0.104 |  |

| D   | 0.35     | 0.49   | 0.014     | 0.019 |  |

| F   | 0.41     | 0.90   | 0.016     | 0.035 |  |

| G   | 1.27 BSC |        | 0.050 BSC |       |  |

| J   | 0.23     | 0.32   | 0.009     | 0.013 |  |

| K   | 0.13     | 0.29   | 0.005     | 0.011 |  |

| M   | 0°       | 8°     | 0°        | 8°    |  |

| P   | 10.05    | 10.55  | 0.395     | 0.415 |  |

| R   | 0.25     | 0.75   | 0.010     | 0.029 |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability, arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free LISA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.