Preliminary, May 2000 (Ver1.1)

## Features

- $\bullet$  256  $\times$  256 non-blocking or 512  $\times$  256 blocking switching

- Support 8-bit or 4-bit channel switching

- Operating at rate of 2.048, 4.096 or 8.192Mbits/s

- Identical & Different I/O data rate selection

- Input frame offset selection

- Per-channel variable/constant throughput delay selection

- Tri-state outputs

- ST-BUS/GCI interfaces identified automatically

- Control port compatible to Motorola/Intel multiplexed buses and Motorola non-multiplexed bus

- +5 V single power supply

- Low power consumption (30 mW Typ.)

- Operating temperature range:

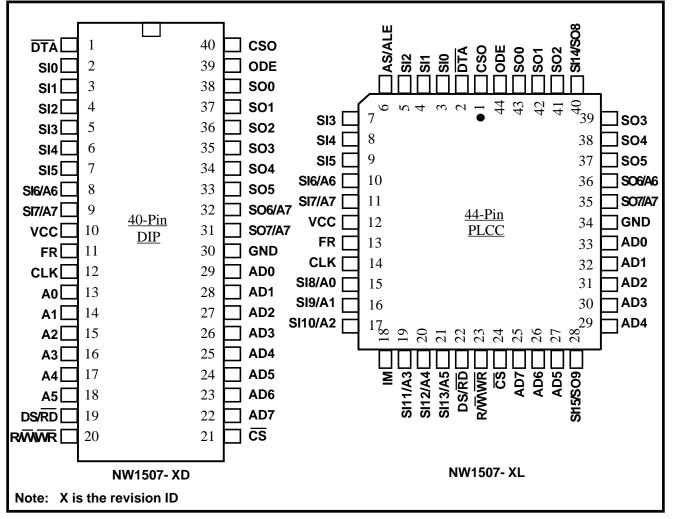

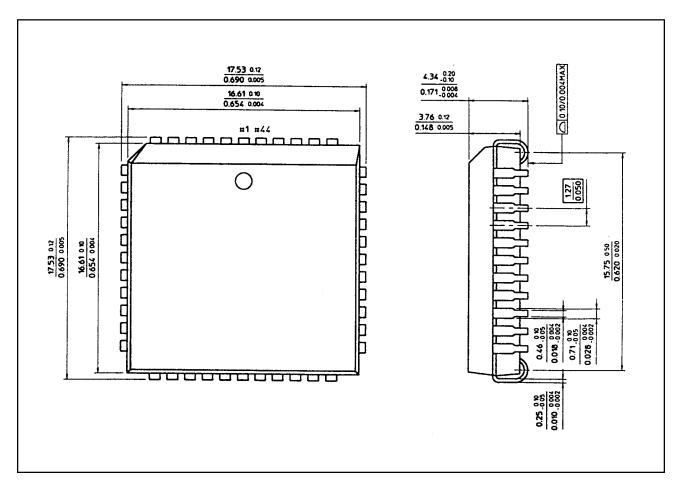

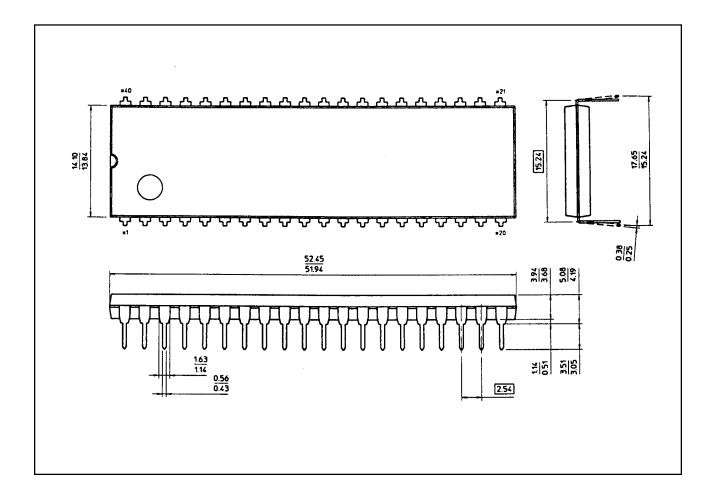

- -40 °C to +85 °C • Packages available: NW1507-XL 44-pin PLCC

- NW1507-XD 40-pin DIP (where X is the revision ID)

## Description

The NW1507 is a digital switch matrix, providing  $256 \times 256$  non-blocking or  $512 \times 256$  blocking switching configurations. The serial input and output streams may have data rates of 2.048, 4.096 or 8.192Mbits/s with 32, 64 or 128 channels respectively. Variable/constant throughput delay selection is provided on per channel basis to maintain the data sequence integrity during the non-blocking switching. In addition, the control interface of the NW1507, compatible with Motorola/ Intel CPUs, provides read and write access to internal registers and memories. The NW1507 can also be used for switching 32Kbits/s channels in ADPCM application.

## Applications

The NW1507 device can be used for the switching of digitized data, voice and video in applications as: Central Office Switch, Private Branch Exchange (PBX), Wireless Base Station, Access Networks, ISDN, Voice/Data multiplexer and voice card.

\* 44 pin package only

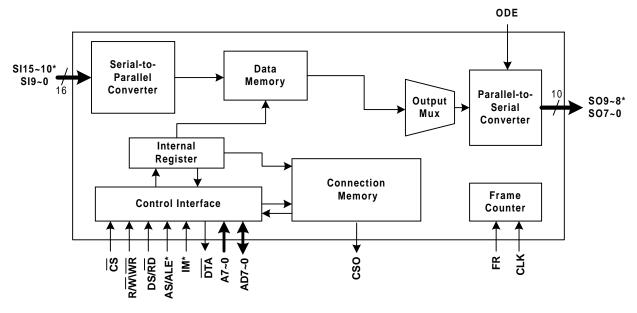

## Figrue-1. Block Diagram

Newave Semiconductor Corp.

2041 Mission College Blvd. Suite 250 Santa Clara, CA 95054, USA

# **Pin Connection**

# **Pin Description**

|                                        |      | Pin N                      | Number                     |                                                                                                                                                                                                                                       |

|----------------------------------------|------|----------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                   | Туре | 40                         | 44                         | DESCRIPTION                                                                                                                                                                                                                           |

|                                        |      | DIP PLCC                   |                            |                                                                                                                                                                                                                                       |

| DTA                                    | 0    | 1                          | 2                          | <b>Data Acknowledgement</b> (Open Drain Output).<br>This is a pin on the microprocessor interface. When this pin is LOW, the data is ready to be accessed. An external 10 K $\Omega$ pull-up resistor is required at this output pin. |

| SI0<br>SI1<br>SI2<br>SI3<br>SI4<br>SI5 | Ι    | 2<br>3<br>4<br>5<br>6<br>7 | 3<br>4<br>5<br>7<br>8<br>9 | Serial ST-BUS <sup>™</sup> Input.<br>Pins for serial input streams, which may have data rates of 2.048, 4.096 or 8.192Mbits/s with 32, 64 or 128 channels per frame respectively.                                                     |

|                                                      |      | Pin N                                        | umber                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------|------|----------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                 | Туре | 40                                           | 44                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |      | DIP                                          | PLCC                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SI6/A6                                               | I    | 8                                            | 10                                           | <b>ST-BUS Input 6/Address Input 6</b><br>When multiplexed CPU bus* is selected or input data rate is 2.048 or<br>4.096Mbits/s, this pin is used as data stream input SI6. When non-<br>multiplexed CPU bus is selected and the input data rate is 4.096 or<br>8.192Mbits/s, this pin is used as address input A6. Please refer to Table-<br>1, 2, 8&9. If SI6 and A6 are required simultaneously, the A6 input<br>should be connected to pin SO6/A6. |

| SI7/A7                                               | I    | 9                                            | 11                                           | <b>ST-BUS Input 7/Address Input 7</b><br>When multiplexed CPU bus* is selected or input data rate is 2.048 or<br>4.096Mbits/s, this pin is used as data stream input SI7. When non-<br>multiplexed CPU bus is selected and the input data rate is 4.096or<br>8.192Mbits/s, this pin is used as address input A7. Please refer to Table-<br>1, 2, 8&9. If SI7 and A7 are required simultaneously, the A7 input<br>should be connected to pin SO7/A7.  |

| VCC                                                  |      | 10                                           | 12                                           | Power Supply of +5V.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FR                                                   | Ι    | 11                                           | 13                                           | <b>Frame Input</b><br>Frame synchronization signals input pin, ST-BUS or GCI are<br>automatically identified.                                                                                                                                                                                                                                                                                                                                        |

| CLK                                                  | Ι    | 12                                           | 14                                           | <b>Clock Input</b><br>Pin of clock input for shifting data I/O on the serial streams, which may be 4.096 or 8.192MHz.                                                                                                                                                                                                                                                                                                                                |

| A0/SI8<br>A1/SI9<br>A2/SI10<br>A3/SI11<br>A4/SI12    | I    | 13<br>14<br>15<br>16<br>17                   | 15<br>16<br>17<br>19<br>20                   | Address Input/Serial Streams Input<br>When non-multiplexed CPU bus is selected, address input function is<br>provided. When $16 \times 8$ switching configuration* is selected, the serial<br>streams input function with data rate of 2.048mbits/s is provided.                                                                                                                                                                                     |

| A5/SI13<br>DS/RD                                     | I    | <u>18</u><br>19                              | 21<br>22                                     | <b>Data Strobe/Read</b><br>When non-multiplexed CPU bus or Motorola multiplexed bus* is<br>selected, the data strobe function is provided.<br>When Intel/National multiplexed bus* is selected, the read function is<br>provided. This active low input configures the AD0~7 as outputs.                                                                                                                                                             |

| R∕₩\₩R                                               | I    | 20                                           | 23                                           | Read/Write \ Write<br>When non-multiplexed or Motorola multiplexed bus* is selected, the<br>read/write function is enabled: High for read, Low for write.<br>When Intel/National multiplexed bus* is selected, the write function is<br>provided. This active low signal configures the AD0~7 as inputs.                                                                                                                                             |

| <b>CS</b>                                            | Ι    | 21                                           | 24                                           | Chip Select<br>Active low Chip Select on the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                               |

| AD7<br>AD6<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD0 | I/O  | 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29 | 25<br>26<br>27<br>29<br>30<br>31<br>32<br>33 | Data Bus of Tri-state I/O<br>Pins of microprocessor access to the internal control registers,<br>Connection Memory High and Low and Data Memory.<br>When multiplexed bus* is selected, address input function is provided.<br>The pins have internal pull down resisters.                                                                                                                                                                            |

| GND                                                  |      | 30                                           | 34                                           | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      |      | Pin N | umber    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                 | Туре | 40    | 44       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                      |      | DIP   | PLCC     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SO7/A7               | 0/I  | 31    | 35       | <b>ST-BUS Output 7/Address Input 7</b><br>When multiplexed CPU bus* is selected or data rate is 2.048Mbits/s, this<br>pin is used as data stream output SO7. When non-multiplexed CPU bus is<br>selected and the data rate is 8.192 or 4.096Mbits/s, this pin is used as<br>address input A7. And this pin has internal pull down resister. Please refer<br>to Table-1, 2, 8&9. If SO7 and A7 are required simultaneously, the A7<br>input should be connected to pin SI7/A7. When both pin SI7/A7 and pin<br>SO7/A7 can be used as A7, pin SO7/A7 is preferred. |

| SO6/A6               | 0/I  | 32    | 36       | <b>ST-BUS Output 6/Address Input 6</b><br>When multiplexed CPU bus* is selected or data rate is 2.048Mbits/s, this<br>pin is used as data stream output SO6. When non-multiplexed CPU bus is<br>selected and the data rate is 8.192 or 4.096Mbits/s, this pin is used as<br>address input A6. And this pin has internal pull down resister. Please refer<br>to Table-1, 2, 8&9. If SO6 and A6 are required simultaneously, the A6<br>input should be connected to pin SI6/A6. When both pin SI6/A6 and pin<br>SO6/A6 can be used as A6, pin SO6/A6 is preferred. |

| SO5                  |      | 33    | 37       | Serial ST-BUS™ Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SO4                  |      | 34    | 38       | Pins for serial output streams, which may have data rates of 2.048, 4.096                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>SO3</b>           | 0    | 35    | 39       | or 8.192Mbits/s with 32, 64 or 128 channels per frame respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SO2                  | U    | 36    | 41       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SO1                  |      | 37    | 42       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SOO                  |      | 38    | 43       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

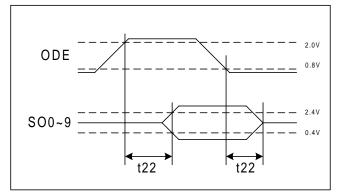

| ODE                  | I    | 39    | 44       | Output Drive Enable<br>Pin to enable the output stream bus.<br>When HIGH, SO9~0 output drivers function normally. When LOW,<br>output drivers go into high impedance state.                                                                                                                                                                                                                                                                                                                                                                                      |

| CSO                  | 0    | 40    | 1        | <b>Control ST-BUS™ Output</b><br>Pin of 2.048Mbits/s output with 256 bits per frame. The values of these bits are decided by bit CMH1 of the CMH.                                                                                                                                                                                                                                                                                                                                                                                                                |

| AS/ALE               | I    | -     | 6        | Address Strobe or Latch Enable<br>Effective only when multiplexed bus* is selected via the IM input pin.<br>The address is sampled into address latch circuit at the falling edge of this<br>input. And this pin has internal pull down resister.                                                                                                                                                                                                                                                                                                                |

| IM                   | I    | -     | 18       | <b>CPU Interface Mode</b><br>When HIGH, the device is in multiplexed microprocessor interface mode.<br>When LOW or left open, it is in non-multiplexed CPU interface mode.<br>And this pin has internal pull down resister.                                                                                                                                                                                                                                                                                                                                      |

| SI15/SO9<br>SI14/SO8 | I/O  | -     | 28<br>40 | ST-BUS <sup>™</sup> Input 15~14/ ST-BUS <sup>™</sup> Output 9~8<br>Effective only when multiplexed bus* is selected. When non-multiplexed<br>bus is selected, the pins are open.<br>When 16 × 8 switching configuration is selected, they are pins for serial<br>ST-BUS <sup>™</sup> Input streams, SI15 and SI14, with data rate of 2.048Mbits/s.<br>When Stream Pair Selection is selected, they are pins for serial ST-BUS <sup>™</sup><br>output streams, SO9 and SO8.<br>The pins have internal pull down resisters.                                        |

\* 44 pin packages only

## FUNCTIONAL DESCRIPTION

The NW1507 device, multi-rate time division switch matrix, is designed for switching 32, 64 or N×64Kbits/s data, while guaranteeing the frame integrity for wideband channels and minimum delay for voice channels. The serial streams can operate at the rate of 2.048, 4.096 or 8.192Mbits/s with 32, 64 and 128 time-slots respectively. The width of each frame is 125  $\mu$ s.

The NW1507 device can be interconnected to backplanes of various speeds like 2.048, 4.096 or 8.192Mbits/s with the use of its built-in rate conversion circuit. The device is compatible with ST-BUS and GCI interface. It can also identify the polarity of the frame synchronization input signal automatically.

Through the CPU Interface Mode input pin, both multiplexed and non-multiplexed bus interfaces can be provided in the 44 pin packages, as well as the compatibility with Intel/ National multiplexed and Motorola multiplexed/nonmultiplexed buses. In the 44 pin packages, the NW1507 device can be configured as  $16 \times 8$ , which provides a  $512 \times$ 256 channel block switching. And the Stream Pair Selection (SPS) function can be used to select which pair of input and output streams will be connected to a internal  $128 \times 128$ channel non-blocking switching.

## **BLOCK DESCRIPTION**

#### DATA MEMORY & CONNECTION MEMORY

In NW1507, there are two memories used to store data: Data Memory & Connection Memory.

Data Memory, with a capacity of 512 bytes, is used to store byte-wide data converted from input serial data stream. Each location in Data Memory is associated with a specific input stream and channel address. Data Memory can also be read by the controlling microprocessor via MCU Interface.

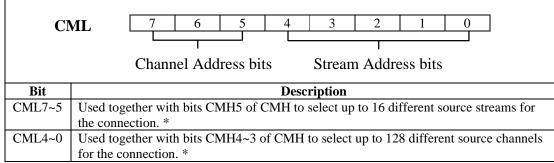

Connection Memory is used to store the switching configuration originated from the microprocessor. Each location of the Connection Memory is associated with a specific output stream and channel. Connection Memory is divided into two sections: Connection Memory Low (CML) and Connection Memory High (CMH). CML stores the address of the Data Memory, and data in the address will be transmitted to the specific output stream and channel. CMH can control if an individual output channel is placed into the high-impedance state.

#### **CONNECTION MODE**

In Connection Mode, the CMH and CML, storing the addresses of the input data, are mapped in a way which each location will correspond to an output channel. After the source address bits being programmed by CPU, the corresponding data in Data Memory will be transmitted to the parallel-to-serial converter. In the case of broadcast facility, an input channel is switched to several output channels.

It is CMH bits that control each output channel's features: constant or variable throughput delay, enable or disable the output driver. For some configuration, additional stream and channel address bits are available in the CMH. In 2.048 Mbits/s applications, one bit is provided by the CMH to control the CSO output.

By pulling the ODE input pin LOW, all output channels can be placed in high impedance. While with the CMH bits, per-channel tri-state control is achievable.

The Data Memory data comes from Serial-to-Parallel Converter, while the Connection Memory data is from control interface. All the data are addressed through the Control register bits and address input pins. The higher order address bits, capable of being written or read via MCU interface, are from the Control register, while the lower ones are from address input pins.

#### SERIAL STREAM INTERFACE

The serial data rate is usually 2.048, 4.096 or 8.194Mbits/s. Data rates must be same among input streams or output streams. While between input and output, data rates can be identical or different. Therefore, the NW1507 device can be applied in backplanes of various rates or rate conversion applications. Identical or Different I/O rates is selected by the IC7 bit in Interface Configuration Register (ICR). And then the IC2-1 bits select the switch configuration and the I/O streams number. When system power on, the IC6-3 bits are also set up.

For applications of Identical I/O rate, the master clock is at 4.096 or 8.192Mbits/s, that is, twice or equal to the data rate, which is selected by the IC0 bit in ICR. For ST-BUS or GCI format, the I/O rate is 2.048Mbits/s, the IC0 bit is set LOW to make the clock 4.096MHz, twice of the data rate. While for applications with I/O rate of 4.096 or 8.192Mbits/s, the IC0 bit is set HIGH to make the clock equal to the data rate. In applications of Different I/O rate, the IC0 bit is not used.

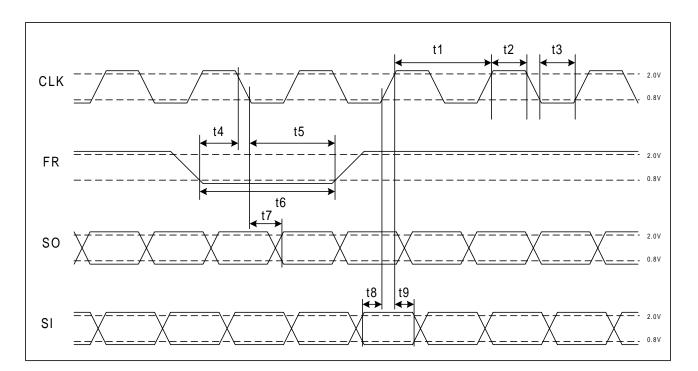

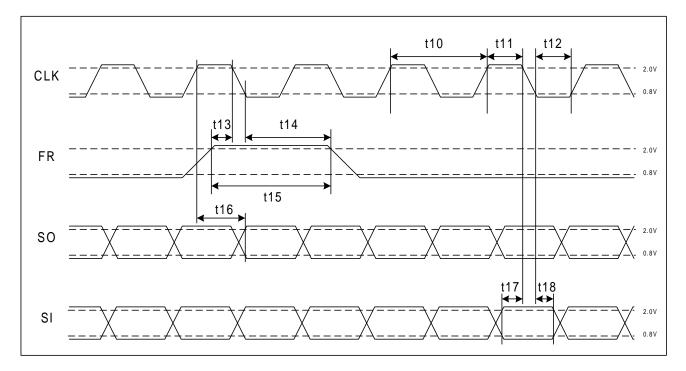

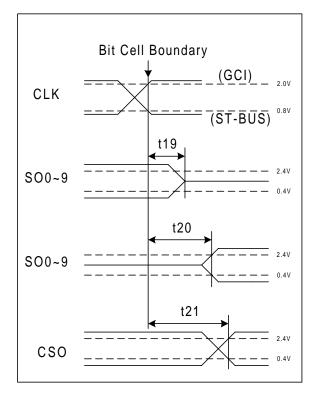

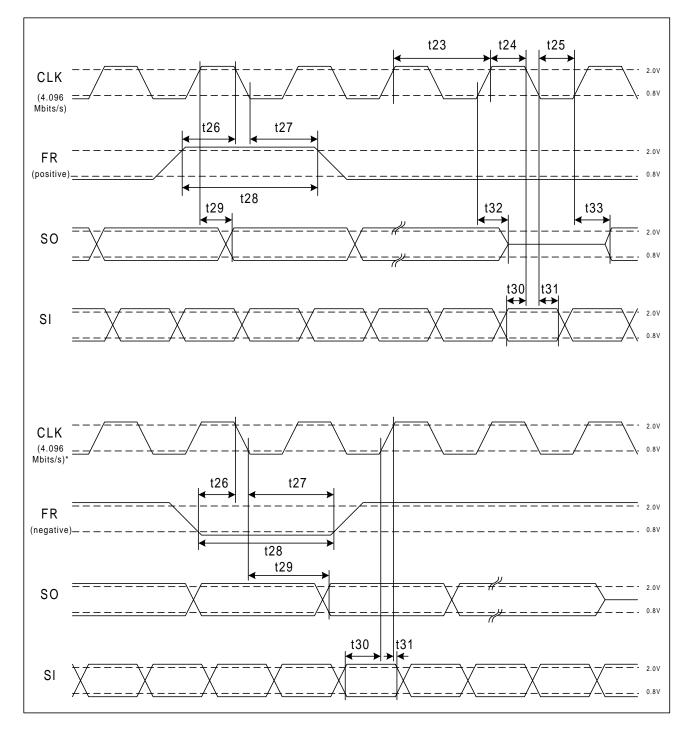

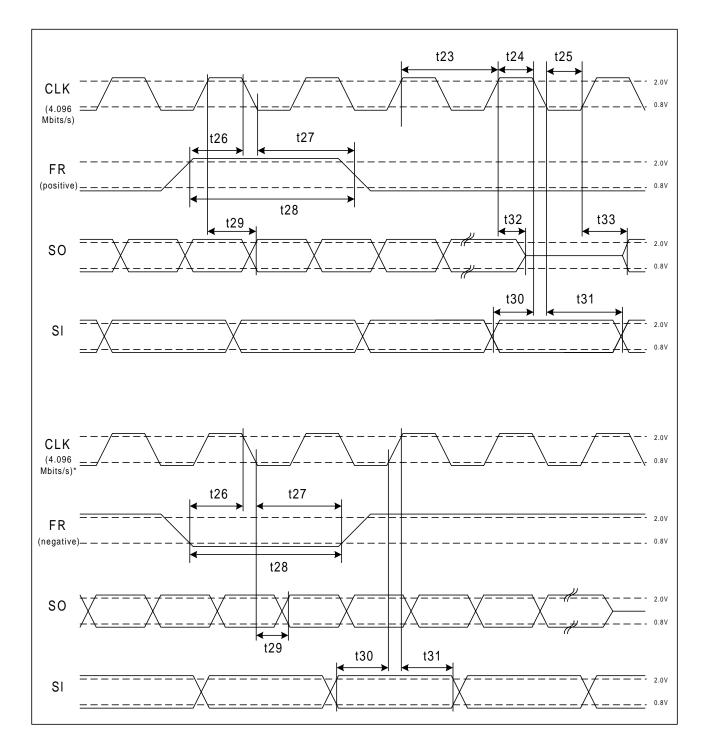

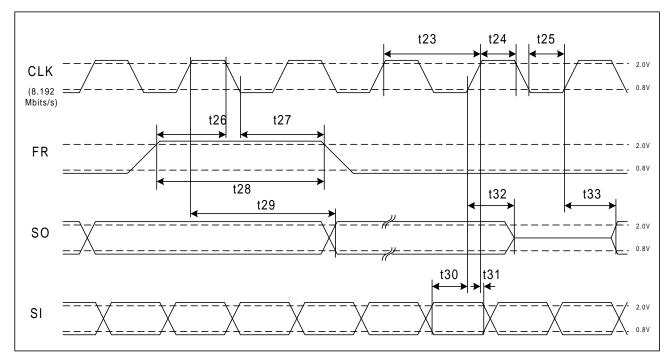

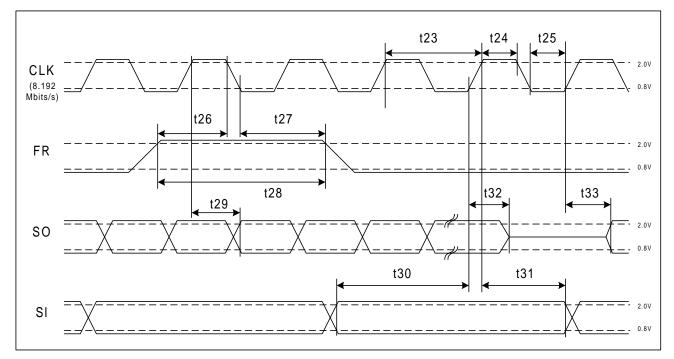

In ST-BUS or GCI format, the input frame pulse is 8kHz. The NW1507 device can automatically identify it, as well as the serial interface. According to the type of backplane on the serial interface, suitable transmit and sampling edges are established by the internal timing unit. In ST-BUS format, bit transmit operation is performed on every second falling edge of the clock, while bit sampling on the rising edge, at three-quarters of the bit boundary. In GCI format, these edges inverted.

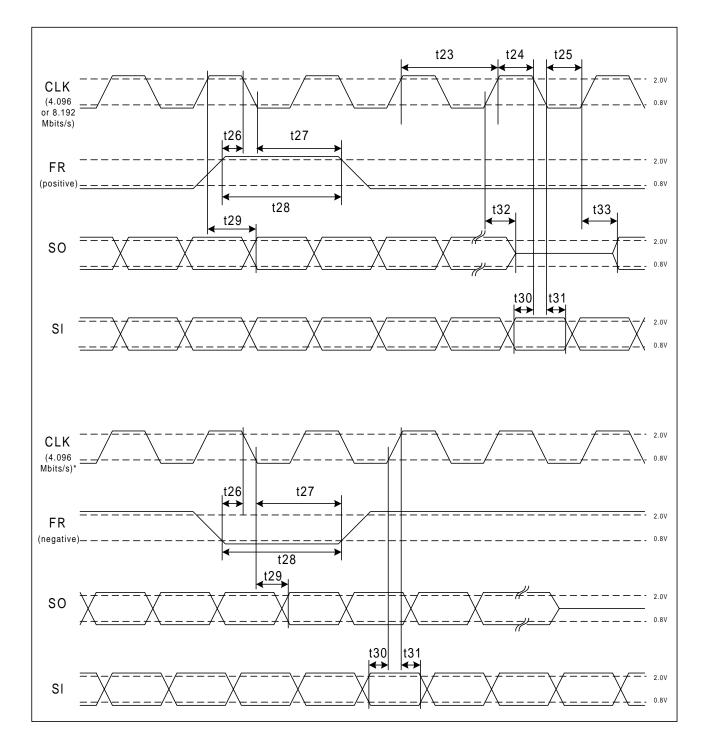

For applications of identical I/O data rate of 4.096 or 8.192Mbits/s, the interface clock is equal to the data rate. For positive frame pulse polarity, every rising edge of the clock marks the bit boundary, while data sampling is performed on every falling edge. For negative frame pulse polarity, every falling edge of the clock marks the bit boundary, while data sampling is performed on every rising edge.

For applications of different I/O data rate, in the 2.048Mbits/ s side, the transmit and sampling edges are established as in ST-BUS or GCI format; in the 4.096 or 8.192Mbits/s side, the edges vary according to the applied frame pulse polarity.

#### SWITCHING CONFIGURATIONS

Switching configurations vary according to the I/O serial rates. For identical I/O rates, the IC7 bit of the ICR is LOW, and IC2-1 bits determine the switching configuration. For different I/O rates, the IC7 bit is HIGH, and the IC6-3 bits define the switching configuration as non-blocking with different I/O stream number.

#### **Identical I/O rates**

When bit IC7 is LOW and the identical I/O rate is determined, bits IC6-5 select the I/O rate. (Bits IC4-3 are ignored.) And bits IC2-1 determine the switching configuration.

2.048Mbits/s serial rates When the I/O rate is selected to be 2.048Mbits/s by bits IC6-5, bits IC2-1 determine the switching configuration among 4 possible types:  $8 \times 8$ ,  $16 \times$ 8,  $4 \times 4$  with SPS (Stream Pair Selection), and nibble switching.

I.

- Switching configuration of 8 × 8 8 serial streams input and 8 output with 32 64Kbits/s channels each, resulting in 256 × 256 non-blocking switchings; ST-BUS and GCI format compatible; variable and constant throughput delay provided; 4.096Mbits/s master clock; 40 and 44 pin packages available.

- Switching configuration of 16 × 8

16 serial streams input and 8 output with 32

64Kbits/s channels each, resulting in 512 ×

256 blocking switchings; ST-BUS and GCI

format compatible; Multiplex bus mode

controller interface; only variable throughput

delay provided; 4.096Mbits/s master clock; 44

pin packages available.

- 3. Switching configuration of 4 × 4 with Stream Pair Selection (SPS)

4 serial streams input and 4 output. 2 pairs of

them (SI0/SO0 & SI1/SO1) are permanently linked. The other 2 pairs (Called Pair A & Pair B) are selected from the remaining 8 pairs of serial streams (SI2/SO2 to SI9/SO9) by SPS register. While CML is set, SI0~3 and SO0~3 are connected respectively.

$128 \times 128$  non-blocking switchings. ST-BUS and GCI format compatible; variable and constant throughput delay provided; 4.096Mbits/s master clock; 44 pin packages available.

4. Nibble switching

4-bit wide 32Kbits/s data is transferred on each serial stream with 64 nibbles per frame. 8 serial streams input and 4 output, resulting in  $512 \times 256$  blocking switchings. In addition, the NW1507 device can also provide  $256 \times 256$  non-blocking switchings, with any 4 of the 8 input streams selected. 4.096Mbits/s master clock.

4.096Mbits/s serial rates

II.

2 types of switching configurations are available:  $8 \times 4$  and  $4 \times 4$ .

- Switching configuration of 8 × 4 8 serial streams input and 4 output with 64 64Kbits/s channels each, resulting in 512 × 256 blocking switchings; only variable throughput delay provided; 4.096Mbits/s master clock.

- Switching configuration of 4 × 4

4 serial streams input and 4 output with 64

64Kbits/s channels each, resulting in 256 ×

256 non-blocking switchings; variable and constant throughput delay provided;

8.192Mbits/s serial rates

Only one type of switching configurations is available: 2×2. 2 serial streams input and 2 output with 128 64Kbits/s channels each, resulting in 256 × 256 non-blocking switchings. 8.192Mbits/s master clock.

| Serial<br>I/O rates<br>(Mbits/s) | Stre                | rial<br>eams<br>< O ) | I/O<br>Streams<br>Selected            | Switching<br>Matrix<br>(channels) | Blocking<br>or<br>Non-blocking | Timeslots<br>per<br>Frame | Throughput<br>Delay<br>Selection | Packages<br>(40/44<br>pin) | Master<br>Clock<br>(MHz) |

|----------------------------------|---------------------|-----------------------|---------------------------------------|-----------------------------------|--------------------------------|---------------------------|----------------------------------|----------------------------|--------------------------|

|                                  | * 8 × 8<br>* 16 × 8 |                       | SI0~7/<br>SO0~7                       | 256 × 256                         | Non-blocking                   |                           | Variable &<br>Constant           | 40 & 44<br>pin             |                          |

| • • • •                          |                     |                       | * 16 × 8 SI0~15/<br>SO0~7 512 × 256 B |                                   | Blocking                       | 32                        | Variable<br>Only                 | 44 pin<br>only             | 1005                     |

| 2.048                            | ** 10 × 10          | 0 × 10                | SI0~9/<br>SO0~9                       | 128 × 128                         | Non-blocking                   |                           | Variable &<br>Constant           | 44 pin<br>only             | 4.096                    |

|                                  | Nibble              | $8 \times 4$          | SI0~7/                                | $512 \times 256$                  | Blocking                       | 64                        | Variable                         | 40 & 44                    |                          |

|                                  | Switch              | *** $8 \times 4$      | SO0~3                                 | $256 \times 256$                  | Non-blocking                   | nibbles                   | Only                             | pin                        |                          |

| 4.006                            | 8>                  | × 4                   | SI0~7/<br>SO0~3                       | 512 × 256                         | Blocking                       | 64                        | Variable<br>Only                 | 40 & 44<br>pin             | 4.096                    |

| 4.090                            | 4.096 4 × 4         |                       | SI0~3/<br>SO0~3                       | 256 × 256                         | Non-blocking                   | 64                        | Variable &<br>Constant           | 40 & 44<br>pin             | 4.090                    |

| 8.192                            | 2 >                 | × 2                   | SI0~1/<br>SO0~1                       | 256 × 256                         | Non-blocking                   | 128                       | Variable &<br>Constant           | 40 & 44<br>pin             | 8.192                    |

III.

\* ST-BUS and GCI interface compatible

\*\* Only 4 input  $\times$  4 output will be selected by SPS

\*\*\* Only 4 of the 8 input streams are selected

#### Table-1. Switching Configurations for identical I/O rates

#### **Different I/O rates**

After bit IC7 in ICR determine the different I/O rates, bits IC6-5 select the input data rates, while bits IC4-3 select the output. (Bits IC2-1 are ignored.) The NW1507 device can convert 2.048Mbits/s serial data into 4.096Mbits/s or 8.192Mbits/s, and vice-versa.

$256 \times 256$  non-blocking switchings are provided, and also the per-channel selection between variable and constant throughput delay.

4 types of switching configurations are available with different master clock and different input stream number and output stream number. *As the following table*

| Input<br>Rate<br>(Mbits/s) | Output<br>Rate<br>(Mbits/s) | Serial<br>Streams<br>(I × O)      | Input<br>Streams<br>Selected | Output<br>Streams<br>Selected | Switching<br>Matrix<br>(channels) | Blocking<br>or<br>Non-blocking | Throughput<br>Delay<br>Selection | Master<br>Clock<br>(MHz) |

|----------------------------|-----------------------------|-----------------------------------|------------------------------|-------------------------------|-----------------------------------|--------------------------------|----------------------------------|--------------------------|

| 2.048<br>2.048             | 4.096<br>8.192              | $\frac{(1 \times 0)}{8 \times 4}$ | SI0-7<br>SI0-7               | SO0-3<br>SO0-1                | (enumers)                         |                                | Variable                         | 4.096                    |

| 4.096                      | 2.048                       | $\frac{8 \times 2}{4 \times 8}$   | SI0-7<br>SI0-3               | SO0-1<br>SO0-7                | 256 × 256                         | Non-blocking                   | &<br>Constant                    | 4.096                    |

| 8.192                      | 2.048                       | $2 \times 8$                      | SI0-1                        | SO0-7                         |                                   |                                | Constant                         | 8.192                    |

#### Table-2. Switching Configurations for different I/O rates

#### **Input Frame Offset Selection**

Because of different backplanes applied, different delay occurs to the input serial data. That is, the serial data are input a little bit later than the frame synchronization signals.

To offset the delay, the function, Input Frame Offset Selection, is offered by the NW1507 device, while the serial interface is at 4.096Mbits/s or 8.192Mbits/s. In this operation, depending on the CPU in the Frame Input Offset Register (FIOR), an internal delay of up to 4 clock periods is added to the input serial data sampling, so as to create a new input frame reference, aligning with the framing of input data.

Meanwhile the frame of the output data is still aligned with the original system frame synchronization. And this function also can be disabled by the FIOR.

#### THROUGHPUT DELAY

Delay occurs when data pass through the switch matrix. To cover it, the NW1507 provides 2 types of throughput delay: one is Variable Delay, provided for voice data to ensure minimum delay; the other is Constant Delay, provided for wideband data to guarantee the frame integrity.

Bit CMH6 of the CMH determines the type of the throughput delay. When bit CMH6 = 0, Variable Delay is selected. When bit CMH6 = 1, Constant Delay is selected.

I. In Variable Mode

> For identical I/O Data Rates, it is the input and output channels that determine the throughput delay, while the serial data rate determine the achievable minimum delay. If the throughput delay is more than the minimum, it must be equal to the difference of the input & output channels. Details can be found in Table-3.

For different I/O Data Rates, the throughput delay is determined by the output streams in cases of 4.096 to 2.048Mbits/s and 8.192 to 2.048Mbits/s rate conversions, and by input streams in cases of 2.048 to 4.096Mbits/s and 2.048 to 8.192Mbits/s. Details can be found in Table-4 & 5.

II. In Constant Mode

> Multiple Data-Memory buffers are used to maintain the data sequence integrity. Suppose the data is written in the buffers during frame n, it will be read out during frame n+2. Therefore, the throughput delay is ranged from 1 frame to (3 frames - 2)timeslots). Details can be found in Table-6:

| I/O               | Timeslot      | Minimum              | Throughput Delay Value (timeslots) |              |           |                 |        |  |  |  |

|-------------------|---------------|----------------------|------------------------------------|--------------|-----------|-----------------|--------|--|--|--|

| Rate<br>(Mbits/s) | Value<br>(µs) | Delay<br>(timeslots) | dc < 0                             | dc = 0, 1, 2 | dc = 3, 4 | dc = 5, 6, 7, 8 | dc > 8 |  |  |  |

| 2.048             | 3.9           | 3                    | 32 + dc                            | 32 + dc      | dc        | dc              | dc     |  |  |  |

| 4.096             | 1.95          | 5                    | 64 + dc                            | 64 + dc      | 64 + dc   | dc              | dc     |  |  |  |

| 8.192             | 0.975         | 9                    | 128 + dc                           | 128 + dc     | 128 + dc  | 128 + dc        | dc     |  |  |  |

\* dc(difference of the output & input channels) = output channel - input channel

| Input<br>Rate | Output<br>Rate | Throughput<br>Delav | hroughput Output Streams |            |            |           |  |  |  |

|---------------|----------------|---------------------|--------------------------|------------|------------|-----------|--|--|--|

| (Mbits/s)     | (Mbits/s)      | (μs)                | 0, 1                     | 2, 3       | 4, 5       | 6, 7      |  |  |  |

| 2.048         | 4.006          | Maximum             |                          | 4          | b + d      |           |  |  |  |

| 2.048         | 4.096          | Minimum             |                          |            |            |           |  |  |  |

| 2.049         | 9 102          | Maximum             | 8a + d                   |            |            |           |  |  |  |

| 2.048         | 8.192          | Minimum             |                          |            | 9a         |           |  |  |  |

| 1.006         | 2.049          | Maximum             | 2                        | c + d      | c + b + d  |           |  |  |  |

| 4.096         | 2.048          | Minimum             |                          | 3c         | 2c +       | b         |  |  |  |

| 9 102         | 2.049          | Maximum             | 2c + d                   | c + 3a + d | c + 2a + d | c + a + d |  |  |  |

| 8.192 2.048   |                | Minimum             | 3c                       | 2c + 3a    | 2c + 2a    | 2c + a    |  |  |  |

#### Table-3. Variable Delay Values for identical I/O rates

8Mbits/s timeslot =  $0.975\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; c = 2Mbits/s timeslot =  $3.9\mu$ s; d = 1fr. =  $125\mu$ s

#### Table-4. Variable Delay Values for different I/O rates (with SO)

| Input<br>Rate | Output<br>Rate | Throughput<br>Delay | Delay Input Streams |           |            |           |  |  |  |

|---------------|----------------|---------------------|---------------------|-----------|------------|-----------|--|--|--|

| (Mbits/s)     | (Mbits/s)      | (µs)                | 0, 1                | 2, 3      | 4, 5       | 6, 7      |  |  |  |

| 2.048         | 4.096          | Maximum             | 2                   | c + d     | c + b -    | + d       |  |  |  |

| 2.048         | 4.090          | Minimum             |                     | 3c        | 2c +       | b         |  |  |  |

| 2.048         | 9 102          | Maximum             | 2c + d              | c + 3a +d | c + 2a + d | c + a + d |  |  |  |

| 2.048         | 8.192          | Minimum             | 3c                  | 2c + 3a   | 2c + 2a    | 2c + a    |  |  |  |

| 4.096         | 2.048          | Maximum             |                     | 4         | b + d      |           |  |  |  |

| 4.090         | 2.048          | Minimum             |                     | 5b        |            |           |  |  |  |

| 8.192         | 2.048          | Maximum             | 8a + d              |           |            |           |  |  |  |

| 0.192         | 2.048          | Minimum             | 9a                  |           |            |           |  |  |  |

\* a = 8Mbits/s timeslot =  $0.975\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; c = 2Mbits/s timeslot =  $3.9\mu$ s; d = 1fr. =  $125\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; c = 2Mbits/s timeslot =  $3.9\mu$ s; d = 1fr. =  $125\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; c = 2Mbits/s timeslot =  $3.9\mu$ s; d = 1fr. =  $125\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; c = 2Mbits/s timeslot =  $3.9\mu$ s; d = 1fr. =  $125\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; c = 2Mbits/s timeslot =  $3.9\mu$ s; d = 1fr. =  $125\mu$ s; b = 4Mbits/s timeslot =  $1.95\mu$ s; b =  $1.95\mu$ ; b =  $1.95\mu$ s; b =  $1.95\mu$ ; b =  $1.95\mu$ ;

#### Table-5. Variable Delay Values for different I/O rates (with SI)

| Serial Rate<br>(Mbits/s)           | 2.048                   | 4.096                   | 8.192                     |  |  |

|------------------------------------|-------------------------|-------------------------|---------------------------|--|--|

| Timeslot Value<br>(µs)             | 3.9                     | 1.95                    | 0.975                     |  |  |

| Throughput<br>Delay<br>(timeslots) | (32 – i) + 32 + (o - 1) | (64 - i) + 64 + (o - 1) | (128 - i) + 128 + (o - 1) |  |  |

| Range of i & o                     | 1 ~ 32                  | 1 ~ 64                  | 1 ~ 128                   |  |  |

\* i: input timeslot; o: output timeslot

#### **Table-6. Constant Delay Values**

#### **MCU Interface**

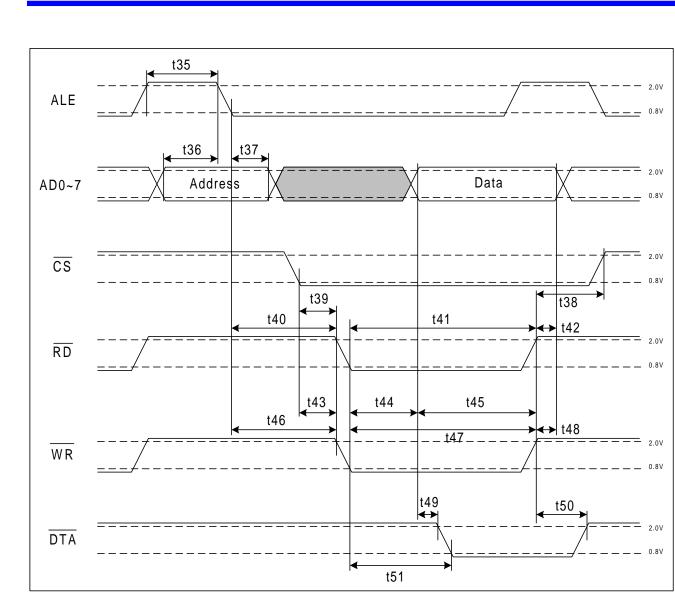

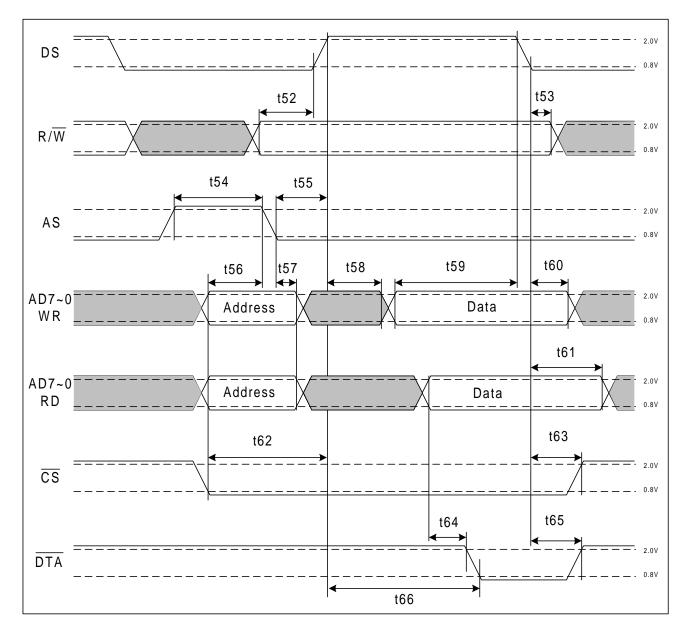

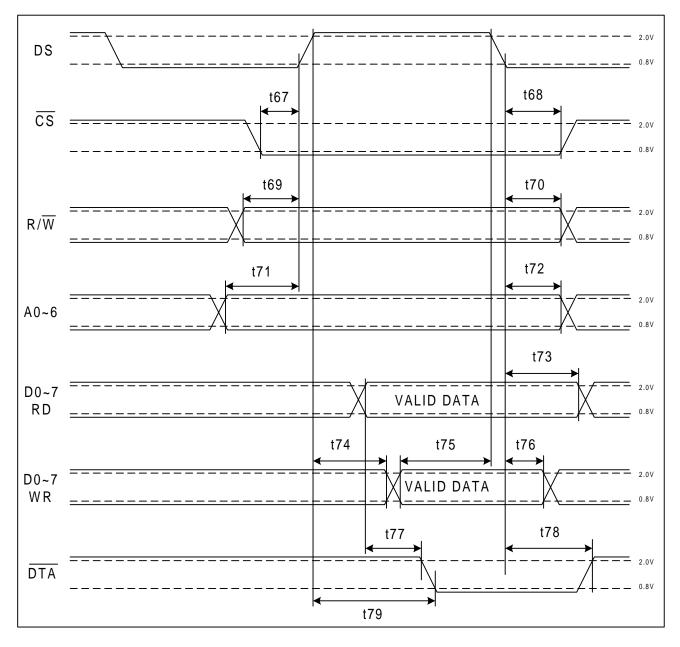

In the 44 pin packages, the NW1507 device provides both non-multiplexed bus interface and multiplexed bus interface, which is determined by the CPU Interface Mode (IM) input pin. When the pin is open or grounded, non-multiplexed bus interface is provided compatible to Motorola CPUs; when it is connected to HIGH, multiplexed bus interface is provided compatible to Motorola, National and Intel CPUs.

The type of CPU bus connected is automatically identified by the MOTEL circuit (Motorola and Intel compatible bus) with the use of  $DS/\overline{RD}$  input pin. While the level of the pin is LOW at the rising edge of AS/ALE, the Motorola bus timing is selected. While it is HIGH, the Intel bus timing is selected.

While Motorola, National or Intel multiplexed bus interfaces are used, following signals are available for controlling the NW1507 device: AD7~0, AS/ALE, DS/RD, R/W\WR,  $\overline{CS}$  and  $\overline{DTA}$ . While Motorola non-multiplexed bus interfaces

are used, following signals are available for controlling the NW1507 device: AD7~0, A0~5, DS/ $\overline{RD}$ , R/ $\overline{W}$ \ $\overline{WR}$ ,  $\overline{CS}$  and  $\overline{DTA}$ .

Via the bus interfaces, the CPU can set connection to Data Memory, Connection Memory, Control Registers, Interface Configuration Register. The Data Memory can be read only, while the others can be both read and written.

#### SOFTWARE CONTROL DESCRIPTION

Address input pins A7~0 determine the internal registers and memories. When A5 is LOW, the combination of A1 and A0 determines the Internal Registers: Internal Control, Interface Mode, Stream Pair Selection and Frame Input Offset registers. When A5 is HIGH, all the other address input pins participate in determining the memory subsections, which is up to 128 locations specifying the input and output channels. *Details can be found in Table-7*.

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Internal Registers / Memory Locations |

|----|----|----|----|----|----|----|----|---------------------------------------|

| ×  | ×  | 0  | ×  | ×  | ×  | 0  | 0  | Control Register                      |

| ×  | ×  | 0  | ×  | ×  | ×  | 0  | 1  | Interface Mode Select Register        |

| ×  | ×  | 0  | ×  | ×  | ×  | 1  | 0  | Stream Pair Select Register           |

| ×  | ×  | 0  | ×  | ×  | ×  | 1  | 1  | Frame Input Offset Register           |

|    |    |    | 0  | 0  | 0  | 0  | 0  | Channel 0                             |

| 0  | 0  | 1  | ſ  | ſ  | ſ  | ſ  | ſ  | ſ                                     |

|    |    |    | 1  | 1  | 1  | 1  | 1  | Channel 31                            |

|    |    |    | 0  | 0  | 0  | 0  | 0  | Channel 32                            |

| 0  | 1  | 1  | ſ  | ſ  | ſ  | ſ  | ſ  | ſ                                     |

|    |    |    | 1  | 1  | 1  | 1  | 1  | Channel 63                            |

|    | 0  |    | 0  | 0  | 0  | 0  | 0  | Channel 64                            |

| 1  | ∫  | 1  | ſ  | ſ  | ſ  | ſ  | ſ  | ſ                                     |

|    | 1  |    | 1  | 1  | 1  | 1  | 1  | Channel 127                           |

\* Channel 0~31 are applied in 2.048Mbits/s ( $8 \times 8$ ,  $16 \times 8$  and  $10 \times 10$ )

\* Channel 0~63 are applied in 4.096Mbits/s (4 × 4, 8 × 4, nibble or different I/O rates)

\* Channel 0~127 are applied in 8.192Mbits/s ( $2 \times 2$  or different I/O rates)

Address input pins and bits of the Control Register determine all sections of the Data Memory and Connection Memory HIGH & LOW.

Bits of the Control Register are divided into 4 types: Split Memory bits, Connection Mode bits, Memory Select bits and Stream Address bits. *Details can be found in Figure 3*.

Bit CR7 of the Control Register, Split Memory bit, determines the split memory operation: reading from the Data Memory and writing to Connection Memory LOW.

Bits CR4 & CR3, Memory Select bits, determine the selection of the Data Memory, the Connection Memory HIGH and LOW.

Bits CR5 and CR2~1, Stream Address bits, determine the memory subsections specifying the input and output channels.

Bit CR6, Connection Mode bit, determines the content of output channels when it is LOW.

When ODE input pin is LOW, all the output channels are in high impedance. When ODE is HIGH, bits CMH0 of the CMH determine the output drivers for the output stream and channel related.

Bit CMH1 of the CMH is only available in 2.048Mbits/s applications. The content of the bit is transmitted on to the CSO pin, synchronous to the ST-BUS stream. When bit CMH1 is HIGH, the related bit on CSO pin is transmitted HIGH. When it is LOW, the related bit is also LOW. The content of the bit is transmitted one channel before the related channel on the output streams.

Bit CMH6 determines Variable and Constant throughput delay modes on per channel basis. *Details can be found in Figure 4a*.

|                                    | Bit               | State        | Description                                                                                                                                                            |

|------------------------------------|-------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | CD7               | 0            | Memory Select bit specifies the memory for subsequent operation                                                                                                        |

| 7 — Split Memory bit<br>Connection | CR7               | 1            | All reads are from Data Memory, while writes are to CML if CR3=0, or to CMH if CR3=1                                                                                   |

| 6 Mode bit<br>5 – Stream Address   | CR6               | 0            | The Connection Memory bits determine the content of output channel related                                                                                             |

| bit                                | CKO               | 1            | Reserved                                                                                                                                                               |

| Memory Select<br>3 bits            | CR5               |              | It is only used in $16 \times 8$ switching configuration of 44 pin packages. With bits CR2~0, it can determine the input serial stream selection.                      |

|                                    | CD 4              | $0 \times 0$ | Undefined                                                                                                                                                              |

|                                    | CR4               | $0 \times 1$ | For selection of Data Memory (if read)                                                                                                                                 |

| 1 – Stream Address                 | ×<br>CR3          | $1 \times 0$ | For selection of CML                                                                                                                                                   |

| bits                               | CKJ               | $1 \times 1$ | For selection of CMH                                                                                                                                                   |

|                                    | CR2<br>CR1<br>CR0 |              | These bits expressed in binary notation indicate the input or<br>output streams corresponding to the subsection of memory<br>made accessible for subsequent operations |

## **Figure-3.** Control Register Bits

|                       | CMI | T                   | Bit          | Description                                                                                                                                 |

|-----------------------|-----|---------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                       |     | ת<br>               | CMH7         | Unused                                                                                                                                      |

| bit                   | 6   | Delay<br>Mode       | CMH6         | Providing per-channel selection of Variable/Constant Throughput<br>Delay Mode while the switching configuration has this function.          |

|                       | - 5 | Mc                  | CMH5         | Used together with bits CML7~5 of CML to select up to 16 different source streams for the connection. *                                     |

| Stream<br>Address     | 4   | nel<br>s bit        | CMH4<br>CMH3 | Used together with bits CML4~0 of CML to select up to 128 different source channels for the connection. *                                   |

|                       | 3   | Channel<br>ddress b | CMH2         | No effect                                                                                                                                   |

|                       | 2   | A                   | CMH1         | Available only in 2.048Mbits/s applications. The content of this bit is output sequentially on to the CSO pin, one channel earlier than the |

| Output<br>Enable<br>I | 1   | CSO<br>bit          |              | related channel on the ST-BUS streams.<br>Effective only when CR6 is LOW. When '1', the output driver of the                                |

|                       | 0   |                     | CMH0         | location's channel and stream is enabled. When '0', the individual channel on individual stream is made high-impedance.                     |

\* Depending the switching configuration and the data rate used in the application, not all the bits have to be used. *Details can be found in table 9 & 10.*

**Figure-4a. Connection Memory High Bits**

\* Depending the switching configuration and the data rate used in the application, not all the bits have to be used. *Details can be found in table 9 &10*.

| Figure 4h  | Connection | Momony | Low Dita |

|------------|------------|--------|----------|

| Figure-40. | Connection | Memory | LOW BITS |

| Device Main                    | Bit        | Description                                                             | State                           | Selection          |  |

|--------------------------------|------------|-------------------------------------------------------------------------|---------------------------------|--------------------|--|

| Operation bit — 7              | IC7        | Used to determine Identical or                                          | 0                               | Identical I/O rate |  |

|                                | IC /       | Different I/O data rate.                                                | 1                               | Different I/O rate |  |

| Input Data Rate 6              | ICC        | Used to determine the input data                                        | $0 \times 0$                    | 2.048Mbits/s       |  |

| Selection bits 5               | IC6        | rate. And also determine the                                            | $0 \times 1$                    | 4.096Mbits/s       |  |

| -                              | ×<br>IC5   | output data rate when IC7 is                                            | $1 \times 0$                    | 8.192Mbits/s       |  |

| Output Data<br>Rate Selection4 | IC.J       | LOW.                                                                    | $1 \times 1$                    | Undefined          |  |

|                                | TOA        |                                                                         | $0 \times 0$                    | 2.048Mbits/s       |  |

| bits L 3                       | IC4        | Used to determine the output data<br>rate. It is not effective when IC7 | $0 \times 1$                    | 4.096Mbits/s       |  |

| Switching - 2                  | ×<br>IC3   | is LOW.                                                                 | $1 \times 0$                    | 8.192Mbits/s       |  |

| Configuration —                | 10.5       | IS LOW.                                                                 | $1 \times 1$                    | Undefined          |  |

| bits                           | IC2<br>IC1 | It is effective only when IC7 is LOW.                                   | Details can be found in Table-1 |                    |  |

| Clock Mode bit $-0$            | IC0        | No effect.                                                              |                                 |                    |  |

**Figure-5. Interface Configuration Register**

|                                                                                    | Bit          |                                                                            |      | Γ    | Descriptio | on                      |

|------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------|------|------|------------|-------------------------|

|                                                                                    | SPS7<br>SPS6 | Ignored                                                                    |      |      |            |                         |

|                                                                                    |              |                                                                            | SPS5 | SPS4 | SPS3       | Stream Pair A Connected |

| 7                                                                                  |              | Besides the                                                                | 0    | 0    | 0          | SI2/SO2                 |

|                                                                                    |              | two pairs of                                                               | 0    | 0    | 1          | SI3/SO3                 |

| 9 bits                                                                             | SPS5         | permanently                                                                | 0    | 1    | 0          | SI4/SO4                 |

|                                                                                    | SPS4         | connected                                                                  | 0    | 1    | 1          | SI5/SO5                 |

| <sup>.</sup>                                                                       | SPS3         | streams<br>SI1/SO1 &<br>SI0/SO0,<br>another two<br>pairs of<br>streams are | 1    | 0    | 0          | SI6/SO6                 |

| ele ele                                                                            |              |                                                                            | 1    | 0    | 1          | SI7/SO7                 |

| $\begin{bmatrix} \infty \\ \nabla \end{bmatrix} = \begin{bmatrix} 4 \end{bmatrix}$ |              |                                                                            | 1    | 1    | 0          | SI8/SO8                 |

|                                                                                    |              |                                                                            | 1    | 1    | 1          | SI9/SO9                 |

| Stream Pair.                                                                       |              |                                                                            | SPS2 | SPS1 | SPS0       | Stream Pair B Connected |

| Stream 5                                                                           |              | selected                                                                   | 0    | 0    | 0          | SI2/SO2                 |

| Stre                                                                               |              | respectively                                                               | 0    | 0    | 1          | SI3/SO3                 |

| -                                                                                  | SPS2         | from the                                                                   | 0    | 1    | 0          | SI4/SO4                 |

| L B                                                                                | SPS1         | remaining                                                                  | 0    | 1    | 1          | SI5/SO5                 |

| Pair 0                                                                             | SPS0         | streams                                                                    | 1    | 0    | 0          | SI6/SO6                 |

| Stream                                                                             |              | SI2~9/SO2~9.                                                               | 1    | 0    | 1          | SI7/SO7                 |

| trea                                                                               |              | *                                                                          | 1    | 1    | 0          | SI8/SO8                 |

| Ň                                                                                  |              |                                                                            | 1    | 1    | 1          | SI9/SO9                 |

\* These bits are only effective while 2.048Mbits/s data rate is selected and bit IC2 = 1 & bit IC1 = 0.

Figure-6. SPS Register Bits

|                | Bit          |                                                                                                                   | Descri | ption |      |               |  |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------|--------|-------|------|---------------|--|

| pits           |              |                                                                                                                   | FIO7   | FIO6  | FIO5 | Number of     |  |

| 6 et 1         |              | Depending on these bits,                                                                                          |        |       |      | Clock Periods |  |

| 0 Uffset       |              | an internal delay of up to                                                                                        | 0      | 0     | 0    | 0             |  |

|                | EIO7         | 4 clock periods to the                                                                                            | 0      | 0     | 1    | 1             |  |

| 4              | FIO7         | actual data input<br>sampling, to create an<br>virtual frame aligning<br>with the input serial data<br>framing. * | 0      | 1     | 0    | 2             |  |

| 3              | FIO6<br>FIO5 |                                                                                                                   | 0      | 1     | 1    | 3             |  |

| 2              | FIUS         |                                                                                                                   | 1      | 0     | 0    | 4             |  |

|                |              |                                                                                                                   | 1      | 0     | 1    | Undefined     |  |

| 1              |              |                                                                                                                   | 1      | 1     | 0    | Undefined     |  |

| 0              |              |                                                                                                                   | 1      | 1     | 1    | Undefined     |  |

| FIO4~0 Ignored |              |                                                                                                                   |        |       |      |               |  |

FIO4~0 | Ignored \* If this function is not required, the register should be set up during system initialization to a state where offset function are disabled.

## Figure-7. FIO Register Bits

| Serial<br>I/O rates<br>(Mbits/s) | Serial<br>Streams<br>(I × O) | Bits for Data<br>Memory<br>subsections<br>selection | Bits for Connection<br>Memory<br>subsections<br>selection | Input Address pins for<br>individual Data &<br>Connection Memory<br>positions access |

|----------------------------------|------------------------------|-----------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                  | $8 \times 8$                 | SA2~0                                               | SA2~0                                                     | A4~0                                                                                 |

| 2.048                            | * 4 × 4                      | SA1~0                                               | SA1~0                                                     | A4~0                                                                                 |

|                                  | * 16 × 8                     | SA3~0                                               | SA2~0                                                     | A4~0                                                                                 |

| 2.048 (Nibble)                   | $8 \times 4$                 | SA2~0                                               | SA1~0                                                     | A6, A4~0                                                                             |

| 4.096                            | $4 \times 4$                 | SA1~0                                               | SA1~0                                                     | A6, A4~0                                                                             |

| 4.090                            | $8 \times 4$                 | SA2~0                                               | SA1~0                                                     | A6, A4~0                                                                             |

| 8.192                            | $2 \times 2$                 | SA0                                                 | SA0                                                       | ** A7~6, A4~0                                                                        |

\* Available only in 44 pin package

\*\* Pin A0 is not required for Data Memory Read operations

#### Table-8. Use of Stream Address Bits for Identical I/O Data Rate Operation

| Input<br>Serial<br>Rate<br>(Mbits/s) | Output<br>Serial<br>Rate<br>(Mbits/s) | Serial<br>Streams<br>(I × O) | Bits for<br>Data<br>Memory<br>subsections<br>selection | Bits for<br>Connection<br>Memory<br>subsections<br>selection | Input Address<br>pins for<br>individual Data<br>Memory<br>positions access | Input Address<br>pins for individual<br>Connection<br>Memory positions<br>access |

|--------------------------------------|---------------------------------------|------------------------------|--------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.048                                | 4.096                                 | $8 \times 4$                 | SA2~0                                                  | SA1~0                                                        | A4~0                                                                       | A7~6, A4~0                                                                       |

| 2.048                                | 8.192                                 | $8 \times 2$                 | SA2~0                                                  | SA0                                                          | A4~0                                                                       | A6, A4~0                                                                         |

| 4.096                                | 2.048                                 | $4 \times 8$                 | SA1~0                                                  | SA2~0                                                        | A6, A4~0                                                                   | A4~0                                                                             |

| 8.192                                | 2.048                                 | $2 \times 8$                 | SA0                                                    | SA2~0                                                        | A7~6, A4~0                                                                 | A4~0                                                                             |

## Table-9. Use of Stream Address Bits for Different I/O Data Rate Operation

| Bit IC7             | Data Rate<br>(Mbits/s) | IC2       | IC1 | Switching<br>Configuration | Blocking/<br>Non-blocking |

|---------------------|------------------------|-----------|-----|----------------------------|---------------------------|

|                     |                        | 0         | 0   | 8 × 8                      | Non-blocking              |

|                     | 2.048                  | 0         | 1   | ** 16 × 8                  | Blocking                  |

|                     | 2.048                  | 1         | 0   | ** 4 × 4 (with SPS)        | Non-blocking              |

| * IC7 = 0,          |                        | 1         | 1   | $8 \times 4$ (Nibble)      | Blocking                  |

| Identical I/O rates | 4.096                  | 0         | 0   | $8 \times 4$               | Blocking                  |

| determined.         |                        | 0         | 1   | $4 \times 4$               | Non-blocking              |

|                     |                        | 1         | 0   | Undefine                   | ed                        |

|                     |                        | 1         | 1   | Undefine                   | ed                        |

|                     | 8.192                  | No effect |     | $2 \times 2$               | Non-blocking              |

\* When IC7 = 1, different I/O rates is determined, the Switching Configurations bits are not effective, and the device is in Non-blocking switch configuration with a  $256 \times 256$  channel capacity.

\*\* Available only in 44 pin packages.

## Table-10. Switching Configurations Bits for Identical I/O Rates

| Serial<br>I/O Rate<br>(Mbits/s) | Serial<br>Streams<br>(I × O) | Source Stream<br>Address Bits<br>used | Source Channel<br>Address Bits<br>used | Source channels<br>determined<br>(channels/stream) |  |

|---------------------------------|------------------------------|---------------------------------------|----------------------------------------|----------------------------------------------------|--|

|                                 | $8 \times 8$                 | CML7~5                                |                                        |                                                    |  |

| 2.048                           | * 4 × 4                      | CML7~6                                | CML4~0                                 | 32                                                 |  |

|                                 | * 16 × 8                     | CMH5, CML7~5                          |                                        |                                                    |  |

| Nibble Switch<br>(2.048)        | $8 \times 4$                 | CML7~5                                | CMH3<br>CML4~0                         | 64                                                 |  |

| 4.096                           | $4 \times 4$                 | CML7~6                                | CMH3                                   | 64 (nibbles/stream)                                |  |

| 4.090                           | $8 \times 4$                 | CML7~5                                | CML4~0                                 | 64 (nibbles/stream)                                |  |

| 8.192                           | $2 \times 2$                 | CML7                                  | CMH4~3<br>CML4~0                       | 128                                                |  |

\* Available only in 44 pin package

| Input<br>Serial Rate<br>(Mbits/s) | Output<br>Serial Rate<br>(Mbits/s) | Serial<br>Streams<br>(I × O) | Source Stream<br>Address Bits<br>used | Source Channel<br>Address Bits<br>used | Source channels<br>determined<br>(channels/stream) |  |

|-----------------------------------|------------------------------------|------------------------------|---------------------------------------|----------------------------------------|----------------------------------------------------|--|

| 2.048                             | 4.096                              | $8 \times 4$                 | CML7~5                                | CML4~0                                 | 20                                                 |  |

| 2.048                             | 8.192                              | $8 \times 2$                 | CML7~5                                | CIVIL4~0                               | 32                                                 |  |

| 4.096                             | 2.048                              | $4 \times 8$                 | CML7~6                                | CMH3, CML4~0                           | 64                                                 |  |

| 8.192                             | 2.048                              | $2 \times 8$                 | CML7                                  | CMH4~3, CML4~0                         | 128                                                |  |

Table 12. Stream & Channel Address Bits used for Different I/O Rate Applications

## **Application Information**

## **Switch Matrices**

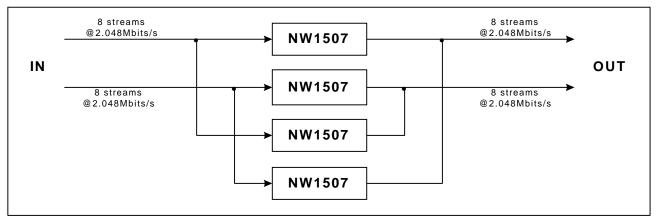

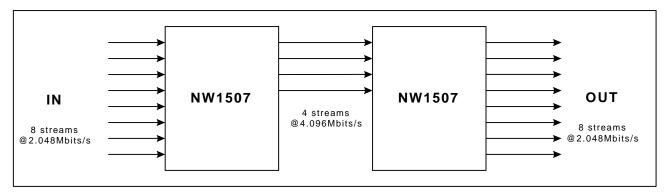

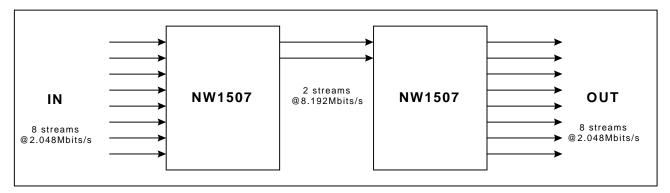

While guaranteeing the integrity of grouped data and mini-

mum delay for voice, the NW1507 device can provides nonblocking switch matrices of up to 512 channels with different connections at different data rates. *Examples see Figure*  $8 \sim 10$ .

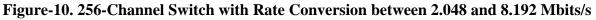

## Figure-8. 512-Channel Switch with Data Rate at 2.048 and 4.096 Mbits/s

## Figure-9. 256-Channel Switch with Rate Conversion between 2.048 and 4.096 Mbits/s

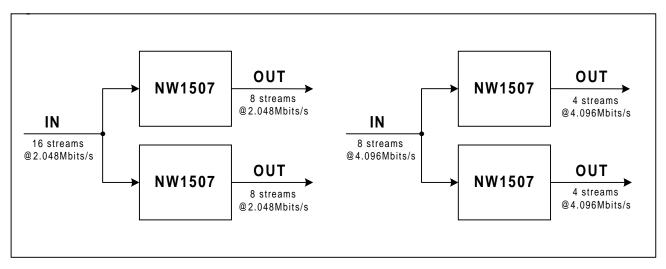

Furthermore, the NW1507 device can also provide nonblocking matrices of up to 1024 channels, while only variable throughput delay is guaranteed. *Examples see Figure 11~12*.

Figure-11. 512-Channel Non-Blocking Switch Matrix with Data Rate at 2.048 or 4.096Mbits/s

#### **Interfacing Microcontroller 8051**

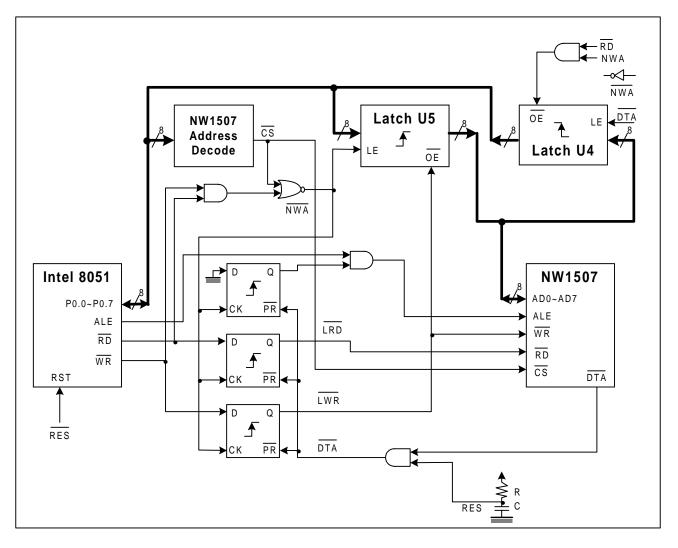

In applications where the NW1507 device is connected to Intel 8051, some external logic are necessary to be provided in the connection to allow read/write operation. *The typical application diagram see Figure-13*.

When reading or writing to NW1507, the address decoded signal  $\overline{(NWA)}$  latches signals  $\overline{RD}$ ,  $\overline{WR}$  and ALE, and releases it when NW1507 output the  $\overline{DTA}$  signal. During a write, Latch U5 stores the 8051 data when  $\overline{DTA}$  goes low.

During a read, Latch U4 stores NW1507 output data when DTA goes low.

One write operation is enough when writing to NW1507, while two read operations are required when reading (only the second operation is valid).

Sufficient time should be guaranteed between two CPU accesses to allow for an internal NW1507 reaction over the first  $\overline{RD}/\overline{WR}$  access. For a read, at least 1220ns; while for a write, at least 800ns.

Figure-13. Interfacing NW1507 with Intel 8051

## **Maximum Rating**