# **Low Power Level Shifter**

The NCN6011 is a level shifter analog circuit designed to translate the voltages between a SIM Card and an external microcontroller. The device handles all the signals needed to control the data transaction between the external Card and the MPU.

#### **Features**

- 2.7 to 6.0 V Input and/or Output Voltage Range

- 500 nA Quiescent Supply Current

- All Pins are Fully ESD Protected

- Supports 10 MHz Clock

- Provides a Logic I/O Enable Function

- Rx/Tx Communication Capability

# **Typical Applications**

• SIM/GSM/SMARTCARD Interface

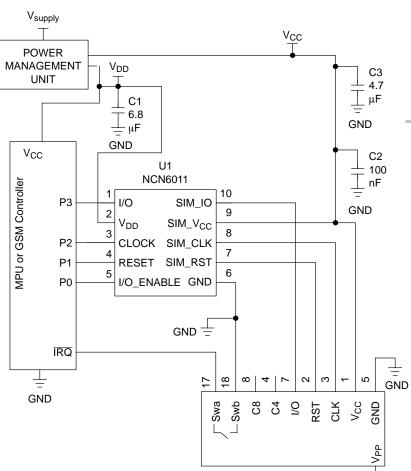

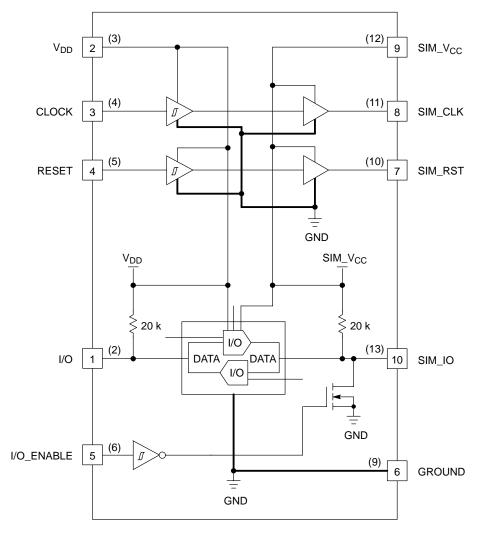

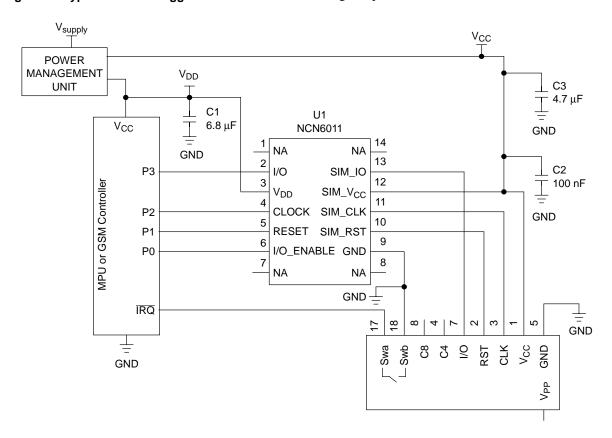

Figure 1. Typical Interface Application

# ON Semiconductor™

http://onsemi.com

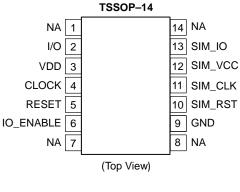

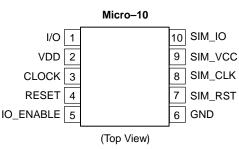

## **PIN CONNECTIONS**

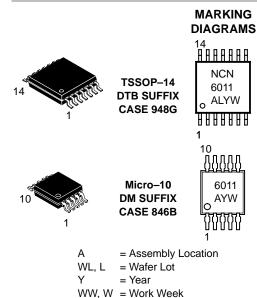

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

# NOTES:

- Numbers in parenthesis adjacent to the pins are related to the TSSOP-14 package.

TSSOP-14 package Pins 1, 7, 8 and 14 are not connected.

Figure 2. Block Diagram

# **ABBREVIATIONS**

| CLOCK   | Input Logic Clock                     |

|---------|---------------------------------------|

| RESET   | Input Logic Reset                     |

| VDD     | Interface Power Supply Input          |

| SIM_VCC | Interface IC Card Power Supply Output |

| SIM_CLK | Interface IC Card Clock Output        |

| SIM_RST | Interface IC Card Reset Output        |

| SIM_IO  | Interface IC Card I/O Signal Line     |

| Class A | 5.0 V Smart Card                      |

| Class B | 3.0 V Smart Card                      |

# PIN DESCRIPTIONS (Pin numbers in parenthesis are related to the TSSOP-14 package) (Pin numbers in bold are related to the Micro-10 package)

| (Pin numbers in bold are related to the Mlcro-10 package) |                 |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------------------------------------------|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                                                       | Name            | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| (1)                                                       | -               | NA     | No Connection. (TSSOP–14 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| <b>1</b> (2)                                              | I/O             | INPUT  | This pin is connected to an external microcontroller. A bidirectional level translator adapts the serial I/O signal between the smart card and the external controller. A built–in constant 20 k $\Omega$ typical resistor provides a high impedance state when not activated.                                                                                                                                                                                                                                               |  |  |  |

| <b>2</b> (3)                                              | V <sub>DD</sub> | POWER  | This pin is connected to the system controller power supply and the input voltage can range from 2.7 to 6.0 V.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| <b>3</b> (4)                                              | CLOCK           | INPUT  | The clock signal, coming from the external controller, must have a Duty Cycle within the Min/Max limits defined by the specification (typically 50%). The built–in level shifter translates the input signal to the external SIM card voltage supply.                                                                                                                                                                                                                                                                        |  |  |  |

| <b>4</b> (5)                                              | RESET           | INPUT  | The RESET signal present at this pin is provided by the MPU. The internal level shifter translates the level according to the voltages applied to pin 3 and pin 12.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| <b>5</b> (6)                                              | IO_ENABLE       | INPUT  | This logic input pin forces SIM_IO pin to Low when IO_ENABLE = Low, leaving this signal High when IO_ENABLE = High. The signal is not latched and the SIM_IO pin is released to a logic High when IO_ENABLE = High. When this condition is met, the SIM_IO logic status depends upon the signal presence pin I/O. When the MPU uses two different channels to exchange data with the SIM card, the IO_ENABLE pin can be used to as a Write line to the external card, the I/O pin being used to Read data from the SIM card. |  |  |  |

| (7)                                                       | -               | NA     | No Connection. (TSSOP–14 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| (8)                                                       | -               | NA     | No Connection. (TSSOP–14 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| <b>6</b> (9)                                              | GND             | GROUND | This pin is the GROUND reference for the integrated circuit and associated signals. High frequency layout techniques are requested to connect the GND pin to the external functions.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| <b>7</b> (10)                                             | SIM_RST         | OUTPUT | This pin is connected to the RST pin of the card connector. A voltage level translator adapts the external RESET signal (coming from the MPU) to the smart card.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| <b>8</b> (11)                                             | SIM_CLK         | OUTPUT | This pin is connected to the CLK pin of the card connector. The CLOCK signal comes from the external clock generator. The internal voltage level shifter adapts the clock signal flowing through this link. Care must be observed to prevent AC coupling with adjacent lines and signals PCB tracks.                                                                                                                                                                                                                         |  |  |  |

| <b>9</b> (12)                                             | SIM_VCC         | POWER  | This pin is connected to the smart card VCC power supply pin. The voltage, provided by an external power supply, can range from 2.7 V to 6.0 V. The NCN6011 does not regulate or protect the voltage supply applied to the external card.                                                                                                                                                                                                                                                                                    |  |  |  |

| <b>10</b> (13)                                            | SIM_I/O         | OUTPUT | This pin handles the connection to the serial I/O of the card connector. A bidirectional voltage level translator adapts the serial I/O signal between the card and the microcontroller. A 20 k $\Omega$ typical pull up resistor provides a High impedance state for the SIM card I/O link.                                                                                                                                                                                                                                 |  |  |  |

| (14)                                                      | -               | NA     | No Connection. (TSSOP–14 Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

## **MAXIMUM RATINGS**

| Rating                                                                                                                                          | Symbol             | Value                         | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|----------|

| Power Supply                                                                                                                                    | V <sub>DD</sub>    | 7.0 V                         | V        |

| External Card and Level Shifter Power Supply                                                                                                    | SIM_VCC            | 7.0 V                         | V        |

| Digital Input Voltage                                                                                                                           | RESET,             | $-0.3 \le V \le V_{DD}$ $1.0$ | V        |

| Digital Input Current                                                                                                                           | IO_ENABLE          |                               | mA       |

| Digital Input Voltage                                                                                                                           | CLOCK              | $-0.3 \le V \le V_{DD}$       | V        |

| Digital Input Current                                                                                                                           |                    | 1.0                           | mA       |

| Digital Input Voltage                                                                                                                           | I/O                | $-0.3 \le V \le V_{DD}$       | V        |

| Digital Input Current                                                                                                                           |                    | 1.0                           | mA       |

| Digital Output Voltage                                                                                                                          | SIM_RST            | -0.3 ≤ V ≤ SIM_VCC            | V        |

| Digital Output Current                                                                                                                          |                    | 25                            | mA       |

| Digital Output/Input Voltage                                                                                                                    | SIM_I/O            | -0.3 ≤ V ≤ SIM_VCC            | V        |

| Digital Output/Input Current                                                                                                                    |                    | 25                            | mA       |

| Digital Output Voltage                                                                                                                          | SIM_CLK            | -0.3 ≤ V ≤ SIM_VCC            | V        |

| Digital Output Current                                                                                                                          |                    | 50                            | mA       |

| Human Body Model: R = 1500 $\Omega$ , C = 100 pF SIM card side, pins <b>7</b> , <b>8</b> , <b>9</b> , <b>10</b> (10, 11, 12, 13) All other pins | ESD                | 4.0<br>2.0                    | kV<br>kV |

| Micro–10 Package Power Dissipation @ T <sub>A</sub> = +85°C Thermal Resistance Junction to Air                                                  | P <sub>D</sub>     | 200                           | mW       |

|                                                                                                                                                 | R <sub>THhja</sub> | 200                           | °C/W     |

| TSSOP-14 Package Power Dissipation @ T <sub>A</sub> = +85°C Thermal Resistance Junction to Air                                                  | P <sub>D</sub>     | 320                           | mW       |

|                                                                                                                                                 | R <sub>THhja</sub> | 125                           | °C/W     |

| Operating Ambient Temperature Range                                                                                                             | T <sub>A</sub>     | -25 to +85                    | °C       |

| Operating Junction Temperature Range                                                                                                            | TJ                 | -25 to +125                   | °C       |

| Maximum Junction Temperature                                                                                                                    | T <sub>Jmax</sub>  | +150                          | °C       |

| Storage Temperature Range                                                                                                                       | T <sub>stg</sub>   | -65 to +150                   | °C       |

Maximum electrical ratings define the values beyond which permanent damage(s) may occur internally to the chip regardless of the operating temperature. Pin numbers in parenthesis are related to the TSSOP–14 package.

**POWER SUPPLY SECTION** (–25°C to +85°C ambient temperature, unless otherwise noted)

(Pin numbers in parenthesis are related to the TSSOP-14 package)

(Pin numbers in bold are related to the Mlcro-10 package)

| Rating                                                                                                                                  | Symbol           | Pin           | Min | Тур  | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-----|------|-----|------|

| Power Supply                                                                                                                            | V <sub>DD</sub>  | <b>2</b> (3)  | 2.7 | -    | 6.0 | V    |

| Standby Supply Current, CLOCK = L, I/O = H, SIM_VCC = 3.0 V, No SIM Card Inserted                                                       | I <sub>VDD</sub> | <b>2</b> (3)  | -   | 0.5  | 2.0 | μА   |

| Input External Power Supply                                                                                                             | SIM_VCC          | <b>9</b> (12) | 2.7 | -    | 6.0 | V    |

| Standby Current, SIM_VCC = 3.0 V, I/O = H,<br>No SIM Card Inserted, CLOCK = L                                                           | lvcc             | <b>9</b> (12) | -   | 0.2  | 0.5 | μА   |

| Power Supply Normal Operating Current  @ VDD = +5.0 V, SIM_VCC = +5.0 V, CLOCK = 5.0 MHz, RESET = H, IO_ENABLE = H, I/O Data = 100 kHz  | I <sub>DD</sub>  | <b>2</b> (3)  | _   | 230  | -   | μА   |

| Power Supply Normal Operating Current  @ VDD = +5.0 V, SIM_VCC = +5.0 V, CLOCK = 5.0 MHz, RESET = H, IO_ENABLE = H, I/O Data = H        | I <sub>DD</sub>  | <b>2</b> (3)  | _   | 80   | -   | μА   |

| Card Level Shifter Operating Current  © VDD = +5.0 V, SIM_VCC = +5.0 V,  CLOCK = 5.0 MHz, RESET = H,  IO_ENABLE = H, I/O Data = 100 kHz | I <sub>CC</sub>  | <b>9</b> (12) | -   | 1.50 | -   | mA   |

| Card Level Shifter Operating Current  @ VDD = +5.0 V, SIM_VCC = +5.0 V, CLOCK = 5.0 MHz, RESET = H, IO_ENABLE = H, I/O Data = H         | I <sub>CC</sub>  | <b>9</b> (12) | -   | 1.30 | -   | mA   |

# DIGITAL INPUT SECTION: CLOCK, RESET, I/O, IO\_ENABLE

(-25°C to +85°C ambient temperature, unless otherwise noted) (Note 1)

| Rating                                                                                                                     | Symbol                                                | Pin                              | Min                   | Тур | Max                                                        | Unit                     |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|-----------------------|-----|------------------------------------------------------------|--------------------------|

| CLOCK, RESET, IO_ENABLE High Level Input Voltage Low Level Input Voltage Input Rise Time Input Fall Time Input Capacitance | V <sub>IH</sub><br>V <sub>IL</sub><br>tr<br>tf<br>Cin | 1, 3,<br>4, 5<br>(2, 4,<br>5, 6) | 0.7 * V <sub>DD</sub> | -   | V <sub>CC</sub><br>0.3 * V <sub>DD</sub><br>50<br>50<br>10 | V<br>V<br>ns<br>ns<br>pF |

| Input @ Duty Cycle = 50% ±1% (Note 2) Clock Rise Time Clock Fall Time Input Clock Capacitance                              | CLOCK                                                 | <b>3</b> (4)                     | -                     | -   | 5.0<br>50<br>50<br>10                                      | MHz<br>ns<br>ns<br>pF    |

| Input/Output Data Transfer Frequency I/O Rise Time I/O Fall Time Input I/O Capacitance                                     | I/O                                                   | <b>1</b> (2)                     | -                     | -   | 160<br>0.8<br>0.8<br>10                                    | kHz<br>μs<br>μs<br>pF    |

<sup>1.</sup> Digital inputs undershoot < -0.30 V, Digital inputs overshoot < 0.30 V.

<sup>2.</sup> The SIM\_CLK clock can operate up to 10 MHz, but, in this case, the rise and fall time are not guaranteed to be fully within the GSM specification over the temperature range.

# SIM INTERFACE SECTION (Note 3)

| Rating                                                                                                                                                                                                                                                  | Symbol       | Pin            | Min                | Тур | Max                                    | Unit                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--------------------|-----|----------------------------------------|---------------------------|

| SIM_VCC = +5.0 V<br>Output RESET $V_{OH}$ @ Irst = +200 $\mu$ A<br>Output RESET $V_{OL}$ @ Irst = -200 $\mu$ A<br>Output RESET Rise Time @ Cout = 30 pF<br>Output RESET Fall Time @ Cout = 30 pF                                                        | SIM_RST      | <b>7</b> (10)  | SIM_VCC - 0.7 V    |     | SIM_VCC<br>0.6<br>100<br>100           | V<br>V<br>ns<br>ns        |

| SIM_VCC = $+3.0 \text{ V}$<br>Output RESET V <sub>OH</sub> @ Irst = $+200 \mu A$<br>Output RESET V <sub>OL</sub> @ Irst = $-200 \mu A$<br>Output RESET Rise Time @ Cout = $30 \text{ pF}$<br>Output RESET Fall Time @ Cout = $30 \text{ pF}$            |              |                | 0.8 * SIM_VCC<br>0 |     | SIM_VCC<br>0.2 * SIM_VCC<br>100<br>100 | V<br>V<br>ns<br>ns        |

| SIM_VCC = +5.0 V<br>Output Duty Cycle @ Fin = 5.0 MHz<br>DC = 50% ± 1%                                                                                                                                                                                  | SIM_CLK      | <b>8</b> (11)  | 40                 |     | 60                                     | %                         |

| Output SIM_CLK Rise Time @ Cout = 30 pF Output SIM_CLK Fall Time @ Cout = 30 pF Output $V_{OH}$ @ Iclk = +20 $\mu$ A Output $V_{OL}$ @ Iclk = -200 $\mu$ A                                                                                              |              |                | 0.7 * SIM_VCC<br>0 |     | 18<br>18<br>SIM_VCC<br>+0.5            | ns<br>ns<br>V<br>V        |

| SIM_VCC = +3.0 V<br>Output Duty Cycle @ Fin = 5.0 MHz<br>DC = 50% ± 1%                                                                                                                                                                                  |              |                | 40                 |     | 60                                     | %                         |

| Output SIM_CLK Rise Time @ Cout = 30 pF<br>Output SIM_CLK Fall Time @ Cout = 30 pF<br>Output $V_{OH}$ @ Iclk = $+20 \mu A$<br>Output $V_{OL}$ @ Iclk = $-20 \mu A$                                                                                      |              |                | 0.7 * SIM_VCC<br>0 |     | 18<br>18<br>SIM_VCC<br>0.2 * SIM_VCC   | ns<br>ns<br>V<br>V        |

| SIM_VCC = +5.0 V @ IO_ENABLE = H SIM_I/O Data Transfer Frequency SIM_I/O Rise Time @ Cout = 30 pF SIM_I/O Fall Time @ Cout = 30 pF Output $V_{OH}$ @ ISIM_IO = +20 $\mu$ A, $V_{IH}$ = $V_{DD}$ Output $V_{OL}$ @ ISIM_IO = -1.0 mA, I/O $V_{IL}$ = 0 V | SIM_I/O      | <b>10</b> (13) | 0.7 * SIM_VCC<br>0 |     | 160<br>0.8<br>0.8<br>SIM_VCC<br>0.4    | kHz<br>μs<br>μs<br>V<br>V |

| SIM_VCC = +3.0 V @ IO_ENABLE = H SIM_I/O Data Transfer Frequency SIM_I/O Rise Time @ Cout = 30 pF SIM_I/O Fall Time @ Cout = 30 pF Output $V_{OH}$ @ ISIM_IO = +20 $\mu$ A, $V_{IH}$ = $V_{DD}$ Output $V_{OL}$ @ ISIM_IO = -1.0 mA, I/O $V_{IL}$ = 0 V |              |                | 0.7 * SIM_VCC<br>0 |     | 160<br>0.8<br>0.8<br>SIM_VCC<br>0.4    | kHz<br>μs<br>μs<br>V<br>V |

| $\begin{split} & \text{SIM\_VCC} = +5.0 \text{ V @ IO\_ENABLE} = \text{L} \\ & \text{SIM\_I/O Fall Time @ Cout} = 30 \text{ pF} \\ & \text{Output V}_{\text{OL}} \text{ @ ISIM\_IO} = -1.0 \text{ mA, I/O V}_{\text{IL}} = 0 \text{ V} \end{split}$     |              |                | 0                  | 150 | 800<br>0.4                             | ns<br>V                   |

| $\begin{split} & \text{SIM\_VCC} = +3.0 \text{ V @ IO\_ENABLE} = \text{L} \\ & \text{SIM\_I/O Fall Time @ Cout} = 30 \text{ pF} \\ & \text{Output V}_{\text{OL}} \text{ @ ISIM\_IO} = -1.0 \text{ mA, I/O V}_{\text{IL}} = 0 \text{ V} \end{split}$     |              |                | 0                  | 150 | 800<br>0.4                             | ns<br>V                   |

| SIM_VCC = +5.0 V @ I/O = H,<br>IO_ENABLE Returns to High<br>SIM_I/O Rise Time @ Cout = 30 pF                                                                                                                                                            |              |                |                    | 2.0 |                                        | μs                        |

| SIM_VCC = +3.0 V @ I/O = H,<br>IO_ENABLE Returns to High<br>SIM_I/O Rise Time @ Cout = 30 pF                                                                                                                                                            |              |                |                    | 1.5 |                                        | μs                        |

| I/O Pull Up Resistor                                                                                                                                                                                                                                    | I/O_RPLD     | <b>1</b> (2)   | 13                 | 20  |                                        | kΩ                        |

| Card I/O Pull Up Resistor                                                                                                                                                                                                                               | SIM_I/O_RPLD | 10             | 13                 | 20  |                                        | kΩ                        |

<sup>3.</sup> SIM logic input undershoot <-0.30 V, SIM logic input overshoot < 0.30 V.

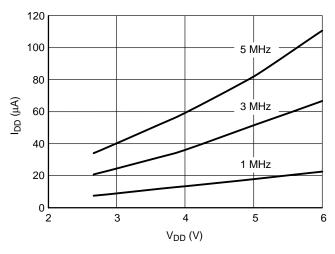

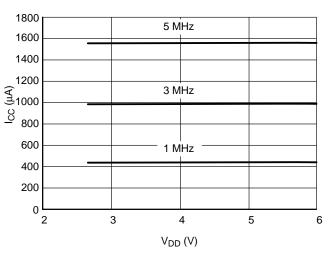

Figure 3. SIM Supply Current as a Function of the V<sub>DD</sub> Voltage, I/O = High

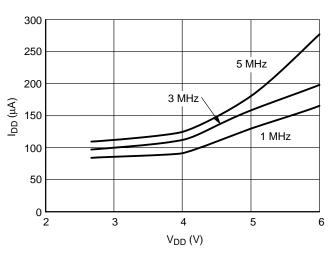

Figure 4. SIM Supply Current as a Function of the V<sub>DD</sub> Voltage, I/O = 100 kHz Data Transfer

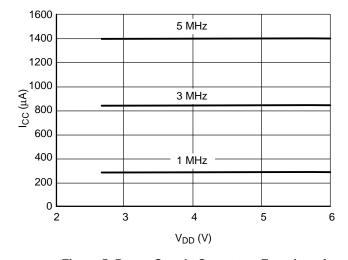

Figure 5. Power Supply Current as Function of the  $V_{CC}$  Input Voltage, I/O = High

Figure 6. Power Supply Current as Function of the V<sub>CC</sub> Input Voltage, I/O = 100 kHz Data Transfer

#### **Level Shifters**

The built—in level shifters accommodate the differential voltage between the external MPU and the SIM card. Neither the logic nor the functions of the SIM signals are affected by the interface.

The NCN6011 does not regulate the SIM\_VCC, nor does it detect the overload current.

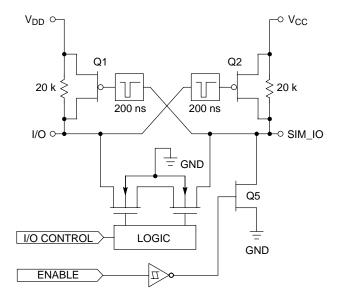

#### **Bidirectional Level Shifter**

The NCN6011 carries out the voltage difference between the MPU and the Smart Card I/O signals. When the start sequence is completed, and if no failures have been detected, the device becomes essentially transparent for the data transferred on the I/O line. To fulfill the ISO7816–3 specification, both sides of the I/O line have built–in pulsed circuitry to accelerate the signal rise transient. The I/O line is connected on both sides of the interface by a NMOS switch which provide the level shifter and, thanks to its relative high internal impedance, protects the Smart Card in the event of data collision. Such a situation could occur if either the MPU of the smart card forces a signal in the opposite logic level direction.

Figure 7. Basic Internal I/O Level Shifter

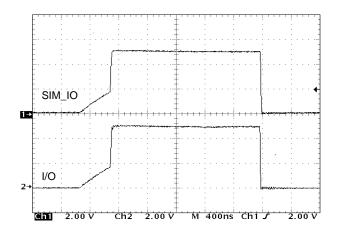

Figure 8. Typical I/O and SIM\_IO Waveform,  $V_{DD} = V_{CC} = 5.0 \text{ V}$ , ENABLE = Low

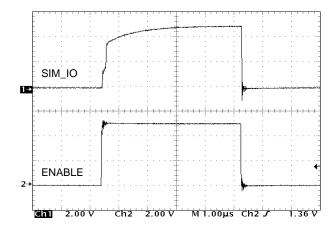

Figure 9. Typical SIM\_IO Activated by ENABLE Pin, I/O = High (open drain)

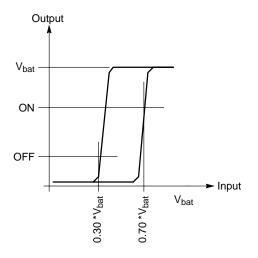

## **Input Schmitt Triggers**

All the Logic Input pins have built—in Schmitt trigger circuits to prevent the NCN6011 against uncontrolled operation. The typical dynamic characteristics of the related pins are depicted in Figure 10.

The output signal is guaranteed to go High when the input voltage is above 0.70\*Vbat, and will go Low when the input voltage is below 0.30\*Vbat.

Figure 10. Typical Schmitt Trigger Characteristic

#### **ESD Protection**

The NCN6011 includes silicon devices to protect the pins against the ESD spikes voltages. To cope with the different ESD voltages developed across these pins, the built—in structures have been designed to handle either 2.0 kV, when related to the microcontroller side, or 4.0 kV when connected with the external contacts. Practically, the SIM\_RST, SIMD\_CLK and SIM\_IO pins can sustain 4.0 kV.

## **Printed Circuit Board Layout**

Since the NCN6011 carries high speed currents together with high frequency clock, the printed circuit board must be carefully designed to avoid the risk of uncontrolled operation of the interface.

Care must be observed to avoid common copper track sharing small signal and high power with a relative high impedance. On top of that, the clock signal (both input and output) shall be properly shielding to minimize the high frequency cross talk between this line and the rest of the circuit. In particular, the SIM\_RST signal shall be protected from interference generated by the SIM\_CLK line. Such protection can be achieved by surrounding the SIM\_CLK track by a copper track connected to ground. Generally speaking, the ground plane shall be as large as possible for a given printed circuit board area.

Figure 11. Typical NCN6011/TSSOP-14 Application

# ORDERING INFORMATION

| Device       | Package  | Shipping         |

|--------------|----------|------------------|

| NCN6011DTB   | TSSOP-14 | 96 Units/Rail    |

| NCN6011DTBR2 | TSSOP-14 | 2500 Tape & Reel |

| NCN6011DMR2  | Micro-10 | 4000 Tape & Reel |

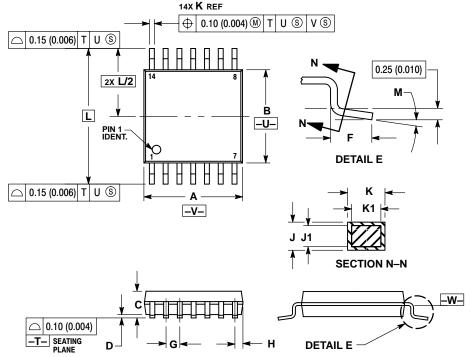

#### PACKAGE DIMENSIONS

# TSSOP-14 **DTB SUFFIX** CASE 948G-01 **ISSUE O**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS. MOLD FLASH

- OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR

- PROTRUSION SHALL NOT EXCEED

0.25 (0.010) PER SIDE.

DIMENSION K DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN

EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIN | IETERS | INC       | HES   |

|-----|--------|--------|-----------|-------|

| DIM | MIN    | MAX    | MIN       | MAX   |

| Α   | 4.90   | 5.10   | 0.193     | 0.200 |

| В   | 4.30   | 4.50   | 0.169     | 0.177 |

| С   |        | 1.20   |           | 0.047 |

| D   | 0.05   | 0.15   | 0.002     | 0.006 |

| F   | 0.50   | 0.75   | 0.020     | 0.030 |

| G   | 0.65   | BSC    | 0.026 BSC |       |

| Н   | 0.50   | 0.60   | 0.020     | 0.024 |

| J   | 0.09   | 0.20   | 0.004     | 0.008 |

| J1  | 0.09   | 0.16   | 0.004     | 0.006 |

| K   | 0.19   | 0.30   | 0.007     | 0.012 |

| K1  | 0.19   | 0.25   | 0.007     | 0.010 |

| L   | 6.40   |        | 0.252     | BSC   |

| М   | ٥°     | 8°     | 0°        | 8°    |

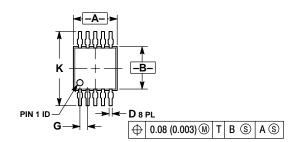

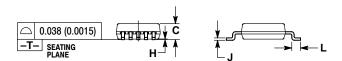

## Micro-10 **DM SUFFIX** CASE 846B-02 **ISSUE B**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION "A" DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

DIMENSION "B" DOES NOT INCLUDE INTERLEAD

- FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010)

- PER SIDE.

5. 846B-01 OBSOLETE. NEW STANDARD 846B-02

|     | MILLIN | IETERS  | INC   | HES   |  |  |

|-----|--------|---------|-------|-------|--|--|

| DIM | MIN    | MIN MAX |       | MAX   |  |  |

| Α   | 2.90   | 3.10    | 0.114 | 0.122 |  |  |

| В   | 2.90   | 3.10    | 0.114 | 0.122 |  |  |

| С   | 0.95   | 1.10    | 0.037 | 0.043 |  |  |

| D   | 0.20   | 0.35    | 0.008 | 0.014 |  |  |

| G   | 0.50   | BSC     | 0.020 | BSC   |  |  |

| Н   | 0.05   | 0.15    | 0.002 | 0.006 |  |  |

| J   | 0.10   | 0.21    | 0.004 | 0.008 |  |  |

| K   | 4.75   | 5.05    | 0.187 | 0.199 |  |  |

| L   | 0.40   | 0.70    | 0.016 | 0.028 |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

# Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax:** 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.