# 12 V Synchronous Buck Power MOSFET Driver

The NCP5355 is a dual MOSFET gate driver optimized to drive the gates of both high- and low-side Power MOSFETs in a Synchronous Buck converter. The NCP5355 is an excellent companion to multiphase controllers that do not have integrated gate drivers, such as ON Semiconductor's NCP5306, NCP5314 or NCP5316. This architecture provides the power supply designer greater flexibility by being able to locate the gate drivers close to the MOSFETs.

Driving MOSFETs with a 12 V source as opposed to a 5.0 V can significantly reduce conduction losses. Optimized internal, adaptive nonoverlap circuitry further reduces switching losses by preventing simultaneous conduction of both MOSFETs.

The floating top driver design can accommodate MOSFET drain voltages as high as 26 V. Both gate outputs can be driven low by applying a low logic level to the Enable (EN) pin. An Undervoltage Lockout function ensures that both driver outputs are low when the supply voltage is low, and a Thermal Shutdown function provides the IC with overtemperature protection.

The NCP5355 has the same pinout as the NCP5351 5.0 V Gate Driver.

#### **Features**

- 8.0-14 V Gate Drive Capability

- 2.0 A Peak Drive Current

- Rise and Fall Times < 15 ns Typical into 3300 pF

- Propagation Delay from Inputs to Outputs < 30 ns

- Adaptive Nonoverlap Time Optimized for Large Power MOSFETs

- Floating Top Driver Accommodates Applications Up to 26 V

- Undervoltage Lockout to Prevent Switching when the Input Voltage is Low

- Thermal Shutdown Protection Against Overtemperature

- TG to DRN Pull-Down Resistor Prevents HV Supply-Induced Turn On of Top MOSFET

- BG to PGND Pull-Down Resistor Prevents Transient Turn On of Bottom MOSFET

- Internal Bootstrap Diode Reduces Parts Count and Total Solution Cost

# ON Semiconductor®

http://onsemi.com

SO-8 D SUFFIX CASE 751

MARKING

DIAGRAM

A = Assembly Location

L = Wafer Lot

′ = Year

W = Work Week

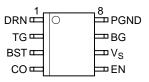

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

| Device     | Package | Shipping         |

|------------|---------|------------------|

| NCP5355D   | SO-8    | 98 Units/Rail    |

| NCP5355DR2 | SO-8    | 2500 Tape & Reel |

Figure 1. Block Diagram

# **MAXIMUM RATINGS\***

| Rating                                                                                                   |                                    | Value              | Unit |

|----------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|------|

| Operating Junction Temperature, T <sub>J</sub>                                                           |                                    | Internally Limited | °C   |

| Package Thermal Resistance:<br>Junction to Case, $R_{\theta JC}$<br>Junction to Ambient, $R_{\theta JA}$ |                                    | 45<br>165          | °C/W |

| Storage Temperature Range, T <sub>S</sub>                                                                |                                    | -65 to 150         | °C   |

| Lead Temperature Soldering:                                                                              | Reflow: (SMD styles only) (Note 1) | 230 peak           | °C   |

| JEDEC Moisture Sensitivity                                                                               |                                    | 1                  | -    |

<sup>\*</sup>The maximum package power dissipation must be observed.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

# **MAXIMUM RATINGS**

| Pin Symbol     | Pin Name                                    | V <sub>MAX</sub>              | V <sub>MIN</sub>                                   | I <sub>SOURCE</sub>                | I <sub>SINK</sub>                  |  |

|----------------|---------------------------------------------|-------------------------------|----------------------------------------------------|------------------------------------|------------------------------------|--|

| V <sub>S</sub> | Main Supply Voltage Input                   | 15 V                          | -0.3 V                                             | NA                                 | 2.0 A Peak (< 100 μs)<br>250 mA DC |  |

| BST            | Bootstrap Supply Voltage<br>Input           | 30 V wrt/PGND<br>15 V wrt/DRN | -0.3 V wrt/DRN                                     | NA                                 | 2.0 A Peak (< 100 μs)<br>250 mA DC |  |

| DRN            | Switching Node<br>(Bootstrap Supply Return) | 26 V                          | -1.0 V DC<br>-5.0 V for 100 ns<br>-6.0 V for 20 ns | 2.0 A Peak (< 100 μs)<br>250 mA DC | NA                                 |  |

| TG             | High-Side Driver Output<br>(Top Gate)       | 30 V wrt/PGND<br>15 V wrt/DRN | -0.3 V wrt/DRN                                     | 2.0 A Peak (< 100 μs)<br>250 mA DC | 2.0 A Peak (< 100 μs)<br>250 mA DC |  |

| BG             | Low-Side Driver Output<br>(Bottom Gate)     | 15 V                          | -0.3 V                                             | 2.0 A Peak (< 100 μs)<br>250 mA DC | 2.0 A Peak (< 100 μs)<br>250 mA DC |  |

| СО             | TG and BG Control Input                     | 5.5 V                         | -0.3 V                                             | 1.0 mA                             | 1.0 mA                             |  |

| EN             | Enable Input                                | 5.5 V                         | -0.3 V                                             | 1.0 mA                             | 1.0 mA                             |  |

| PGND           | Ground                                      | 0 V                           | 0 V                                                | 2.0 A Peak (< 100 μs)<br>250 mA DC | NA                                 |  |

NOTE: All voltages are with respect to PGND except where noted.

<sup>1. 60</sup> seconds maximum above 183°C.

$\label{eq:continuous} \textbf{ELECTRICAL CHARACTERISTICS} \text{ (Note 2) } (0 ^{\circ}\text{C} < \text{T}_{\text{J}} < 125 ^{\circ}\text{C}; 9.2 \text{ V} < \text{V}_{\text{S}} < 13.2 \text{ V}; 9.2 \text{ V} < \text{V}_{\text{BST}} < 26 \text{ V}; \text{V}_{\text{EN}} = \text{Float}; \text{C}_{\text{LOAD}} = 3.3 \text{ nF}; \text{unless otherwise noted.) }$

| Parameter                                     | Test Conditions                                                                                                               | Min  | Тур  | Max  | Unit |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| DC OPERATING SPECIFICATIONS<br>Power Supply   |                                                                                                                               |      |      |      |      |

| V <sub>S</sub> Quiescent Current, Operating   | V <sub>CO</sub> = 0 V or 4.5 V; No output switching                                                                           | -    | 1.0  | 2.0  | mA   |

| V <sub>BST</sub> Quiescent Current, Operating | V <sub>CO</sub> = 0 V or 4.5 V; No output switching                                                                           | -    | 3.8  | 5.0  | mA   |

| Undervoltage Lockout                          |                                                                                                                               | •    | -    | -    | •    |

| Start Threshold                               | V <sub>CO</sub> = 0 V                                                                                                         | 7.0  | 8.0  | 9.2  | V    |

| Stop Threshold                                | V <sub>CO</sub> = 0 V                                                                                                         | 6.0  | 7.0  | 8.0  | V    |

| Hysteresis                                    | V <sub>CO</sub> = 0 V                                                                                                         | 0.70 | 1.00 | 1.60 | V    |

| CO Input Characteristics                      |                                                                                                                               |      |      |      |      |

| High Threshold                                | -                                                                                                                             | 2.0  | -    | -    | V    |

| Low Threshold                                 | -                                                                                                                             | -    | -    | 0.8  | V    |

| Input Bias Current                            | 0 < V <sub>CO</sub> < 5.0 V                                                                                                   | -    | 0    | 1.0  | μΑ   |

| EN Input Characteristics                      |                                                                                                                               |      |      |      |      |

| High Threshold                                | Both output respond to CO                                                                                                     | 2.0  | -    | -    | V    |

| Low Threshold                                 | Both output are low independent of CO                                                                                         | -    | -    | 0.8  | V    |

| Input Bias Current                            | 0 < V <sub>EN</sub> < 5.0 V                                                                                                   | -7.0 | -3.0 | +2.0 | μА   |

| Thermal Shutdown                              |                                                                                                                               |      |      |      |      |

| Overtemperature Trip Point                    | Note 3                                                                                                                        | 150  | 170  | -    | °C   |

| Hysteresis                                    | Note 3                                                                                                                        | -    | 20   | -    | °C   |

| High-Side Driver                              |                                                                                                                               |      |      |      |      |

| Peak Output Current                           | Note 3                                                                                                                        | -    | 2.0  | -    | Α    |

| Output Resistance (Sourcing)                  | Duty Cycle < 2.0%, Pulse Width < 100 $\mu$ s,<br>$T_J$ = 125°C, $V_{BST}$ - $V_{DRN}$ = 12 V,<br>$V_{TG}$ = 10 V + $V_{DRN}$  | ı    | 1.0  | -    | Ω    |

| Output Resistance (Sinking)                   | Duty Cycle < 2.0%, Pulse Width < 100 $\mu$ s,<br>$T_J$ = 125°C, $V_{BST}$ - $V_{DRN}$ = 12 V,<br>$V_{TG}$ = 2.0 V + $V_{DRN}$ | ı    | 1.0  | -    | Ω    |

| Low-Side Driver                               |                                                                                                                               |      |      |      |      |

| Peak Output Current                           | Note 3                                                                                                                        | -    | 2.0  | -    | Α    |

| Output Resistance (Sourcing)                  | Duty Cycle < 2.0%, Pulse Width < 100 $\mu$ s,<br>T <sub>J</sub> = 125°C, V <sub>S</sub> = 12 V, V <sub>BG</sub> = 10 V        | -    | 1.1  | -    | Ω    |

| Output Resistance (Sinking)                   | Duty Cycle < 2.0%, Pulse Width < 100 $\mu$ s,<br>T <sub>J</sub> = 125°C, V <sub>S</sub> = 12 V, V <sub>BG</sub> = 2.0 V       | -    | 1.0  | -    | Ω    |

| Charge Pump Diode                             |                                                                                                                               |      |      |      |      |

| Forward Voltage Drop                          | I <sub>D</sub> = 100 mA                                                                                                       | -    | 1.1  | 1.4  | V    |

All limits at temperature extremes are guaranteed by characterization using Standard Statistical Quality Control methods.

Guaranteed by design, not 100% tested in production.

$\textbf{ELECTRICAL CHARACTERISTICS} \; (\text{Note 4}) \; (0^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}; \; 9.2 \; \text{V} < \text{V}_{\text{S}} < 13.2 \; \text{V}; \; 9.2 \; \text{V} < \text{V}_{\text{BST}} < 26 \; \text{V}; \; \text{V}_{\text{EN}} = \text{Float}; \; \text{V}_{\text{E$  $C_{LOAD}$  = 3.3 nF; unless otherwise noted.)

| Parameter                                                     | Symbol             | Test Conditions                                                            | Min | Тур | Max | Unit             |

|---------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|-----|-----|-----|------------------|

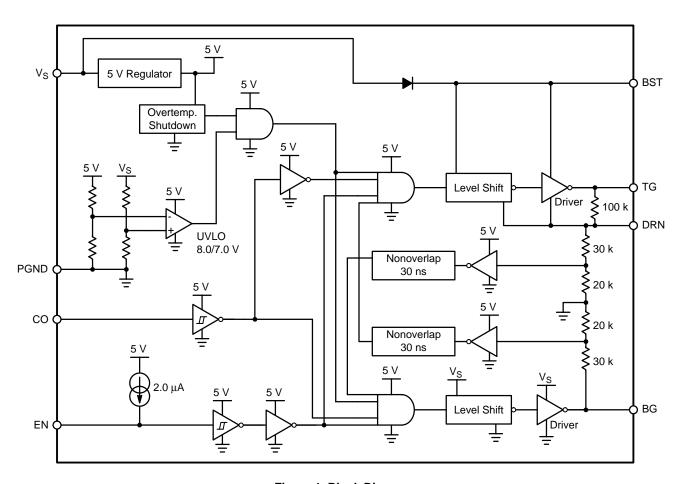

| AC OPERATING SPECIFIC High-Side Driver                        | CATIONS            |                                                                            |     |     |     |                  |

| Rise Time                                                     | tr <sub>TG</sub>   | $V_{BST} - V_{DRN} = 12 \text{ V}, V_{S} = 12 \text{ V} \text{ (Note 5)}$  | -   | 15  | 25  | ns               |

| Fall Time                                                     | tf <sub>TG</sub>   | V <sub>BST</sub> - V <sub>DRN</sub> = 12 V, V <sub>S</sub> = 12 V (Note 5) | -   | 15  | 25  | ns               |

| Propagation Delay Time,<br>TG Going High<br>(Nonoverlap Time) | tpdh <sub>TG</sub> | V <sub>BST</sub> - V <sub>DRN</sub> = 12 V, V <sub>S</sub> = 12 V (Note 5) | 15  | 30  | 55  | ns               |

| Propagation Delay Time,<br>TG Going Low                       | tpdl <sub>TG</sub> | $V_{BST} - V_{DRN} = 12 \text{ V}, V_{S} = 12 \text{ V} \text{ (Note 5)}$  | -   | 45  | 60  | ns               |

| Low-Side Driver                                               | -                  |                                                                            | -   | -   | -   | - <del>-</del> - |

| Rise Time                                                     | tr <sub>BG</sub>   | (Note 5)                                                                   | -   | 10  | 20  | ns               |

| Fall Time                                                     | tf <sub>BG</sub>   | (Note 5)                                                                   | -   | 10  | 20  | ns               |

| Propagation Delay Time,<br>BG Going High<br>(Nonoverlap Time) | tpdh <sub>BG</sub> | (Note 5)                                                                   | 15  | 30  | 55  | ns               |

| Propagation Delay Time,<br>BG Going Low                       | tpdl <sub>BG</sub> | (Note 5)                                                                   | -   | 35  | 55  | ns               |

- 4. All limits at temperature extremes are guaranteed by characterization using Standard Statistical Quality Control methods.

5. AC specifications are guaranteed by characterization, not 100% tested in production.

Figure 2. Timing Diagram

# PACKAGE PIN DESCRIPTION

| Pin | Pin Symbol     | Description                                                                                                                                                                                                          |

|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DRN            | The switching node common to the high and low-side FETs. The high-side (TG) driver and supply (BST) are referenced to this pin.                                                                                      |

| 2   | TG             | Driver output to the high-side MOSFET gate.                                                                                                                                                                          |

| 3   | BST            | Bootstrap supply voltage input. In conjunction with an internal diode to $V_S$ , a 0.1 $\mu F$ to 1.0 $\mu F$ ceramic capacitor connected between BST and DRN develops supply voltage for the high-side driver (TG). |

| 4   | СО             | Logic level control input produces complementary output states - no inversion at TG; inversion at BG.                                                                                                                |

| 5   | EN             | Logic level enable input forces TG and BG low when EN is low. When EN is high (5.0 V), normal operation ensues. No connect defaults EN high. Note: maximum high input is 5.0 V.                                      |

| 6   | V <sub>S</sub> | Power supply input. A 0.1 $\mu\text{F}$ to 1.0 $\mu\text{F}$ ceramic capacitor should be connected from this pin to PGND.                                                                                            |

| 7   | BG             | Driver output to the low-side (synchronous rectifier) MOSFET gate.                                                                                                                                                   |

| 8   | PGND           | Ground.                                                                                                                                                                                                              |

http://onsemi.com

ATX 12 V O-

#### **APPLICATIONS INFORMATION**

#### **Enable Pin**

The Enable pin allows logic level On/Off control of the NCP5355. A Logic Level Low (< 0.8 V) disables the part by forcing both TG and BG low. Bringing both gates low *prevents* the output voltage\_from ringing below ground at turn-off. A Logic Level High (> 2.0 V) enables the part by allowing CO to control TG and BG.

If the Enable function is not being used, the Enable pin should be left unconnected. This will Enable the part by default, as the Enable pin will be internally pulled high by a  $2.0~\mu A$  current. The maximum high voltage level is 5.0~V. Voltages greater than this may damage the part.

#### **Undervoltage Lockout**

Gates TG and BG are both held low until  $V_s$  reaches the UVLO Start Threshold of 8.0 V during startup.  $V_s$  exceeding the UVLO threshold allows CO to take control of both gates. If  $V_s$  falls below the UVLO Stop Threshold of 7.0 V, both gates are then forced low until  $V_s$  again exceeds the Start Threshold.

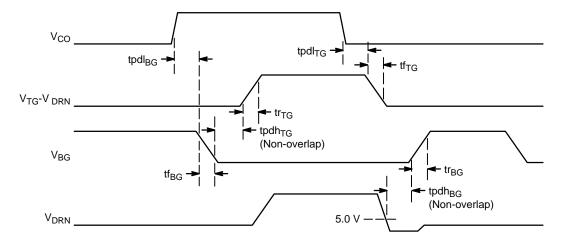

## **Supply Capacitor Selection**

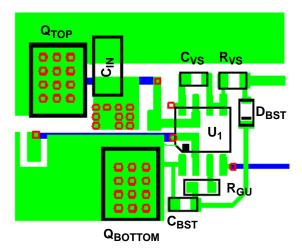

A 1.0  $\mu$ F ceramic capacitor ( $C_{VS}$  in Figure 4) should be located close to the  $V_s$  supply pins to provide peak current and to reduce noise. A small 1.0 to 5.0  $\Omega$  resistor ( $R_{VS}$  in Figure 4) may also be added in series with  $C_{VS}$  to provide additional filtering in noisy environments.

#### **Bootstrap Capacitor Selection**

The size of the Top MOSFET bootstrap capacitor ( $C_{BST}$  in Figure 4) is determined from the following equation:

$$C_{BST} \geq \frac{Q_{TtopFETs}}{\Delta V_{BST}}$$

where

Q<sub>TtopFETs</sub> is the sum of the Top MOSFETs total gate

charge,

$\Delta V_{BST} \hspace{0.5cm} \text{is the maximum change in voltage across}$

the bootstrap capacitor and is typically designed for a drop of less than a 1.0 V.

For example, a circuit using one Top MOSFET with a typical Q<sub>TtopFETs</sub> of 60 nC (at 12 V Vgs) and 1.0 V of droop would give a minimum value for C<sub>BST</sub> of 60 nF.

#### **Internal or External Bootstrap Diode**

For convenience, a bootstrap diode is internally provided by the NCP5355. This internal diode reduces system cost and parts count.

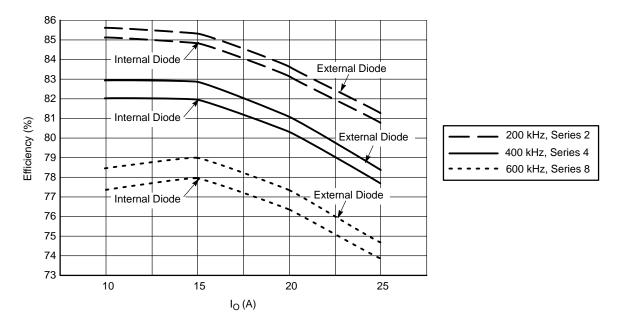

However, this diode will have higher losses than a standard small signal switching or schottky diode. By using an external schottky diode ( $D_{BST}$  in Figure 4) a small improvement in efficiency can be achieved as illustrated by the graph in Figure 5.

While the difference in efficiency is relatively small, this difference represents heat loss in the driver and on average driver temperature may be reduced by about 10°C if using an external diode. If an external diode is used, it should be a Schottky or switching diode. (For example: ON Semiconductor Part Number BAT54HT1 or BAS16HT1.)

#### **Adaptive Nonoverlap**

The NCP5355 includes adaptive nonoverlap protection to prevent top and bottom MOSFET cross conduction.

When CO goes low signaling TG to turn off the top MOSFET, BG does not go high until the switch node (DRN pin) has fallen below 5.0~V and a fixed amount of delay (tpdh<sub>BG</sub>) has elapsed. This ensures that the top MOSFET is off before the bottom MOSFET is turned on.

Figure 4. Typical NCP5355 Application

Figure 5. Efficiency With and Without an Added External Bootstrap Diode, See Figure 4 for Test Circuit

When CO goes high signaling BG turn off the Bottom MOSFET, TG does not go high until BG has fallen below a threshold of 5.0 V and a fixed amount of time has elapsed (tpdh<sub>TG</sub>).

However, caution must be observed if too much gate resistance and inductance is introduced into the path between the IC and the gate of the low MOSFET. A condition can occur where the NCP5355 will sense that BG has fallen below 5.0 V while the gate end of the MOSFET still has not fallen low enough to turn off the device. This parasitic gate impedence between the driver and MOSFET can reduce the nonoverlap time, and result in shoot-through currents.

# **Power Dissipation**

Driver power dissipation may be approximated by the following equation:

$$\begin{aligned} P_{loss} &= f_{SW} \cdot V_{S} \cdot (1.5 \cdot Q_{TtopFET_{S}} + Q_{TbottomFET_{S}}) \\ &+ V_{S} \cdot I_{S} \end{aligned}$$

where

$f_{SW}$  is the switching frequency,  $V_s$  is the supply voltage,

$Q_{TtopFETs}$  is the sum of the Top MOSFETs total

gate charge,

Q<sub>TbottomFETs</sub> is the sum of the Bottom MOSFETs

total gate charge

I<sub>s</sub> is the supply quiescent current, typically

around 5.0 mA

The 1.5 factor is a result of the internal bootstrap diode whose loss is equivalent to the charge lost in turning on the Top MOSFET. If an external diode is used to improve efficiency, the 1.5 factor is replaced with 1.0 as this loss will now occur outside the package.

Safe design practice requires limiting the SO8 device power dissipation to around 700 mW. Higher frequency designs may require limiting the supply voltage ( $V_s$ ) to less than 12 V to maintain this limit.

#### Switch Node Overshoot and Ringing

Due to the high current sourcing capability of the NCP5355, increased overshoot and ringing may be noticed at the switch node (DRN pin). This can be reduced in several ways.

One is by adding a low ESR 1.0-10  $\mu$ F ceramic capacitor ( $C_{IN}$  in Figure 4) from  $V_{IN}$  to ground near each Qtop. This capacitor should be located in such a manner as to reduce the loop area of the switch node as shown in Figure 6. A smaller loop area from  $C_{IN}$ + to Qtop to Qbottom and back to  $C_{IN}$ -will reduce the amount of ringing by reducing the PCB inductance. If further reduction in overshoot and ringing is desired, a Top MOSFET gate drive resistor may be added ( $R_{GU}$  in Figure 4) to slow the turn-on of the Top MOSFET without increasing the turn-off time.

# **Layout Guidelines**

When designing any switching regulator, the layout is very important for proper operation. Gate drivers experience high di/dt during switching, and the inductance of the gate drive traces need to be minimized. Gate drive traces should be kept as short and wide (25 to 30 mils) as practical, and should have a return path directly below the gate trace. The use of a ground plane is a desirable way to return ground

signals. Component location is very important. The boost and the  $V_s$  capacitor are the most critical, and need to be placed as close as possible to the driver IC pins ( $C_{VS}$  and  $C_{BST}$  in Figure 4) as shown in Figure 6. Higher frequency designs will magnify any layout problems, and added attention to these guidelines should be observed in designs above 250 kHz.

Figure 6. Typical NCP5355 PCB Layout

# **PACKAGE DIMENSIONS**

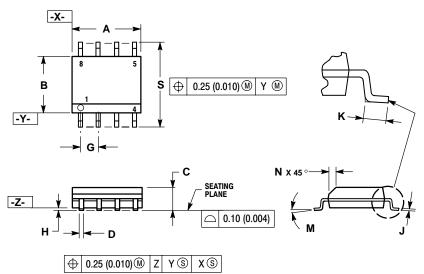

## **SO-8 D SUFFIX** CASE 751-07 **ISSUE AA**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07

|     | MILLIMETERS |          | INCHES |           |  |

|-----|-------------|----------|--------|-----------|--|

| DIM | MIN         | MIN MAX  |        | MAX       |  |

| Α   | 4.80        | 5.00     | 0.189  | 0.197     |  |

| В   | 3.80        | 4.00     | 0.150  | 0.157     |  |

| С   | 1.35        | 1.75     | 0.053  | 0.069     |  |

| D   | 0.33        | 0.51     | 0.013  | 0.020     |  |

| G   | 1.27        | 1.27 BSC |        | 0.050 BSC |  |

| Н   | 0.10        | 0.25     | 0.004  | 0.010     |  |

| J   | 0.19        | 0.25     | 0.007  | 0.010     |  |

| K   | 0.40        | 1.27     | 0.016  | 0.050     |  |

| M   | 0 °         | 8 °      | 0 °    | 8 °       |  |

| N   | 0.25        | 0.50     | 0.010  | 0.020     |  |

| S   | 5.80        | 6.20     | 0.228  | 0.244     |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

## Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada **Fax**: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051

Phone: 81-3-5773-3850

$\textbf{ON Semiconductor Website}: \ \text{http://onsemi.com}$

For additional information, please contact your local

Sales Representative.