# agere

# LCK4310 Low-Voltage PLL Clock Driver

# Features

- Output operating frequencies up to 1.25 GHz max.

- 100 ps part-to-part skew.

- 40 ps typical output-to-output skew.

- Cycle-to-cycle jitter less than 7 ps max.

- 3.3 V and 2.5 V compatible.

- Internal input pulldown resistors.

- Q output will default low with inputs open or at VEE.

- Meets or exceeds Joint Electron Device Engineering Council (JEDEC) specification EIA<sup>®</sup>/ JESD78 IC latchup test.

- Moisture sensitivity level 1.

- Flammability rating: UL<sup>®</sup>-94 code V-0 at 1/8 in., oxygen index 28 to 34.

- Pin-for-pin compatible with ON Semiconductor<sup>®</sup> part number MC100LVE310.

# Description

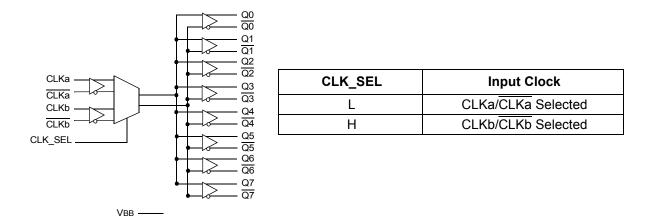

The LCK4310 is a low-voltage, low-skew 2:8 differential emitter-coupled logic (ECL) fanout buffer designed with clock distribution in mind. The device features fully differential clock paths to minimize both device and system skew. The LCK4310 offers two selectable clock inputs to allow for redundant or test clocks to be incorporated into the system clock trees. To ensure that the tight skew specification is met, it is necessary that both sides of the differential output are terminated into  $50 \Omega$ , even if only one side is being used. In most applications, all eight differential pairs will be used and therefore terminated. In the case where fewer than eight pairs are used and in order to maintain minimum skew, it is necessary to terminate at least the output pairs adjacent to the output pair being used. Failure to follow this guideline will result in small degradations of propagation delay (on the order of 10 ps—20 ps) of the outputs being used, while not catastrophic to most designs this will result in an increase in skew.

**Note:** The package corners isolate outputs from one another such that the guideline expressed above holds only for outputs on the same side of the package.

The LCK4310, as with most ECL devices, can be operated from a positive voltage supply (VDD) in LVPECL mode. This allows the LCK4310 to be used for high performance clock distribution in 3.3 V/2.5 V systems. Designers can take advantage of the LCK4310's performance to distribute low-skew clocks across the backplane or the board. In a PECL environment (series or Thevenin), line terminations are typically used as they require no additional power supplies. If parallel termination is desired, a terminating voltage of VDD – 2.0 V will need to be provided.

An internally generated voltage supply (VBB pin) is available to this device only. For single-ended input conditions, the unused differential input is connected to VBB as a switching reference voltage. VBB may also rebias ac coupled inputs. When used, decouple VBB and VDD via a 0.01  $\mu$ F capacitor and limit current sourcing or sinking to 0.5 mA. When not used, VBB should be left open.

# **Pin Information**

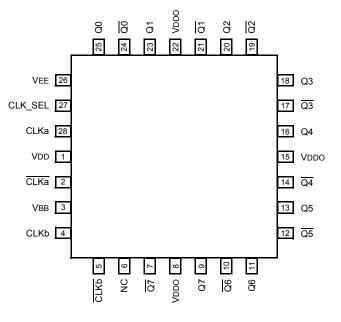

# Pin Diagram

# WARNING: All VDD, VDDO, and VEE pins must be externally connected to a power supply to guarantee proper operation.

#### **Pin Descriptions**

#### Table 1. Pin Descriptions

| Pin                              | Symbol  | Туре    | I/O | Description                                                         |

|----------------------------------|---------|---------|-----|---------------------------------------------------------------------|

| 1                                | Vdd     | Power   | —   | Positive Power Supply.                                              |

| 2                                | CLKa    | PECL    | I   | ECL Differential Input Clock. Makes input pair with CLKa.           |

| 3                                | VBB     | VREFOUT | 0   | Reference Voltage Output.                                           |

| 4                                | CLKb    | LVTTL   | I   | ECL Differential Input Clock. Makes input pair with CLKb.           |

| 5                                | CLKb    | LVTTL   | I   | ECL Differential Input Clock. Makes input pair with CLKb.           |

| 6                                | NC      | —       |     | No Connect.                                                         |

| 7, 10, 12, 14, 17,<br>19, 21, 24 | Q[7:0]  | PECL    | 0   | ECL Differential Outputs.                                           |

| 8, 15, 22                        | Vddo    | Power   |     | Positive Power Supply.                                              |

| 9, 11, 13, 16, 18,<br>20, 23, 25 | Q[7:0]  | PECL    | 0   | ECL Differential Outputs.                                           |

| 26                               | VEE     | Power   | _   | Negative Power Supply.                                              |

| 27                               | CLK_SEL | LVTTL   | I   | ECL Input Clock Select.<br>0 = CLKa selected.<br>1 = CLKb selected. |

| 28                               | CLKa    | LVTTL   | Ι   | ECL Differential Input Clock. Makes input pair with CLKa.           |

# Pin Information (continued)

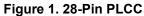

# Logic Symbol

Figure 2. Logic Symbol

# **Absolute Maximum Ratings**

Stresses which exceed the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods of time can adversely affect device reliability.

| Parameter                 | Symbol | Conditions               | Min     | Max     | Unit |

|---------------------------|--------|--------------------------|---------|---------|------|

| PECL Mode Positive Power  | Vdd    | VEE = 0 V                |         | 5       | V    |

| Supply                    |        |                          |         |         |      |

| Input Voltage:            | VI     |                          |         |         |      |

| PECL Mode Positive Input  |        | VEE = 0 V, $VI \leq VDD$ | 0       | 5       | V    |

| Voltage                   |        |                          |         |         |      |

| Output Current            | Ιουτ   | Continuous surge         | 50      | 100     | mA   |

| VBB Sink/Source           | IBB    |                          | -0.5    | 0.5     | mA   |

| Storage Temperature Range | Tstg   |                          | -65     | 150     | °C   |

| Ambient Temperature       | TA     |                          | -40     | 85      | °C   |

| Thermal Resistance        | θJA    | 0 LFPM, 28 PLCC          |         | 63.5    | °C/W |

| (junction to ambient)     |        | 500 LFPM, 28 PLCC        | —       | 43.5    |      |

| Thermal Resistance        | θJC    | Standard board, 28 PLCC  | 22 ± 5% | 26 ± 5% | °C/W |

| (junction to case)        |        |                          |         |         |      |

| Wave Solder               | TSOL   | <2 s to 3 s at 248 °C    |         | 265     | °C   |

# **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Agere Systems employs a human-body model (HBM) and charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used in the defined model. No industrywide standard has been adopted for the CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes.

#### **Table 3. ESD Protection Characteristics**

| Device  | Minimum Threshold |

|---------|-------------------|

|         | НВМ               |

| LCK4310 | >2,000 V          |

## **Electrical Characteristics**

#### dc Characteristics

#### Table 4. LVPECL 3.3 V dc Characteristics

VDD = 3.3 V, VEE = 0 V. Input and output parameters vary 1:1 with VDD. VEE can vary ±0.3 V. Devices are designed to meet the dc specifications shown in Table 4 below, after thermal equilibrium has been established.

| Parameter                                                              | Symbol | –40 °C |       | 25 °C |       |       | 85 °C |       |       | Unit  |    |

|------------------------------------------------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----|

|                                                                        |        | Min    | Тур   | Мах   | Min   | Тур   | Мах   | Min   | Тур   | Max   |    |

| Power Supply Current                                                   | IEE    |        | 55    | 60    |       | 55    | 60    | _     | 65    | 70    | mA |

| Output High Voltage*                                                   | Vон    | 2,215  | 2,295 | 2,420 | 2,275 | 2,345 | 2,420 | 2,275 | 2,345 | 2,420 | mV |

| Output Low Voltage*                                                    | Vol    | 1,470  | 1,605 | 1,745 | 1,490 | 1,595 | 1,680 | 1,490 | 1,595 | 1,680 | mV |

| Input High Voltage<br>(single-ended)                                   | Vih    | 2,135  | —     | 2,420 | 2,135 | _     | 2,420 | 2,135 | —     | 2,420 | mV |

| Input Low Voltage<br>(single-ended)                                    | VIL    | 1,490  | _     | 1,825 | 1,490 | -     | 1,825 | 1,490 | _     | 1,825 | mV |

| Output Voltage<br>Reference                                            | VBB    | 1.92   | _     | 2.06  | 1.92  | -     | 2.06  | 1.92  | _     | 2.06  | V  |

| Input High Voltage<br>Common-mode<br>Range (differential) <sup>†</sup> | VIHCMR | 1.8    | —     | 2.9   | 1.8   | —     | 2.9   | 1.8   | —     | 2.9   | V  |

| Input High Current                                                     | Іін    | —      | _     | 150   |       | —     | 150   | _     | _     | 150   | μA |

| Input Low Current                                                      | lı∟    | 0.5    | _     | _     | 0.5   | _     | _     | 0.5   | —     | —     | μA |

Outputs are terminated through a 50  $\Omega$  resistor to VDD – 2 V. VIHCMR minimum varies 1:1 with VEE, maximum varies 1:1 with VDD. VIHCMR is defined as the range within which the VIH level may vary, with the device still meeting the propagation delay specification. The VIL level must be such that the peak-to-peak voltage is less † than 1.0 V and greater than or equal to Vp-pmin.

# Electrical Characteristics (continued)

#### dc Characteristics (continued)

#### Table 5. LVPECL 2.5 V dc Characteristics

VDD = 2.5 V, VEE = 0 V. Input and output parameters vary 1:1 with VDD. VEE can vary ±0.3 V. Devices are designed to meet the dc specifications shown in Table 5 below, after thermal equilibrium has been established.

| Parameter                                                              | Symbol | –40 °C |      | 25 °C |       |      | 85 °C |       |      | Unit  |    |

|------------------------------------------------------------------------|--------|--------|------|-------|-------|------|-------|-------|------|-------|----|

|                                                                        |        | Min    | Тур  | Max   | Min   | Тур  | Мах   | Min   | Тур  | Max   |    |

| Power Supply Current                                                   | IEE    |        | 55   | 60    | _     | 55   | 60    |       | 65   | 70    | mA |

| Output High Voltage*                                                   | Vон    | 1425   | 1495 | 1620  | 1425  | 1507 | 1620  | 1425  | 1520 | 1620  | mV |

| Output Low Voltage*                                                    | Vol    | 730    | 790  | 955   | 730   | 820  | 955   | 730   | 825  | 955   | mV |

| Input High Voltage<br>(single-ended)                                   | Vih    | 2000   | _    | 2400  | 2000  | _    | 2400  | 2000  | _    | 2400  | mV |

| Input Low Voltage<br>(single-ended)                                    | VIL    | 400    | _    | 1030  | 400   | _    | 1030  | 400   | _    | 1030  | mV |

| Output Voltage<br>Reference                                            | VBB    | 1.019  | _    | 1.361 | 1.019 | _    | 1.361 | 1.019 | -    | 1.361 | V  |

| Input High Voltage<br>Common-mode<br>Range (differential) <sup>†</sup> | VIHCMR | 1.0    | —    | 2.1   | 1.0   | —    | 2.1   | 1.0   | —    | 2.1   | V  |

| Input High Current                                                     | Іін    | —      | —    | 150   | —     | —    | 150   | _     | —    | 150   | μA |

| Input Low Current                                                      | ١L     | 0.5    |      | _     | 0.5   |      | _     | 0.5   | _    | —     | μA |

\* Outputs are terminated through a 50 Ω resistor to VDD – 2 V.

† VIHCMR minimum varies 1:1 with VEE, maximum varies 1:1 with VDD. VIHCMR is defined as the range within which the VIH level may vary, with the device still meeting the propagation delay specification. The VIL level must be such that the peak-to-peak voltage is less than 1.0 V and greater than or equal to Vp-pmin.

#### **Electrical Characteristics** (continued)

#### ac Characteristics

VDD = 3.3/2.5 V, VEE = 0 V, or VDD = 0 V, VEE = -3.3/2.5 V.  $VEE can vary \pm 0.3 V$ .

#### Table 6. ac Characteristics

| Parameter                                        | Symbol          | –40 °C |     | 25 °C |     |     | 85 °C |     |     | Unit  |     |

|--------------------------------------------------|-----------------|--------|-----|-------|-----|-----|-------|-----|-----|-------|-----|

|                                                  |                 | Min    | Тур | Max   | Min | Тур | Max   | Min | Тур | Max   |     |

| Maximum Toggle<br>Frequency                      | fMAX            | _      | _   | 1.25  | _   | _   | 1.25  |     | —   | 1.25  | GHz |

| Propagation Delay to<br>Output:                  |                 |        |     |       |     |     |       |     |     |       | ps  |

| In (differential)*                               | tPLH            | 525    | —   | 725   | 550 | —   | 750   | 575 | —   | 775   |     |

| In (single-ended) <sup>†</sup>                   | <b>t</b> PHL    | 500    | —   | 750   | 550 | —   | 800   | 600 | —   | 850   |     |

| Within Device Skew <sup>‡</sup>                  | tskew           | _      |     | 40    |     |     | 40    |     |     | 40    | ps  |

| Part-to-part Skew <sup>‡</sup><br>(differential) | tskew           | _      | —   | 100   | _   | _   | 100   |     | —   | 100   | ps  |

| Cycle-to-cycle Jitter                            | <b>I</b> JITTER | —      | —   | 7     | _   | _   | 7     | _   | —   | 7     | ps  |

| Input Swing <sup>§</sup>                         | Vp-p            | 500    | —   | 1,000 | 500 | —   | 1,000 | 500 | —   | 1,000 | mV  |

| Output Rise/Fall Time<br>(20%—80%)               | tr/tf           | 200    |     | 600   | 200 |     | 600   | 200 |     | 600   | ps  |

The differential propagation delay is defined as the delay from the crossing points of the differential input signals to the crossing point of the differential output signals. The single-ended propagation delay is defined as the delay from the 50% point of the input signal to the 50% point of the output signal. The within device skew is defined as the worst case difference between any two similar delay paths within a single device. Vp-pmin is defined as the minimum input differential voltage which will cause no increase in the propagation delay. The Vp-pmin is ac limited for the LCK4310 as a differential input as low as 50 mV will still produce full ECL levels at the output.

‡ §

Figure 3. Typical Termination for Output Driver and Device Evaluation

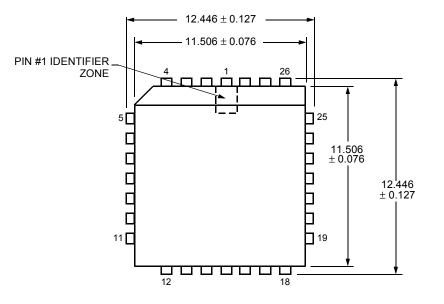

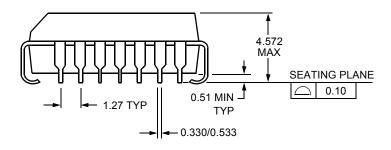

# **Outline Diagrams**

Dimensions are in millimeters.

5-2608 (F)

## **Ordering Information**

| Device  | Part Number  | Pin Count | Package | Туре | Comcode   |

|---------|--------------|-----------|---------|------|-----------|

| LCK4310 | LCK4310GF-DB | 28        | PLCC    | Reel | 700020216 |

|         | LCK4310GF-DT | 28        | PLCC    | Таре | 700020217 |

*EIA* is a registered trademark of Electronic Industries Association.

UL is a registered is a registered trademark of Underwriters Laboratories, Inc.

ON Semiconductor is a registered trademark of Semiconductor Components Industries, L.L.C.

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET:

http://www.agere.com

E-MAIL:

docmaster@agere.com

N. AMERICA:

Agere Systems Inc., Lehigh Valley Central Campus, Room 10A-301C, 1110 American Parkway NE, Allentown, PA 18109-9138

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA:

Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shanghai), (86) 755-25881122 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

EUROPE:

Tel. (44) 1344 296 400

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. Agere, Agere Systems, and the Agere logo are trademarks of Agere Systems Inc.

Copyright © 2003 Agere Systems Inc. All Rights Reserved