## LXT901/907

## Universal 10BASE-T and AUI Transceivers

## **General Description**

The LXT901 and LXT907 Universal 10BASE-T and AUI Transceivers are designed for IEEE 802.3 physical layer applications. They provide all the active circuitry to interface most standard 802.3 controllers to either the 10BASE-T media or Attachment Unit Interface (AUI). In addition to standard 10 Mbps Ethernet, they also support full-duplex operation at 20 Mbps.

The LXT901 and LXT907 are identical except for the function of one pin. The LXT901 offers selectable termination impedance to allow the use of either shielded or unshielded twisted-pair cable. The LXT907 offers a signal quality error (SQE) disable function.

Common LXT901 and LXT907 functions include Manchester encoding/decoding, receiver squelch and transmit pulse shaping, jabber, link testing and reversed polarity detection/correction. Integrated filters simplify the required for FCC-compliant EMI design work performance.

## Applications

- 10BASE-T hub and switching products

- Computer/Workstation 10BASE-T LAN adapters

### **Features**

### **Functional Features**

- Integrated Manchester Encoder/Decoder

- 10BASE-T Transceiver

- · AUI Transceiver

- Full-Duplex Capable (20 Mbps)

#### **Convenience Features**

- Automatic/Manual AUI/RJ45 Selection

- **Automatic Polarity Correction**

- SOE Disable function (*LXT907 only*)

- Programmable Impedance Driver (*LXT901 only*)

- Power Down Mode and four loopback modes

- LXT901 available in 64-pin LQFP and 44-pin PLCC

- LXT907 available in 44-pin PLCC

### **Diagnostic Features**

- · Four LED Drivers

- AUI/RJ45 Loopback

- · Remote Signaling of Link Down and Jabber conditions

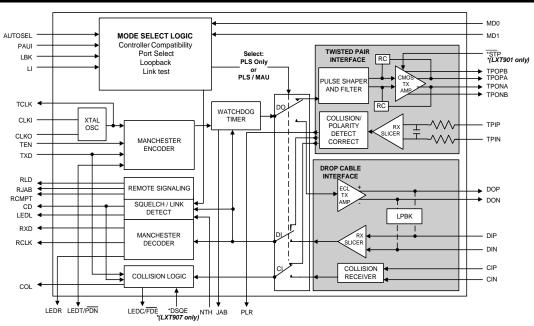

## LXT901/907 Block Diagram

Refer to www.level1.com for most current information.

## **TABLE OF CONTENTS**

| Pin Assignments and Signal Descriptions                                                  | 3              |

|------------------------------------------------------------------------------------------|----------------|

| Functional Description                                                                   | 7              |

| Controller Compatibility Modes                                                           | 7              |

| Transmit Function Jabber Control Function SQE Function                                   | 8              |

| Receive Function                                                                         |                |

| Collision Detection Function                                                             |                |

| Loopback Function Standard TP Loopback External Loopback Forced TP Loopback AUI Loopback | 10<br>10<br>10 |

| Link Integrity Test FunctionRemote Signaling                                             |                |

| Application Information                                                                  | 13             |

| Twisted-Pair Impedance Matching                                                          | 13             |

| Crystal Information                                                                      | 13             |

| Magnetics Information                                                                    | 13             |

| Typical Applications  Auto Port Select with External Loopback                            | 14             |

| Full - Duplex Support                          | .16  |

|------------------------------------------------|------|

| Dual Network Support - 10BASE-T and Token Ring | . 17 |

| Manual Port Select & Link Test Function        |      |

| Three Media Application                        | 20   |

| AUI Encoder/Decoder Only                       |      |

| Shielded Twisted-Pair Only                     | .22  |

| Fest Specifications                            | 23   |

| Absolute Maximum Ratings                       |      |

| Recommended Operating Conditions               | 23   |

| I/O Electrical Characteristics                 |      |

| AUI Electrical Characteristics                 | .24  |

| Twisted-Pair Electrical Characteristics        | .24  |

| Switching Characteristics                      | 25   |

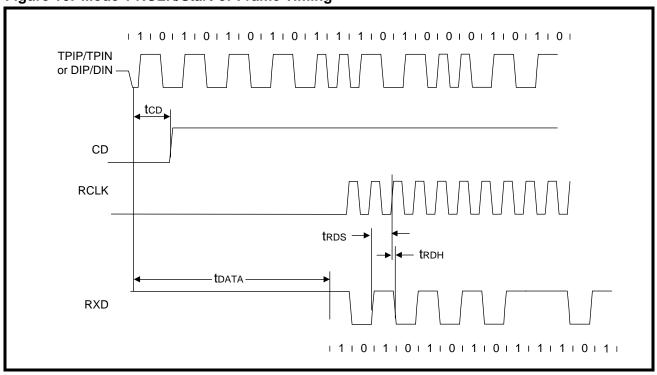

| RCLK/Start-of-Frame Timing                     | 25   |

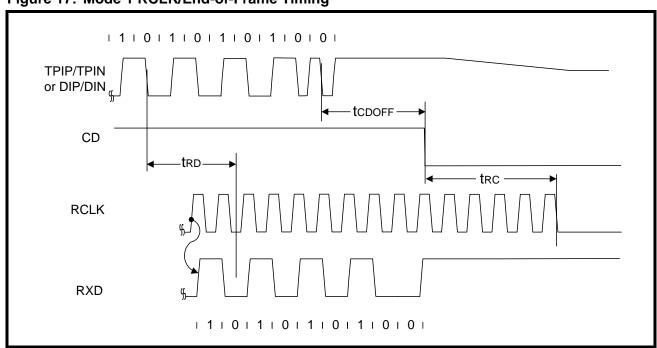

| RCLK/End-of-Frame Timing                       | 26   |

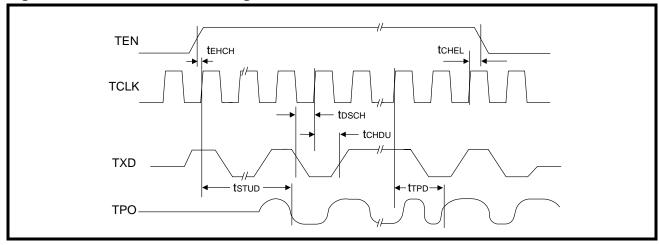

| Transmit Timing                                | 26   |

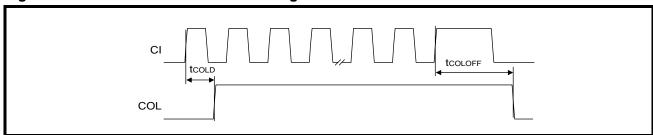

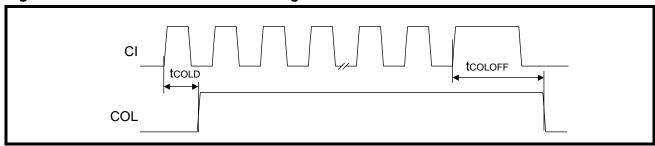

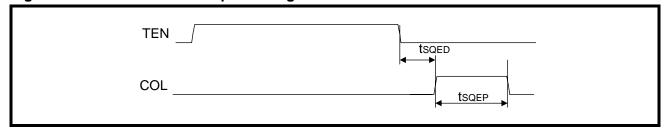

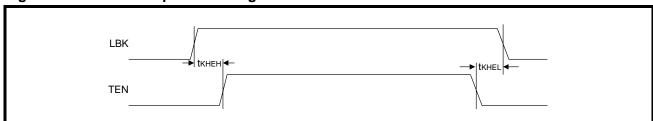

| Collision, COL/CI Output and Loopback Timing   | 27   |

| Mode 1 Timing Diagrams                         | 28   |

| Mode 2 Timing Diagrams                         | 30   |

| Mode 3 Timing Diagrams                         | .32  |

| Mode 4 Timing Diagrams                         | 36   |

| Mechanical Specifications                      | .38  |

| Revision History                               | 30   |

## PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

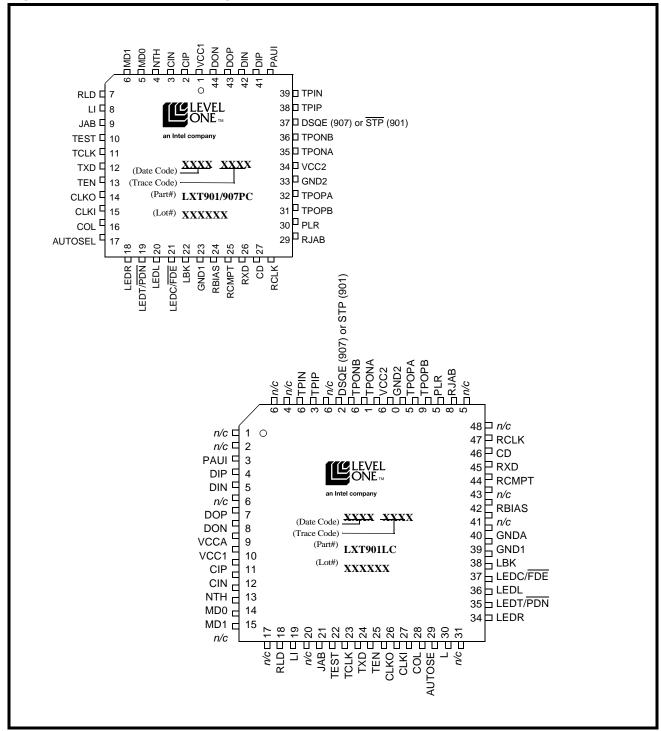

Figure 1: LXT901/907 Pin Assignments

Table 1: LXT901/907 Signal Descriptions

| PLCC        | LQFP        | Symbol            | I/O      | Description                                                                                                                                                                                                                                        |

|-------------|-------------|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>34     | 10<br>56    | VCC1<br>VCC2      | I<br>I   | <b>Power Inputs.</b> Power supply inputs of +5 volts.                                                                                                                                                                                              |

| -           | 9           | VCCA              | I        | (LQFP Only)                                                                                                                                                                                                                                        |

| 2<br>3      | 11<br>12    | CIP<br>CIN        | I<br>I   | <b>AUI Collision Pair.</b> Differential input to the AUI transceiver CI circuit. The input is collision signaling or SQE.                                                                                                                          |

| 4           | 13          | NTH               | Ι        | Normal Threshold. Selects normal or reduced threshold.  When NTH is High, the normal TP squelch threshold is in effect.  When NTH is Low, the normal TP squelch threshold is reduced by 4.5 dB.                                                    |

| 5<br>6      | 14<br>15    | MD0<br>MD1        | I<br>I   | Mode Select 0 (MD0), Mode Select 1 (MD1). Mode select pins determine the controller compatibility mode in accordance with Table 2.                                                                                                                 |

| 7           | 18          | RLD               | О        | <b>Remote Link Down.</b> Output goes high to signal to the controller that the remote port is in link down condition.                                                                                                                              |

| 8           | 19          | LI                | 1        | <b>Link Test Enable.</b> Controls Link Integrity Test; enabled when LI = High, disabled when LI = Low                                                                                                                                              |

| 9           | 21          | JAB               | О        | Jabber Indicator. Output goes High to indicate Jabber state.                                                                                                                                                                                       |

| 10          | 22          | TEST              | I        | <b>Test.</b> For Level One internal use only. It is recommended to tie this pin High externally.                                                                                                                                                   |

| 11          | 23          | TCLK              | O        | <b>Transmit Clock.</b> A 10 MHz clock output. This clock signal should be directly connected to the transmit clock input of the controller.                                                                                                        |

| 12          | 24          | TXD               | I        | <b>Transmit Data.</b> Input signal containing NRZ data to be transmitted on the network. Connect TXD directly to the transmit data output of the controller.                                                                                       |

| 13          | 25          | TEN               | Ι        | <b>Transmit Enable.</b> Enables data transmission and starts the watchdog timer. Synchronous to TCLK (see Test Specifications for details).                                                                                                        |

| 14<br>15    | 26<br>27    | CLKO<br>CLKI      | O<br>I   | <b>Crystal Oscillator.</b> A 20 MHz crystal must be connected across these pins, or a 20 MHz clock applied at CLKI with CLKO left open.                                                                                                            |

| 16          | 28          | COL               | О        | <b>Collision Detect.</b> Output which drives the collision detect input of the controller.                                                                                                                                                         |

| 17          | 29          | AUTOSEL           | Ι        | Automatic Port Select.  When High, automatic port selection is enabled (the 901/907 defaults to the AUI port only if TP link integrity = Fail).                                                                                                    |

|             |             |                   |          | When Low, manual port selection is enabled (the PAUI pin determines the active port).                                                                                                                                                              |

| 18          | 34          | LEDR              | OD       | <b>Receive LED.</b> Open drain driver for the receive indicator LED. Output is pulled Low during receive.                                                                                                                                          |

| 19          | 35          | LEDT/<br>PDN      | OD<br>I  | Transmit LED (LEDT)/Power Down (PDN). Open drain driver for the transmit indicator. Output is pulled Low during transmit. Do not allow this pin to float. If unused, tie High.  If externally pulled Low, the LXT901/907 goes to power down state. |

| 1. I/O Colu | umn Coding: | I = Input, O = Ou | tput, OD | = Open Drain                                                                                                                                                                                                                                       |

Table 1: LXT901/907 Signal Descriptions – continued

| PLCC      | LQFP | Symbol       | I/O     | Description                                                                                                                                                                                                                               |

|-----------|------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20        | 36   | LEDL         | OD<br>I | Link LED. Open drain driver for link integrity indicator. Output is pulled Low during link test pass.  If externally tied Low, internal circuitry is forced to "Link Pass" state and the 901/907 transmits link test pulses continuously. |

| 21        | 37   | LEDC/<br>FDE | OD      | <b>Collision LED (LEDC)/Full Duplex Enable (FDE).</b> Open drain driver for the collision indicator pulls Low during collision. LED "On"(i.e., Low output) time is extended by approximately 100 ms.                                      |

|           |      |              |         | If externally tied Low, the LXT901/907 enables full duplex operation by disabling the internal TP loopback and collision detection circuits in anticipation of external TP loopback or full duplex operation.                             |

|           |      |              |         | If this pin is not used, tie high or directly to VCC.                                                                                                                                                                                     |

| 22        | 38   | LBK          | I       | <b>Loopback.</b> Enables internal loopback mode.<br>Refer to Functional Descriptions for details.                                                                                                                                         |

| 23        | 39   | GND1         | _       | Ground Returns. Grounds                                                                                                                                                                                                                   |

| 33        | 55   | GND2         | _       | (COPPO 1)                                                                                                                                                                                                                                 |

| _         | 40   | GNDA         | _       | (LQFP Only)                                                                                                                                                                                                                               |

| 24        | 42   | RBIAS        | I       | <b>Bias Control.</b> A 12.4 k $\Omega$ 1% resistor to ground at this pin controls operating circuit bias.                                                                                                                                 |

| 25        | 44   | RCMPT        | О       | <b>Remote Compatibility.</b> Output goes High to signal the controller that the remote port is compatible with the LXT901/LXT907 remote signaling features.                                                                               |

| 26        | 45   | RXD          | О       | <b>Receive Data.</b> Connect RXD directly to the receive data input of the controller.                                                                                                                                                    |

| 27        | 46   | CD           | О       | <b>Carrier Detect.</b> An output to notify the controller of activity on the network.                                                                                                                                                     |

| 28        | 47   | RCLK         | О       | <b>Receive Clock.</b> A recovered 10 MHz clock which is synchronous to the received data. Connect to the controller receive clock input.                                                                                                  |

| 29        | 51   | RJAB         | О       | <b>Remote Jabber.</b> Output goes High to indicate the remote port is in Jabber condition.                                                                                                                                                |

| 30        | 52   | PLR          | 0       | <b>Polarity Reverse.</b> Output goes High to indicate reversed polarity at the TP input.                                                                                                                                                  |

| 1 1/0 0 1 | C 1' |              |         | 0 0                                                                                                                                                                                                                                       |

<sup>1.</sup> I/O Column Coding: I = Input, O = Output, OD = Open Drain

Table 1: LXT901/907 Signal Descriptions – continued

| PLCC                 | LQFP                                                                                        | Symbol                           | I/O              | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31<br>36<br>32<br>35 | 53<br>58<br>54<br>57                                                                        | TPOPB<br>TPONB<br>TPOPA<br>TPONA | 0<br>0<br>0<br>0 | <b>Twisted-Pair Transmit Pairs A &amp; B.</b> Two differential driver pair outputs (A and B) to the twisted-pair cable. The outputs are pre-equalized. Each pair must be shorted together and tied to the transformer with a 24.9 $\Omega$ 1% series resistor to match impedance of $100\Omega$ . Refer to Figure 15 in the Applications Section for information on $150\Omega$ configurations. |

| 37                   | 59                                                                                          | STP<br>(LXT901)                  | I                | STP Select (LXT901 only).  When $\overline{STP}$ is Low, 150 $\Omega$ termination for shielded TP is selected.  When $\overline{STP}$ is High, 100 $\Omega$ termination for unshielded TP is selected.  LXT907 is designed for 100 $\Omega$ UTP termination (not selectable).                                                                                                                   |

|                      |                                                                                             | DSQE<br>( <b>LXT907</b> )        | I                | Disable SQE (LXT907 only).  When DSQE is High, the SQE function is disabled.  When DSQE is Low, the SQE function is enabled.  SQE must be disabled for normal operation in Hub/Switch applications.  LXT901operates with SQE enabled (not selectable).                                                                                                                                          |

| 38<br>39             | 61<br>62                                                                                    | TPIP<br>TPIN                     | I<br>I           | Twisted-Pair Receive Pair. A differential input pair from the TP cable.  Receive filter is integrated on-chip. No external filters are required.                                                                                                                                                                                                                                                |

| 40                   | 3                                                                                           | PAUI                             | I                | Port/AUI Select. In Manual Port Select mode (AUTOSEL Low), PAUI selects the active port.  When PAUI is High, the AUI port is selected.  When PAUI is Low, the TP port is selected.  In Auto Port Select mode, PAUI must be tied to ground.                                                                                                                                                      |

| 41<br>42             | 4<br>5                                                                                      | DIP<br>DIN                       | I                | <b>AUI Receive Pair.</b> Differential input pair from the AUI transceiver DI circuit. The input is Manchester encoded.                                                                                                                                                                                                                                                                          |

| 43<br>44             | 7<br>8                                                                                      | DOP<br>DON                       | 0<br>0           | <b>AUI Transmit Pair.</b> A differential output driver pair for the AUI transceiver cable. The output is Manchester encoded.                                                                                                                                                                                                                                                                    |

| -                    | 1, 2, 6,<br>16, 17,<br>20, 30,<br>31, 32,<br>33, 41,<br>43, 48,<br>49, 50,<br>60, 63,<br>64 | N/C                              | -                | No Connect (Internally tied to ground).                                                                                                                                                                                                                                                                                                                                                         |

<sup>1.</sup> I/O Column Coding: I = Input, O = Output, OD = Open Drain

## **FUNCTIONAL DESCRIPTION**

The LXT901/907 Universal 10BASE-T and AUI Transceivers perform the physical layer signaling (PLS) and Media Attachment Unit (MAU) functions as defined by the IEEE 802.3 specification. They function as PLS-Only devices (for use with 10BASE-2 or 10BASE-5 coaxial cable networks) or as Integrated PLS/MAU devices (for use with 10BASE-T twisted-pair networks). In addition to standard 10 Mbps operation, they also support full-duplex 20 Mbps operation. Unless otherwise noted, all the information in this data sheet applies to both the LXT901 and LXT907.

The LXT901/907 interface a back end controller to either an AUI drop cable or a twisted-pair (TP) cable. The controller interface includes transmit and receive clock and NRZ data channels, as well as mode control logic and signaling. The AUI interface comprises three circuits: Data Output (DO), Data Input (DI) and Collision (CI). The twisted-pair interface comprises two circuits: Twisted-Pair Input (TPI) and Twisted-Pair Output (TPO). In addition to the three basic interfaces, the LXT901/907 contain an internal crystal oscillator and four LED drivers for visual status reporting.

Functions are defined from the back end controller side of the interface. The Transmit function refers to data transmitted by the back end to the AUI cable (PLS-Only mode) or to the twisted-pair network (Integrated PLS/MAU mode). The Receive function refers to data received by the back end from the AUI cable (PLS-Only) or from the twisted-pair network (Integrated PLS/MAU mode). In the integrated PLS/MAU mode, the LXT901/907 perform all required MAU functions defined by the IEEE 802.3 10BASE-T specification such as collision detection, link integrity testing, signal quality error messaging, jabber control and loopback. In the PLS-Only mode, the LXT901/907 receive incoming signals from the AUI DI circuit with  $\pm\,18$  ns of jitter and drives the AUI DO circuit.

## Controller Compatibility Modes

The LXT901/907 are compatible with most industry standard controllers including devices produced by Motorola, AMD, Intel, Fujitsu, National Semiconductor, Seeq and Texas Instruments. Four different control signal timing and polarity schemes (Modes 1 through 4) are required to achieve this compatibility. Mode select pins (MD0 and MD1) determine controller compatibility modes as listed in Table 2. Refer to Test Specifications for a complete set of timing diagrams for each mode.

**Table 2: Controller Compatibility Modes**

| Controller Mode                                                                                        | Setting |      |  |

|--------------------------------------------------------------------------------------------------------|---------|------|--|

| Controller Mode                                                                                        | MD1     | MD0  |  |

| Mode 1<br>For Motorola 68EN360, MPC860,<br>Advanced Micro Devices AM7990, or<br>compatible controllers | Low     | Low  |  |

| Mode 2<br>For Intel 82596 or<br>compatible controllers <sup>1</sup>                                    | Low     | High |  |

| Mode 3<br>For Fujitsu MB86950, MB86960 or<br>compatible controllers (Seeq 8005) <sup>2</sup>           | High    | Low  |  |

| Mode 4 For National Semiconductor 8390 or compatible controllers (TI TMS380C26)                        | High    | High |  |

- Refer to Level One Application Note 51 when designing with Intel controllers.

- SEEQ controllers require inverters on CLKI, LBK, RCLK and COL.

## **Transmit Function**

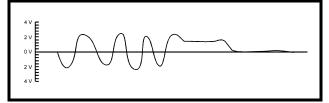

The LXT901/907 receive NRZ data from the controller at the TXD input as shown in the block diagram on the first page of this Data Sheet, and pass it through a Manchester encoder. The encoded data is then transferred to either the AUI cable (the DO circuit) or the twisted-pair network (the TPO circuit). The advanced integrated pulse shaping and filtering network produces the output signal on TPON and TPOP, shown in Figure 2. The TPO output is pre-distorted and prefiltered to meet the 10BASE-T jitter template. An internal continuous resistor-capacitor filter is used to remove any high-frequency clocking noise from the pulse shaping circuitry. Integrated filters simplify the design work required for FCC compliant EMI performance. During idle periods, the LXT901/907 transmit link integrity test pulses on the TPO circuit (if LI is enabled and integrated PLS/ MAU mode is selected). External resistors control the termination impedance for LXT907. External resistors and the STP pin control termination impedance on the LXT901.

Figure 2: LXT901/907 TPO Output Waveform

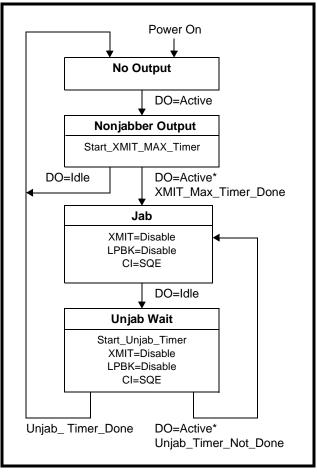

### **Jabber Control Function**

Figure 3 is a state diagram of the LXT901/907 Jabber control function. The on-chip watchdog timer prevents the DTE from locking into a continuous transmit mode. When a transmission exceeds the time limit, the watchdog timer disables the transmit and loopback functions, and activates the JAB pin. Once the LXT901/907 are in the jabber state, the TXD circuit must remain idle for a period of 250 to 750 ms before it exits the jabber state.

Figure 3: Jabber Control Function

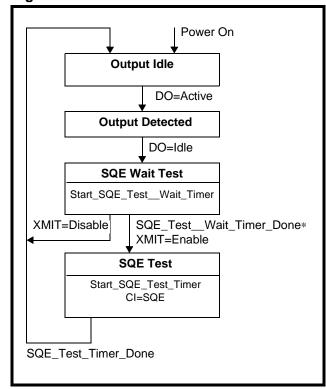

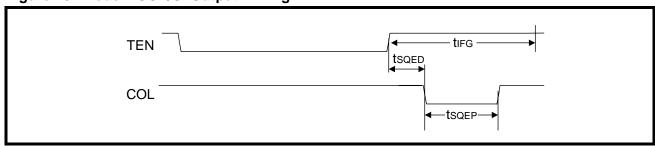

## **SQE Function**

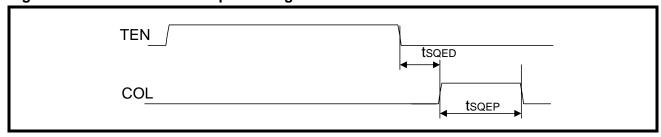

In the integrated PLS/MAU mode, the LXT901/907 support the signal quality error (SQE) function as shown in Figure 4. After every successful transmission on the 10BASE-T network when SQE is enabled, the LXT901/907 transmit the SQE signal for  $10BT \pm 5BT$  over the internal CI circuit which is indicated on the COL pin of the device. When using the 10BASE-2 port of the LXT901/907, the SQE function is determined by the external MAU attached.

## SQE Disable Function (LXT907 only)

SQE must be disabled for normal operation in hub and switch applications. The LXT907 offers an SQE disable function. The SQE function is disabled when DSQE is set High, and enabled when DSQE is Low.

Figure 4: SQE Function

## Receive Function

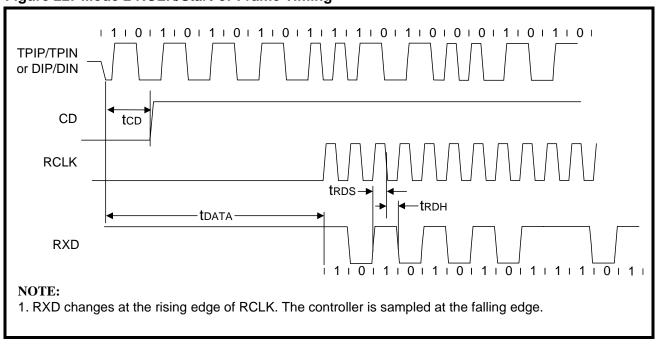

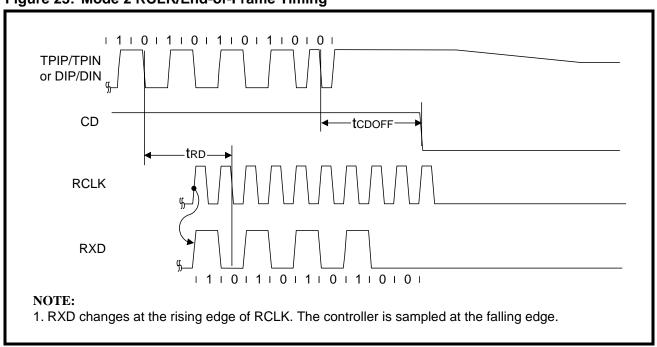

The LXT901/907 receive function acquires timing and data from the twisted-pair network (the TPI circuit) or from the AUI (the DI circuit). Valid received signals are passed through the on-chip filters and Manchester decoder then output as decoded NRZ data and receive timing on the RXD and RCLK pins, respectively.

An internal RC filter and an intelligent squelch function discriminate noise from link test pulses and valid data streams. The receive function is activated only by valid data streams above the squelch level and with proper timing. If the differential signal at the TPI or the DI circuit inputs falls below 75% of the threshold level (unsquelched) for 8 bit times (typical), the LXT901/907 receive function enters the idle state. If the polarity of the TPI circuit is reversed, LXT901/907 detect the polarity reverse and reports it via the PLR output. The LXT901/907 automatically correct reversed polarity.

## **Polarity Reverse Function**

The LXT901/907 polarity reverse function uses both link pulses and end-of-frame data to determine the polarity of the received signal. If Link Integrity Testing is disabled, polarity detection is based only on received data. A reversed polarity condition is detected when eight opposite receive link pulses are detected without receipt of a link pulse of the expected polarity. Reversed polarity is also detected if four frames are received with a reversed start-of-idle. Whenever a correct polarity frame or a correct link pulse is received, these two counters are reset to zero. If the LXT901/907 enter the link fail state and no valid data or link pulses are received within 96 to 128 ms, the polarity is reset to the default non-flipped condition. Polarity correction is always enabled.

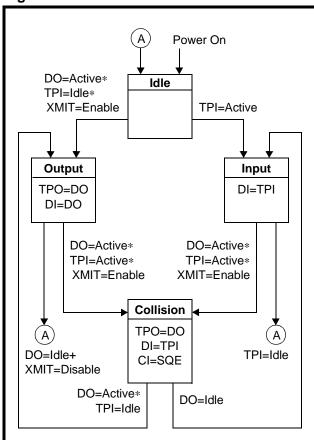

## **Collision Detection Function**

The collision detection function operates on the twisted pair side of the interface. For standard (half-duplex) 10BASE-T operation, a collision is defined as the simultaneous presence of valid signals on both the TPI circuit and the TPO circuit. The LXT901/907 report collisions to the back-end via the COL pin. If the TPI circuit becomes active while there is activity on the TPO circuit, the TPI data is passed to the back-end over the RXD circuit, disabling normal loopback. Figure 5 is a state diagram of the LXT901/907 collision detection function. Refer to Test Specifications for collision detection and COL/CI output timing. (NOTE: For full-duplex operation on TP and AUI ports, the collision detection circuitry must be disabled.)

Figure 5: Collision Detection Function

## Loopback Functions

## **Standard TP Loopback**

The LXT901/907 provide the standard loopback function defined by the 10BASE-T specification for the twisted-pair port. The loopback function operates in conjunction with the transmit function. Data transmitted by the back-end is internally looped back within the LXT901/907 from the TXD pin through the Manchester encoder/decoder to the RXD pin and returned to the back-end. This standard loopback function is disabled when a data collision occurs, clearing the RXD circuit for the TPI data. Standard loopback is also disabled during link fail and jabber states. The LXT901/907 also provide three additional loopback functions.

## **External Loopback**

An external loopback mode, useful for system-level testing, is controlled by the LEDC pin. When LEDC is tied Low, the LXT901/907 disable the collision detection and internal loopback circuits, to allow external loopback. External loopback mode can be set on either TP or AUI ports.

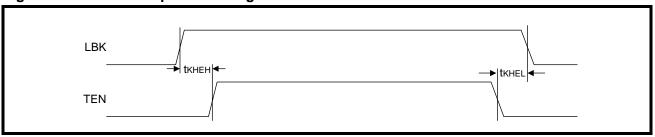

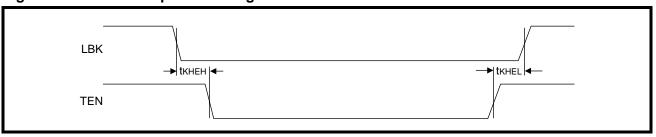

## Forced TP Loopback

"Forced" TP loopback is controlled by the LBK pin. When the TP port is selected and LBK is High, TP loopback is "forced", overriding collisions on the TP circuit. When LBK is Low, normal loopback is in effect.

## **AUI Loopback**

AUI loopback is also controlled by the LBK pin. When the AUI port is selected and LBK is High, data transmitted by the back-end is internally looped back from the TXD pin through the Manchester encoder/decoder to the RXD pin. When LBK is Low, no AUI loopback occurs.

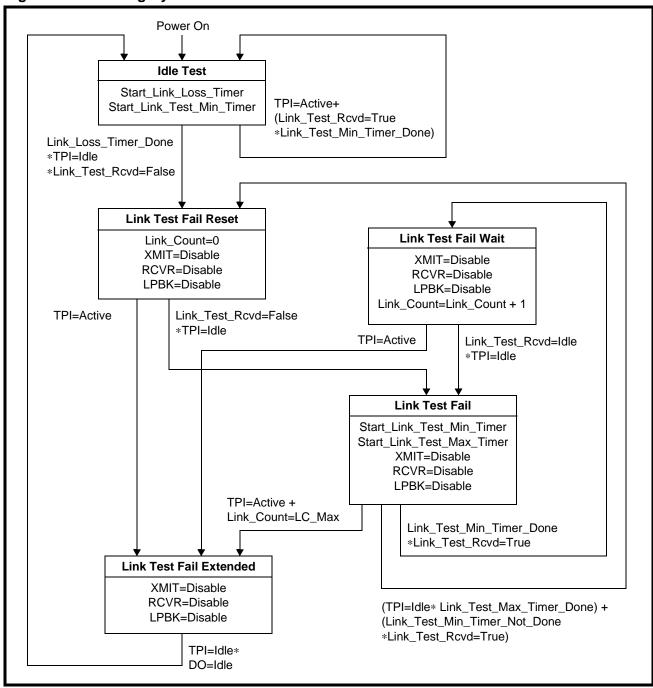

## Link Integrity Test Function

Figure 6 is a state diagram of the LXT901/907 Link Integrity test function. The link integrity test is used to determine the status of the receive side twisted-pair cable. Link integrity testing is enabled when the LI pin is tied High. When enabled, the receiver recognizes link integrity pulses which are transmitted in the absence of receive traffic. If no serial data stream or link integrity pulses are

detected within 50 - 150 ms, the chip enters a link fail state and disables the transmit and normal loopback functions. The LXT901/907 ignore any link integrity pulse with interval less than 2 - 7 ms. The LXT901/907 remain in the link fail state until detecting either a serial data packet or two or more link integrity pulses.

Figure 6: Link Integrity Test Function

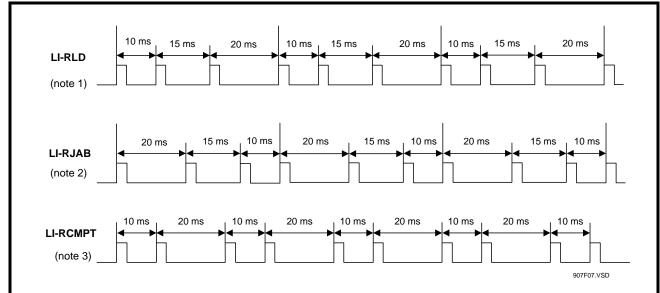

## **Remote Signaling**

The LXT901/907 transmit standard link pulses which meet the 10BASE-T specification. However, the LXT901/907 encode additional status information into the link pulse by varying the link pulse timing. This is referred to as remote signaling. Using alternate pulse intervals, the LXT901/907 can signal three local conditions: link down, jabber and

remote signaling compatibility. Figure 7 shows the interval variations used to signal local status to the other end of the line. The LXT901/907 also recognize these alternate pulse intervals when received from a remote unit. Remote status conditions are reported to the controller over the RLD, RJAB and RCMPT output pins.

Figure 7: Remote Signaling Link Integrity Pulse Timing

#### **NOTES**

- For Remote Link Down (RLD) signaling, the interval between LI pulses increments from 10ms to 15ms, and then the cycle starts over.

- 2. For Remote Jabber (RJAB) signaling, the interval between LI pulses decrements from 20ms to 15ms to 10ms, and then the cycle starts over.

- For Remote Compatibility (RCMPT) signaling, the interval between LI pulses continually switches between 10ms and 20ms.

## **APPLICATION INFORMATION**

# Twisted-Pair Impedance Matching

Resistors must be installed on each input and output pair to match impedance of the network media being used. LXT907 is configured with  $100\Omega$  termination for Unshielded Twisted-Pair (UTP). In this case, the positive and negative sides of both output pairs are shorted together (TPOPA/TPOPB and TPONA/TPONB) and tied to the transformer through a  $24.9\Omega$  1% series resistor.

The LXT901 is designed with an  $\overline{STP}$  Select pin that allows the device to match both  $100\Omega$  and  $150\Omega$  media. A dual resistor combination can be configured to accommodate either line termination as shown in Figure 15. When  $100\Omega$  termination is selected, both A and B pairs are driven in parallel. When  $150\Omega$  termination is selected, the B pair is tri-stated and only the A pair is driven.

## **Crystal Information**

Designers should test and validate crystals to system requirements before committing to a specific component. Crystal specifications for LXT901/907 are shown in Table 3. Based on limited evaluation, Table 4 lists some suitable crystals.

Table 3: Crystal Specifications

| Table 5. Orystal Opcomoations       |     |      |       |       |  |  |

|-------------------------------------|-----|------|-------|-------|--|--|

| Parameter                           | Min | Nom  | Max   | Units |  |  |

| Frequency                           | -   | 20.0 | -     | MHz   |  |  |

| Frequency <sup>1</sup><br>Stability | _   | _    | +/-80 | ppm   |  |  |

| 1. Test condition = -40 - 85°C      |     |      |       |       |  |  |

Table 4: Suitable Crystals

| Manufacturer | Part Number |

|--------------|-------------|

| MTRON        | MP-1        |

|              | MP-2        |

## Magnetics Information

The LXT901 and LXT907 require a 1:1 ratio for the receive transformer and a  $1:\sqrt{2}$  ratio for the transmit transformer on the twisted-pair interface. The AUI Interface requires a 1:1 ratio for both the transmit and receive transformers. Designers should test and validate magnetics for system requirements before committing to a specific component. Table 5 lists some suitable magnetics.

**Table 5: Suitable Magnetics**

|              | Manufacturer | Part Number |

|--------------|--------------|-------------|

| Twisted-Pair | Fil-Mag      | 23Z128      |

|              |              | 23Z128SM    |

|              | Valor        | PT4069      |

|              |              | ST7011      |

|              | Belfuse      | A553-0716   |

|              |              | S553-0716   |

|              | HALO         | TD42-2006Q  |

|              |              | TG42-1406N1 |

| AUI          | Fil-Mag      | 23Z90       |

|              |              | 23Z90SM     |

|              | Valor        | LT6032      |

|              |              | ST7032      |

|              | HALO         | TD01-0756K  |

|              |              | TG01-0756N  |

## **Typical Applications**

Figures 8 through 15 show typical LXT901/907 applications.

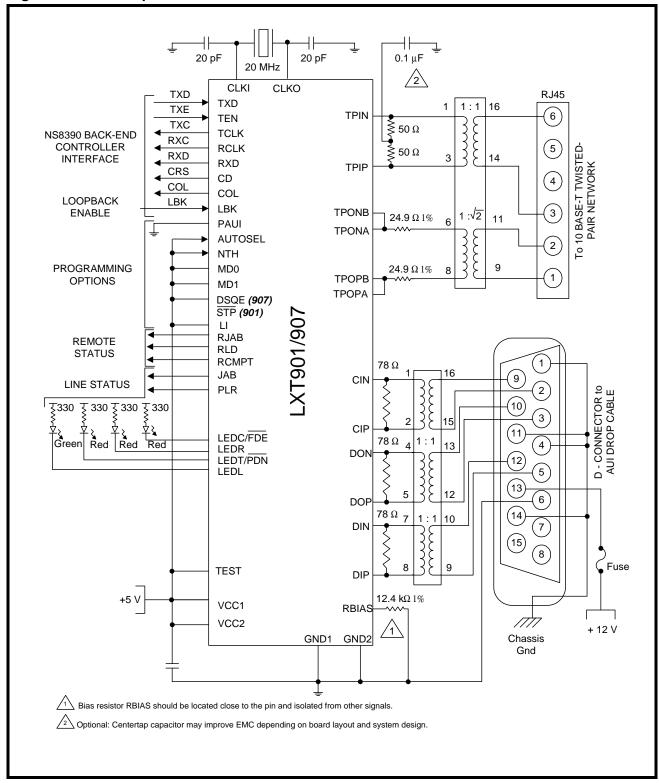

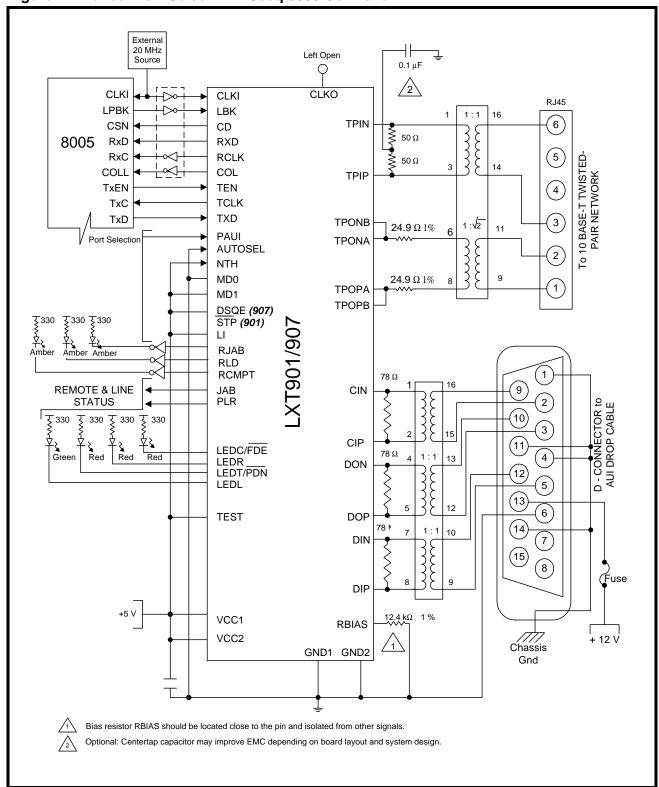

## Auto Port Select with External Loopback Control

Figure 8 is a typical LXT901/907 application. The diagram is arranged to group similar pins together; it does not represent the actual LXT901/907 pinout. The controller interface pins (transmit data, clock and enable; receive data and clock; and the collision detect, carrier detect and loopback control pins) are shown at the top left.

Programmable option pins are grouped center left. The PAUI pin is tied Low and all other option pins are tied High. This set-up selects the following options:

- Automatic Port Selection (PAUI Low and AUTOSEL High)

- Normal Receive Threshold (NTH High)

- Mode 4, compatible with National NS8390 controllers (MD0 High, MD1 High)

- SQE Disabled (DSQE High on LXT907 only)

- $100\Omega$  termination UTP cable (STP High on LXT901 only)

- Link Testing Enabled (LI High)

Status outputs are grouped at lower left. Local status outputs drive LED indicators and remote status indicators are available as required.

Power and ground pins are shown at the bottom of the diagram. A single power supply is used for both VCC1 and VCC2 with a decoupling capacitor installed between the power and ground busses.

The TP and AUI interfaces are shown at upper and lower right, respectively. Impedance matching resistors for  $100\Omega$  UTP are installed in each I/O pair but no external filters are required.

Figure 8: LAN Adapter Board - Auto Port Select with External LPBK Control

## **Full Duplex Support**

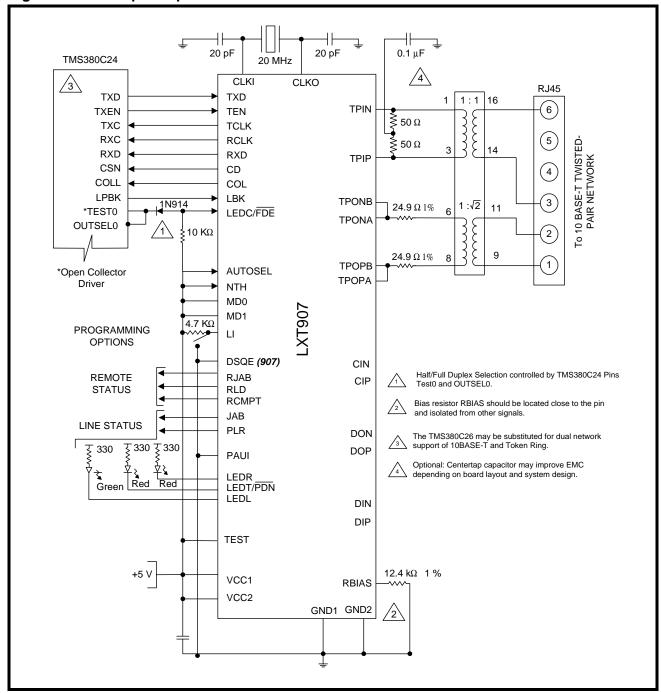

Figure 9 shows the LXT907 with a Texas Instruments 380C24 CommProcessor. The 380C24 is compatible with Mode 4 (MD0 and MD1 both High). When used with the 380C24 or other full duplex-capable controller, the

LXT907 supports full-duplex Ethernet, effectively doubling the available bandwidth of the network. In this application the SQE function is enabled (DSQE tied Low), and the AUI port is not used.

Figure 9: Full-Duplex Operation

# **Dual Network Support - 10Base-T** and Token Ring

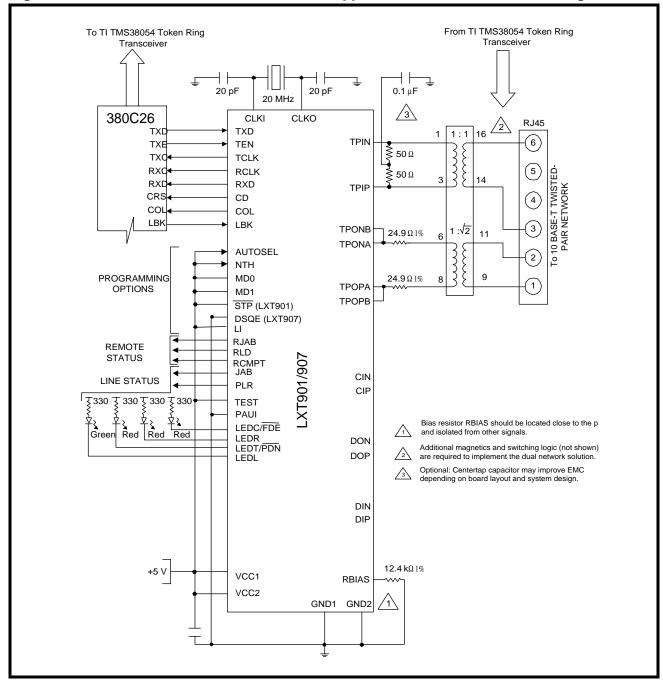

Figure 10 shows the LXT901/907 with a Texas Instruments 380C26 CommProcessor. The 380C26 is compatible with Mode 4 (MD0 and MD1 both High). When used with the 380C26, both the LXT901/907 and a

TMS38054 Token Ring transceiver can be tied to a single RJ45 allowing dual network support from a single connector. The LXT901/907 AUI port is not used. The LXT901 STP is High and the LXT907 DSQE is Low.

Figure 10: 380C26 Interface for Dual Network Support of 10BASE-T and Token Ring

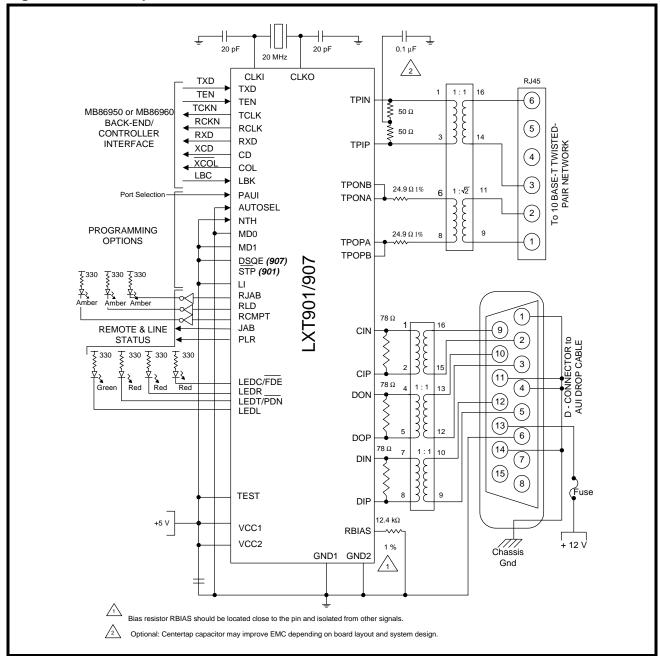

## Manual Port Select with Link Test Function

With MD0 Low and MD1 tied High, the LXT901/907 logic and framing are set to Mode 3 (compatible with Fujitsu MB86950 and MB86960, and Seeq 8005 controllers). Figure 11 shows the setup for Fujitsu controllers. Figure 11 on page 18 shows the four inverters required to interface with the Seeq 8005 controller. As in Figure 8 on page 15, both these Mode 3 applications show the LI pin

tied High, enabling Link Testing; and the  $\overline{STP}$  (LXT901 only) and NTH pins are both tied High, selecting the standard receiver threshold and 100  $\Omega$  termination for unshielded TP cable. However, in these applications AUTOSEL is tied Low, allowing external port selection through the PAUI pin. The remote status outputs are inverted to drive LED indicators.

Figure 11: LAN Adapter Board - Manual Port Select with Link Test Function

Figure 12: Manual Port Select with Seeq 8005 Controller

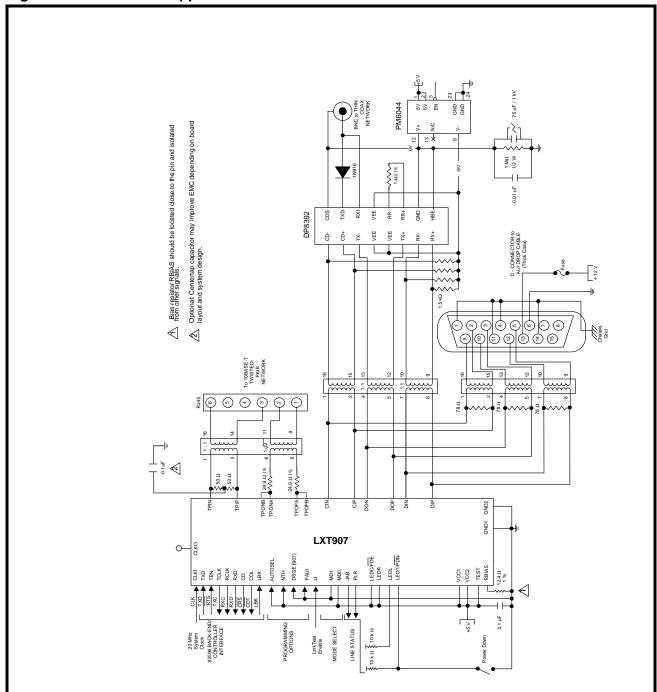

## **Three Media Application**

Figure 13 shows the LXT907 in Mode 2 (compatible with Intel 82596 controllers) with additional media options for the AUI port. Two transformers are used to couple the AUI

port to either a D-connector or a BNC connector. (A DP8392 coax transceiver with PM6044 power supply are required to drive the thin coax network through the BNC.)

Figure 13: Three Media Application

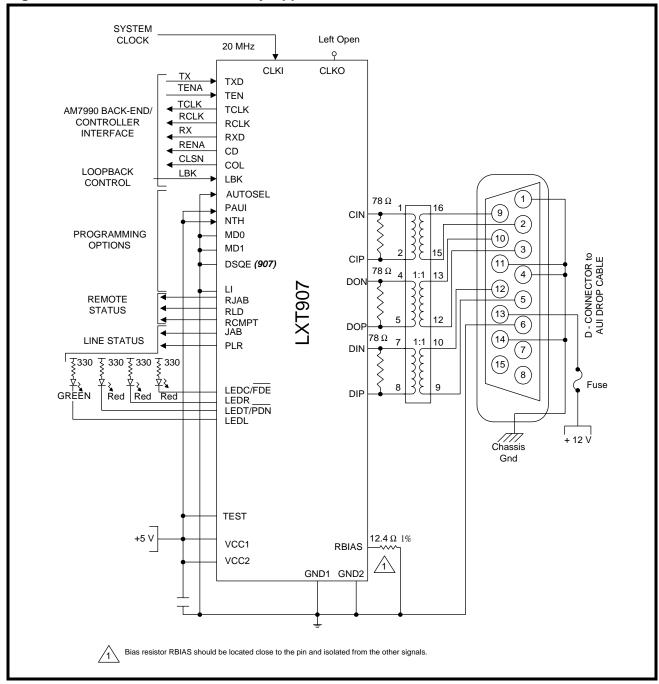

## **AUI Encoder/Decoder ONLY**

In Figure 14, the DTE is connected to a coaxial network through the AUI. AUTOSEL is tied Low and PAUI is tied High, manually selecting the AUI port. The twisted-pair port is not used. With MD1 and MD0 both Low, the logic and framing are set to Mode 1 (compatible with AMD

AM7990 controllers). The LI pin is tied Low, disabling the link test function. The DSQE pin is also Low, enabling the SQE function on the LXT907. The LBK input controls loopback. A 20 MHz system clock is supplied at CLK1 with CLK0 left open.

Figure 14: AUI Encoder/Decoder Only Application

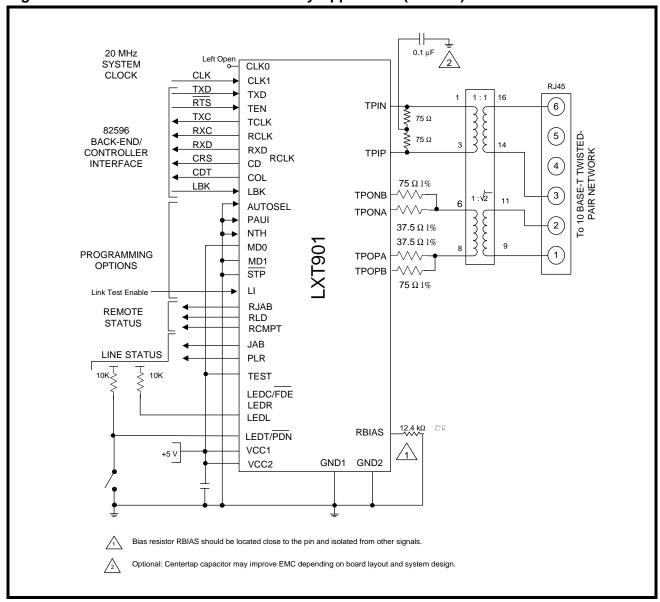

# 150 $\Omega$ SHIELDED TWISTED-PAIR ONLY (LXT901 only)

Figure 15 shows the LXT901 in a typical twisted-pair only application. The DTE is connected to a 10BASE-T network through the twisted-pair RJ45 connector. (The AUI port is not used). With MD0 tied High and MD1 Low, the LXT901 logic and framing are set to Mode 2 (compatible with Intel 82596 controllers).

A 20 MHz system clock input at CLK1 is used in place of the crystal oscillator. (CLK0 is left open). The L1 pin externally controls the link test function. The UTP/STP and NTH pins are both tied Low, selecting the reduced receiver threshold and 150  $\Omega$  termination for shielded TP cable. The switch at LEDT/PDN manually controls the power down mode.

Figure 15: 150  $\Omega$  Shielded Twisted-Pair Only Application (LXT901)

## **TEST SPECIFICATIONS**

### **NOTE**

Tables 6 through 15 and Figures 16 through 41 represent the performance specifications of the LXT901/907. These specifications are guaranteed by test except where noted "by design." Minimum and maximum values listed in Tables 8 through 15 apply over the recommended operating conditions specified in Table 7.

Table 6: Absolute Maximum Ratings

| Parameter                     | Symbol | Min  | Max  | Units |

|-------------------------------|--------|------|------|-------|

| Supply voltage                | Vcc    | -0.3 | 6    | V     |

| Ambient operating temperature | TA     | 0    | 70   | °C    |

| Storage temperature           | Tstg   | -65  | +150 | °C    |

### **CAUTION**

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

Exposure to maximum rating conditions for extended periods may affect device reliability.

**Table 7: Recommended Operating Conditions**

| Parameter                               | Symbol | Min  | Тур | Max  | Units |

|-----------------------------------------|--------|------|-----|------|-------|

| Recommended supply voltage <sup>1</sup> | Vcc    | 4.75 | 5.0 | 5.25 | V     |

| Recommended operating temperature       | Тор    | 0    | _   | 70   | °C    |

<sup>1.</sup> Voltages with respect to ground unless otherwise specified. Power supply should be filtered to suppress high frequency transients, consistent with good PCB design.

Table 8: I/O Electrical Characteristics

| Parameter                                     | Sym  | Min | Typ <sup>1</sup> | Max | Units | Test Conditions |

|-----------------------------------------------|------|-----|------------------|-----|-------|-----------------|

| Input low voltage <sup>2</sup>                | VIL  | _   | -                | 0.8 | V     |                 |

| Input high voltage <sup>2</sup>               | Vih  | 2.0 | -                | -   | V     |                 |

| Output low voltage                            | Vol  | _   | -                | 0.4 | V     | IOL = 1.6 mA    |

|                                               | Vol  | _   | -                | 10  | %Vcc  | IOL < 10 μA     |

| Output low voltage<br>(Open drain LED driver) | Voll | _   | _                | 0.7 | %Vcc  | IOLL = 10 mA    |

| Output high voltage                           | Voн  | 2.4 | -                | _   | V     | IοH = 40 μA     |

|                                               | Voн  | 90  | -                | _   | %Vcc  | IOH < 10 μA     |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

<sup>2.</sup> Limited functional tests are performed at these input levels. The majority of functional tests are performed at levels of 0V and 3V.

Table 8: I/O Electrical Characteristics – continued

| Para                | Parameter         |     | Min | Typ <sup>1</sup> | Max   | Units | Test Conditions     |

|---------------------|-------------------|-----|-----|------------------|-------|-------|---------------------|

| Output rise time    | CMOS              | _   | _   | 3                | 12    | ns    | CLOAD = 20 pF       |

| TCLK & RCLK         | TTL               | _   |     | 2                | 8     | ns    |                     |

| Output fall time    | CMOS              | _   | _   | 3                | 12    | ns    | CLOAD= 20 pF        |

| TCLK & RCLK         | TTL               | -   | -   | 2                | 8     | ns    |                     |

| CLKI rise time (ext | ternally driven)  | -   | -   | -                | 10    | ns    |                     |

| CLKI duty cycle (e  | xternally driven) | _   | _   | 50/50            | 40/60 | %     |                     |

| Supply current      |                   | Icc | _   | 65               | 85    | mA    | Idle Mode           |

|                     | Normal Mode       | Icc | -   | 90               | 110   | mA    | Transmitting on TP  |

|                     |                   | Icc | _   | 70               | 90    | mA    | Transmitting on AUI |

|                     | Power Down Mode   | Icc | _   | 0.75             | 2     | mA    |                     |

<sup>1.</sup> Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

Table 9: AUI Electrical Characteristics

| Parameter                      | Symbol | Min  | Typ <sup>1</sup> | Max   | Units | Test Conditions         |

|--------------------------------|--------|------|------------------|-------|-------|-------------------------|

| Input Low current              | IIL    | _    | _                | -700  | μA    |                         |

| Input High current             | Іін    | _    | _                | 500   | μΑ    |                         |

| Differential output voltage    | Vod    | ±550 | _                | ±1200 | mV    |                         |

| Differential squelch threshold | Vds    | 150  | 250              | 350   | mV    | 5 MHz square wave input |

<sup>1.</sup> Typical values are at 25  $^{\circ}$ C and are for design aid only; not guaranteed and not subject to production testing.

**Table 10: TP Electrical Characteristics**

| Parameter                                                | Symbol | Min | Typ <sup>1</sup> | Max  | Units | Test Conditions                                                          |

|----------------------------------------------------------|--------|-----|------------------|------|-------|--------------------------------------------------------------------------|

| Transmit output impedance                                | Zout   | -   | 5                | -    | Ω     |                                                                          |

| Transmit timing jitter addition                          | -      | -   | ±3.3             | ±10  | ns    | 0 line length for internal MAU                                           |

| Transmit timing jitter added by the MAU and PLS sections | -      | -   | ±3.3             | ±5.5 | ns    | After line model specified<br>by IEEE 802.3 for<br>10BASE-T internal MAU |

<sup>1.</sup> Typical values are at 25  $^{\circ}$ C and are for design aid only; not guaranteed and not subject to production testing.

<sup>2.</sup> Limited functional tests are performed at these input levels. The majority of functional tests are performed at levels of 0V and 3V.

Table 10: TP Electrical Characteristics - continued

| Parameter                         |                                    | Symbol             | Min        | Typ <sup>1</sup> | Max          | Units         | Test Conditions                         |

|-----------------------------------|------------------------------------|--------------------|------------|------------------|--------------|---------------|-----------------------------------------|

| Receive input impedance           |                                    | ZIN                | _          | 20               | _            | kΩ            | Between TPIP/TPIN,<br>CIP/CIN & DIP/DIN |

| Differential Squelch<br>Threshold | Normal<br>Threshold;<br>NTH = High | VDS                | 300        | 400              | 585          | mV            | 5 MHz square wave input                 |

|                                   | Reduced<br>Threshold;<br>NTH = Low | Vds                | 180        | 250              | 345          | mV            | 5 MHz square wave input                 |

| Typical values are at 2           | 25 °C and are for dea              | sign aid only; not | guaranteed | l and not su     | bject to pro | duction testi | ng.                                     |

**Table 11: Switching Characteristics**

|                     | Parameter                                | Symbol            | Minimum            | Typical <sup>1</sup> | Maximum | Units |

|---------------------|------------------------------------------|-------------------|--------------------|----------------------|---------|-------|

| Jabber Timing       | Maximum transmit time                    | _                 | 20                 | -                    | 150     | ms    |

|                     | Unjab time                               | _                 | 250                | _                    | 750     | ms    |

| Link Integrity      | Time link loss receive                   | _                 | 50                 | _                    | 150     | ms    |

| Timing              | Link min receive                         |                   | 2                  | _                    | 7       | ms    |

| i                   | Link max receive                         | _                 | 50                 | _                    | 150     | ms    |

|                     | Link transmit period                     | _                 | 8                  | 10                   | 24      | ms    |

| 1. Typical values a | are at 25 °C and are for design aid only | y; not guaranteed | and not subject to | production testing   |         |       |

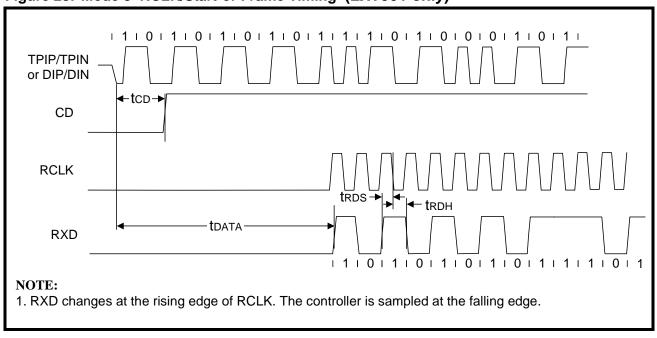

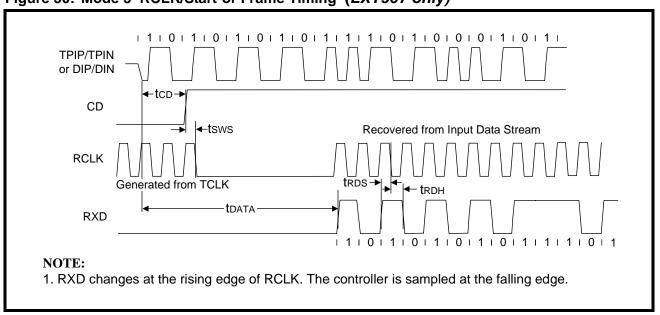

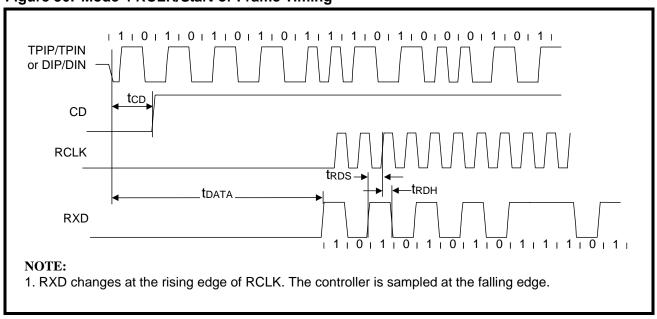

Table 12: RCLK/Start-of-Frame Timing

| Parameter                |                  | Symbol | Minimum | Typical <sup>1</sup> | Maximum | Units |

|--------------------------|------------------|--------|---------|----------------------|---------|-------|

| Decoder acquisition time | AUI              | tDATA  | _       | 900                  | 1100    | ns    |

|                          | TP               | tDATA  | _       | 1200                 | 1500    | ns    |

| CD turn-on delay         | AUI              | tCD    | _       | 25                   | 200     | ns    |

|                          | TP               | tCD    | _       | 425                  | 550     | ns    |

| Receive data setup from  | Mode 1           | trds   | 60      | 70                   | -       | ns    |

| RCLK                     | Modes 2, 3 and 4 | trds   | 30      | 45                   | _       | ns    |

Table 12: RCLK/Start-of-Frame Timing

| Parameter                                                   |                  | Symbol | Minimum | Typical <sup>1</sup> | Maximum | Units |

|-------------------------------------------------------------|------------------|--------|---------|----------------------|---------|-------|

| Receive data hold from                                      | Mode 1           | trdh   | 10      | 20                   | _       | ns    |

| RCLK                                                        | Modes 2, 3 and 4 | trdh   | 30      | 45                   | _       | ns    |

| RCLK shut off delay from CD assert<br>(LXT907 only; Mode 3) |                  | tsws   | -       | ±90                  | -       | ns    |

<sup>1.</sup> Typical values are at 25° C and are for design aid only; not guaranteed and not subject to production testing.

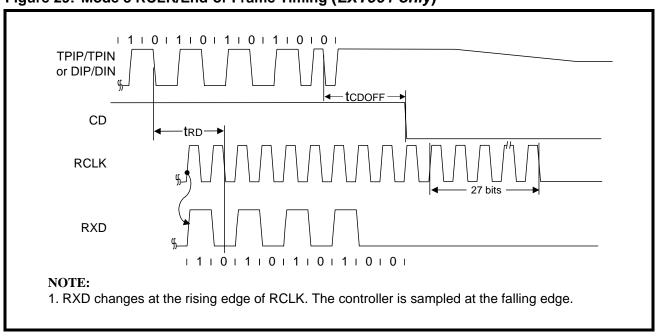

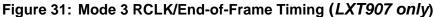

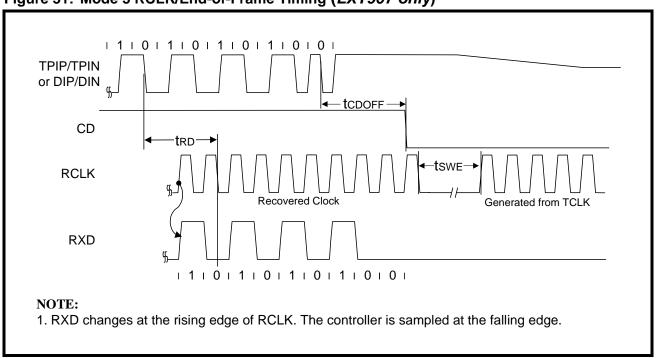

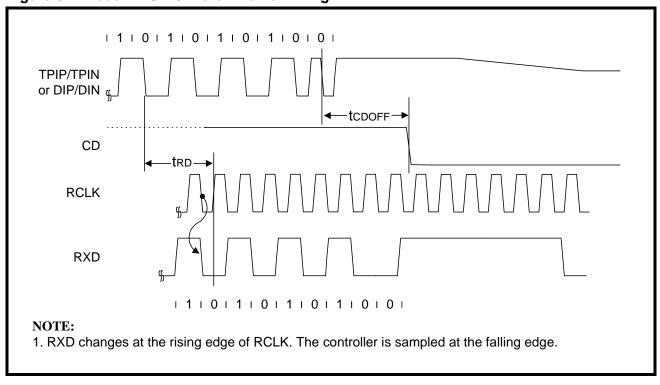

Table 13: RCLK/End-of-Frame Timing

| Parameter                                               | Туре             | Sym    | Mode 1 | Mode 2 | Mode 3   | Mode 4 | Units |

|---------------------------------------------------------|------------------|--------|--------|--------|----------|--------|-------|

| RCLK after CD off                                       | Min              | trc    | 5      | 1      | 27       | 5      | bt    |

| Rcv data throughput delay                               | Max              | trd    | 400    | 375    | 375      | 375    | ns    |

| CD turn off delay <sup>2</sup>                          | Max              | tCDOFF | 500    | 475    | 475      | 475    | ns    |

| Receive block out after TEN off                         | Typ <sup>1</sup> | tIFG   | 5      | 50     | _        | _      | bt    |

| RCLK switching delay after CD off (LXT907 only; Mode 3) | Typ <sup>1</sup> | tswe   | _      | _      | 120(±80) | -      | ns    |

<sup>1.</sup> Typical values are at 25° C and are for design aid only; not guaranteed and not subject to production testing.

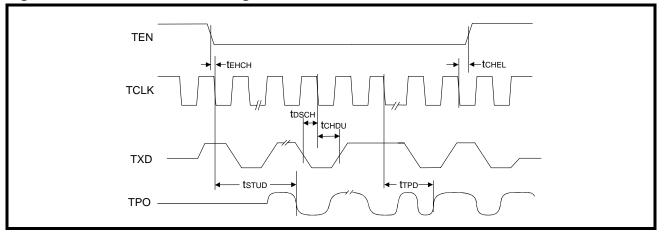

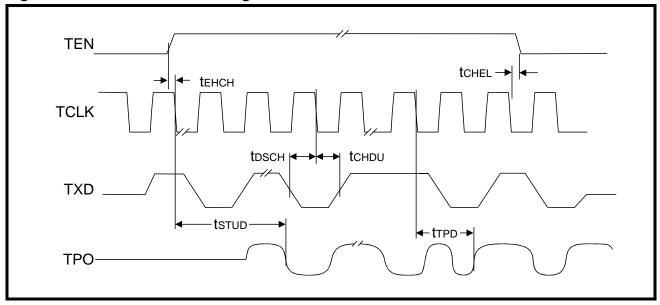

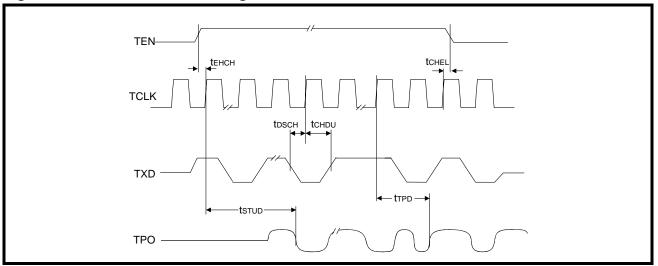

**Table 14: Transmit Timing**

| Parameter                        | Symbol | Minimum | Typical <sup>1</sup> | Maximum | Units |

|----------------------------------|--------|---------|----------------------|---------|-------|

| TEN setup from TCLK              | tehch  | 22      | _                    | 1       | ns    |

| TXD setup from TCLK              | tDSCH  | 22      | _                    | -       | ns    |

| TEN hold after TCLK              | tCHEL  | 5       | _                    | _       | ns    |

| TXD hold after TCLK              | tCHDU  | 5       | _                    | _       | ns    |

| Transmit start-up delay - AUI    | tstud  | _       | 220                  | 450     | ns    |

| Transmit start-up delay - TP     | tstud  | _       | 430                  | 450     | ns    |

| Transmit through-put delay - AUI | tTPD   | _       | _                    | 300     | ns    |

| Transmit through-put delay - TP  | tTPD   | _       | 300                  | 350     | ns    |

<sup>1.</sup> Typical values are at  $25^{\circ}$  C and are for design aid only; not guaranteed and not subject to production testing.

<sup>2.</sup> CD turn-off delay measured from middle of last bit: timing specification is unaffected by the value of the last bit.

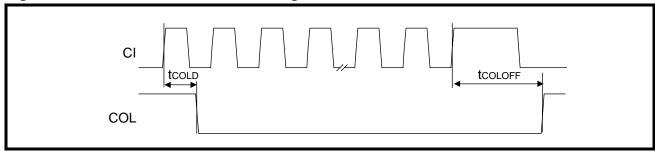

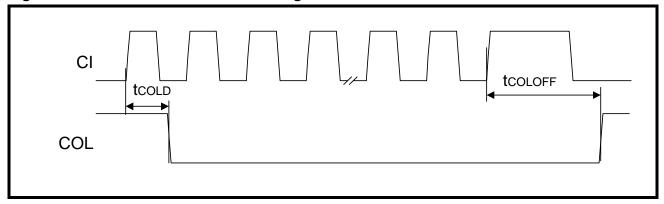

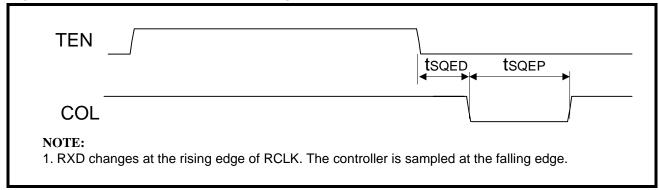

Table 15: Collision, COL/CI Output and Loopback Timing

| Parameter                     | Symbol  | Minimum | Typical <sup>1</sup> | Maximum | Units |

|-------------------------------|---------|---------|----------------------|---------|-------|

| COL turn-on delay             | tCOLD   | _       | 40                   | 500     | ns    |

| COL turn-off delay            | tCOLOFF | _       | 420                  | 500     | ns    |

| COL (SQE) Delay after TEN off | tSQED   | 0.65    | 1.2                  | 1.6     | μs    |

| COL (SQE) Pulse Duration      | tSQEP   | 500     | 1000                 | 1500    | ns    |

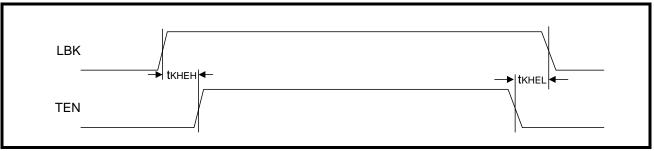

| LBK setup from TEN            | tkheh   | 10      | 25                   | _       | ns    |

| LBK hold after TEN            | tkhel   | 10      | 0                    | _       | ns    |

<sup>1.</sup> Typical values are at  $25^{\circ}$  C and are for design aid only; not guaranteed and not subject to production testing.

## Timing Diagrams for Mode 1 (MD1 = Low, MD0 = Low) Figures 16 through 21

Figure 16: Mode 1 RCLK/Start-of-Frame Timing

Figure 17: Mode 1 RCLK/End-of-Frame Timing

Figure 18: Mode 1 Transmit Timing

Figure 19: Mode 1 Collision Detect Timing

Figure 20: Mode 1 COL/CI Output Timing

Figure 21: Mode 1 Loopback Timing

## Timing Diagrams for Mode 2 (MD1=Low, MD0=High) Figures 22 through 27

Figure 22: Mode 2 RCLK/Start-of-Frame Timing

Figure 23: Mode 2 RCLK/End-of-Frame Timing

Figure 24: Mode 2 Transmit Timing

Figure 25: Mode 2 Collision Detect Timing

Figure 26: Mode 2 COL/CI Output Timing

Figure 27: Mode 2 Loopback Timing

## Timing Diagrams for Mode 3 (MD1 = High, MD0 = Low) Figures 28 through 35

Figure 28: Mode 3 RCLK/Start-of-Frame Timing (LXT901 only)

Figure 29: Mode 3 RCLK/End-of-Frame Timing (LXT901 only)

Figure 30: Mode 3 RCLK/Start-of-Frame Timing (LXT907 only)

Figure 32: Mode 3 Transmit Timing

Figure 33: Mode 3 Collision Detect Timing

Figure 34: Mode 3 COL/CI Output Timing

Figure 35: Mode 3 Loopback Timing

## Timing Diagrams for Mode 4 (MD1 = High, MD0 = High) Figures 36 through 41

Figure 36: Mode 4 RCLK/Start-of-Frame Timing

Figure 37: Mode 4 RCLK/End-of-Frame Timing

Figure 38: Mode 4 Transmit Timing

Figure 39: Mode 4 Collision Detect Timing

Figure 40: Mode 4 COL/CI Output Timing

Figure 41: Mode 4 Loopback Timing

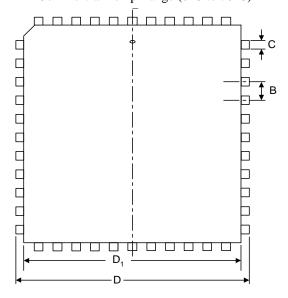

## **MECHANICAL SPECIFICATIONS**

## Figure 42: LXT901/907 Package Specifications

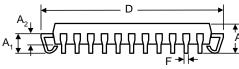

### 44-Pin PLCC

- Part Number LXT901PC and LXT907PC

- Commercial Temp Range (0°C to 70°C)

|     | Inc   | hes   | Millimeters |        |  |

|-----|-------|-------|-------------|--------|--|

| Dim | Min   | Max   | Min         | Max    |  |

| A   | 0.165 | 0.180 | 4.191       | 4.572  |  |

| A1  | 0.090 | 0.120 | 2.286       | 3.048  |  |

| A2  | 0.062 | 0.083 | 1.575       | 2.108  |  |

| В   | 0.050 | -     | 1.270       | _      |  |

| С   | 0.026 | 0.032 | 0.660       | 0.813  |  |

| D   | 0.685 | 0.695 | 17.399      | 17.653 |  |

| D1  | 0.650 | 0.656 | 16.510      | 16.662 |  |

| F   | 0.013 | 0.021 | 0.330       | 0.533  |  |

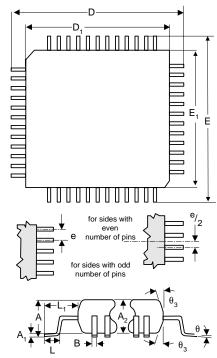

### 64-Pin LQFP

- Part Number LXT901LC

- Commercial Temp Range (0°C to 70°C)

|            | Inc     | hes       | Millim    | neters |  |

|------------|---------|-----------|-----------|--------|--|

| Dim        | Min Max |           | Min       | Max    |  |

| A          | -       | 0.063     | _         | 1.60   |  |

| A1         | 0.002   | 0.006     | 0.05      | 0.15   |  |

| A2         | 0.053   | 0.057     | 1.35      | 1.45   |  |

| В          | 0.007   | .011      | 0.17      | 0.27   |  |

| D          | 0.472   | 2 BSC     | 12.00     | BSC    |  |

| D1         | 0.394   | 4 BSC     | 10.00 BSC |        |  |

| Е          | 0.472   | 2 BSC     | 12.00 BSC |        |  |

| E1         | 0.394   | 4 BSC     | 10.00     | BSC    |  |

| e          | 0.020   | ) BSC     | 0.50      | BSC    |  |

| L          | 0.018   | 0.030     | 0.45      | 0.75   |  |

| L1         | 0.039   | 0.039 REF |           | REF    |  |

| $\theta_3$ | 11°     | 13°       | 11°       | 13°    |  |

| θ          | 0°      | 7°        | 0°        | 7°     |  |

## **REVISION HISTORY**

Table 16: Changes from Reivision 3.2 to Revision 3.3 (10/00)

| Section                           | Page # | Change | Text                                                        |

|-----------------------------------|--------|--------|-------------------------------------------------------------|

| Table 3 Crystal<br>Specifications | 13     | Modify | Change frequency value under Nom from "25" MHz to "20" MHz. |

Table 17: Changes from Reivision 3.1 to Revision 3.2 (06/00)

| Section                                      | Page # | Change | Text                                                                                     |

|----------------------------------------------|--------|--------|------------------------------------------------------------------------------------------|

| Figure 1<br>LXT901/907 Pin<br>Assignments    | 3      | Modify | Remove "A" from 901 and 907.<br>Correct drawing to line up pin numbers with signals.     |

| Table 1<br>LXT901/907 Signal<br>Descriptions | 4      | Modify | Add text to LEDT/PDN description: "Do not allow this pin to float. If unused, tie High." |

Table 18: Changes From Revision 3.0 to Revision 3.1 (03/99)

| Table 10. Changes I form Revision 5.5 to Revision 5.1 (65/55) |        |        |                                                                                                               |  |  |

|---------------------------------------------------------------|--------|--------|---------------------------------------------------------------------------------------------------------------|--|--|

| Section                                                       | Page # | Change | Text                                                                                                          |  |  |

| Front Page                                                    | 1      | Update | Change package options for the LXT907 to 44-Pin PLCC only. LXT901 is available in 64-Pin LQFP and 44-Pin PLCC |  |  |

| Figure 1                                                      | 3      | Update | Delete LXT907 from LC (LQFP) package.                                                                         |  |  |

| Pin Assignments                                               |        |        |                                                                                                               |  |  |

| Figure 42                                                     | 38     | Update | Delete LXT907 from 64-Pin LQFP package.                                                                       |  |  |

| Mechanical                                                    |        |        |                                                                                                               |  |  |

| Specifications                                                |        |        |                                                                                                               |  |  |

| All                                                           | All    | Update | Update format.                                                                                                |  |  |

## **Corporate Headquarters**

9750 Goethe Road

Sacramento, California 95827 Telephone: (916) 855-5000 Web: www.level1.com

### The Americas

### Eastern Area **Headquarters**

234 Littleton Road, Unit 1A Westford, MA 01886 **USA**

**EAST**

Tel: (978) 692-1193 Fax: (978) 692-1244

**North Central**

**Regional Office**

One Pierce Place

Itasca, IL 60143

Suite 500E

**USA**

## Western Area **Headquarters**

**WEST**

3375 Scott Blvd., #110 Santa Clara, CA 95054 USA

Tel: (408) 496-1950

Fax: (408) 496-1955

## ASIA/PACIFIC

### Asia / Pacific Area **Headquarters**

101 Thomson Road United Square #08-01 Singapore 307591 Thailand

Tel: +65 353 6722 Fax: +65 353 6711

## Central Asia/Pacific **Regional Office**

12F-1, No. 128, Section 3, Ming Sheng East Road Taipei, Taiwan,

R.O.C.

Tel: +886 2 2547 5227 Fax: +886 2 2547 5228

## **Regional Office** 800 E. Campbell Road

**South Central**

Suite 199 Richardson, TX 75081 **USA**

Tel: (972) 680-5207 Fax: (972) 680-5236

### Southwestern **Regional Office**

28202 Cabot Road Suite 300 Laguna Niguel, CA 92677

**USA**

Tel: (949) 365-5655 Fax: (949) 365-5653

### Northern Asia/Pacific Regional Office

Shinjuku Tsuji Building, 2F 2-10-4, Yoyogi, Shibuya-Ku Tokyo, 151-0053 Japan Tel: 81-3-5333-1780

Fax: 81-3-5333-1785

### **EUROPE**

## European Area HQ & Southern Regional Office

Parc Technopolis-Bat. Zeta 3, avenue du Canada -Z.A. de Courtaboeuf Les Ulis Cedex 91974

France

International

Tel: +33 1 64 86 2828 Fax: +33 1 60 92 0608

### Central Europe Regional Office

Lilienthalstr.25 D-85399

Hallbergmoos, Germany Tel: +49-811-60068-0 Fax: +49-811-60068-15

### **Northern Europe** Regional Office

Isafjordsgatan 11 164/40 Kista/Stockholm,

Sweden

Tel: +46 8 594 617 30 Fax: +46 8 594 617 01

### Israel **Regional Office**

Regus Instant Off.-Harel House 3 Abba Hillel Silver Street Ramat Gan, 52522 Israel Tel: +972-3-754-1130

Fax: +972-3-754-1100

## Southeastern **Regional Office**

Tel: (630) 250-6044

Fax: (630) 250-6045

One Copley Parkway Suite 309

Morrisville, NC 27560

USA

Tel: (919) 463-0488 Fax: (919) 463-0486

### Latin/South America

9750 Goethe Road Sacramento, CA 95827

USA

Tel: (916) 855-5000 Fax: (916) 854-1102

Correct Nom value in Table 3.

#### Revision Date **Status** 3.3 11/00

Correct 44-pin PLCC pin assignment diagram; add text to Table 1 for LEDT/PDN. 3.2 06/99

Information in this document is provided in connection with Level One products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Level One's Terms and Conditions of Sale for such products, Level One assumes no liability whatsoever, and Level One disclaims any express or implied warranty, relating to sale and/or use of Level One products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Level One products are not interned for use in medical, life saving, or life sustaining applications.

Level One may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Level One reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Third party brands and names are the property of their respective owners.

The products listed in this publication are covered by one or more of the following patents. Additional patents pending.

5,008,637; 5,028,888; 5,057,794; 5,059,924; 5,068,628; 5,077,529; 5,084,866; 5,148,427; 5,153,875; 5,157,690; 5,159,291; 5,162,746; 5,166,635; 5,181,228; 5,204,880; 5,249,183; 5,257,286; 5,267,269; 5,461,661; 5,493,243; 5,534,863; 5,574,726; 5,581,585; 5,608,341; 5,666,129; 5,671,249; 5,701,099; 5,717,714; 5,742,603; 5,748,634; 5,764,638; 5,777,996; 5,802,052; 5,880,645; 5,881,074; 5,907,553; 5,926,049; 5,926,504; 5,946,398

Copyright © 2000 Level One Communications, Inc., an Intel Company. Specifications subject to change without notice. All rights reserved.