#### 512K x 8 Bit ROM and 32K x 8 Bit SRAM Low Voltage Combo Memory

#### **FEATURES**

- Both ROM and RAM in one chip

- Wide Operating Voltage Range: 1.8 3.3V

- Fast Access Time

1.8 V Operation: 500 ns (Max.) 3.0 V Operation: 150 ns (Max.)

• Low Power Dissipation:

Standby

1.8 V Operation: 0.1μW (Typ.)3.0 V Operation: 1.0μW (Typ.)

Operating

1.8 V Operation: 1.6 mW (Typ.) 3.0 V Operation: 20 mW (Typ.)

• Fully Static Operation

No clock or refresh required

- Three state Outputs

- Standard 32 Pin TSOP type 1 package

- Industrial Temperature -40 to 85 °C

#### **GENERAL DESCRIPTION**

The LX50CM432 is a combination memory chip consist of 4M-bit Read Only Memory organized as 512K words by 8 bits and a 256K-bit Static Random Access Memory organized as 32Kwords by 8 bits. Output Enable Input ( $\overline{OE}$ ) is pin-shared with  $\overline{CS}2$  (RAM Enable Input) signal in order to maintain the standard 32 pin TSOP package. The device is fabricated using Linvex's advanced CMOS low power process technology. The LX50CM432 has an output enable input for

The LX50CM432 has an output enable input for precise control of the data outputs. It also has two (2) sepreate chip enable inputs for selection of either RAM or ROM and minimize current drain during power-down mode.

The LX50CM432 is particularly well suited for use in low voltage (1.8 - 3.3 V) operation and with large ROM requirement such as pager and other handheld applications.

#### PIN CONFIGURATION (TOP VIEW)

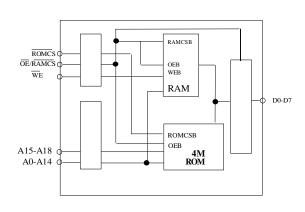

#### **FUNCTIONAL BLOCK DIAGRAM**

| WE | LX50CM432I<br>32-Pin TSOP | 32   GECS2   31   A10   30   CES1   29   D7   28   D6   27   D5   26   D4   25   D3   24   VSS   23   D2   22   D1   21   D0   20   A0   19   A1   18   A2   17   A3 |

|----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                         | Pin Function             |

|----------------------------------|--------------------------|

| A <sub>0</sub> - A <sub>18</sub> | Address Inputs           |

| $\overline{	ext{WE}}$            | Write Enable Input       |

| OE/CS2                           | Output Enable/RAM Enable |

|                                  | Input                    |

| CS 1/ROMCSB                      | ROM Enable Input         |

| CS 2/RAMCSB                      | RAM Enable Input         |

| D0-D7                            | Data Inputs / Outputs    |

| $V_{CC}$                         | Power (1.8 v - 3.3 v)    |

| $V_{SS}$                         | Ground                   |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Item                                              | Symbol           | Rating                     | Unit           |

|---------------------------------------------------|------------------|----------------------------|----------------|

| Voltage on any pin relative to V <sub>SS</sub>    | $V_{\rm IN,OUT}$ | $-0.5$ to $V_{CC} + 0.5$   | V              |

| Voltage on Vcc Supply Relative to V <sub>SS</sub> | $V_{CC}$         | -0.5 to 4.0                | V              |

| Power Dissipation                                 | $P_{\mathrm{D}}$ | 1.0                        | W              |

| Storage Temperature                               | $T_{stg}$        | -65 to 150                 | o <sub>C</sub> |

| Operating Temperature                             | $T_{A}$          | -40 to 85                  | °C             |

| Soldering Temperature and Time                    | $T_{solder}$     | 260 °C, 10 sec (Lead Only) | -              |

<sup>\*</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **RECOMMENDED DC OPERATING CONDITIONS** ( $T_A = -40 \text{ TO } 85 ^{\circ}\text{C}$ )

| Item                       | Symbol      | Min. | Max.           | Unit |

|----------------------------|-------------|------|----------------|------|

| Supply Voltage             | $V_{CC}$    | 1.8  | 3.3            | V    |

| Ground                     | $V_{SS}$    | 0    | 0              | V    |

| Input High Voltage- 1.8 v  | $V_{IH}$    | 1.4  | $V_{CC} + 0.5$ | V    |

| Input High Voltage - 3.0 v | $V_{IH}$    | 2.4  | $V_{CC} + 0.5$ | V    |

| Input Low Voltage - 1.8 v  | $V_{ m IL}$ | -0.3 | 0.3            | V    |

| Input Low Voltage - 3.0 v  | $V_{ m IL}$ | -0.3 | 0.3            | V    |

### DC AND OPERATING CHARACTERISTICS (Ta = -40 to 85 °C)

| Item                            | Symbol          | Test Conditions                                                                                                                                                             | VCC: | =1.8V | VCC=3.0 | V <u>+</u> 0.3       | Units |

|---------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------|----------------------|-------|

|                                 |                 |                                                                                                                                                                             | Min  | Max   | Min     | Max                  |       |

| Input Leakage<br>Current        | $I_{LI}$        | $V_{IN}=V_{SS}$ to $V_{CC}$                                                                                                                                                 | -500 | 500   | -500    | 500                  | nA    |

| Output Leakage<br>Current       | $I_{LO}$        |                                                                                                                                                                             | -500 | 500   | -500    | 500                  | nA    |

| ROM Operating<br>Supply Current | $I_{CC1}$       | $\begin{array}{c} \overline{CS} \ 1=V_{IL}, \ \overline{CS} \ 2=V_{IH}, \\ V_{IN}=V_{IH} \ or \ V_{IL}, \ I_{I/O}=0 \\ mA \end{array}$                                      | -    | -     | -       | 10.00<br>+<br>1.1(f) | mA    |

| RAM Operating<br>Current        | $I_{CC2}$       | $\frac{\overline{\text{CS}}}{\overline{\text{CS}}} 1 = V_{\text{IH,}}$ $\frac{\overline{\text{CS}}}{\overline{\text{CS}}} 2 = V_{\text{IL}}, I_{\text{I/O}} = 0 \text{ mA}$ | 1    | 1     | -       | 9.00<br>+<br>1(f)    | mA    |

| Standby Power Supply Current    | $I_{SB}$        | $\overline{CS} \ge V_{CC}-0.2V$ $V_{IN} \le 0.2V, V_{IN} \ge V_{CC}-0.2V$                                                                                                   | -    | -     | -       | 30                   | μΑ    |

| Output Low Voltage              | V <sub>OL</sub> | $I_{OL}$ = 1.0 mA at 3.3 V                                                                                                                                                  |      | 0.4   |         | 0.4                  | V     |

| Output High Voltage             | $V_{OH}$        | $I_{OH}$ = -0.5 mA at 3.3 V                                                                                                                                                 | 0.8  | -     | 2.2     | -                    | V     |

**NOTE:**  $\overline{CS} = \overline{CS}$  1 &  $\overline{CS}$  2,  $\overline{CS}$  1 = ROMCSB,  $\overline{CS}$  2 = RAMCSB, f=1/cycle time

### **CAPACITANCE** \*(f =1MHz, Ta = 25 °C)

| Item                       | Symbol    | Test Condition | Min | Max | Unit |

|----------------------------|-----------|----------------|-----|-----|------|

| Input Capacitance          | $C_{IN}$  | $V_{IN}=0V$    | -   | 6   | pF   |

| Input / Output Capacitance | $C_{I/O}$ | $V_{I/O}=0V$   | -   | 8   | pF   |

### **TEST CONDITIONS** (Ta=-40 TO 85 °C)

| Parameter                                | Value                    |                              |  |  |  |  |

|------------------------------------------|--------------------------|------------------------------|--|--|--|--|

|                                          | $V_{CC} = 1.8 \text{ V}$ | $V_{\rm CC} = 3.0 \text{ V}$ |  |  |  |  |

| Input Pulse Level                        | 0 to 3V                  | 0 to 3V                      |  |  |  |  |

| Input Rise and Fall Time                 | 5 ns                     | 5 ns                         |  |  |  |  |

| ( 10% to 90% VCC )                       |                          |                              |  |  |  |  |

| Input and Output Timing Reference Levels | 0.90 V                   | 1.5 V                        |  |  |  |  |

| Output Load                              | CL=100pF                 | CL=100pF                     |  |  |  |  |

<sup>\*</sup> Including scope and jig capacitance

## I. ROM Operation ( $\overline{CS} = RAMCSB = VIH$ )

#### **READ CYCLE**

| Parameter                       | Symbol           | Vcc=1.8 V<br>Worse Case |     | Vcc=3.0 V ± 0.3<br>Worse Case |     | Unit |

|---------------------------------|------------------|-------------------------|-----|-------------------------------|-----|------|

|                                 |                  | Min                     | Max | Min                           | Max |      |

| Read Cycle Time                 | t <sub>RC</sub>  | 500                     |     | 150                           |     | ns   |

| Address Access Time             | t AA             |                         | 500 |                               | 150 | ns   |

| Chip Select to Output           | t co             |                         | 500 |                               | 150 | ns   |

| Output Enable to Valid Output   | t OE             |                         | 250 |                               | 100 | ns   |

| Chip Select to Low-Z Output     | $t_{LZ}$         | 25                      |     | 15                            |     | ns   |

| Output Enable to Low-Z Output   | t <sub>OLZ</sub> | 25                      |     | 15                            |     | ns   |

| Chip Disable to High-Z Output   | t <sub>HZ</sub>  | 0                       | 30  | 0                             | 30  | ns   |

| Output Disable to High-Z Output | t <sub>OHZ</sub> | 0                       | 30  | 0                             | 30  | ns   |

| Output Hold from Address Change | t <sub>OH</sub>  | 8                       |     | 10                            |     | ns   |

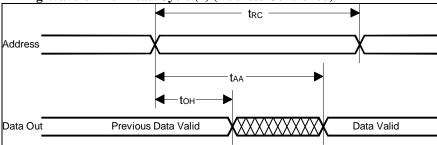

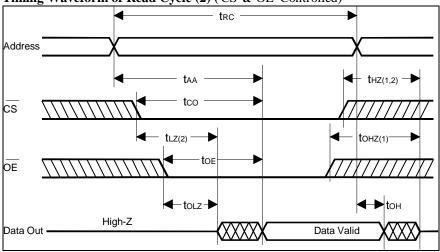

#### **TIMING DIAGRAMS**

Timing Waveform of Read Cycle (1) (Address Controlled)

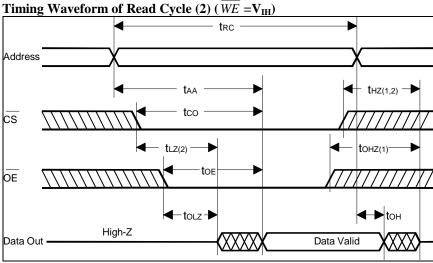

Timing Waveform of Read Cycle (2) ( CS & OE Controlled)

#### **NOTES (READ CYCLE)**

- 1.  $t_{HZ}$  and  $t_{OHZ}$  are defined as the time at which the outputs achieve the open circuit condition and are referenced to the  $V_{OH}$  or  $V_{OL}$ .

- 2. At any given temperature and voltage condition t<sub>HZ</sub>(max) is less than t<sub>LZ</sub>(min) both for a given device and from device to device.

- 3. CS 2/RAMCSB is high for read cycle.

- Address valid prior to or coincident with CS 1 transition Low.

### II. SRAM Operation ( $\overline{CS} 1 = ROMCSB = VIH$ )

#### **READ CYCLE**

| Parameter                       | Symbol           | Vcc=1.8 V<br>Worse Case |     | Vcc=3.0 V ± 0.3<br>Worse Case |     | Unit |

|---------------------------------|------------------|-------------------------|-----|-------------------------------|-----|------|

|                                 |                  | Min                     | Max | Min                           | Max |      |

| Read Cycle Time                 | t <sub>RC</sub>  | 500                     |     | 150                           |     | ns   |

| Address Access Time             | t AA             |                         | 500 |                               | 150 | ns   |

| Chip Select to Output           | t co             |                         | 500 |                               | 150 | ns   |

| Output Enable to Valid Output   | t oe             |                         | 250 |                               | 100 | ns   |

| Chip Select to Low-Z Output     | $t_{LZ}$         | 25                      |     | 15                            |     | ns   |

| Output Enable to Low-Z Output   | t <sub>OLZ</sub> | 25                      |     | 15                            |     | ns   |

| Chip Disable to High-Z Output   | t <sub>HZ</sub>  | 0                       | 30  | 0                             | 30  | ns   |

| Output Disable to High-Z Output | t <sub>OHZ</sub> | 0                       | 30  | 0                             | 30  | ns   |

| Output Hold from Address Change | t <sub>OH</sub>  | 15                      |     | 10                            |     | ns   |

#### **WRITE CYCLE**

| Parameter                     | Symbol            | Vcc=1.8V |     | $Vcc=3.0V \pm 0.3$ |     | Unit |

|-------------------------------|-------------------|----------|-----|--------------------|-----|------|

|                               |                   | Min      | Max | Min                | Max |      |

| Write Cycle Time              | $t_{WC}$          | 500      |     | 150                |     | ns   |

| Chip Select to End of Write   | $t_{CW}$          | 365      |     | 120                |     | ns   |

| Address Valid to End of Write | $t_{AW}$          | 375      |     | 120                |     | ns   |

| Address Set-up Time           | $t_{AS}$          | 0        |     | 0                  |     | ns   |

| Write Pulse Width             | $t_{\mathrm{WP}}$ | 375      |     | 110                |     | ns   |

| Write Recovery Time           | $t_{\mathrm{WR}}$ | 0        |     | 0                  |     | ns   |

| Write to Output High-Z        | $t_{ m WHZ}$      | -        | 80  | 0                  | 70  | ns   |

| Data to Write Time Overlap    | $t_{\mathrm{DW}}$ | 200      |     | 100                |     | ns   |

| Data Hold from Write Time     | t <sub>DH</sub>   | 0        |     | 0                  |     | ns   |

| End Write to Output Low-Z     | t <sub>OW</sub>   | 15       |     | 10                 |     | ns   |

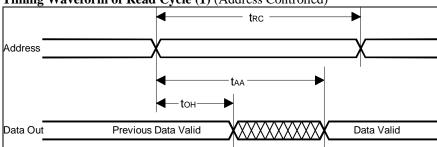

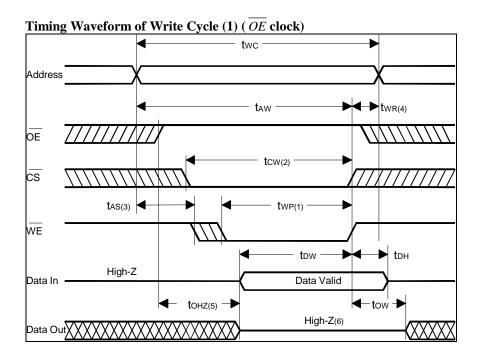

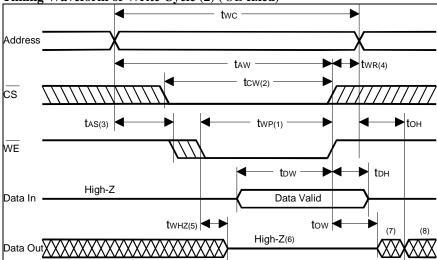

#### **TIMING DIAGRAMS**

Timing Waveform of Read Cycle (1) (Address Controlled)

#### **NOTES (READ CYCLE)**

- $t_{HZ}$  and  $t_{OHZ}$  are defined as the time at which the outputs achieve the open circuit condition and are referenced to the  $V_{OH}$  or  $V_{OL}$

- At any given temperature and voltage condition  $t_{HZ}(max)$  is less than  $t_{LZ}(min)$  both for a given device and from device to device. 2.

- 3. WE is high for read cycle.

- Address valid prior to or coincident with  $\overline{\text{CS}}$  2 transition Low.

Timing Waveform of Write Cycle (2) ( $\overline{OE}$  fixed)

#### **NOTES (WRITE CYCLE)**

- 1. A write occurs during the overlap  $(t_{WP})$  of a low  $\overline{CS}$  2 and low  $\overline{WE}$ . A write begins at the latest transition among  $\overline{CS}$  2 going low and  $\overline{WE}$  going low: A write end at the earliest transition among  $\overline{CS}$  2 going high and  $\overline{WE}$  going high,  $t_{WP}$  is measured from the beginning of write to the end of write.

- 2.  $t_{CW}$  is measured from the later of  $\overline{CS}$  2 going low to end of write.

- 3.  $t_{AS}$  is measured from the address valid to the beginning of write.

- $\label{eq:twr} 4. \hspace{0.5cm} t_{WR} \mbox{ is measured from the end of write to the address change}.$

- if OE , WE are in the read mode during this period, the I/O pins are in the outputs Low-Z state. Inputs of opposite phase of the output must not be applied because bus contention can occur.

- 6. If  $\overline{\text{CS}}$  2 goes low simultaneously with  $\overline{\text{WE}}$  going low or after  $\overline{\text{WE}}$  going low, the outputs remain high impedance state.

- 7.  $D_{OUT}$  is the same phase of the latest written data in this write cycle.

- 8. D<sub>OUT</sub> is the read data of new address

- 9.  $\overline{CS}$  1= ROMCSB = VIH

## **Functional Description/Truth Table**

| A0=A18                  | ROMCSB | RAMCSB/OE  | WE | D0-D7 |          |

|-------------------------|--------|------------|----|-------|----------|

|                         |        | (PIN 32)   |    |       |          |

| X                       | Н      | Н          | X  | Z     | Standby  |

|                         |        |            |    |       |          |

| A0-A18                  | L      | OE (H)     | X  | Z     | Output   |

|                         |        |            |    |       | Floating |

| A0-A18                  | L      | OE (L)     | X  | Dout  | ROM      |

|                         |        |            |    |       | read     |

| Only A0-A14 are vaild * | Н      | RAMCSB (L) | Н  | Dout  | RAM      |

| •                       |        |            |    |       | read     |

| Only A0-A14 are vaild * | Н      | RAMCSB (L) | L  | Din   | RAM      |

|                         |        |            |    |       | write    |

<sup>\*</sup> A15 to A18 must be fixed to "L" or "H"

Note: (1)  $\overline{OE}$  &  $\overline{CS}2$  are pin-shared

(2) X means Don't Care.

#### PACKAGE OUTLINES AND DIMENSIONS

1050 E. Duane Avenue, Suite E Tel: (408) 732-2378 Sunnyvale, Ca. 94086

Fax: (408) 732-1748