# L9520 POTS/DSL Enhanced Line Interface Low-Power SLIC and Ring Relay with Integrated Test

### Introduction

The Agere Systems Inc. L9520 is a combination full-feature, ultralow-power SLIC, solid-state ringing access relay, and line test matrix. It forms an ideal chip set with the Agere T8531/2 codec for POTS and DSL line cards, providing *Telcordia*<sup>™</sup> GR844 test capability, tone plant, and fully programmable ac parameters. The chip set will meet TR57 POTS requirements including the effects of the DSL coupling and POTS filter.

# **Applications**

- POTS plus DSL

- Digital loop carrier (DLC)

- Central office (CO)

### **Features Overview**

- Integrated SLIC, solid-state ring relay, and line test

- Ideal for POTS and DSL applications

- TR57 compliant POTS interface

- 5 V and battery operation

- Optional automatic battery switch

- 15 operational and test modes

- Two performance grades based on TR57 58 dB or ETSI/ITU-T 46 dB longitudinal balance requirements

- Minimal external components required at all interfaces

- Ultralow power dissipation

- Software/hardware adjustable dc parameters and supervision thresholds

- Ground start/ground key compatible

- Low impulse noise associated with ring relay

- Current-limited switches/thermal protection

- When paired with T8531/2 codec provides hardware and software for GR844 testing

- 68-pin MLCC package

# **Description Overview**

The L9520 electronic line interface and line access circuit provides all the functions that are necessary to interface a codec to the tip and ring of a subscriber loop, integrating the battery feed and ringing access relay and the line test access in one low-power, low-cost package.

The L9520 provides an ideal solution for POTS plus DSL applications when used with the Agere Systems T8531/2 codec. Together, this chip set provides fully programmable ac parameters that are consistent with TR57 requirements, undergirded test that is consistent with GR844 requirements, and tone plant that includes DTMF generation, reception caller ID, and call progress tones.

The L9520 is optimized to interface to the Agere Systems T8531/2 codec. It will also cleanly interface to the Agere T8534/6 series codec. This device will not interface to any commercially available codec other than the Agere T8531/2 or T8534/6.

The L9520 requires a 5 V and battery supply to operate. Included is an automatic battery switch. The battery feed offers forward and reverse battery, on-hook transmission, ground start, ground key, and meter pulse operational modes. It also has a low-power scan and a disconnect mode.

In all operating states, this IC is designed for minimal power dissipation. This device is designed to minimize the number of external components required at all interfaces.

The dc template, current limit, and overhead voltage and loop supervision threshold are programmable via an applied voltage source. The voltage source may be an external programmable voltage source or derived from the VREF SLIC output.

The integrated solid-state switch offers power ringing access. Impulse noise is minimized, therefore eliminating the need for external zero-cross switching circuitry.

**Page**

# **Table of Contents**

| Contents                              | Page | Contents                                      | age |

|---------------------------------------|------|-----------------------------------------------|-----|

| Introduction                          | 1    | Automatic Battery Switch                      | 29  |

| Applications                          | 1    | dc Loop Current Limit                         |     |

| Features Overview                     | 1    | Overhead Voltage                              | 31  |

| Description Overview                  | 1    | Loop Range                                    | 32  |

| Features                              | 4    | Battery Feed                                  | 32  |

| Description                           | 4    | Battery Reversal Rate                         | 33  |

| Architecture                          | 8    | Longitudinal to Metallic Balance              | 33  |

| Pin Information                       | 9    | Supervision                                   | 33  |

| Operating States                      | 12   | Loop Closure                                  | 33  |

| Input State Coding                    | 12   | Ring Trip                                     | 34  |

| State Definitions                     | 14   | Tip or Ring Ground Detector                   | 34  |

| Primary Control Modes                 | 14   | Switching Behavior                            |     |

| Powerup, Forward Battery              | 14   | Make-Before-Break Operation                   | 34  |

| Powerup, Reverse Battery              | 14   | Break-Before-Make Operation                   |     |

| Scan                                  | 14   | Protection                                    | 35  |

| Ground Start                          | 14   | External Protection                           | 35  |

| Ringing                               | 15   | Active Mode Response at PT/PR                 | 36  |

| Disconnect—Break Before Make          | 15   | Ring Mode Response at PT/PR                   | 37  |

| Tip Amp                               | 15   | Internal Tertiary Protection                  | 37  |

| Ring Amp                              | 15   | Diode Bridge                                  | 37  |

| Tip and Ring Amp Open                 | 15   | Battery Out of Range Detector:                |     |

| Reset                                 | 15   | High (Magnitude)                              | 37  |

| Secondary Control Mode States         | 15   | Battery Out of Range Detector:                |     |

| Voltage: Tip to Ground                | 15   | Low (Magnitude)                               | 37  |

| Voltage: Ring to Ground               | 15   | Line Test with Agere T8531/2 Codec            | 38  |

| Voltage: Tip to Ring                  | 15   | ac Applications                               | 39  |

| Current: Tip to Ring—VTX              | 15   | ac Parameters                                 | 39  |

| Current: Tip to Ring—VITR             | 16   | Codec Types                                   | 39  |

| Voltage: Reference—VREF               | 16   | First-Generation Codecs                       | 39  |

| TEST-R                                | 16   | Third-Generation/Fourth-Generation Codecs     | 39  |

| TEST-R Off                            | 16   | ac Interface Network                          | 39  |

| Special States                        | 16   | Design Tools                                  | 39  |

| Thermal Shutdown                      | 16   | PSPICE® Models                                | 39  |

| Battery Out of Range                  | 16   | Application System                            | 39  |

| Absolute Maximum Ratings              | 17   | Application Boards                            | 39  |

| Electrical Characteristics            | 18   | Third-Generation Codec ac Interface Network:  |     |

| Package Thermal Characteristics       | 19   | Complex Termination                           | 40  |

| Ring Trip Detector                    | 19   | Fourth-Generation Codec ac Interface Network: |     |

| Test                                  |      | Complex Termination                           | 42  |

| SLIC 2-Wire Port                      | 21   | Outline Diagram                               |     |

| Analog Pin Characteristics            | 22   | 68-Pin MLCC                                   |     |

| ac Feed Characteristics               |      | Ordering Information                          | 45  |

| Logic Inputs and Outputs, VDD = 5.0 V | 24   |                                               |     |

| Timing Requirements                   |      |                                               |     |

| Switch Characteristics                | 25   |                                               |     |

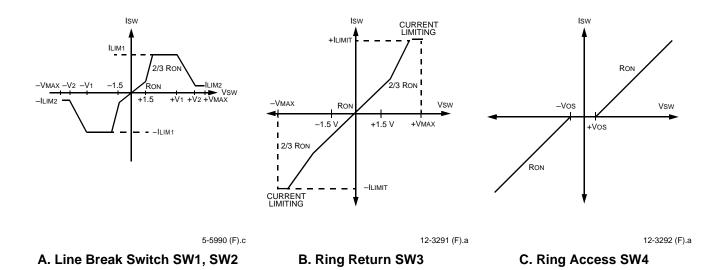

| On-State Switch I-V Characteristics   | 26   |                                               |     |

| Test Configurations                   | 27   |                                               |     |

| Applications                          |      |                                               |     |

| dc Characteristics                    |      |                                               |     |

| Power Control                         | 29   |                                               |     |

| Power Derating                        | 29   |                                               |     |

# Table of Contents (continued)

| Table     | Page                                  | Figure    | Page                                     |

|-----------|---------------------------------------|-----------|------------------------------------------|

| Table 1.  | Pin Descriptions10                    | Figure 1. | Architecture Diagram 8                   |

| Table 2.  | Primary Control States13              | Figure 2. | Test Switch Configuration9               |

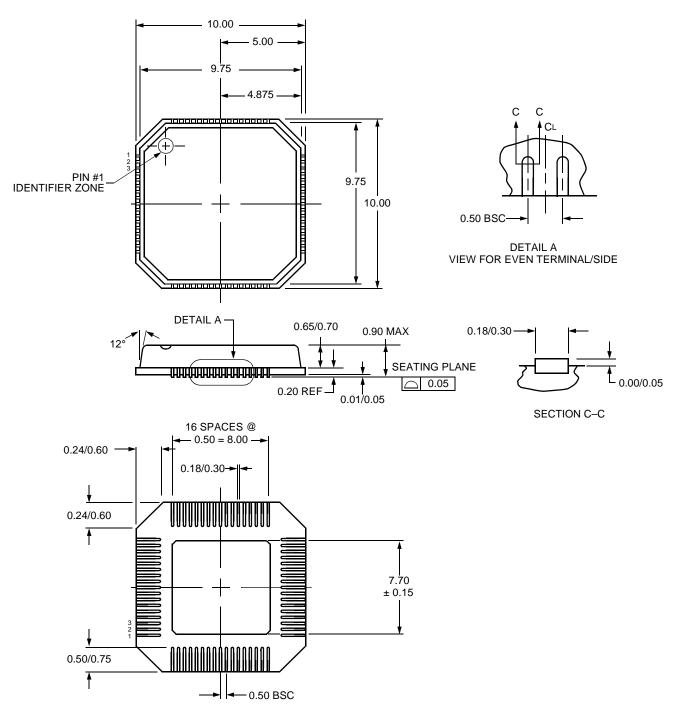

| Table 3.  | Secondary Control States13            | Figure 3. | 68-Pin MLCC                              |

| Table 4.  | Supervision Coding13                  | Figure 4. | Timing Requirements24                    |

| Table 5.  | Absolute Maximum Ratings17            | Figure 5. | On-State Switch I-V Characteristics 26   |

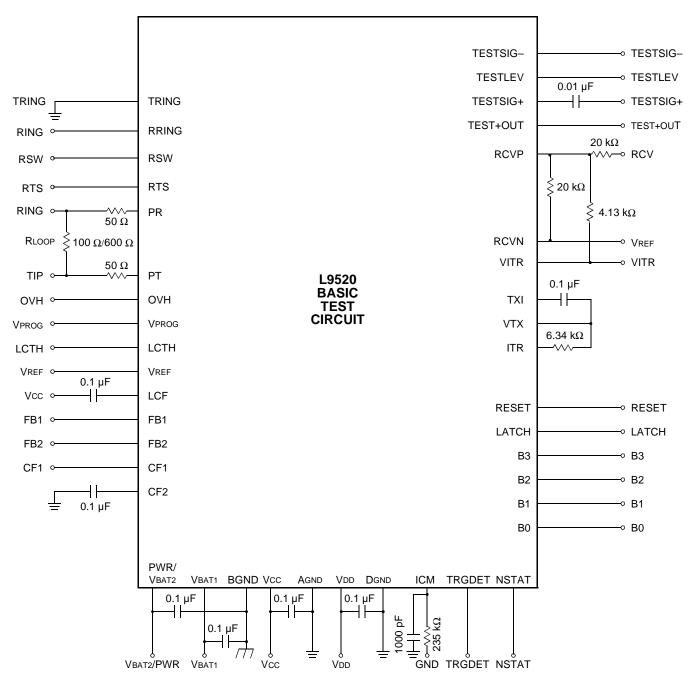

| Table 6.  | Device Operating Conditions           | Figure 6. | Basic Test Circuit27                     |

|           | and Powering18                        | Figure 7. | Metallic PSRR28                          |

| Table 7.  | Thermal19                             | Figure 8. | Longitudinal PSRR28                      |

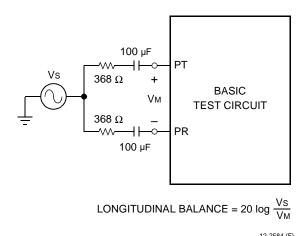

| Table 8.  | Ring Trip Detector19                  |           | Longitudinal Balance 28                  |

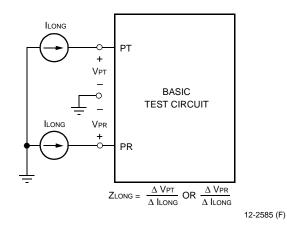

| Table 9.  | ac Test Source20                      | Figure 10 | Longitudinal Impedance28                 |

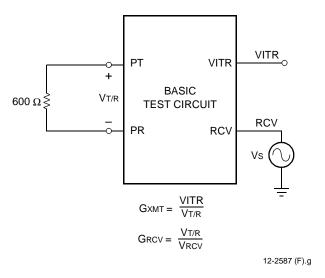

|           | Test Sense20                          |           | . ac Gains 28                            |

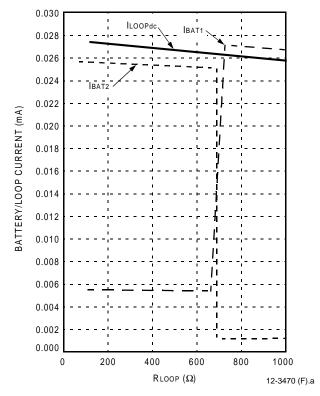

| Table 11. | SLIC 2-Wire Port21                    | Figure 12 | . L9520 Loop/Battery Current (with       |

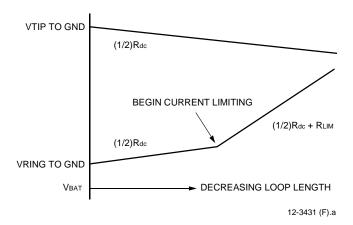

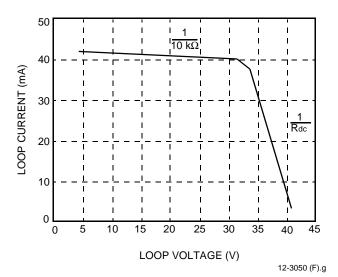

| Table 12. | Analog Pin Characteristics22          |           | Battery Switch) vs. Loop Resistance 30   |

|           | ac Feed Characteristics23             |           | . Tip/Ring Voltage 32                    |

|           | Logic Inputs and Outputs24            |           | . L9520 Loop Current vs. Loop Voltage 33 |

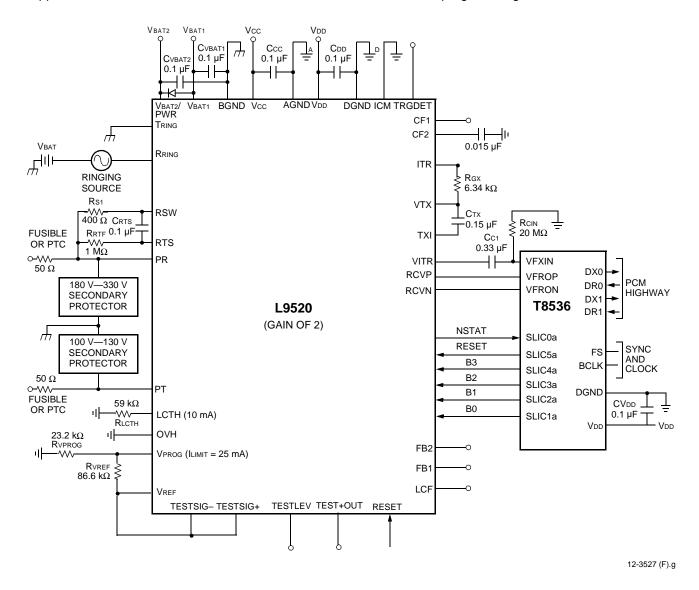

|           | Timing Requirements24                 | Figure 15 | . L9520 SLIC for Agere T8536 Third-      |

|           | Break Switches (SW1, SW2)25           |           | Generation Codec, Dual-Battery           |

| Table 17. | Ring Return Switch (SW3)25            |           | Operation, ac Parameters, Fully          |

| Table 18. | Ringing Access Switch (SW4)26         |           | Programmable40                           |

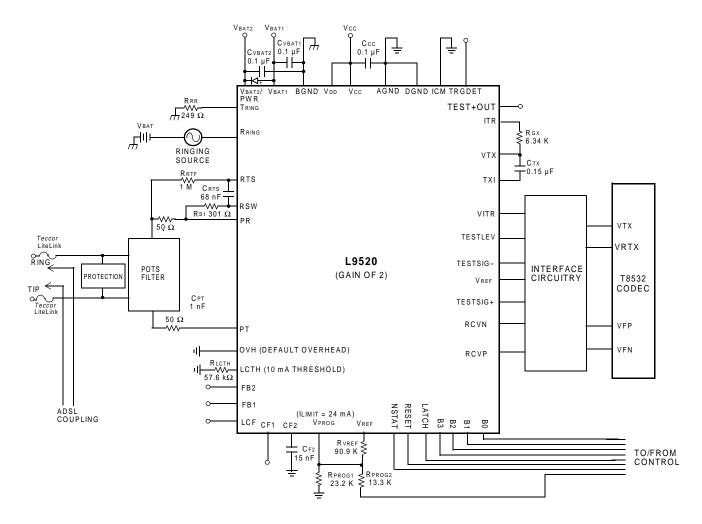

| Table 19. | Typical Active Mode On- to Off-Hook   | Figure 16 | . L9520 SLIC for Agere T8531/2 Fourth-   |

|           | Tip/Ring Current-Limit Transient      |           | Generation Codec, with DSL               |

|           | Response31                            |           | Compensation, Dual-Battery Operation,    |

| Table 20. | FB1 and FB2 Values vs. Typical        |           | ac and dc Parameters, and Fully          |

|           | Ramp Time33                           |           | Programmable per Line Test 42            |

| Table 21. | Break-Before-Make Logic Control       |           |                                          |

|           | Sequence Device Switching35           |           |                                          |

|           | TESTLEV Output Options38              |           |                                          |

| Table 23. | L9520 Parts List for Agere T8536      |           |                                          |

|           | Third-Generation Codec Meter Pulse    |           |                                          |

|           | Application, Dual-Battery Operation,  |           |                                          |

|           | ac and dc Parameters, and Fully       |           |                                          |

|           | Programmable41                        |           |                                          |

| Table 24. | L9520 Parts List for Agere T8531/2    |           |                                          |

|           | Fourth-Generation Codec, with DSL     |           |                                          |

|           | Compensation, Dual-Battery Operation, |           |                                          |

|           | ac and dc Parameters, and Fully       |           |                                          |

|           | Programmable per Line Test43          |           |                                          |

|           |                                       |           |                                          |

#### **Features**

- SLIC, solid-state ring relay, and line test access, integrated into a single package

- 5 V and battery operation

- User-defined power control options:

- Automatic battery switch

- Power control resistor

- Package thermal capabilities

- Minimal external components required

- Operating states:

- Forward active

- Reverse active (controlled rate of reversal)

- Scar

- Ground start (tip open)

- All-off or disconnect

- Ring

- Line test modes (dc/ac line voltage/current)

- Ultralow power:

- Scan state, 15 mW

- Active state, on-hook, 83 mW

- Ring state, on-hook, 155 mW

- Disconnect state, 7 mW

- Adjustable overhead voltage:

- Default overhead adequate for 3.14 dB into  $900 \Omega$  overload

- Controlled rate of overhead adjustment

- Latched parallel input data interface with reset

- Interrupt (unlatched) based loop status monitor

- Adjustable current limiter:

- 10 mA to 70 mA programming range

- Adjustable loop closure detector with hysteresis:

- 4 mA detect, 2.5 mA no detect minimum, upper limit of 15 mA detect

- Hysteresis, typical 20% of programmed on-hook to off-hook threshold

- Ring trip detector:

- Single-pole filtering

- Thermal shutdown protection with hysteresis

- Line break switch will foldover into a low-current state under high-voltage fault conditions

- Battery out-of-range monitor circuit:

- All-off upon loss of battery (low battery condition)

- All-off upon high battery (fault condition)

- Longitudinal balance:

- TR57 balance (L9520G)

- ETSI/ITU-T balance (L9520K)

- Ground start:

- Tip open state

- Ring ground detector

- Ground key:

- Tip/ring ground detector

- Line test:

- Line test modes (ac or dc), including the following:

- Voltage tip to ground

- Voltage ring to ground

- Voltage tip to ring

- Current tip to ring

- Current tip to ground

- Current ring to ground

- Generate test tones and control script via T8532 codec

- Direct coupling to T8531 codec

- Integrated 2 form C ring relay:

- Low impulse noise

- Current-limited switches

- Break-before-make and make-before-break switching

- Meets ITU-T K20, ITU-T K21, and Telcordia GR1089 requirements with external protection device

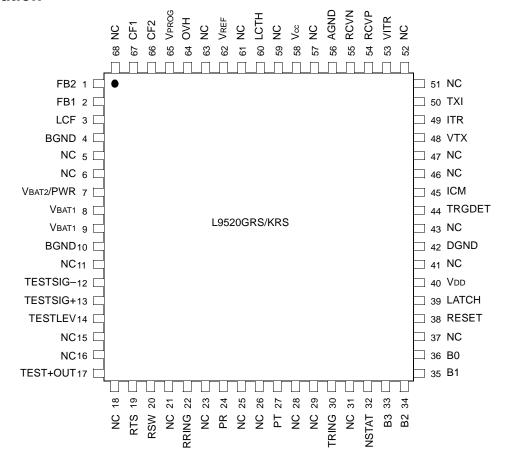

- 68-pin, surface-mount MLCC

# **Description**

The L9520 electronic line interface and line access circuit provides all the functions that are necessary to interface a codec to the tip and ring of a subscriber loop, integrating the battery feed and ringing access relay in one low-power, low-cost package. The physical construction of the device is two chips. The first chip is manufactured in Agere's 90 V complementary bipolar integrated circuit (CBIC-S) technology. This chip contains the following SLIC functionality:

- ac transmission path

- dc feedback and functions

- Active dc current limit

- Active mode loop supervision

- Thermal shutdown

The second chip is manufactured with Agere's dielectrically isolated 320 V bipolar CMOS diffused metal oxide semiconductor (BCDMOS III) technology. This chip contains the following:

- Ring access relay

- Scan clamp circuitry

- Logic control

- Ring trip

- Test

- Thermal shutdown

- Battery monitor circuit

# **Description** (continued)

The L9520 requires a 5 V power supply and a battery supply to operate. No -5 V supply is required. A battery switch is included that will automatically (based on subscriber loop length) apply either the primary higher-voltage battery or an optional lower-voltage auxiliary battery. Use of this feature will minimize off-hook power dissipation.

The switch point is a function of the user-programmed dc current limit and the magnitude of the auxiliary battery. Switching from the high-voltage battery to the low-voltage battery is quiet and does not interrupt the dc loop current, therefore preventing any impulse noise generation at the switch point. Design equations for the switch point and a graph showing loop/battery current versus loop resistance are given in the dc Characteristics section of this data sheet.

If the user does not want to provide an auxiliary battery, the design of the L9520 battery switch allows use of a power control resistor at the auxiliary battery input. This scheme will not reduce short-loop, off-hook power dissipation, but it will control power dissipation on the SLIC by sharing power among the SLIC, power resistor, and dc loop. However, in most cases, without the auxiliary battery, the power dissipation capabilities of the 68-pin MLCC package are enough that the power control resistor will not be needed. Design equations for power control options are given in the dc Characteristics section of this data sheet.

The L9520 has two active transmission ready states, forward active and reverse active. Both on-hook and off-hook transmission are provided during the forward and reverse battery modes. Battery reversal is quiet and does not break the ac path. Rate of battery reversal may be ramped to control switching time via optional external capacitors. Equations relating rate of battery reversal to these optional external capacitors are given in the dc Characteristics, Power Control section of this data sheet.

A low-power scan mode is available to reduce idle mode on-hook power. This mode is realized by using a scan clamp circuit. The following occurs in low-power scan mode:

- The scan clamp circuitry is active.

- Loop closure is active.

- All ac transmission, dc feed, and other supervision circuits, including ring trip, are shut down.

- Test is powered down.

- Thermal shutdown is active.

- Low battery sense shutdown is on.

- On-hook transmission is disabled.

When the scan clamp circuitry is on, overhead voltage is fixed and not controlled by OVH. When the scan clamp is on, current limit is not controlled by VPROG; rather, it is set by the internal capabilities of the scan clamp circuit. See the dc Loop Current Limit and Overhead Voltage sections of this data sheet for more details.

A forward disconnect mode, where all circuits are turned off and power is denied to the loop, is also provided. During this mode, the NSTAT supervision output will read on-hook.

In the ring mode, the line break switches are opened and the power ring access switches are closed. In this mode, the ring trip detector in the SLIC is active and all other detectors and the tip/ring drive amplifiers are turned off to conserve power.

Make-before-break or break-before-make switching is achievable during ring cadence or ring trip. Toggling directly into or directly out of the ring mode table will give make-before-break switching. To achieve break-before-make switching, go to an intermediate all-off state (use forward disconnect state) before entering the ring mode or before leaving the ring mode. See the Switching Behavior section of this data sheet for more details on switching behavior.

Voltage transients or impulse noise associated with ring cadence or ring trip are minimized or eliminated with the L9520, therefore possibly eliminating the need for external zero-cross switching circuitry.

A tip open switch configuration is also available for ground start applications. A common-mode current detector is included for ground start and ground key applications.

Both the ring trip and loop closure supervision functions are included. Loop closure threshold is set by applying a voltage source to the LCTH input. The voltage source may be an external voltage source or derived from the SLIC VREF output. A programmable external voltage source may be used to provide software control of the loop closure threshold. Design equations for the loop closure threshold are given in the Supervision section of this data sheet. Hysteresis is included.

The ring trip detector requires only a single-pole filter at the input. This will minimize the required number of external components. To help minimize device power dissipation, the ring trip detector is active only during the power ring mode.

# **Description** (continued)

Ring trip and loop supervision status outputs appear in a common output pin, NSTAT. NSTAT is an unlatched supervision output; therefore, an interrupt-based control scheme may be used.

The dc current limit is set in the active modes via an applied voltage source. The voltage source may be an external voltage source. The voltage may be derived via a resistor divider network from the VREF SLIC output. A programmable external voltage source may be used to provide software control of the loop closure threshold. Programming range is 10 mA to 70 mA. Design equations for this feature are given in the dc Characteristics section of this data sheet.

Overhead is programmable in the active modes via an applied voltage source. The voltage source may be an external voltage source or derived via a resistor divider network from the VREF SLIC output.

A programmable external voltage source may be used to provide software control of the overhead voltage. A potential application of this feature is to increase overhead during test modes requiring higher voltages and reduce overhead during periods of nontest. The rate of change of the overhead voltage may be controlled by use of a single external capacitor at the CF1 node. If the rate of change is uncontrolled, there may be audible noise associated with this transition. Design equations for this feature are given in the dc Characteristics section of this data sheet.

If the overhead is not programmed via a resistor, the device develops a default overhead suitable for a 3.14 dBm overload into 900  $\Omega$ . For the default overhead, OVH is connected to ground.

The L9520 provides line test capability. In the test mode, a voltage proportional to the ac or dc tip-to-ground, ring-to-ground, tip-to-ring voltage or current may be presented at the SLIC TESTLEV output.

An ac test tone may also be applied to either a test input (TESTSIG-) or through the TESTSIG+ input. By varying the frequency of the applied test tone, parameters such as line capacitance may be measured.

This test feature may be conveniently utilized with the T8531/2 codec. This codec provides necessary test tones and provides control and data interpretation to run a test script consistent with GR844 requirements.

The TESTSIG inputs should be externally connected to the device's VREF if they are not used.

Test level outputs at TESTLEV are referenced to the internally generated reference voltage VREF. This reference voltage may also be output at TESTLEV so the

users can compensate test results at TESTLEV for the internal reference.

Note that during nontest modes, TESTLEV is high impedance to conserve power. Inputs TESTSIG are turned off during any nontest mode and during the VREF test mode.

The various test modes are achieved through a series of integrated analog switches that can reconfigure the SLIC to provide normal SLIC operation or the appropriate test function.

Test modes are achieved through the device state table. When entering a test mode, the state of the SLIC is unchanged; therefore, testing can be done with the SLIC in forward and reverse battery active modes. Additionally, via the line break switches associated with the ring relay, use of a tip-open or ring-open state is used to make single-ended voltage and current measurements.

Data control is via a parallel latched data control scheme. Data latches are edge-level sensitive. Data is latched in when the LATCH control input goes low. While LATCH is low, the user cannot change the data control inputs. The data control inputs may only be changed when LATCH is high.

Incorporation of data latches allows for data control information and loop supervision information to be passed to and from the SLIC via data buses rather than on a per-line basis, therefore minimizing routing complexity and board routing area.

A device RESET pin is included. When this pin is low, the logic inputs are overridden and the device will be reset into SLIC forward disconnect state and the switch into the all-off state. NSTAT is forced to the on-hook condition when RESET is low.

The overall device protection is achieved through a combination of an external secondary protector along with an integrated thermal shutdown feature, a battery voltage window comparator, the break switch foldback characteristic, and the dc/dynamic current-limit response of the break and tip return switches.

For protection against long duration fault conditions, such as power cross and tip/ring shorts, a thermal shutdown mechanism is integrated into the device. Upon reaching the thermal shutdown temperature, the device will enter an all-off mode. Upon cooling, the device will re-enter the state it was in prior to thermal shutdown. Hysteresis is built in to prevent oscillation. During this mode, the NSTAT supervision output overrides the actual loop status and forces an off-hook.

# **Description** (continued)

The line break switches and tip return switch are current-limited switches. The current-limit mechanism limits current through the switch to the specified dc current limit under low frequency or dc faults (power cross and/ or tip/ring to ground short) and limits the current to the specified dynamic current-limit response under transient faults, such as lightning.

A foldover characteristic is incorporated into the line break switches within their I-V curve. Under voltage conditions higher than the normal operating range, such as may be seen under an extreme lightning or power cross fault condition, the line break switch will foldover into a low-current state. This feature allows for more relaxed specifications on the ring side protector, therefore allowing for higher-voltage ringing signals. (Tip side protector is limited by the requirements on the tip return switch.) This feature is part of the overall device protection scheme.

This device uses a window comparator to force an alloff condition if the battery drops below, or rises above, a specified threshold.

Upon loss of VBAT1, the L9520 will automatically enter an all-off mode. The device will enter this mode if the magnitude of the battery drops below a nominal 15 V and will remain in this mode until the magnitude of the battery rises above a typical 20 V. During this mode, the NSTAT supervision output will override the actual hook status and force an off-hook or logic low.

When the device is in the scan mode, because of the design of the scan clamp circuit, common-mode current can be forced into or out of the battery supply. Because of this, and depending upon power supply design, the magnitude of the battery may rise above the maximum operating condition during extended longitudinal currents or during a power cross fault condition. To prevent excess current from being forced into or out of the battery, if the magnitude of the battery rises typically above 75 V to 80 V, the device will enter an all-off state. The device will remain in the all-off state until the magnitude of the battery drops into the normal operating range. During this mode, the NSTAT supervision output will override the actual hook status and force an off-hook or logic low.

See the Protection section of this data sheet for more details on device protection. Contact your Agere account representative for a recommended secondary protection device.

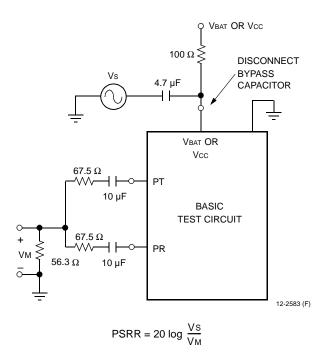

Two performance grades based on longitudinal balance are available. The higher-grade longitudinal balance is consistent *Telcordia* TR57 requirements. The lower-grade, with European ETSI and *Telcordia* GR-909 requirements.

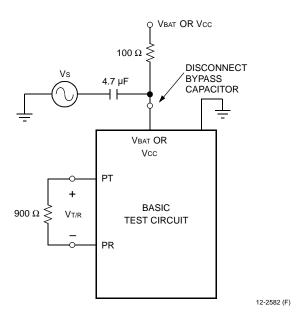

Transmit and receive gains have been chosen to minimize the number of external components required in the SLIC-codec ac interface. The L9520 uses a voltage feed, current sense architecture; therefore, the transmit gain is a transimpedance. The L9520 transimpedance is set via a single external resistor, and this device is designed for optimal performance with a transimpedance set at 300 V/A. The L9520 offers a single-ended to differential receive gain of 2.

A receive gain of 2 is appropriate when choosing an Agere System third-generation type codec. Third-generation codecs will synthesize termination impedance, set hybrid balance, and set overall gains. To accomplish these functions, third-generation codecs typically have both analog and digital gain filters. For optimal signal-to-noise performance, it is best to operate the codec at a higher-gain level. If the SLIC then provides a high gain, the SLIC output may be saturated, causing clipping distortion of the signal at tip and ring. To avoid this situation with a higher-gain SLIC, external resistor dividers are used. These external components are not necessary with the lower gain offered by the L9520.

A higher receive gain is needed when choosing a first-generation type codec where termination impedance, hybrid balance, and overall gains are set by external analog filters. The higher gain is typically required for interface to a competitive third-generation type codec requiring an inherent resistive termination. Since a higher-gain option is not available with this part, the device may only be used with the Agere T8531/2 or T8534/6 codecs.

This device is packaged in a 68-pin MLCC surfacemount package.

# **Architecture**

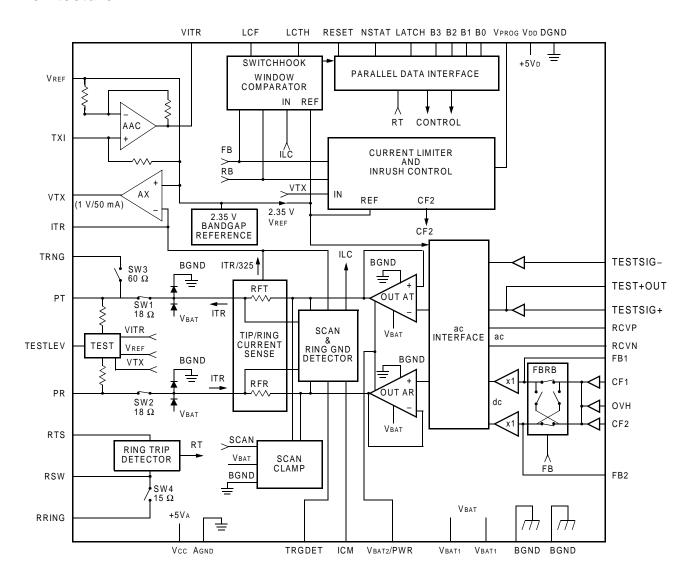

Figure 1. Architecture Diagram

12-3525 (F).c

9

# Architecture (continued)

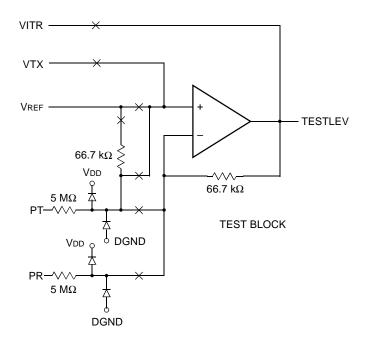

Figure 2. Test Switch Configuration

# **Pin Information**

Figure 3. 68-Pin MLCC

# Pin Information (continued)

**Table 1. Pin Descriptions**

| Pin | Symbol    | Type | Name/Function                                                                                                                                                                                                                                                                                         |

|-----|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FB2       | _    | <b>Polarity Reversal Slowdown Capacitor.</b> Connect a capacitor from this node to ground to control the rate of battery reversal. If controlled battery reversal is not desired, leave this pin open.                                                                                                |

| 2   | FB1       | _    | <b>Polarity Reversal Slowdown Capacitor.</b> Connect a capacitor from this node to ground to control the rate of battery reversal. If controlled battery reversal is not desired, leave this pin open.                                                                                                |

| 3   | LCF       |      | <b>Loop Closure Filter Capacitor.</b> Connect a capacitor from this node to Vcc to filter the loop closure detector. If loop closure filtering is not required, leave this node open.                                                                                                                 |

| 4   | BGND      | G    | Battery Ground. Ground return for the battery supply.                                                                                                                                                                                                                                                 |

| 7   | VBAT2/PWR | Р    | <b>Auxiliary Battery.</b> If a lower-voltage auxiliary battery is used, connect the auxiliary battery supply to this node. If a power control resistor is used, connect the power control resistor from this node to VBAT1. If no power control technique is used, connect this node to VBAT1.        |

| 8   | VBAT1     | Р    | Office Battery Supply. Negative high-voltage power supply.                                                                                                                                                                                                                                            |

| 9   | VBAT1     | Р    | Office Battery Supply. Negative high-voltage power supply.                                                                                                                                                                                                                                            |

| 10  | BGND      | G    | Battery Ground. Ground return for the battery supply.                                                                                                                                                                                                                                                 |

| 12  | TESTSIG-  | I    | <b>Test Input</b> —. This input injects a test signal to the line when an appropriate test operational state is chosen. This node is active when any TEST mode is chosen, overhead is not increased per ROVH in TEST modes. Connect this node to VREF if not used.                                    |

| 13  | TESTSIG+  | I    | <b>Test Input+.</b> This input injects a test signal to the line when an appropriate test operational state is chosen. Before this node can be used, the test sense circuity must be activated via a test mode; then activate Test Input+ via the TEST-R mode. Connect this node to VREF if not used. |

| 14  | TESTLEV   | 0    | <b>Test Level Output.</b> This output pin will provide a voltage that is proportional to either the dc line voltage, dc line current, ac line voltage, ac line current, or internal reference voltage, dependent upon which operational state is selected.                                            |

| 17  | TEST+OUT  | 0    | TEST+OUT. Output of TESTSIG+ amplifier.                                                                                                                                                                                                                                                               |

| 19  | RTS       |      | Ring Trip Sense. Sense input for the ring trip detector.                                                                                                                                                                                                                                              |

| 20  | RSW       | 0    | Ring Lead Ringing Access Switch. Ringing relay connects this pin to pin RRING. Connect this pin to pin PR through a 400 $\Omega$ current-limiting resistor.                                                                                                                                           |

| 22  | RRING     | I    | <b>Ringing Access.</b> Input to solid-state ringing access switch. Connect to ringing generator.                                                                                                                                                                                                      |

| 24  | PR        | I/O  | <b>Protected Ring.</b> The output of the ring driver amplifier and input to loop sensing connected through solid-state break switch. Connect to subscriber loop through overvoltage/current protection.                                                                                               |

| 27  | PT        | I/O  | <b>Protected Tip.</b> The output of the tip driver amplifier and input to loop sensing connected through solid-state break switch. Connect to subscriber loop through overvoltage/current protection.                                                                                                 |

| 30  | TRING     | 0    | <b>Tip Ringing Return.</b> Ring relay connects this pin to PT. Connect to ringing supply return.                                                                                                                                                                                                      |

| 32  | NSTAT     | 0    | <b>Loop Status.</b> The output of the loop status detector (loop start detector wired-OR with ring trip detector). This loop status supervision output is not controlled by the data latch.                                                                                                           |

|     | В3        |      | Data Control Input. See Table 2 and Table 3 for details.                                                                                                                                                                                                                                              |

# Pin Information (continued)

Table 1. Pin Descriptions (continued)

| Pin | Symbol | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-----|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 34  | B2     | ı    | Data Control Input. See Table 2 and Table 3 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 35  | B1     | I    | Data Control Input. See Table 2 and Table 3 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 36  | В0     | I    | Data Control Input. See Table 2 and Table 3 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 38  | RESET  | ı    | Reset. A logic low will override the B[0:3] and LATCH inputs and reset the state of                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|     |        |      | the SLIC to the disconnect state and the switch to the all-off state.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 39  | LATCH  | I    | Latch Control Input. Edge-level sensitive control for data latches.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 40  | Vdd    | Р    | 5 V Digital Power Supply. 5 V supply for digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 42  | DGND   | G    | Digital Ground. Ground return for VDD current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 44  | TRGDET | 0    | <b>Tip/Ring Ground Detect.</b> When high, this open collector output indicates the presence of a ring ground or a tip ground. This supervision output may be used in ground start, ground key, or common-mode fault detection applications. It has an internal pull-up.                                                                                                                                                                                                                                                   |  |  |  |  |

| 45  | ICM    | Ι    | <b>Common-Mode Current Sense.</b> To program tip or ring ground sense threshold, connect a resistor to ground and connect a capacitor to AGND to filter 50 Hz/60 Hz. If unused, the pin is connected to ground.                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 48  | VTX    | 0    | <b>Tip/Ring Voltage Output.</b> This output is a voltage that is directly proportional differential tip/ring current. A resistor from this node to ITR sets the device trapedance. Gain shaping for termination impedance with a COMBO I codec is a achieved with a network from this node to ITR.                                                                                                                                                                                                                        |  |  |  |  |

| 49  | ITR    | _    | <b>Transmit Gain.</b> A current output that is proportional to the differential current flor from tip to ring. Input to AX amplifier. Connect a resistor from this node to VTX to transmit gain to 300 $\Omega$ . Gain shaping for termination impedance with a COMBO codec is also achieved with a network from this node to VTX.                                                                                                                                                                                        |  |  |  |  |

| 50  | TXI    | _    | <b>Transmit ac Input (Noninverting).</b> Connect a 0.1 µF capacitor from this pin to VTX for dc blocking.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 53  | VITR   | 0    | <b>Transmit ac Output Voltage.</b> The output is a voltage that is directly proportional to the differential ac tip/ring current. This output is connected via a proper interface network to the codec.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 54  | RCVP   | I    | <b>Receive ac Signal Input (Noninverting).</b> This high-impedance input controls the ac differential voltage on tip and ring.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 55  | RCVN   | I    | <b>Receive ac Signal Input (Inverting).</b> This high-impedance input controls the ac differential voltage on tip and ring.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 56  | AGND   | G    | Analog Ground. Ground return for Vcc current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 58  | Vcc    | Ρ    | <b>5 V Analog Power Supply.</b> 5 V supply for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 60  | LCTH   | I    | <b>Loop Closure Program Input.</b> Connect a voltage source or ground, via a resistor, to this point to program the loop closure threshold.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 62  | Vref   | 0    | SLIC Internal Reference Voltage. Output of internal 2.35 V SLIC reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 64  | OVH    | I    | Overhead Voltage Program Input. Connect a voltage source to this point to program the overhead voltage. Voltage source may be external or derived via a resistor divider from VREF. A programmable external voltage source may be used to provide software control of the overhead voltage. If a resistor or voltage source is not connected, the overhead voltage will default to approximately 5.5 V (sufficient to pass 3.14 dBm in to $900~\Omega$ ). If the default overhead is desired, connect this pin to ground. |  |  |  |  |

# Pin Information (continued)

Table 1. Pin Descriptions (continued)

| Pin             | Symbol | Type | Name/Function                                                                               |  |  |  |  |

|-----------------|--------|------|---------------------------------------------------------------------------------------------|--|--|--|--|

| 65              | VPROG  | ı    | Current-Limit Program Input. Connect a voltage source to this point to program              |  |  |  |  |

|                 |        |      | ne dc current limit. Voltage source may be external or derived via a resistor               |  |  |  |  |

|                 |        |      | divider from VREF. A programmable external voltage source may be used to pro-               |  |  |  |  |

|                 |        |      | vide software control of the loop closure threshold.                                        |  |  |  |  |

| 66              | CF2    | _    | <b>Filter Capacitor.</b> Connect a 0.1 µF capacitor from this node to ground for filtering. |  |  |  |  |

| 67              | CF1    | _    | Filter Capacitor. Connect a capacitor from this node to OVH to control the rate of          |  |  |  |  |

|                 |        |      | change of the overhead voltage. If controlled overhead is not desired, leave this           |  |  |  |  |

|                 |        |      | node open.                                                                                  |  |  |  |  |

| 5, 6, 11, 15,   | NC     | _    | No Connection.                                                                              |  |  |  |  |

| 16, 18, 21, 23, |        |      |                                                                                             |  |  |  |  |

| 25, 26, 28, 29, |        |      |                                                                                             |  |  |  |  |

| 31, 37, 41, 43, |        |      |                                                                                             |  |  |  |  |

| 46, 47, 51, 52, |        |      |                                                                                             |  |  |  |  |

| 57, 59, 61, 63, |        |      |                                                                                             |  |  |  |  |

| 68              |        |      |                                                                                             |  |  |  |  |

# **Operating States**

# **Input State Coding**

State control is via a tiered logic system. The device must initially be set to a primary control state (B3 = 0). This will set the operational state of the SLIC and switch. The secondary control table (B3 = 1) is used to turn on the TESTLEV+ amplifier or to turn on the test circuitry and TESTSIG— amplifier to enter a test state. The primary state of the device (the state of the SLIC and switch) will not change when entering a secondary control state.

Within the primary control table, each state will set the SLIC and the switch to a specific mode. The exception is the tip-amp and ring-amp states. The tip-amp and ring-amp states will change the configuration of the switches, but leave the state of the SLIC unchanged from the previous primary control mode.

Once a primary (device) control state is selected, the TESTSIG+ amplifier or the TESTSIG- amplifier and test circuitry can be activated via a secondary control state. Within the secondary control table, there are TEST active and TEST-R active modes. Upon entering a TEST active mode in the secondary control table, both TESTLEV output and TESTSIG- input are active and the test switches set to the appropriate condition. (See Figure 2.) An exception is the VREF test active mode. Upon entering VREF, only the TESTLEV output is active, and the internal (2.35 V typical) reference voltage appears at TESTLEV. In the VREF mode, the TESTSIG- input is deactivated.

TEST-R modes will only activate the TESTSIG+ amplifier. In order to use TESTSIG+, first enter a TEST mode to turn on the test circuit (also turns on TESTSIG-), then enter a TEST-R mode to turn on the TESTSIG+ amplifier. TEST-R mode is designed for testing of higher voltage signals such as many be seen in ringer equivalent tests.

Once TESTSIG+ is on, the user may reverse the battery in the primary state table without turning off TESTSIG+. If the user goes to scan, ring, or disconnect mode, TESTSIG+ is turned off.

Unlike TESTSIG+, the test feature, once on, will remain on if the user transitions to forward active, reverse active, scan, ring, or disconnect state in the primary state table.

TESTSIG+ is deactivated by selecting TEST off in the secondary control table.

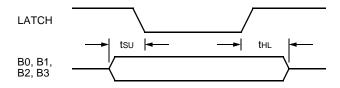

Data control is via a parallel latched data control scheme. Data latches are edge-level sensitive. Data is latched in when the LATCH control input goes low. Data must be set up 200 ns before LATCH goes low and held 50 ns after LATCH goes high. While LATCH is low, the user should not change the data control inputs at B0, B1, B2, and B3. The data control inputs at B0, B1, B2, and B3 may only be changed when LATCH is high. NSTAT supervision output is not controlled by the LATCH control input.

# Operating States (continued)

# Input State Coding (continued)

**Table 2. Primary Control States**

| В3 | B2 | B1 | В0 | RESET | State                                                           |  |

|----|----|----|----|-------|-----------------------------------------------------------------|--|

| 0  | 0  | 0  | 0  | 1     | Scan                                                            |  |

| 0  | 0  | 0  | 1  | 1     | Powerup, forward battery                                        |  |

| 0  | 0  | 1  | 0  | 1     | Powerup, reverse battery                                        |  |

| 0  | 0  | 1  | 1  | 1     | Tip and ring amp open                                           |  |

| 0  | 1  | 0  | 0  | 1     | Ring                                                            |  |

| 0  | 1  | 0  | 1  | 1     | Tip amp                                                         |  |

| 0  | 1  | 1  | 0  | 1     | Ring amp                                                        |  |

| 0  | 1  | 1  | 1  | 1     | Disconnect, break-before-make                                   |  |

| Х  | Х  | Х  | Х  | 0     | Reset—disconnect, break-before-make, and TESTLEV high impedance |  |

**Table 3. Secondary Control States**

| В3 | B2 | B1 | В0 | Туре | Active State                                |                                            | Change Test<br>Switch<br>Configuration <sup>1</sup> |  |

|----|----|----|----|------|---------------------------------------------|--------------------------------------------|-----------------------------------------------------|--|

| 1  | 0  | 0  | 0  | Test | TESTLEV, TESTSIG-                           | ESTLEV, TESTSIG- Voltage: Tip to Ring      |                                                     |  |

| 1  | 0  | 0  | 1  | Test | FESTLEV, TESTSIG- Voltage: Tip to Ground    |                                            | Y                                                   |  |

| 1  | 0  | 1  | 0  | Test | TESTLEV, TESTSIG-                           | ESTLEV, TESTSIG- Voltage: Ring to Ground   |                                                     |  |

| 1  | 0  | 1  | 1  | Test | TESTLEV, TESTSIG-                           | TESTLEV, TESTSIG— Current: Tip to Ring—VTX |                                                     |  |

| 1  | 1  | 0  | 0  | Test | TESTLEV                                     | TESTLEV Voltage: Reference—VREF            |                                                     |  |

| 1  | 1  | 0  | 1  | Test | TESTLEV, TESTSIG- Current: Tip to Ring-VITR |                                            | Y                                                   |  |

| 1  | 1  | 1  | 0  | Test | TESTLEV, TEST+OUT, TESTSIG+ TEST-R          |                                            | N                                                   |  |

| 1  | 1  | 1  | 1  | Test | TESTLEV TEST-R off                          |                                            | N                                                   |  |

<sup>1.</sup> Refer to Figure 2.

# **Table 4. Supervision Coding**

| Pin NSTAT                    | Pin TRGDET         |  |  |  |

|------------------------------|--------------------|--|--|--|

| 0 = off-hook or ring trip    | 0 = ring ground    |  |  |  |

| 1 = on-hook and no ring trip | 1 = no ring ground |  |  |  |

# State Definitions

# **Primary Control Modes**

### Powerup, Forward Battery

- Normal talk and battery feed state.

- Pin PT is positive with respect to pin PR.

- All ac transmission and dc feed circuits are powered up.

- On-hook transmission is enabled.

- Thermal shutdown is active.

- Battery window comparator sense shutdown is on.

- Switch break switches (SW1 and SW2) are closed and ring access switches (SW3 and SW4) are open.

- VBAT1 is applied to tip and ring during on-hook conditions.

- Automatic battery switch selects VBAT1 or VBAT2 during off-hook conditions.

- All supervision circuits except for ring trip detector are active.

- Overhead is set via pin OVH.

- TEST+OUT is in the high-impedance mode, and TESTSIG+ input is off unless this feature is selected via the secondary control table.

- NSTAT represents the loop closure detector status.

### Powerup, Reverse Battery

- Normal talk and battery feed state.

- Pin PR is positive with respect to pin PT.

- All ac transmission and dc feed circuits are powered up.

- On-hook transmission is enabled.

- Thermal shutdown is active.

- Battery window comparator sense shutdown is on.

- Switch break switches (SW1 and SW2) are closed, and ring access switches (SW3 and SW4) are open.

- VBAT1 is applied to tip and ring during on-hook conditions.

- Automatic battery switch selects VBAT1 or VBAT2 under off-hook conditions.

- All supervision circuits except for ring trip detector are active.

- Overhead is set via pin OVH.

- TEST+OUT is in the high-impedance mode, and TESTSIG+ input is off unless this feature is selected via the secondary control table.

- NSTAT represents the loop closure detector status.

#### Scan

- Scan clamp circuitry is active.

- Loop closure is active.

- All ac transmission, dc feed, and other supervision circuits, including ring trip, are shut down.

- Test circuitry is powered down.

- Thermal shutdown is active.

- Battery window comparator sense shutdown is on.

- On-hook transmission is disabled.

- Pin PT is positive with respect to PR, and VBAT1 is applied to tip/ring.

- Switch break switches (SW1 and SW2) are closed, and ring access switches (SW3 and SW4) are open.

- When the scan clamp circuitry is on, overhead voltage is fixed and not controlled by OVH. Also the current limit is not the normal current limit set at VPROG.

- NSTAT represents the loop closure detector status.

### **Ground Start**

- Tip amplifier is on, and the tip break switch is open.

- The device presents a high impedance (>100 kΩ) to pin PT and a current-limited battery (VBAT2) to PR.

- Common-mode current detector is on.

- Ring trip detector is off.

- Output TRGDET indicates current flowing in the ring lead.

- This is not a defined state in the primary control mode table. It is achieved via the powerup and the ring amp states in the primary control mode table.

# State Definitions (continued)

### **Primary Control Modes** (continued)

### Ringing

- Switch break switches (SW1 and SW2) are open, and ring access switches (SW3 and SW4) are closed.

- Tip/ring drive amplifiers are powered down.

- Ring trip circuit is active.

- Loop supervision and common-mode current detectors are powered down.

- NSTAT represents the ring trip detector status.

#### Disconnect—Break Before Make

- The tip and ring amplifiers are turned off to conserve power.

- Break switches (SW1 and SW2) and ring access switches (SW3 and SW4) are open. This mode is also used as a transitional mode to achieve breakbefore-make switching from the power ring to active or scan mode.

- All supervision circuits are powered down; NSTAT overrides the actual loop condition and is forced high (on-hook).

### **Tip Amp**

- The tip-side break switch is closed, and the ring-side break switch and ring access switches are open.

- SLIC mode is unaffected by reconfiguring the ring relay via this mode; therefore, SLIC will remain in the mode it was in prior to selecting this mode.

#### Ring Amp

- The ring-side break switch is closed, and the tip-side break switch and ring access switches are open.

- SLIC mode is unaffected by reconfiguring the ring relay via this mode; therefore, SLIC will remain in the mode it was in prior to selecting this mode.

### Tip and Ring Amp Open

■ The tip-side and ring-side break switches are open and the ring access switches are open.

- SLIC mode is unaffected by reconfiguring the break switches via this mode; therefore, SLIC will remain in the mode it was in prior to selecting this mode.

- This is the calibration mode for differential and single-ended tip/ring current measurements.

#### Reset

■ Selection of device reset via the RESET pin will set the device into the disconnect, break-before-make, and TESTLEV high impedance state.

# **Secondary Control Mode States**

# **Voltage: Tip to Ground**

- A voltage proportional to the tip-to-ground voltage appears at the TESTLEV output.

- TESTSIG- input is on.

#### **Voltage: Ring to Ground**

- A voltage proportional to the ring-to-ground voltage appears at the TESTLEV output.

- TESTSIG- input is on.

#### Voltage: Tip to Ring

- A voltage proportional to the differential tip-to-ring voltage appears at the TESTLEV output.

- TESTSIG- input is on.

### Current: Tip to Ring—VTX

- A voltage proportional to the ac, plus dc tip-to-ring differential current, tip-to-ground current, or ring-to-ground current appears at the TESTLEV output. Use this state for dc measurements.

- Choice is determined by primary control mode table.

- Differential current is selected by choosing powerup forward or reverse from the primary control mode table.

- Tip-to-ground or ring-to-ground current is selected by first choosing powerup forward or reverse from the primary mode table, and then choosing tip amp or ring amp from the primary mode table.

- TESTSIG- input is on.

# State Definitions (continued)

# Secondary Control Mode States (continued)

# **Current: Tip to Ring—VITR**

- A voltage proportional to the ac tip-to-ring differential current, tip-to-ground current, or ring-to-ground currents appears at TESTLEV output. Use this state for ac measurements.

- Choice is determined by primary control mode table.

- Differential current is selected by choosing powerup forward or reverse from the primary control mode table.

- Tip-to-ground current or ring-to-ground current is selected by first choosing powerup forward or reverse from the primary mode table, and then choosing tip amp or ring amp from the primary mode table.

- TESTSIG- input is on.

### Voltage: Reference—VREF

- A voltage proportional to the internal dc reference voltage (VREF) appears at the TESTLEV output.

- TESTSIG-/TESTSIG+ inputs are off.

- This is the calibration state for voltage measurements.

### TEST-R

- The TESTSIG+ input is activated.

- The TEST+OUT output is activated.

- Device mode per primary control mode table. Turn on the test sense circuitry by choosing the appropriate test state via the secondary control table. Once test sense circuitry is active, choose TEST-R to turn on TESTSIG+ amplifier.

#### **TEST-R Off**

- The TESTSIG+ input is deactivated.

- TEST+OUT is high impedance.

- Device mode is per primary control mode table.

### **Special States**

#### Thermal Shutdown

- Not controlled via truth table inputs.

- This mode is caused by excessive heating of the device, which may be encountered in an extended power cross situation.

- Upon reaching the thermal shutdown temperature, the device will enter an all-off mode.

- Upon cooling, the device will re-enter the state it was in prior to thermal shutdown.

- Hysteresis is built in to prevent oscillation. In this mode, supervision output NSTAT is forced low (off-hook) regardless of loop status or if the disconnect logic state is selected.

### **Battery Out of Range**

- Not controlled via truth table inputs.

- This mode is caused by a battery out of range; that is, the battery voltage rising above or below a specified threshold.

- Upon reaching the specified high or low battery voltage, the device will enter an all-off mode.

- Upon the battery returning to the specified normal operating range, the device will re-enter the state it was in prior to the low battery shutdown.

- Hysteresis is built in to prevent oscillation. In this mode, supervision output NSTAT is forced low (off-hook) regardless of loop status or if the disconnect logic state is selected.

# **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

### **Table 5. Absolute Maximum Ratings**

TA = 25 °C.

| Parameter                               | Symbol | Min             | Max            | Unit |

|-----------------------------------------|--------|-----------------|----------------|------|

| 5 V dc Supplies (Vcc + Vdd)             | _      | -0.5            | 7.0            | V    |

| High Office Battery Supply (VBAT1)      | _      | <del>-</del> 75 | 0.5            | V    |

| Auxiliary Office Battery Supply (VBAT2) | _      | _               | VBAT1 to 0.5 V | V    |

| Ringing Voltage                         | _      | _               | 110            | Vrms |

| Logic Input Voltage                     | _      | -0.5            | Vcc + 0.5 V    | V    |

| Maximum Junction Temperature            | _      | _               | 165            | °C   |

| Storage Temperature Range               | _      | -40             | 125            | °C   |

| Relative Humidity Range                 | _      | 5               | 95             | %    |

| Switch 1, 2, 3; Pole to Pole            | _      | _               | 320            | V    |

| Switch 4; Pole to Pole                  | _      | _               | 465            | V    |

| Switch Input to Output                  | _      | _               | 320            | V    |

Note: The IC can be damaged unless all ground connections are applied before, and removed after, all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds the device ratings. For example, inductance in a supply lead could resonate with the supply filter capacitor to cause a destructive overvoltage.

# **Electrical Characteristics**

In general, minimum and maximum values are testing requirements. However, some parameters may not be tested in production because they are guaranteed by design and device characterization. Typical values reflect the design center or nominal value of the parameter; they are for information only and are not a requirement. Minimum and maximum values apply across the entire temperature range (-40 °C to +85 °C) and entire battery range (-36 V to -70 V). Unless otherwise specified, typical is defined as 25 °C, Vcc = Vdd = 5.0, VBAT1 = -48 V VBAT2 = -25 V. Positive currents flow into the device.

**Table 6. Device Operating Conditions and Powering**

| Parameter                                                                                                                                   | Min      | Тур                    | Max                 | Unit                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|---------------------|----------------------|

| Temperature Range                                                                                                                           | -40      | _                      | 85                  | °C                   |

| Humidity Range                                                                                                                              | 5        | _                      | 95 <sup>1</sup>     | %RH                  |

| VBAT1 Operational Range                                                                                                                     | -36      | -48                    | -72                 | V                    |

| VBAT2 Operational Range                                                                                                                     | -19      | -25                    | VBAT1               | V                    |

| 5 V dc Supplies (Vcc, Vdd)                                                                                                                  | 4.75     | 5.0                    | 5.25                | V                    |

| Supply Currents, Scan State  No Loop Current, VBAT = -48 V, VCC = VDD = 5 V:  IVCC+VDD                                                      |          | 2                      | 2.5                 | m Λ                  |

| IVEC+VDD                                                                                                                                    |          | 2<br>100               | 2.5<br>200          | mΑ<br>μΑ             |

| Power Dissipation                                                                                                                           |          | 15                     | 200                 | μΑ<br>mW             |

| Supply Currents, Forward/Reverse Active State  No Loop Current, with On-hook Transmission, Test Not Active,  VBAT = -48 V, VCC = VDD = 5 V: |          |                        |                     |                      |

| IVCC+VDD                                                                                                                                    | _        | 6                      | 6.5                 | mA                   |

| IVBAT1                                                                                                                                      | _        | 1.1                    | 1.4                 | mA                   |

| Power Dissipation                                                                                                                           | _        | 83                     | 100                 | mW                   |

| Supply Currents, Forward Disconnect State, VBAT = -48 V, VCC = VDD = 5 V:    VCC+VDD                                                        | _<br>_   | 1.2<br>20<br>7         | 1.85<br>275<br>22.5 | mΑ<br>μΑ<br>mW       |

| Supply Currents, Ring State, No Loop Current,  VBAT = -48 V, VCC = VDD = 5 V, VRING = 80 Vrms:                                              |          |                        |                     |                      |

| IVCC+VDD IVBAT1 IRING Generator Power Dissipation                                                                                           |          | 5<br>200<br>1.5<br>155 | _<br>_<br>_<br>_    | mΑ<br>μΑ<br>mΑ<br>mW |

| Power Adders, Vcc = Vdd = 5 V, Power Test Amplifiers Drawn Only from 5 V Supply: TESTSIG+ TESTSIG-                                          |          | 1 5                    |                     | mW<br>mW             |

| PSRR 500 Hz—3000 Hz: VBAT1, VBAT2 VCC                                                                                                       | 45<br>30 | <u> </u>               | <u> </u>            | dB<br>dB             |

<sup>1.</sup> Not to exceed 26 grams of water per kilogram of dry air.

# **Package Thermal Characteristics**

### Table 7. Thermal

| Parameter                                                                                     | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Thermal Protection Shutdown (TTSD) <sup>1, 2</sup>                                            | 150 | 165 | _   | °C   |

| Thermal Resistance, Junction to Ambient (⊖JA) <sup>1, 3</sup> : Natural Convection 1S2P Board | _   | 17  | _   | °C/W |

- 1. This parameter is not tested in production. It is guaranteed by design and device characterization.

- Careful thermal design as a function of maximum battery, loop length, maximum ambient temperature packages, thermal resistance, airflow, PCB board layers, and other related parameters must ensure that thermal shutdown temperature is not exceeded under normal use conditions

- 3. Airflow, PCB board layers, and other factors can greatly affect this parameter.

# **Ring Trip Detector**

**Table 8. Ring Trip Detector**

| Parameter                                                                                  | Min               | Тур          | Max              | Unit            |

|--------------------------------------------------------------------------------------------|-------------------|--------------|------------------|-----------------|

| Voltage at Input that Will Cause Ring Trip After Appropriate Zero Crossings                | ±2.0              | ±2.4         | ±2.8             | V               |

| Voltage at Input that Will Cause Immediate Ring Trip                                       | ±12               | ±15          | ±18              | V               |

| Ringing Source <sup>1</sup> : Frequency (f) dc Voltage ac Voltage                          | 19<br>-39.5<br>60 | 20<br>—<br>— | 28<br>-57<br>105 | Hz<br>V<br>Vrms |

| Ring Trip (NDET = 0) <sup>2</sup> , <sup>3</sup> :  Loop Resistance  Trip Time  NDET Valid | 2000<br>—<br>—    | _<br>_<br>_  | <br>200<br>80    | Ω<br>ms<br>ms   |

<sup>1.</sup> The ringing source may be either of the following:

The ringing source consists of the ac and dc voltages added together (battery-backed ringing); the ringing return is ground. The ringing source consists of only the ac voltage (earth-backed ringing); the ringing return is the dc voltage.

<sup>2.</sup> NDET must also indicate ring trip when the ac ringing voltage is absent (<5 Vrms) from the ringing source.

<sup>3.</sup> Pretrip ringing must not be tripped by a 10 k $\Omega$  resistor in parallel with an 8  $\mu$ F capacitor applied across tip and ring.

### **Test**