# LCK4973V Low-Voltage PLL Clock Driver

#### **Features**

- Fully integrated PLL.

- Compatible with *PowerPC*® and *Pentium*® microprocessors.

- 52-pin TQFPT.

- 3.3 V power supply.

- Pin compatible with *Motorola* ® MPC973, CY7BZ9973V, and P16C2973V.

- Selectable 1 differential PECL pair or 2 singleended TTL inputs

- 2.5 MHz—200 MHz output operation.

- Output-to-output skews <350 ps.

- Total timing budget <800 ps.

- Less than 100 ps typical cycle-to-cycle jitter.

### **Description**

Agere Systems Inc.'s LCK4973V is a 3.3 V PLL-based clock driver for high-performance RISC or CISC processor based systems. The LCK4973V has output frequencies of 2.5 MHz—200 MHz and skews of <350 ps, making it ideal for synchronous systems. The LCK4973V contains 12 low-skew outputs which provide selectable frequency ratios of 1:1, 2:1, 3:1, 3:2, 4:3, 5:1, 5:2, 5:3, 6:1, and 6:5 between outputs.

There is an additional feedback output provided to enable the PLL to multiply the external frequency by 4, 6, 8, 10, 12, 16, or 20.

The outputs can each drive 50  $\Omega$  transmission lines; series terminated lines have the ability of driving two 50  $\Omega$  lines in parallel, effectively doubling the fan out.

A total timing budget feature is added to provide the maximum error from REFCLK to any of the outputs.

### **Pin Information**

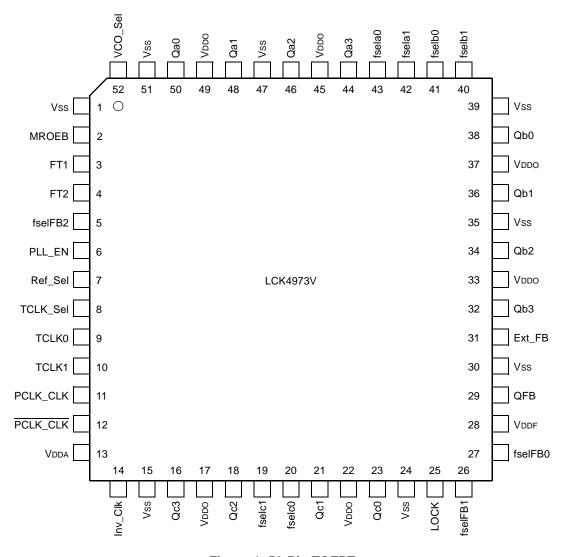

## **Pin Diagram**

Figure 1. 52-Pin TQFPT

# Pin Information (continued)

# **Pin Descriptions**

**Table 1. Pin Descriptions**

| Pin                                    | Symbol    | Туре   | I/O | Description                                                                                                                                                                                                                                    |

|----------------------------------------|-----------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 15,<br>24, 30,<br>35, 39,<br>47, 51 | Vss       | Ground | _   | PLL Ground.                                                                                                                                                                                                                                    |

| 2                                      | MROEB     | LVTTL  | I   | Master Reset and Output Enable Input.  Note: When MR/OE is set high, the PLL will have been disturbed and the outputs will be at an indeterminate frequency until it is relocked.                                                              |

| 3, 4                                   | FT[1:2]   | LVTTL  | I   | Factory Test Mode. When PLL_EN is high, these inputs are ignored and may be set to any logic level or left open.                                                                                                                               |

| 5                                      | fselFB2   | LVTTL  | I   | <b>Feedback Output Divider Function Select.</b> This input, along with pins fselFB0 and fselFB1, controls the divider function of the feedback bank of outputs. See Table 3 for more details.                                                  |

| 6                                      | PLL_EN    | LVTTL  | I   | <ul> <li>PLL Bypass Select.</li> <li>0 = The internal PLL is bypassed and the selected reference input provides the clocks to operate the device.</li> <li>1 = The internal PLL provides the internal clocks to operate the device.</li> </ul> |

| 7                                      | Ref_Sel   | LVTTL  | -   | Reference Select Input. The Ref_Sel input controls the reference input to the PLL.  0 = The input is selected by the TCLK_Sel input.  1 = The PCLK_CLK is selected.                                                                            |

| 8                                      | TCLK_Sel  | LVTTL  | -   | TTL Clock Select Input. The TCLK_Sel input controls which TCLK input will be used as the reference input if Ref_Sel is set to 0. 0 = TCLK0 is selected. 1 = TCLK1 is selected.                                                                 |

| 9, 10                                  | TCLK[0:1] | LVTTL  | I   | LVTLL Reference Input. These inputs provide the reference frequency for the internal PLL when selected by Ref_Sel and TCLK_Sel.                                                                                                                |

| 11                                     | PCLK_CLK  | LVTTL  | I   | <b>Differential Reference Input.</b> This low-voltage differential PECL input provides the reference frequency for the internal PLL when selected by Ref_Sel.                                                                                  |

| 12                                     | PCLK_CLK  | LVTTL  | I   | <b>Differential Reference Input.</b> This low-voltage differential PECL input provides the reference frequency for the internal PLL when selected by Ref_Sel.                                                                                  |

| 13                                     | Vdda      | Power  | _   | PLL Power.                                                                                                                                                                                                                                     |

| 14                                     | Inv_Clk   | LVTTL  | I   | Invert Mode. This input only affects the Qc bank.  0 = All outputs of the Qc bank are in the normal phase alignment.  1 = Qc2 and Qc3 are inverted from the normal phase of Qc0 and Qc1.                                                       |

| 16, 18,<br>21, 23                      | Qc[3:0]   | LVTTL  | 0   | <b>Clock Output.</b> These outputs, along with the Qa[0:3], Qb[0:3], and QFB outputs, provide numerous divide functions determined by the fsela[0:3], fselb[0:3], and the fselFB[0:2] See Table 2 and Table 3 for more details.                |

| 17, 22,<br>33, 37,<br>45, 49           | VDDO      | Power  | _   | Output Buffer Power.                                                                                                                                                                                                                           |

# Pin Information (continued)

## Pin Descriptions (continued)

Table 1. Pin Descriptions (continued)

| Pin               | Symbol     | Туре  | I/O | Description                                                                                                                                                                                                                                                                                                                          |

|-------------------|------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19, 20            | fselc[1:0] | LVTTL | I   | Output Divider Function Select. Each pair controls the divider function of the respective bank of outputs. See Table 2 for more details.                                                                                                                                                                                             |

| 25                | LOCK       | LVTTL | 0   | PLL Lock Indicator.  0 = The PLL is attempting to acquire lock.  1 = This output indicates that the internal PLL is locked to the reference signal.                                                                                                                                                                                  |

|                   |            |       |     | Note: If there is no activity on the selected reference input, LOCK may not accurately reflect the state of the internal PLL. This pin will drive logic, but not Thevenin terminated transmission lines. It is always active and does not go to a high impedance state. LOCK provides TEST MODE information when PLL_EN is set to 0. |

| 26                | fselFB1    | LVTTL | I   | <b>Feedback Output Divider Function Select.</b> This input, along with pins fselFB1 and fselFB2, controls the divider function of the feedback bank of outputs. See Table 3 for more details.                                                                                                                                        |

| 27                | fselFB0    | LVTTL | _   | <b>Feedback Output Divider Function Select.</b> This input, along with pins fselFB0 and fselFB2, controls the divider function of the feedback bank of outputs. See Table 3 for more details.                                                                                                                                        |

| 28                | VDDF       | Power | _   | PLL Power.                                                                                                                                                                                                                                                                                                                           |

| 29                | QFB        | LVTTL | 0   | <b>Clock Output.</b> This output, along with the Qa[0:3] and Qc[0:3] outputs, provide numerous divide functions determined by the fsela[0:3], fselb[0:3], and the fselFB[0:2]. See Table 2 and Table 3 for more details.                                                                                                             |

| 31                | Ext_FB     | LVTTL | I   | PLL Feedback Input. This input is used to connect one of the clock outputs (usually QFB) to the feedback input of the PLL.                                                                                                                                                                                                           |

| 32, 34,<br>36, 38 | Qb[3:0]    | LVTTL | 0   | <b>Clock Output.</b> These outputs, along with the Qa[0:3], Qc[0:3], and QFB outputs, provide numerous divide functions determined by the fsela[0:3], fselb[0:3], and the fselFB[0:2]. See Table 2 and Table 3 for more details.                                                                                                     |

| 40, 41            | fselb[1:0] | LVTTL | I   | Output Divider Function Select. Each pair controls the divider function of the respective bank of outputs. See Table 2 for more details.                                                                                                                                                                                             |

| 42, 43            | fsela[1:0] | LVTTL | I   | Output Divider Function Select. Each pair controls the divider function of the respective bank of outputs. See Table 2 for more details.                                                                                                                                                                                             |

| 44, 46,<br>48, 50 | Qa[3:0]    | LVTTL | 0   | <b>Clock Output.</b> These outputs, along with the Qb[0:3], Qc[0:3] and QFB outputs, provide numerous divide functions determined by the fsela[0:3], fselb[0:3], and the fselFB[0:2]. See Table 2 and Table 3 for more details.                                                                                                      |

| 52                | VCO_Sel    | LVTTL | I   | Vco Frequency Select Input. This input selects the nominal operating range of the Vco used in the PLL.  0 = The Vco range is 100 MHz—240 MHz.  1 = The Vco range is 200 MHz—480 MHz.                                                                                                                                                 |

# **Functional Description**

Table 2. Function Table for Qa, Qb, and Qc

| fsela1 | fsela0 | Qa  | fselb1 | fselb0 | Qb  | fselc1 | fselc0 | Qc |

|--------|--------|-----|--------|--------|-----|--------|--------|----|

| 0      | 0      | ÷4  | 0      | 0      | ÷4  | 0      | 0      | ÷2 |

| 0      | 1      | ÷6  | 0      | 1      | ÷6  | 0      | 1      | ÷4 |

| 1      | 0      | ÷8  | 1      | 0      | ÷8  | 1      | 0      | ÷6 |

| 1      | 1      | ÷12 | 1      | 1      | ÷10 | 1      | 1      | ÷8 |

**Table 3. Function Table for QFB**

| fselFB2 | fselFB1 | fselFB0 | QFB |

|---------|---------|---------|-----|

| 0       | 0       | 0       | ÷4  |

| 0       | 0       | 1       | ÷6  |

| 0       | 1       | 0       | ÷8  |

| 0       | 1       | 1       | ÷10 |

| 1       | 0       | 0       | ÷8  |

| 1       | 0       | 1       | ÷12 |

| 1       | 1       | 0       | ÷16 |

| 1       | 1       | 1       | ÷20 |

**Table 4. Function Table for Logic Selection**

| Control Pin | Logic 0                    | Logic 1           |

|-------------|----------------------------|-------------------|

| VCO_Sel     | VCO/2                      | VCO               |

| Ref_Sel     | TCLK                       | PECL              |

| TCLK_Sel    | TCLK0                      | TCLK1             |

| PLL_EN      | Bypass PLL                 | Enable PLL        |

| MR/OE       | Master Reset/Output High-Z | Enable Outputs    |

| Inv_Clk     | Noninverted Qc2, Qc3       | Inverted Qc2, Qc3 |

# Functional Description (continued)

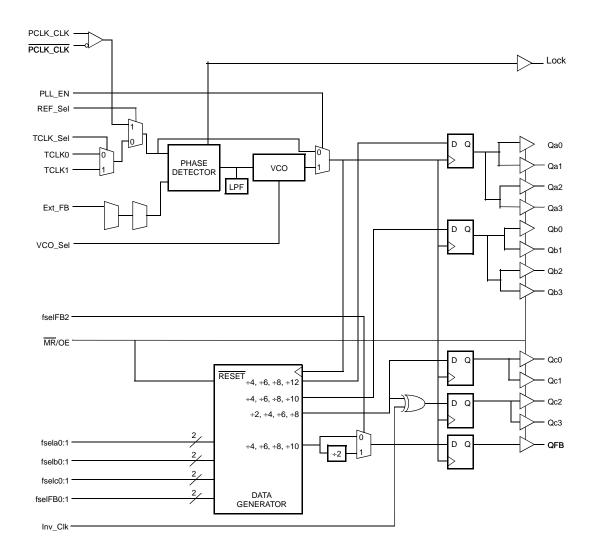

2332.b (F)

Figure 2. LCK4973V Logic Diagram

### **Absolute Maximum Ratings**

Stresses which exceed the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods of time can adversely affect device reliability.

**Table 5. Absolute Maximum Ratings**

| Parameter                         | Symbol | Min  | Max       | Unit |

|-----------------------------------|--------|------|-----------|------|

| Supply Voltage                    | VDD    | -0.5 | 4.6       | V    |

| Input Voltage                     | Vı     | -0.3 | VDD + 0.5 | V    |

| Input Current                     | lin    | _    | ±20       | mA   |

| Storage Temperature Range         | Tstg   | -40  | 125       | °C   |

| Ambient Temperature               | TA     | -40  | 125       | °C   |

| Output Current Into Outputs (Low) | lout   | _    | 40        | mA   |

| Latch-up Current                  | IL     | _    | ±200      | mA   |

### **Recommended Operating Conditions**

**Table 6. Recommended Operating Conditions**

| Range      | Ambient Temperature | VDD         |

|------------|---------------------|-------------|

| Commercial | 0 °C to 70 °C       | 3.3 V ± 10% |

| Industrial | −40 °C to 85 °C     | 3.3 V ± 10% |

## **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Agere Systems employs a human-body model (HBM) and charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used in the defined model. No industrywide standard has been adopted for the CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes.

**Table 7. Handling Precautions**

| Device   | Voltage  | Туре                          |  |  |

|----------|----------|-------------------------------|--|--|

| LCK4973V | >2,000 V | ESD (electrostatic discharge) |  |  |

### **Electrical Characteristics**

#### **Table 8. PLL Input Reference Characteristics**

TA = 0 °C to 70 °C, VDD =  $3.3 \text{ V} \pm 10\%$ .

| Parameter                  | Symbol | Condition | Min | Max | Unit |

|----------------------------|--------|-----------|-----|-----|------|

| TCLK Input Rise/Fall       | tr, tf | _1        | _   | 3.0 | ns   |

| Reference Input Frequency  | fref   | _         | 2.5 | 120 | MHz  |

| Reference Input Duty Cycle | trefDC | _         | 25  | 75  | %    |

<sup>1.</sup> Tested initially and after any design or process changes that may affect these parameters.

#### dc Characteristics

#### **Table 9. dc Characteristics**

TA = 0 °C to 70 °C, VDD =  $3.3 \text{ V} \pm 5\%$

| Parameter                                                       | Symbol | Condition                                                    | Min        | Тур | Max        | Unit |

|-----------------------------------------------------------------|--------|--------------------------------------------------------------|------------|-----|------------|------|

| Input High Voltage                                              | VIH    | _                                                            | 2.0        | _   | 3.6        | V    |

| Input Low Voltage                                               | VIL    | _                                                            | _          | _   | 0.8        | V    |

| Peak-to-Peak Input Voltage PCLK_CLK                             | Vp-p   | _                                                            | 400        | _   | Vdd        | mV   |

| Common Mode Voltage Range (crossing) PCLK_CLK                   | VCMR   | _1                                                           | 8.0        | _   | VDD        | V    |

| Output High Voltage: All Q Outputs LOCK Outputs                 | Voн    | $IOH = -20 \text{ mA}^2$<br>$IOH = -20 \text{ mA}^2$         | 2.4<br>2.4 | _   |            | ٧    |

| Output Low Voltage: All Q Outputs LOCK Outputs                  | Vol    | IOL = 20 mA<br>IOL = 20 mA                                   | _          | _   | 0.5<br>0.5 | V    |

| Input Current <sup>3</sup>                                      | lin    | All control inputs<br>Vss < VIN < VDD                        | _          | _   | ±120       | μΑ   |

|                                                                 |        | PCLK_CLK and TCLK[0:1]<br>Vss < VIN < VDD                    | _          | _   | ±500       |      |

| Hot Insertion Input Current                                     | lı     | PCLK_CLK and TCLK[0:1]<br>VIN ≤ 3.63 V<br>VDD = VSS          | _          | _   | 100        | μA   |

| Maximum Quiescent Supply Current                                | Iccq   | Sum all VDD pins PLL_EN = 0 reference off                    | _          | 50  | 150        | mA   |

| Maximum Dynamic Supply Current (neglecting output load current) | ICCD   | Outputs unloaded<br>fselFB = 010(÷8)<br>reference = 12.5 MHz | _          | 237 | 270        | mA   |

| Output Dynamic Supply Current                                   | ICCN   | _                                                            | _          | _   | 8.6        | mA   |

| Input Capacitance                                               | CIN    | _                                                            |            | _   | 4          | pF   |

<sup>1.</sup> VCMR is the difference taken form the most positive side of the differential input signal. The high input within the VCMR range and the input lying within the Vp-p specification designates normal operation.

<sup>3.</sup> The LCK4973V inputs can drive series of parallel terminated transmission lines on the incident edge.

<sup>3.</sup> Inputs have pull-up/pull-down resistors which affect input current.

### **Electrical Characteristics** (continued)

### ac Characteristics

Table 10. ac Characteristics

| Parameter                                                                   | Symbol        | Condition                   | Min            | Тур                | Max            | Unit |

|-----------------------------------------------------------------------------|---------------|-----------------------------|----------------|--------------------|----------------|------|

| Output Rise Time                                                            | tr            | 0.8 V to 2.0 V <sup>1</sup> | 0.15           | _                  | 1.2            | ns   |

| Output Fall Time                                                            | tf            | 2.0 V to 0.8 V <sup>1</sup> | 0.15           | _                  | 1.2            | ns   |

| Output Duty Cycle                                                           | tpw           | 2, 3                        | tcycle/2 - 500 | $tCYCLE/2 \pm 400$ | tCYCLE/2 + 500 | ps   |

| Propagation Delay (selected reference input rise to Ext_FB rise):  QFB = ÷8 | tpd           | 3, 4                        | -200           | _                  | 200            | ps   |

| Output-to-Output Skews                                                      | tskew         | 3, 5                        | _              | _                  | 350            | ps   |

| PLL Vco Lock Range                                                          | fvco          | _                           | 200            | _                  | 480            | MHz  |

| Maximum Output Frequency                                                    | fmax          | _                           | _              | _                  | 200            | MHz  |

| Cycle-to-Cycle Jitter (peak-to-peak)                                        | tjitter       | _                           | _              | _                  | 125            | ps   |

| Output Disable Time                                                         | tOLZ,<br>tOHZ | _                           | 1              | _                  | 10             | ns   |

| Output Enable Time                                                          | tozl,<br>tozh | _                           | 0.5            | _                  | 14             | ns   |

| Maximum PLL Lock Time                                                       | tlock         |                             |                |                    | 10             | ms   |

| Total Timing Budget                                                         | TTB           | 6                           | _              | _                  | 800            | ps   |

<sup>1</sup> Measured no load.

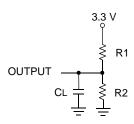

#### ac Test Loads

For LOCK output only:

■ R1 = 910  $\Omega$ , R2 = 910  $\Omega$ , CL < 30 pF.

For all other outputs:

■ R1 = 100  $\Omega$ , R2 = 100  $\Omega$ , CL < 25 pF or 10 pF connected to output pin.

Figure 3. LVTTL ac Test Load

<sup>2</sup> tPW measured at VDD/2.

<sup>3 50</sup>  $\Omega$  transmission line terminated with VDD/2.

<sup>4</sup> tPD specified for 50 MHz reference.

<sup>5</sup> All outputs at same frequency.

<sup>6</sup> tpd + tSKEW + tjitter = TTB.

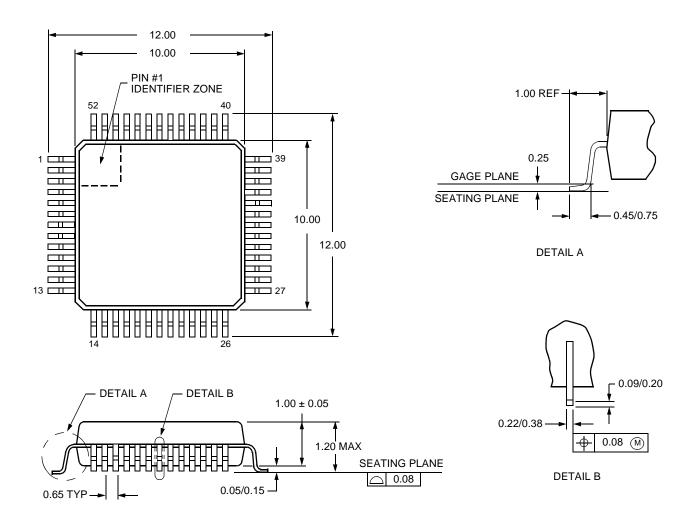

### **Outline Diagram**

52-pin TQFPT package outline. All dimensions are in millimeters.

PowerPC is a registered trademark of International Business Machines Corporation. Pentium is a registered trademark of Intel Corporation. Motorola is a registered trademark of Motorola, Inc.

For additional information, contact your Agere Systems Account Manager or the following: INTERNET: http://www.agere.com

E-MAIL: docmaster@agere.com

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 N. AMERICA:

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA: Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020 CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 6778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

**EUROPE:** Tel. (44) 7000 624624, FAX (44) 1344 488 045

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.