THE INFINITE POWER OF INNOVATION

# LX1570/1571

PHASE MODULATED AC SYNCHRONOUS SECONDARY-SIDE CONTROLLER

PRELIMINARY DATA SHEET

## DESCRIPTION

The LX1570/71 series of controller ICs are designed to provide all control functions in a secondary-side regulator for isolated auxiliary or secondary power supplies. Auxiliary or secondary-side controllers are used in a variety of applications including multiple output off-line power supplies, commonly found in desktop computers, as well as telecommunications applications. Although they can be used in all secondary output applications requiring precision regulation, they are mainly optimized for outputs delivering more than 3A current where standard three-terminal regulators lack the desired efficiency. For these applications, the Mag Amp regulators have traditionally been used. However, Mag Amps have several disadvantages. First, because they have to withstand the maximum input voltage during a short-circuit condition, they are "over designed", typically by 2 times. increasing the cost and size of the power supply. Second, Mag Amps are inherently leading edge modulators, so they can only

approach a certain maximum duty cycle, limited by the minimum delay and the magnetic BH loop characteristic of the Mag Amp core. This forces an increase in the size of the main transformer as well as the output inductor, resulting in higher overall system cost. The LX1570/71 eliminates all the disadvantages of the Mag Amp approach as well as improving system performance and reducing overall system cost.

The LX1570/71 is a current mode controller IC that controls the duty cycle of a switch in series with the secondary AC output of the power transformer in buck-derived applications, such as forward or bridge topologies. It offers features such as 100% duty cycle operation for maximum energy transfer, pulse-by-pulse and hiccup current limiting with long off-time between the cycles for reduced power dissipation, high-frequency operation for smaller magnetics, soft-start, and current mode control for excellent dynamic response.

## **KEY FEATURES**

- REPLACES COSTLY MAG-AMP CORES WITH A LOW ON-RESISTANCE MOSFET

- □ LOOK-AHEAD SWITCHING™ ENSURES SWITCH TURN ON BEFORE THE AC INPUT TO ACHIEVE 100% ENERGY TRANSFER

- LOWER OVERALL SYSTEM COST

- LOWER PEAK CURRENT STRESS ON THE PRIMARY SWITCH

- ALLOWS HIGHER OPERATING FREQUENCY AND SMALLER OUTPUT INDUCTOR

- EASY SHORT-CIRCUIT PROTECTION

- ☐ CURRENT MODE APPROACH ACHIEVES EXCELLENT DYNAMIC RESPONSE

#### **APPLICATIONS**

- SECONDARY-SIDE REGULATOR IN OFF-LINE POWER SUPPLIES

- COMPUTER POWER SUPPLIES, 3.3V OUTPUT FOR NEW LOW-VOLTAGE PROCESSORS AND MEMORIES

- TELECOMMUNICATION AND MILITARY DC/DC CONVERTERS

## PRODUCT HIGHLIGHT

AVAILABLE OPTIONS PER PART #

| Part # | C.L.<br>Threshold | C.S.<br>Option                    | Application                |  |  |

|--------|-------------------|-----------------------------------|----------------------------|--|--|

| LX1570 | -0.2V             | Resistive<br>Sensing              | Output<br>Currents<br>< 4A |  |  |

| LX1571 | 1V                | Current<br>Transformer<br>Sensing | Output<br>Currents<br>> 4A |  |  |

|                     |                        | DER INFORMAT             | ION                    |

|---------------------|------------------------|--------------------------|------------------------|

| T <sub>A</sub> (°C) | M Plastic DIP<br>8-pin | DM Plastic SOIC<br>8-pin | Y Ceramic DIP<br>8-pin |

| 0 to 70             | LX157xCM               | LX157xCDM                | _                      |

| -40 to 85           | LX157xIM               | LX157xIDM                | _                      |

| -55 to 125          | _                      | _                        | LX157xMY               |

Note: All surface-mount packages are available in Tape & Reel. Append the letter "T" to part number. (i.e. LX157xCDMT)

## Preliminary Data Sheet

## ABSOLUTE MAXIMUM RATINGS Digital Inputs .....-0.3 to 7V Note 1. Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal. THERMAL DATA M PACKAGE: THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta$ 95°C/W DM PACKAGE: THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{i,i}$ 165°C/W **Y PACKAGE:**

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ . The  $\theta_{IA}$  numbers are guidelines for the thermal performance of the device/pc-board system.

THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{LA}$

All of the above assume no ambient airflow.

## PACKAGE PIN OUTS S.S. □ COMP ☐ OUT DRV GND C.S. M & Y PACKAGE (Top View) S.S. V<sub>FB</sub> $\square$ 7 🖽 **V**" COMP I 6 DOUT DRV 5 GND C.S. DM PACKAGE (Top View)

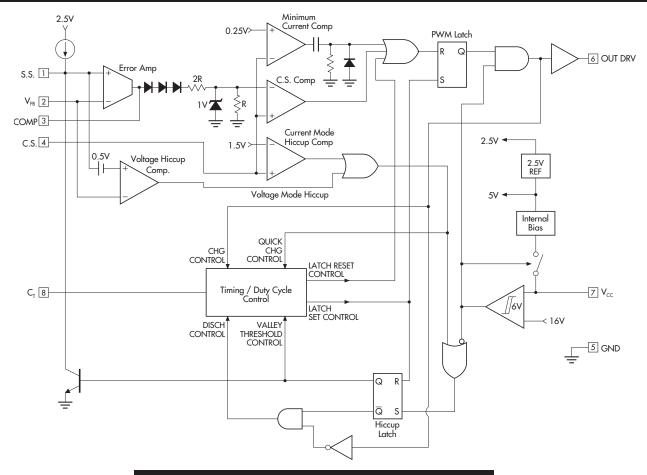

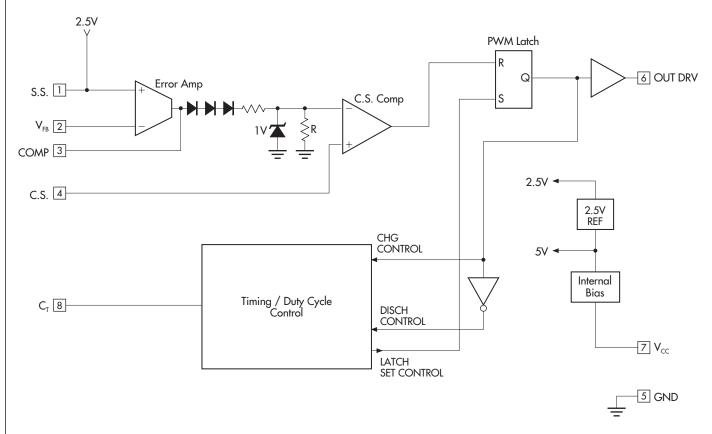

## LX1571 BLOCK DIAGRAM

130°C/W

## PRELIMINARY DATA SHEET

## **ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified, these specifications apply over the ranges  $T_A$  = -55 to 125°C for the LX1570M/1571M,  $T_A$  = -40 to 85°C for the LX1570I/1571I, and  $T_A$  = 0 to 70°C for LX1570C/1571C.  $V_{CC}$  = 15V. Typ. number represents  $T_A$  = 25°C value.)

| Parameter                             |        | Symbol                | Test Conditions                                       | LX1570/1571  Min. Typ. Max. |       |       |       |

|---------------------------------------|--------|-----------------------|-------------------------------------------------------|-----------------------------|-------|-------|-------|

| Reference Section                     |        |                       |                                                       | Willt                       | Тур.  | Max.  |       |

| Initial Accuracy                      |        | V <sub>RI</sub>       | T <sub>A</sub> = 25°C, measured at F.B pin            | 2.475                       | 2.500 | 2.525 | V     |

| Line Regulation                       |        | $\Delta V_{RL}$       | 11V < V <sub>cc</sub> < 25                            |                             |       | ±1    | %     |

| Temp Stability                        |        | $\Delta V_{RT}$       | Note 2                                                |                             |       | ±1.5  | %     |

| Timing Section                        |        | I KI                  |                                                       |                             |       |       |       |

| Initial Accuracy                      |        | f <sub>o</sub>        | $C_T = T_1 = 25$ °C, measured at pin 6                | 90                          | 100   | 110   | kHz   |

|                                       |        |                       | Over Temp, measured at pin 6                          | 85                          | 100   | 115   | kHz   |

| Line Voltage Stability                |        | $\Delta f_{OL}$       |                                                       |                             |       | ±1    | %     |

| Charging Current                      |        | I <sub>CHG</sub>      |                                                       |                             | 3     |       | mA    |

| Discharging Current                   |        | I <sub>DISCH</sub>    |                                                       |                             | 3.5   |       | mA    |

| Leakage Current                       |        | I <sub>LK</sub>       | C.S. <sub>INPUT</sub> = 1.5V                          |                             | 4     |       | μA    |

| Ramp PK to PK                         |        | V <sub>RPP</sub>      | C.S. <sub>INPUT</sub> = 0V                            |                             | 0.6   |       | ٧     |

|                                       |        |                       | $C.S{INPUT} = 1.5V (1571), C.S{INPUT} = -0.4V (1570)$ |                             | 6     |       | ٧     |

| Error Amp / Soft Start Comp Sect      | ion    |                       |                                                       |                             |       |       |       |

| Transconductance                      |        | S <sub>m</sub>        |                                                       |                             | 0.005 |       | μΩ    |

| Input Bias Current                    |        |                       |                                                       |                             | 0.1   | 1     | μΑ    |

| Open Loop Gain                        |        |                       |                                                       | 60                          | 70    |       | dB    |

| Output Sink Current                   |        |                       | $V_{FB} = 2.6V$                                       | 200                         | 400   |       | μA    |

| Output Source Current                 |        | L <sub>EA(SINK)</sub> | $V_{FB} = 2.4V$                                       | 200                         | 400   |       | μΑ    |

| Output HI Voltage                     |        | V <sub>COMP-HI</sub>  |                                                       |                             | 5.1   |       | ٧     |

| Output LO Voltage                     |        | V <sub>COMP-LO</sub>  |                                                       |                             |       | 0.8   | ٧     |

| Slew Rate                             |        | S                     |                                                       |                             | 1     |       | V/µSe |

| Soft-Start Section                    |        |                       |                                                       |                             |       |       |       |

| Soft Start Timing Factor              |        | K <sub>ss</sub>       |                                                       | 35                          | 50    | 65    | ms/µl |

| Soft Start Discharge Current          |        | I <sub>SS-DIS</sub>   |                                                       |                             | TBD   |       | mA    |

| Current Sense Section                 |        |                       |                                                       |                             |       |       |       |

| Input Range                           | LX1570 | V <sub>csi</sub>      |                                                       |                             |       | -0.8  | ٧     |

|                                       | LX1571 |                       |                                                       | -0.3                        |       | 6     | ٧     |

| Input Current                         | LX1570 | I <sub>CSB</sub>      |                                                       |                             |       | 25    | μΑ    |

|                                       | LX1571 |                       |                                                       |                             |       | 1     | μΑ    |

| C.S. Amplifier Gain                   | LX1570 | A <sub>cs</sub>       |                                                       | -13.5                       | -15   | -16.5 | V/V   |

|                                       | LX1571 |                       |                                                       | 2.7                         | 3     | 3.3   | V/V   |

| Minimum Current Threshold Voltage     | LX1570 | V <sub>CSMIN</sub>    |                                                       |                             | -50   |       | m۷    |

| LX1571                                |        |                       |                                                       |                             | 250   |       | m۷    |

| C.S. Delay to Driver Output           |        |                       | 10% Overdrive                                         |                             | 100   | 200   | ns    |

| C.L. Pulse-By-Pulse Threshold Voltage | LX1570 | V <sub>CLP</sub>      |                                                       | -0.18                       | -0.2  | -0.22 | ٧     |

|                                       | LX1571 | 1                     |                                                       | 0.9                         | 1     | 1.1   | ٧     |

| C.L. Hiccup Threshold Voltage         | LX1570 | V <sub>CLH</sub>      |                                                       |                             | -0.3  |       | ٧     |

|                                       | LX1571 |                       |                                                       |                             | 1.5   |       | ٧     |

| Voltage Hiccup Threshold              |        | V <sub>HCCP</sub>     |                                                       |                             | 2     |       | ٧     |

Note 2. Although this parameter is guaranteed, it is not 100% tested in production.

## PRELIMINARY DATA SHEET

| E                               | LECTRICAL        | . CHARACTERISTICS (Con't.)                                               | )    |             |      |      |  |

|---------------------------------|------------------|--------------------------------------------------------------------------|------|-------------|------|------|--|

| Parameter Symbol                |                  | Test Conditions                                                          | LX   | LX1570/1571 |      |      |  |

| i didiletei                     | 3,111001         | rest conditions                                                          | Min. | Тур.        | Max. | Unit |  |

| PWM Section                     |                  |                                                                          |      |             |      |      |  |

| E.A. Output to PWM Drive Offset | V <sub>OFS</sub> |                                                                          | 1.7  | 2.0         | 2.4  | ٧    |  |

| Fixed Duty Cycle                | D                |                                                                          | 52   | 54          | 56   | %    |  |

| Output Drive Section            | •                |                                                                          |      |             |      |      |  |

| Rise / Fall Time                | $t_R / t_F$      | C <sub>L</sub> = 1000pF                                                  |      | 50          |      | ns   |  |

| Output HI                       | V <sub>DH</sub>  | $I_{SOURCE} = 200 \text{mA}, V_{CS} = 0 \text{V}, V_{FB} = 2.3 \text{V}$ |      | 13.5        |      | ٧    |  |

| Output LO                       | V <sub>DL</sub>  | $I_{SINK} = 200 \text{mA}, V_{CS} = 1.2 \text{V}, V_{FB} = 2.3 \text{V}$ |      | 0.8         |      | ٧    |  |

| Output Pull Down                |                  | $V_{CC} = 0V$ , $I_{PULL\ UP} = 2mA$                                     |      | 1           |      | ٧    |  |

| UVLO Section                    |                  |                                                                          |      |             |      |      |  |

| Start-Up Threshold              | V <sub>ST</sub>  |                                                                          | 15   | 16          | 17   | ٧    |  |

| Turn Off Threshold              | V <sub>OFF</sub> |                                                                          | 9    | 10          | 11   | ٧    |  |

| Hysterises V,                   |                  |                                                                          | 5.5  | 6           | 6.5  | ٧    |  |

| Supply Current Section          |                  |                                                                          |      |             |      |      |  |

| Dynamic Operating Current       | I <sub>Qd</sub>  | Out Freq = $100kHz$ , $C_L = 0$                                          |      | 18          | 30   | mA   |  |

| Start-Up Current                | I <sub>ST</sub>  |                                                                          |      | 150         | 250  | μA   |  |

| FUNCTIONAL PIN DESCRIPTION |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                        | # | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| S.S.                       | 1 | This pin acts as the soft-start pin. A capacitor connected from this pin to GND allows slow ramp up of the NI input resulting in output soft start during start up. This pin is clamped to the internal voltage reference during the normal operation and sets the reference for the feedback regulator.                                                                                                                                                                        |  |  |  |

| V <sub>FB</sub>            | 2 | This pin is the inverting input of the Error Amplifier. It is normally connected to the switching power supply output through a resistor divider to program the power supply voltage. This pin instead of the NI pin is internally trimed to 1% tolerance to include the offset voltage error of the error amp.                                                                                                                                                                 |  |  |  |

| COMP                       | 3 | This pin is the Error Amplifier output and is made available for loop compensation. Typically a series R&C network is connected from this pin to GND.                                                                                                                                                                                                                                                                                                                           |  |  |  |

| C.S.                       | 4 | A voltage proportional to the inductor current is sensed by an external sense resistor (1570) or current transformer (1571) in series with the return line and is connected to this pin. The output drive is terminated and latched off when this voltage amplified by the internal gain (see option table) exceeds the voltage set by the E.A output voltage. The maximum allowable voltage at this pin during normal operation is -0.8V typ for LX1570 and 6V typ for LX1571. |  |  |  |

| GND                        | 5 | This pin is combined control circuitry and power GND. All other pins must be positive with respect to this pin, except for C.S pin.                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| OUT<br>DRV                 | 6 | This pin drives a gate drive transformer which drives the power mosfet. A Schottky diode such as 1N5817 must be connected from this pin to GND in order to prevent the substrate diode conduction.                                                                                                                                                                                                                                                                              |  |  |  |

| V <sub>cc</sub>            | 7 | This pin is the positive supply voltage for the control IC. A high frequency capacitor must be closely placed and connected from this pin to GND to provide the turn-on and turn-off peak currents required for fast switching of the power Mosfet.                                                                                                                                                                                                                             |  |  |  |

| C <sub>T</sub>             | 8 | The free running oscillator frequency is programmed by connecting a capacitor from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

## PRELIMINARY DATA SHEET

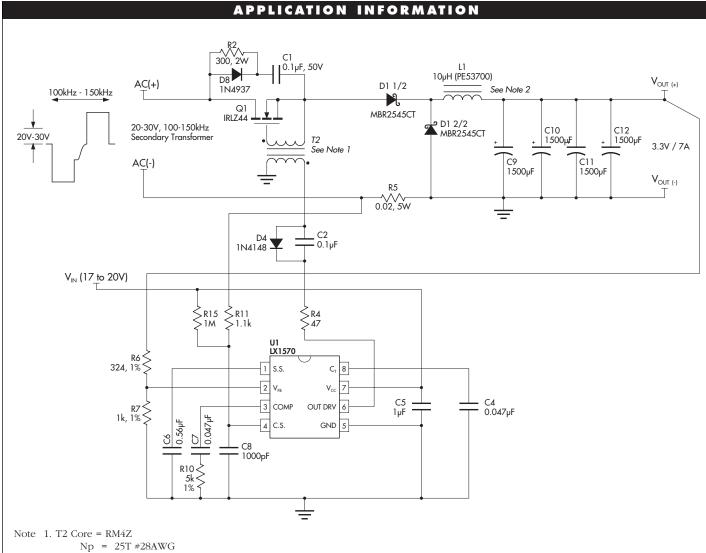

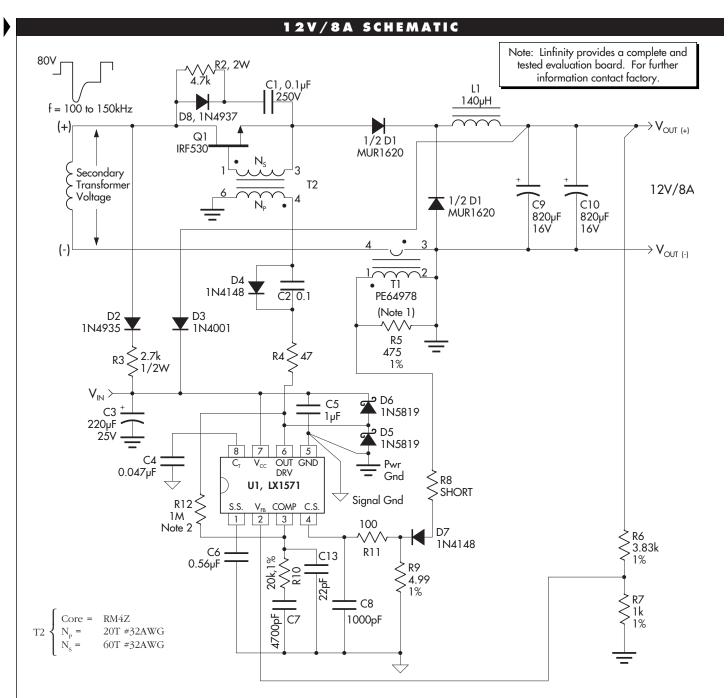

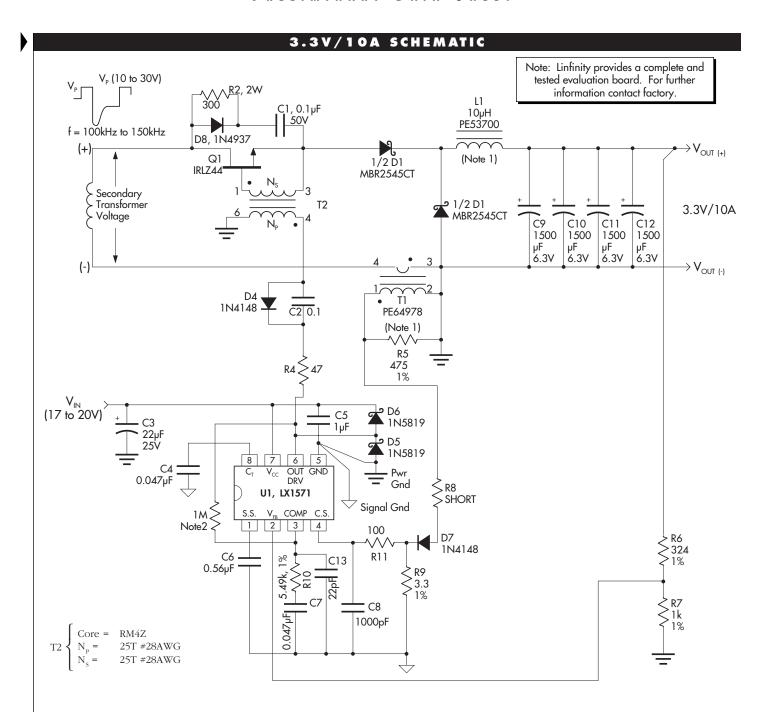

Ns = 25T #28AWG

2. For further information on PE53700 and PE64978, contact Pulse Engineering at (619) 674-8100.

FIGURE 1 — THE LX1570 IN A TYPICAL 3.3V / 7A SECONDARY-SIDE POWER SUPPLY APPLICATION

## PRELIMINARY DATA SHEET

## APPLICATION INFORMATION

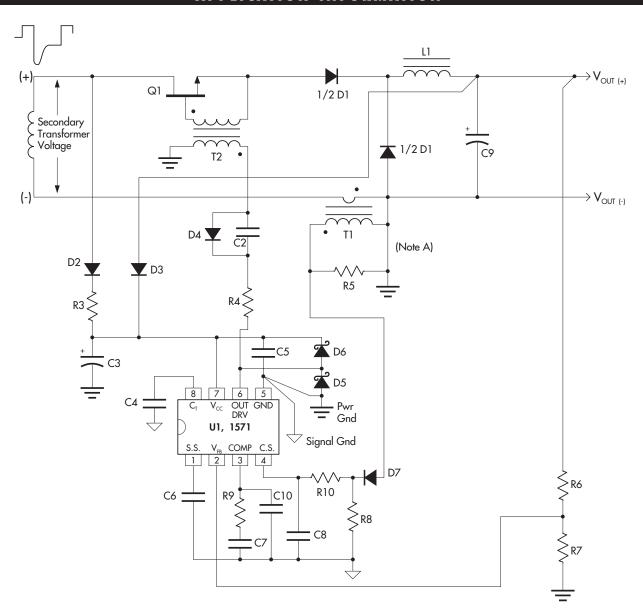

FIGURE 2 — THE LX1571 IN A TYPICAL SECONDARY-SIDE POWER SUPPLY APPLICATION

### PRELIMINARY DATA SHEET

## IC DESCRIPTION

#### STEADY-STATE OPERATION

Steady-state operation is best described by referring to the main block diagram and the typical application circuit shown in Figure 2. The output drive turns the external power MOSFET on and current ramps up in the inductor. Inductor current is sensed with an external resistor (or in the case of LX1571 with a current transformer) and is compared to the threshold at the inverting input of the current sense (C.S.) comparator. This threshold is set by the voltage feedback loop, which is controlled by the error amplifier. Exceeding this threshold resets the PWM latch and turns the MOSFET off. The Output drive goes low, turning the  $\rm C_T$  charging current off and the discharging current on, causing the  $\rm C_T$  voltage to ramp down. When this voltage goes below 1.5V, it sets the PWM latch and turns the output drive back on prior to the next rising edge of the transformer voltage, and the cycle repeats.

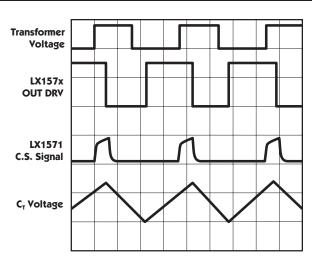

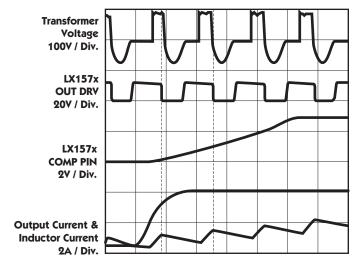

The Steady-State Operation Timing Diagram - Normal Mode (Figure 4A) shows typical waveforms in the steady-state condi-

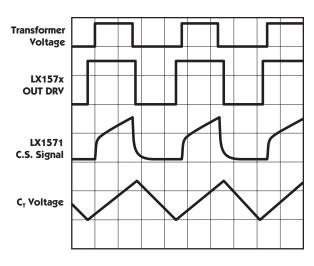

tion. Notice that when the current sense signal turns the MOSFET off, it also synchronizes the output drive to the transformer voltage (see discussion under heading Timing Section). In addition, the energy transfer occurs only when both transformer voltage and OUT DRV pin are "HI" at the same time, establishing the effective on-time of the converter. This shows that the regulation of this converter is achieved by modulating the trailing edge of the output drive with respect to the leading edge of the AC voltage, while maintaining a fixed output drive duty cycle. In other words, the converter duty cycle seen by L1 is controlled by varying the phase between the AC voltage and the output driver signal (phase modulation). Maximum converter duty cycle is achieved when both signals are in phase, as shown in Figure 4B. The LX1570/71 output drive always maintains a fixed duty cycle (≈54%), since both charge and discharge currents are almost equal as shown in Figures 4A and 4B.

FIGURE 3 — STEADY-STATE OPERATION BLOCK DIAGRAM

## Preliminary Data Sheet

## IC DESCRIPTION

2us / Div.

FIGURE 4A — STEADY-STATE OPERATION TIMING DIAGRAM (NORMAL MODE)

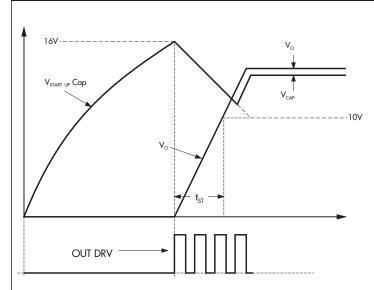

#### START-UP OPERATION

Using the main Block Diagram and the LX157x  $\boldsymbol{V}_{_{\mathrm{CC}}}$  Start-Up Voltage Timing Diagram (Figure 5) as a reference, when the  $V_{\scriptscriptstyle CC}$ voltage passes the UVLO threshold (16V typ.), the output of the UVLO comparator changes to the "HI" state, which causes the following: a) provides biasing for internal circuitry, and b) enables the output drive and the HICCUP latch. This signal sets the "Q" output of the HICCUP latch "LO", allowing the soft-start (S.S.) capacitor voltage to ramp up, forcing the regulator output to follow this voltage. Since the IC provides a constant current source for charging the S.S. capacitor, the resulting waveform is a smooth linear ramp, which provides lower in-rush current during start up.

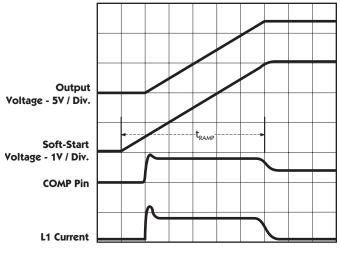

The Start-Up Timing Diagram (Figure 6) shows the output voltage and the S.S. capacitor during start up. Notice that the output voltage does not respond to the S.S. capacitor until this voltage goes above≈0.65 volts, allowing this pin to be used as an external shutdown pin. The value of the soft start capacitor must be selected such that its ramp up time  $(\boldsymbol{t}_{\text{\tiny RAMP}})$  is always greater than the start up time of the converter, so that the converter is able to follow the soft-start capacitor.

It is recommended that the soft start capacitor is always selected such that its ramp up time  $(t_{RAMP})$  be at least 4 times greater than the converter's minimum start-up time. Equations 1 and 2 show how to select this capacitor.

$$t_{RAMP} = 4 * \frac{C_{o} * V_{o}}{I_{o}}$$

Equation 1

Once  $t_{RAMP}$  is known, the soft-start capacitor can then be calculated as follows:  $C_{ss} = \frac{t_{RAMP}}{35} \qquad \text{Equation 2}$

$$C_{ss} = \frac{t_{RAMP}}{35}$$

Equation 2

2us / Div.

FIGURE 4B — STEADY-STATE OPERATION TIMING DIAGRAM (MAXIMUM DUTY CYCLE)

where  $C_{SS}$  is in  $\mu F$  and  $t_{RAMP}$  is in ms.

Example: If

$$C_O = 1600\mu F$$

,  $V_O = 12V$ ,  $I_O = 4A$

$$t_{RAMP} = 4 * \frac{1600 * 10^{-6} * 12}{4} = 19.2 ms$$

$$C_{SS} = \frac{19.2}{35} = 0.55 \mu F$$

The LX1570/71 series also features micropower start-up current that allows these controllers to be powered off the transformer voltage via a low-power resistor and a start-up capacitor. After the IC starts operating, the output of the converter can be used to power the IC. In applications where the output is less than the minimum operating voltage of the IC, an extra winding on the inductor can be used to perform the same function. The start-up capacitor must also be selected so that it can supply the power to the IC long enough for the output of the converter to ramp up beyond the start-up threshold of the IC. Equation 3 shows how to select the start-up capacitor.

$$C_{ST} = 2 \left( \frac{I_{Q} * t_{ST}}{V_{H}} \right)$$

Equation 3

where:  $I_Q^{} \equiv Dynamic operating current of the IC$  $<math>t_{ST}^{} \equiv Time for the bootstrap voltage to go above$

the minimum operating voltage (10V typ.)

$V_{HYST} \equiv Minimum hysteresis voltage of the IC$

Example: If

$$I_Q = 30\text{mA}$$

,  $t_{ST} = 19\text{ms}$ ,  $V_{HYST} = 5.5V$

$$C_{ST} = 2 \left( \frac{30 * 10^{-3} * 19 * 10^{-3}}{5.5} \right) = 207\mu\text{F}$$

### PRELIMINARY DATA SHEET

## IC DESCRIPTION

**FIGURE 5** — LX157x  $V_{cc}$  START-UP VOLTAGE TIMING DIAGRAM

FIGURE 6 — START-UP TIMING DIAGRAM

1ms / Div.

#### **TIMING SECTION**

A capacitor connected from the  $C_T$  pin to ground performs several functions. First, it sets the OUT DRV duty cycle to a constant 54% (regardless of the  $C_T$  value) in order to: a) provide the gate drive for an N-channel MOSFET, utilizing a simple gate drive transformer, and b) insure reliable operation with a transformer duty cycle within a 0 to 50% range. Second, it sets the freerunning frequency of the converter in order to insure the continuous operation during non-steady state conditions, such as start up, load transient and current limiting operations. The value of the timing capacitor is selected so that the free-running frequency is always 20% below the minimum operating frequency of the secondary transformer voltage, insuring proper operation.

$$\mathbf{C}_{_{\mathrm{T}}} = \frac{1}{\mathbf{V}_{_{\mathrm{RPP}}} * \mathbf{f}_{_{\mathrm{S}}} * \left[ \frac{1}{\mathbf{I}_{_{\mathrm{CHG}}}} + \frac{1}{\mathbf{I}_{_{\mathrm{DISCH}}}} \right]} \qquad \text{Equation 4}$$

$\begin{array}{ccc} \mbox{where:} & V_{_{RPP}} & \equiv & \mbox{Peak to peak voltage of } C_{_{T}} \, (0.6V \ \mbox{typ.}) \\ f_{_{S}} & \equiv & \mbox{Free-running frequency of the converter.} \\ & \mbox{Selected to be 80\% of the minimum freq.} \\ & \mbox{of the seconday side transformer voltage.} \end{array}$

Equation 4 shows how to select the timing capacitor  $C_{T}$ .

$I_{CHG} \equiv C_{T}$  charging current (3mA typ.)  $I_{DISCH} \equiv C_{T}$  discharge current (3.5mA typ.) Example: Assuming the transformer frequency is at 100kHz,  $V_{_{RPP}}$  = 0.6V,  $I_{_{CHG}}$  = 3mA,  $I_{_{DISCH}}$  = 3.5mA.

$$C_{T} = \frac{1}{0.6 * 80 * 10^{3} * \left[ \frac{1}{3 * 10^{-3}} + \frac{1}{3.5 * 10^{-3}} \right]} = 0.033 \mu F$$

#### **CURRENT LIMITING**

Using the main Block Diagram as a reference and the typical application circuit of Figure 2, note that current limiting is performed by sensing the current in the return line using a current transformer in series with the switch. The voltage at C.S. pin is then amplified and compared with an internal threshold. Exceeding this threshold turns the output drive off and latches it off until the set input of the PWM latch goes high again. However, if the current keeps rising such that it exceeds the HICCUP comparator threshold, or if the output of the converter drops by ≈20% from its regulated point, two things will happen. First, the HICCUP comparator pulls  $C_{\scriptscriptstyle T}$  pin to 6V, which keeps the output drive off and causes C<sub>T</sub> charging current to be disconnected. Second, it sets the HICCUP latch, causing the discharge current to be turned off until the  $C_{\rm T}$  capacitor voltage goes below 0.3V. Since both charge and discharge currents are disconnected from the capacitor, the only discharge path for C<sub>T</sub> is the internal 2μA current source. When this happens, a very slow discharge occurs, resulting in a long delay time between current limit cycles which greatly reduces power MOSFET dissipation under short circuit conditions.

### PRELIMINARY DATA SHEET

## IC DESCRIPTION

#### MINIMUM CURRENT COMPARATOR

One of the main advantages of replacing a Magnetic Amplifier with a MOSFET, is the MOSFET's ability to respond quickly to large changes in load requirements. Because the LX1570/71 relies on the C.S. signal for synchronization, special circuitry had to be added to keep the output drive synchronized to the transformer voltage during such load transient conditions. This condition is best explained by referring to Figure 7. In Figure 7, it can be seen that the load current is stepped from 0.4A to 4A, causing the COMP pin to slew faster than the inductor current, starting with the second switching cycle after the load transient has occured. This condition eliminates the normal means of resetting the PWM latch through the C.S. comparator path. To compensate for this condition, a second comparator is ORed with the C.S. comparator, which resets the latch on the falling edge of the C.S. signal caused by the falling edge of the transformer voltage.

In other words, the function of the minimum C.S. comparator is to turn OUT DRV off on the falling edge of the C.S. signal, if it is not already off. This assures that the output drive is on before the start of the next AC input cycle (Look-Ahead Switching $^{TM}$ ), allowing maximum converter duty cycle.

#### **ERROR AMPLIFIER**

The function of the error amplifier is to set a threshold voltage for inductor peak current and to control the converter duty cycle, such that power supply output voltage is closely regulated. Regulation is done by sensing the output voltage and comparing it to the internal 2.5V reference. A compensation network based on the application is placed from the output of the amplifier to GND for closed loop stability purposes as well as providing high DC gain for tight regulation. The function of "3V $_{\rm BE}$ " offset is to keep output drive off without requiring the error amplifier output to swing to ground level. The transfer function between error amp output (V $_{\rm COMP}$ ) and peak inductor current is therefore given by:

$$V_{COMP} - 3V_{BE} = I_{P} * G$$

where

I<sub>p</sub> = inductor peak current,

G = resistor divider gain,

(-15 for LX1570, 3 for LX1571)

$V_{BE}$  = diode forward voltage (0.65V typ)

FIGURE 7 — MINIMUM CURRENT COMPARATOR EFFECT DURING LOAD TRANSIENT

## PRELIMINARY DATA SHEET

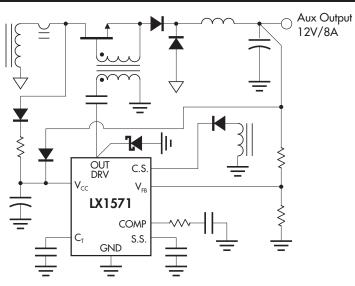

**FIGURE 8** — THE LX1571 IN A 12V/8A SECONDARY-SIDE POWER SUPPLY APPLICATION

Unless otherwise noted all resistors are 1/4W, 5%.

Note 1: For further information on PE64978 contact Pulse Engineering at 619-674-8100.

Note 2: A high value resistor must be coupled back to "COMP" pin to insure proper operation under light load conditions.

## PRELIMINARY DATA SHEET

**FIGURE 9** — THE LX1571 IN A 3.3V/10A SECONDARY-SIDE POWER SUPPLY APPLICATION

Unless otherwise noted all resistors are 1/4W, 5%.

Note 1: For further information on PE53700 and PE64978 contact Pulse Engineering at 619-674-8100.

Note 2: A high value resistor must be coupled back to "COMP" pin to insure proper operation under light load conditions.