# MiniRISC<sup>®</sup> LR4500 Superscalar Microprocessor

# **Technical Manual**

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000066-00, First Edition (May 1998)

This document describes revision A of LSI Logic Corporation's MiniRISC<sup>®</sup> LR4500 Superscalar Microprocessor and will remain the official reference source for all revisions of this product until rescinded by an update.

To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1997, 1998 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design, CoreWare, G10, and MiniRISC are registered trademarks and SerialICE is a trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# **Contents**

| Preface   |       |             |                              |     |

|-----------|-------|-------------|------------------------------|-----|

| Chapter 1 | Intro | duction     |                              |     |

| •         | 1.1   | LR4500 (    | Overview                     | 1-1 |

|           | 1.2   | LR4500 F    | Features                     | 1-3 |

| Chapter 2 | Fund  | ctional Blo | cks                          |     |

|           | 2.1   | CW4011      | Shell                        | 2-2 |

|           |       | 2.1.1       | CW4011 Core                  | 2-3 |

|           |       | 2.1.2       | Multiply/Divide Unit         | 2-3 |

|           |       | 2.1.3       | Memory Management Unit Shell | 2-3 |

|           |       | 2.1.4       | Write Back Buffer            | 2-3 |

|           |       | 2.1.5       | Caches                       | 2-4 |

|           | 2.2   | Synchron    | ous DRAM Controller          | 2-4 |

|           | 2.3   | SCbus to    | Local I/O Bus Converter      | 2-4 |

|           | 2.4   | PLL Cloc    | k Circuit                    | 2-5 |

|           | 2.5   | ICEport L   | JART                         | 2-6 |

|           | 2.6   | Pipeline A  | Architecture                 | 2-7 |

| Chapter 3 | Prog  | ramming M   | Model (                      |     |

|           | 3.1   | Register    | Set                          | 3-2 |

|           | 3.2   | Memory I    | Mapping                      | 3-4 |

|           | 3.3   | System C    | Configuration                | 3-5 |

|           |       | 3.3.1       | CCC Register                 | 3-5 |

|           |       | 3.3.2       | Lbus Controller Registers    | 3-9 |

Contents iii

| Chapter 4 | Inst | ruction Se   | t                                      |      |

|-----------|------|--------------|----------------------------------------|------|

|           | 4.1  | Instruction  | n Set                                  | 4-1  |

|           | 4.2  | CW4011       | Instruction Set Extensions             | 4-15 |

|           | 4.3  | CPU Inst     | ruction Opcode Bit Encoding            | 4-30 |

| Chapter 5 | Bus  | Interface [  | Descriptions                           |      |

|           | 5.1  | External     | Interfaces                             | 5-2  |

|           |      | 5.1.1        | Mbus Interface                         | 5-2  |

|           |      | 5.1.2        | Lbus Interface                         | 5-5  |

|           |      | 5.1.3        | Phase-Locked Loop (PLL) Clock Signals  | 5-9  |

|           |      | 5.1.4        | Test Signals                           | 5-10 |

|           |      | 5.1.5        | CW4011 Core Monitor Signal             | 5-11 |

|           | 5.2  | Internal I   | nterface                               | 5-11 |

|           |      | 5.2.1        | SCbus Interface                        | 5-11 |

|           |      | 5.2.2        | External Buffering for SCbus Signals   | 5-19 |

|           |      | 5.2.3        | CW4011 Shell Reset/Interrupt Interface | 5-22 |

| Chapter 6 | DRA  | M Controll   | er and Memory Bus                      |      |

|           | 6.1  | DRAM Ty      | pes and Available DRAM Address Area    | 6-1  |

|           | 6.2  | Memory I     | Interface                              | 6-2  |

|           | 6.3  | Address      | Bit Assignment                         | 6-4  |

|           | 6.4  |              | ontroller Configuration Register       | 6-5  |

|           | 6.5  | DRAM M       | ode Register                           | 6-9  |

|           | 6.6  | DRAM R       | efresh                                 | 6-11 |

|           | 6.7  | DRAM C       | ommands                                | 6-13 |

|           | 6.8  | Initializing | DRAM and Programming the Mode Register | 6-14 |

|           | 6.9  | DRAM Tr      | ansactions                             | 6-19 |

| Chapter 7 | SCbi | us and Loc   | cal I/O Bus Converter Module           |      |

| -         | 7.1  | Lbus Fea     | tures                                  | 7-1  |

|           | 7.2  | LR4500 a     | as Master on the Lbus                  | 7-2  |

|           | 7.3  | LR4500 a     | as Slave on the Lbus                   | 7-5  |

|           | 7.4  | SCbus Ti     | meout Watchdog Timer                   | 7-8  |

|           | 7.5  |              | Vectored Interrupt (EVInt) Support     | 7-9  |

| Chapter 8  | Cach | e Confi                 | guration and Maintenance              |      |

|------------|------|-------------------------|---------------------------------------|------|

|            | 8.1  | 8.1 Cache Configuration |                                       | 8-   |

|            | 8.2  | Cache                   | Maintenance                           | 8-4  |

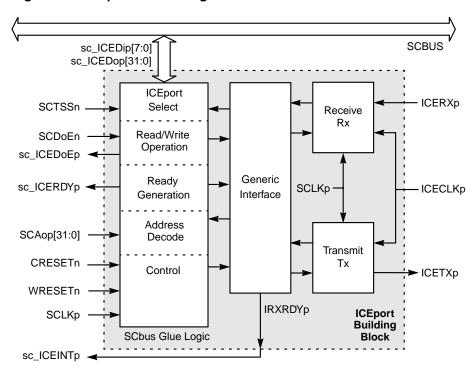

| Chapter 9  | ICEp | ort                     |                                       |      |

|            | 9.1  | Overvi                  | ew                                    | 9-   |

|            | 9.2  | <b>ICEpor</b>           | t Features                            | 9-2  |

|            | 9.3  | <b>ICEpor</b>           | t Functional Blocks                   | 9-3  |

|            |      | 9.3.1                   | Receive and Transmit Interface Logic  | 9-4  |

|            |      | 9.3.2                   | Generic Interface Logic               | 9-4  |

|            |      | 9.3.3                   | SCbus Interface Logic                 | 9-4  |

|            | 9.4  | <b>ICEpor</b>           | t Signals                             | 9-   |

|            |      | 9.4.1                   | Monitored SCbus Signals               | 9-0  |

|            |      | 9.4.2                   | Other SCbus Signals                   | 9-7  |

|            |      | 9.4.3                   | ICEport Scan and Clocking I/O Signals | 9-8  |

|            | 9.5  | <b>ICEpor</b>           | t Registers                           | 9-9  |

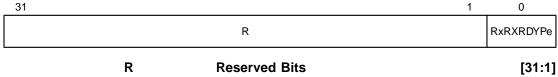

|            |      | 9.5.1                   | Rx Status Register                    | 9-1  |

|            |      | 9.5.2                   | Rx Setup Register                     | 9-12 |

|            |      | 9.5.3                   | Rx Data Register                      | 9-12 |

|            |      | 9.5.4                   | Tx Status Register                    | 9-13 |

|            |      | 9.5.5                   | Tx Data Register                      | 9-14 |

|            | 9.6  | <b>ICEpor</b>           | t Operations                          | 9-14 |

|            |      | 9.6.1                   | SCbus Read/Write Transactions         | 9-14 |

|            |      | 9.6.2                   | Reset                                 | 9-17 |

|            |      | 9.6.3                   | The Serial Bit Stream                 | 9-18 |

|            |      | 9.6.4                   | ICEport Receive and Transmit          | 9-18 |

|            |      | 9.6.5                   | Clock Domains and Properties          | 9-2  |

|            | 9.7  | ICEpor                  | t Pin Buffers and Drivers             | 9-22 |

| Chapter 10 | Orga | nization                | of Clock and Exception Signals        |      |

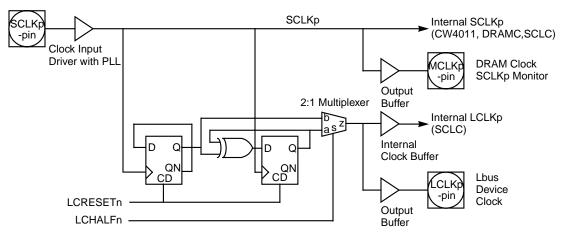

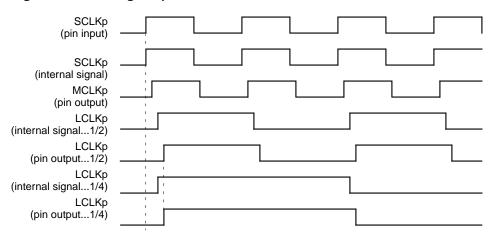

| -          | 10.1 | Clock (                 | Circuitry                             | 10-  |

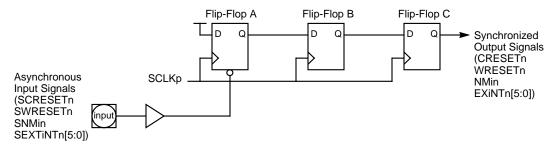

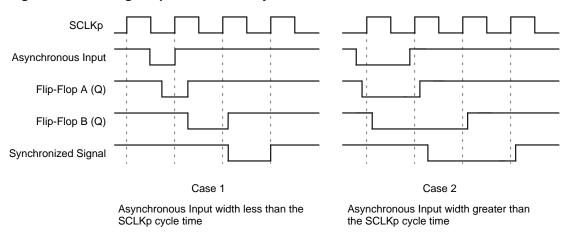

|            | 10.2 | Except                  | ion Inputs                            | 10-3 |

| Chapter 11 | Spec | ification               | us .                                  |      |

| -          | 11.1 | Electric                | cal Characteristics                   | 11-  |

|            |      | 11 1 1                  | Absolute Maximum Ratings              | 11-1 |

Contents

|         | 11.2<br>11.3 | Packaging Pinouts                                      | 11-6<br>11-8 |

|---------|--------------|--------------------------------------------------------|--------------|

|         | Custo        | Customer Feedback                                      |              |

| Figures |              |                                                        |              |

|         | 1.1          | Block Diagram of LR4500 and Evaluation Board Circuitry | 1-2          |

|         | 2.1          | LR4500 Block Diagram                                   | 2-2          |

|         | 2.2          | LR4500 PLL Circuit Diagram                             | 2-6          |

|         | 2.3          | LR4500 Instruction Pipeline                            | 2-7          |

|         | 3.1          | LR4500 Master/Slave Memory Map                         | 3-4          |

|         | 3.2          | CCC Register                                           | 3-5          |

|         | 3.3          | SCbus Status Register                                  | 3-10         |

|         | 3.4          | SCbus Error Address Register                           | 3-10         |

|         | 3.5          | External Vectored Interrupt Register                   | 3-11         |

|         | 5.1          | LR4500 Interfaces                                      | 5-2          |

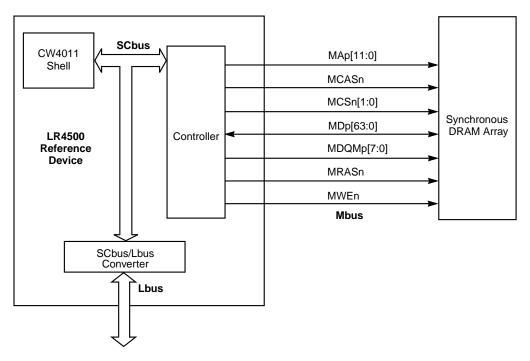

|         | 5.2          | Mbus Interface                                         | 5-3          |

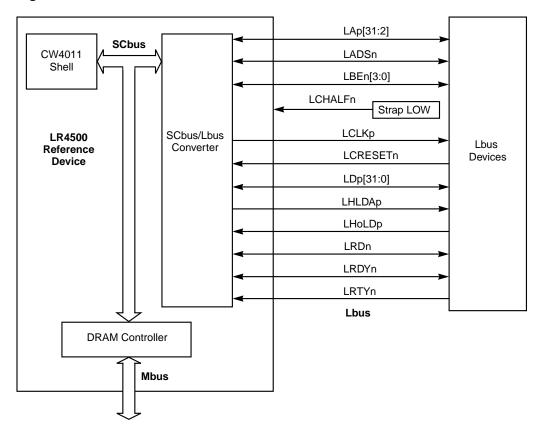

|         | 5.3          | Lbus Interface                                         | 5-6          |

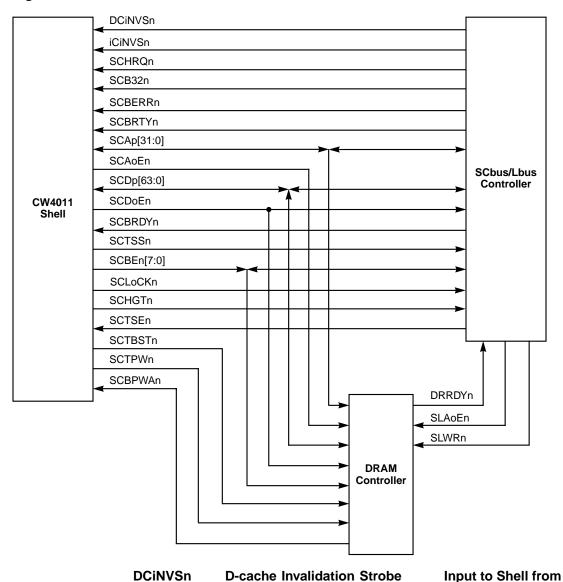

|         | 5.4          | SCbus Interface                                        | 5-13         |

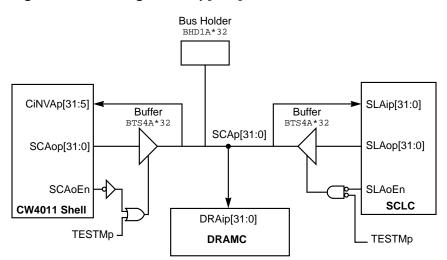

|         | 5.5          | Buffering for SCAp[31:0] Address Bus                   | 5-20         |

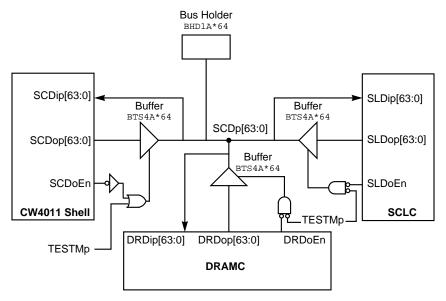

|         | 5.6          | Buffering for SCDp[63:0] Data Bus                      | 5-21         |

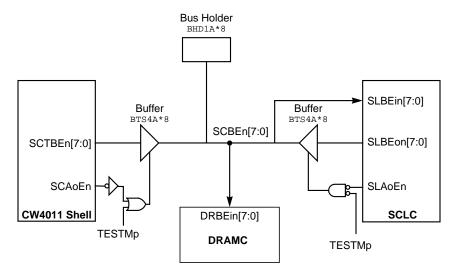

|         | 5.7          | Buffering for SCBEn[7:0] Byte Enable                   | 5-21         |

|         | 5.8          | Shell Reset/Interrupt Interface                        | 5-22         |

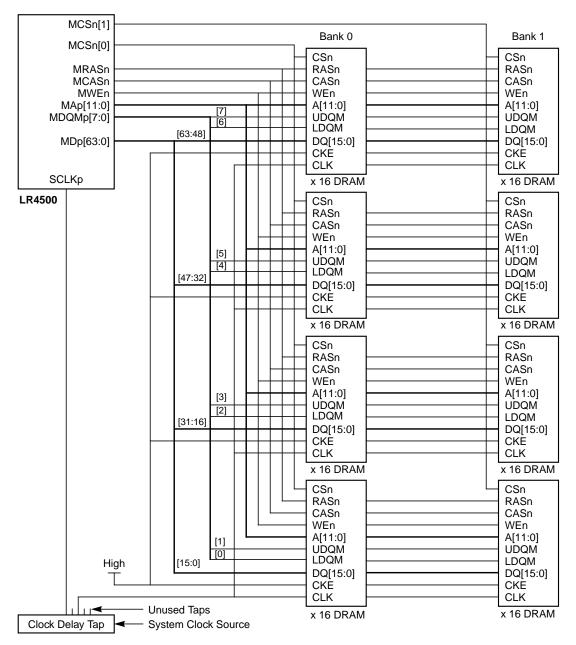

|         | 6.1          | LR4500 Interface with DRAM                             | 6-3          |

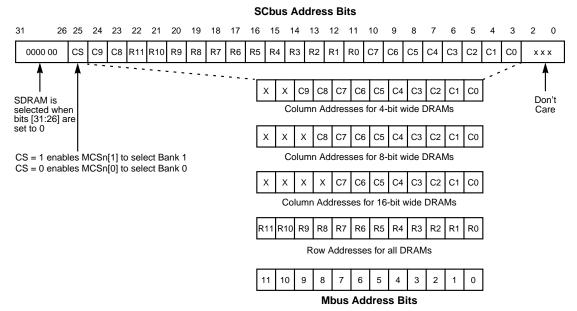

|         | 6.2          | SCbus DRAM Address Bit Assignment                      | 6-4          |

|         | 6.3          | DRAM Controller Configuration Register Format          | 6-5          |

|         | 6.4          | DRAM Mode Register Format                              | 6-10         |

|         | 6.5          | DRAM Refresh Interval Timer                            | 6-12         |

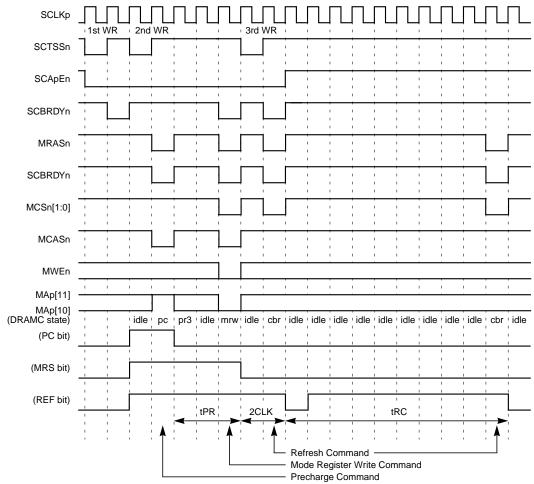

|         | 6.6          | Timing Requirements for DRAM Initialization Sequence   | 6-18         |

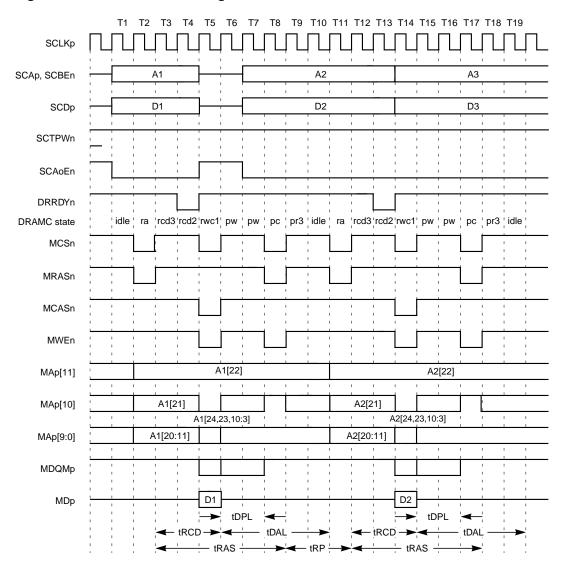

|         | 6.7          | Single Burst Read Transaction                          | 6-20         |

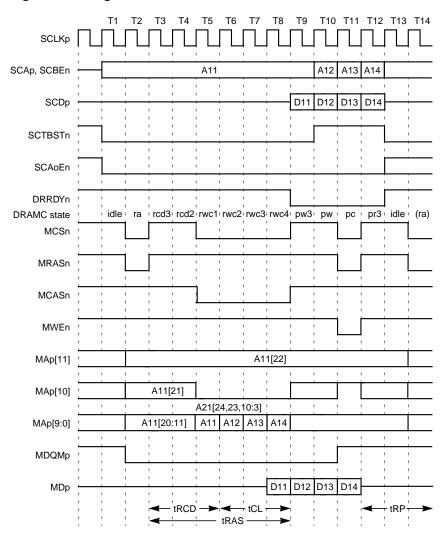

|         | 6.8          | Two Continuous Single Write Transactions               | 6-21         |

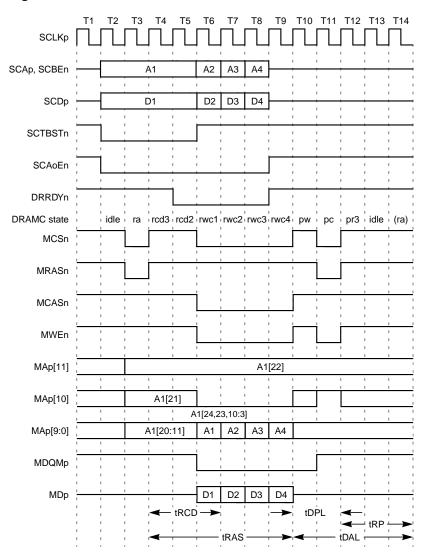

|         | 6.9          | Burst Write Transaction                                | 6-22         |

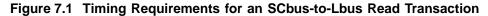

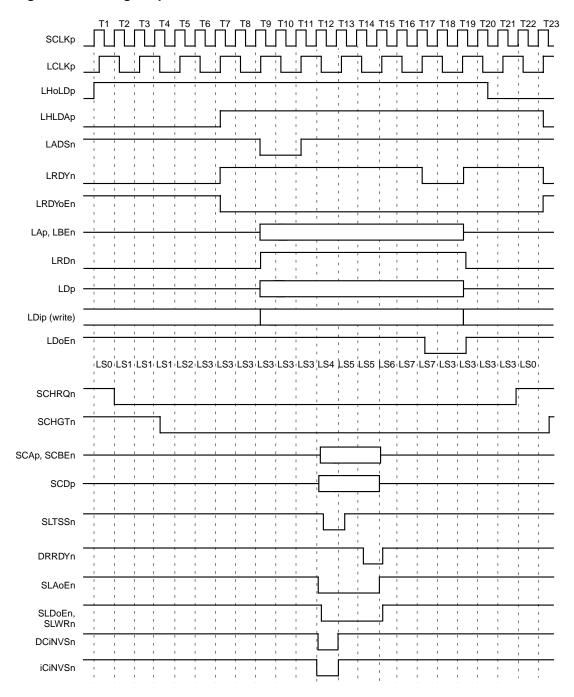

|         | 7.1          | Timing Requirements for an SCbus-to-Lbus Read          |              |

Recommended Operating Conditions

Input/Output Capacitance

**DC** Characteristics

11.1.5 AC Timing Specifications

11-2

11-2

11-2

11-3

11.1.2

11.1.3

11.1.4

vi Contents

|        |      | Iransaction                                              | 7-3  |

|--------|------|----------------------------------------------------------|------|

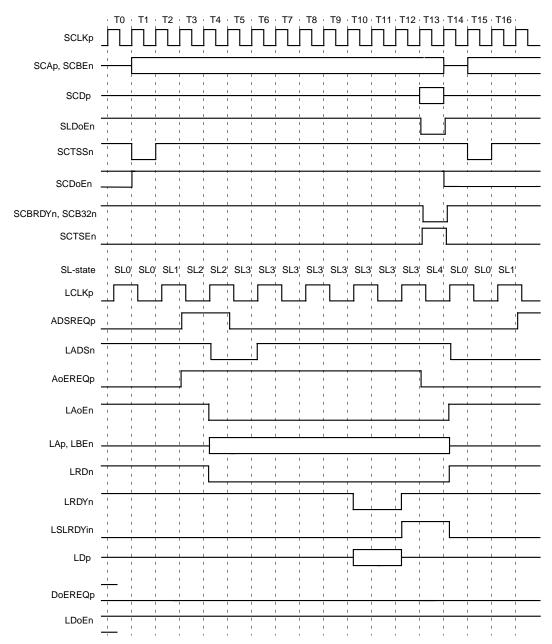

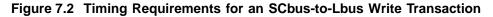

|        | 7.2  | Timing Requirements for an SCbus-to-Lbus Write           | 7.4  |

|        | 7.0  | Transaction                                              | 7-4  |

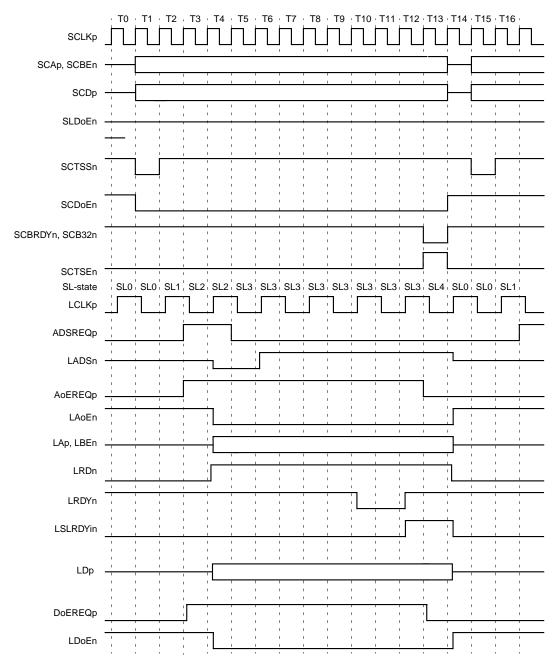

|        | 7.3  | Timing Requirements for Lbus-to-SCbus Read Transaction   | 7-6  |

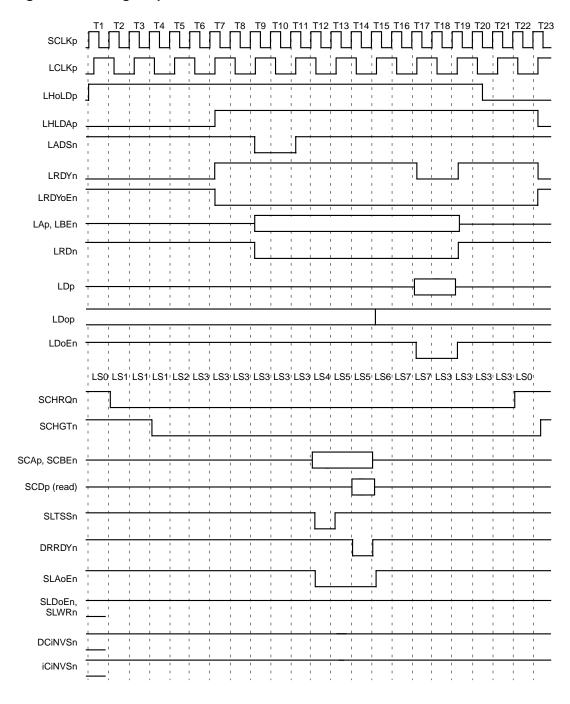

|        | 7.4  | Timing Requirements for Lbus-to-SCbus Write Transaction  | 7-7  |

|        | 7.5  | SCbus Error Address and Error Status Register Bit Format | 7-8  |

|        | 7.6  | External Vectored Interrupt Register Bit Format          | 7-9  |

|        | 9.1  | CW4011 Design with ICEport                               | 9-2  |

|        | 9.2  | ICEport Block Diagram                                    | 9-3  |

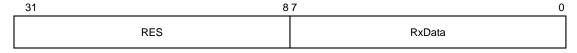

|        | 9.3  | Rx Status Register                                       | 9-11 |

|        | 9.4  | Rx Setup Register                                        | 9-12 |

|        | 9.5  | Rx Data Register                                         | 9-13 |

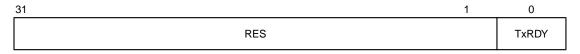

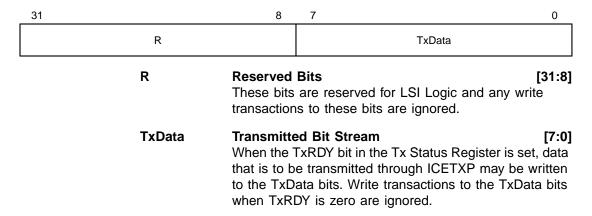

|        | 9.6  | Tx Status Register                                       | 9-13 |

|        | 9.7  | Tx Data Register                                         | 9-14 |

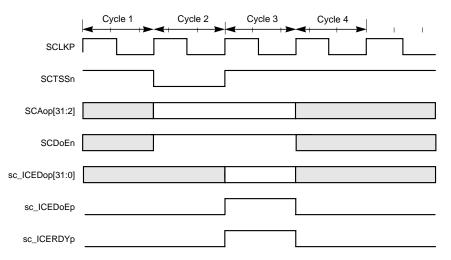

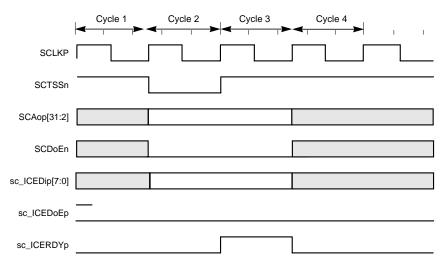

|        | 9.8  | Read Transaction                                         | 9-16 |

|        | 9.9  | Write Transaction                                        | 9-16 |

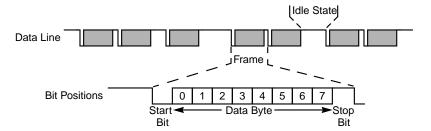

|        | 9.10 | Serial Bit Stream                                        | 9-18 |

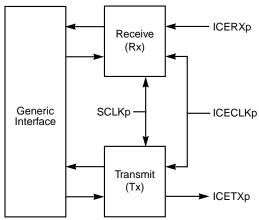

|        | 9.11 | Rx and Tx Blocks                                         | 9-19 |

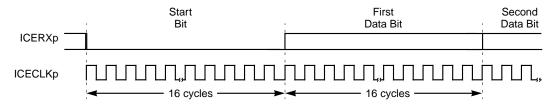

|        | 9.12 | Received Bit Timing                                      | 9-20 |

|        | 10.1 | LR4500 PLL Clock Circuitry                               | 10-2 |

|        | 10.2 | Timing Requirements for the CW4011 and Lbus Clocks       | 10-3 |

|        | 10.3 | Exception Inputs Synchronization Circuitry               | 10-4 |

|        | 10.4 | Timing Requirements for Synchronization Circuit          | 10-4 |

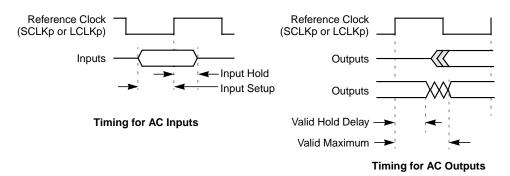

|        | 11.1 | AC Timing for LR4500 Inputs and Outputs                  | 11-5 |

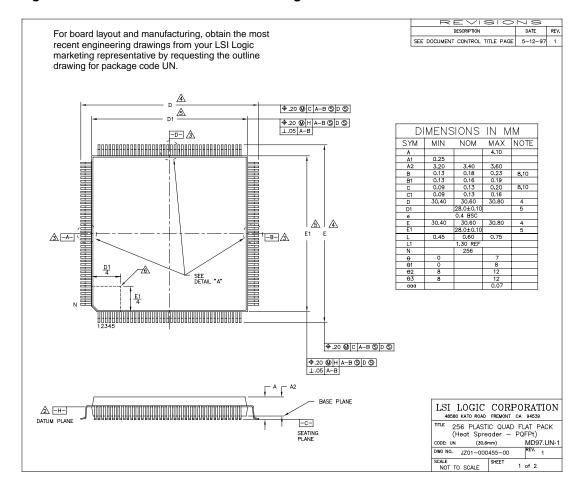

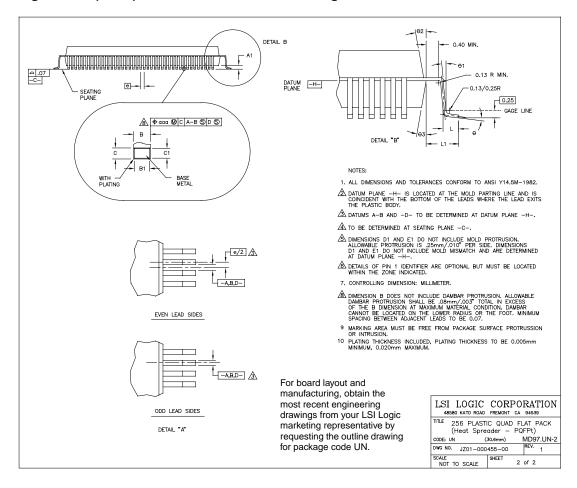

|        | 11.2 | 256 PQFPt Mechanical Drawing                             | 11-6 |

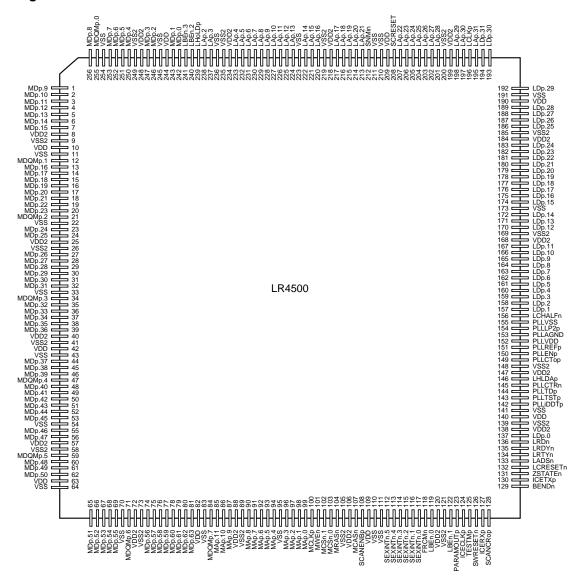

|        | 11.3 | 256 PQFPt Pinouts                                        | 11-8 |

| Tables |      |                                                          |      |

|        | 3.1  | LR4500 Registers                                         | 3-2  |

|        | 4.1  | Load and Store Instructions                              | 4-2  |

|        | 4.2  | Load Linked MIPS II Instructions                         | 4-3  |

|        | 4.3  | ALU Immediate Instructions                               | 4-4  |

|        | 4.4  | ALU Three-Operand Register Type Instructions             | 4-5  |

|        | 4.5  | Shift Instructions                                       | 4-6  |

|        | 4.6  | Multiply/Divide Instructions                             | 4-7  |

|        | 4.7  | Extended Computational Instructions                      | 4-8  |

|        | 4.8  | Jump Instructions                                        | 4-9  |

|        | -    |                                                          | _    |

Contents vii

| 4.9  | Branch Instructions                               | 4-10 |

|------|---------------------------------------------------|------|

| 4.10 | Branch Likely Instructions                        | 4-11 |

| 4.11 | Trap Instructions                                 | 4-12 |

| 4.12 | Special Instructions                              | 4-13 |

| 4.13 | CP0 Instructions                                  | 4-13 |

| 4.14 | Cache Maintenance Instructions                    | 4-14 |

| 4.15 | CW4011 Opcode Bit Encoding                        | 4-31 |

| 4.16 | SPECIAL Opcode Bit Encoding                       | 4-32 |

| 4.17 | REGIMM Opcode rt Bit Encoding                     | 4-32 |

| 4.18 | CACHE <sup>x2</sup> Opcode rt Bit Encoding        | 4-33 |

| 4.19 | COPz rs Opcode Bit Encoding                       | 4-33 |

| 4.20 | COPz rt Opcode Bit Encoding                       | 4-33 |

| 4.21 | CP0 Opcode Bit Encoding                           | 4-34 |

| 6.1  | DRAM Configurations                               | 6-2  |

| 6.2  | SCbus Address and Mbus Address Bit Assignment     | 6-5  |

| 6.3  | Relationship Between Frequency and Latency        | 6-9  |

| 6.4  | Refresh Register Programming Values               | 6-13 |

| 6.5  | Refresh Register Setting for 80 MHz 12.5 ns DRAM  | 6-13 |

| 6.6  | Summary of DRAM Commands and Mbus Control Signals | 6-14 |

| 6.7  | Timing Signals                                    | 6-16 |

| 8.1  | Cache Size and Accessing                          | 8-2  |

| 8.2  | D-cache Scratchpad RAM Configuration              | 8-3  |

| 8.3  | I-cache Instruction RAM Configuration             | 8-3  |

| 9.1  | ICEport Signals                                   | 9-6  |

| 9.2  | ICEport Register Addresses                        | 9-10 |

| 10.1 | Summary of LR4500 Clocks                          | 10-2 |

| 11.1 | Absolute Maximum Ratings                          | 11-1 |

| 11.2 | Recommended Operating Conditions                  | 11-2 |

| 11.3 | Input/Output Capacitance                          | 11-2 |

| 11.4 | DC Characteristics                                | 11-3 |

| 11.5 | LR4500 AC Timing Specifications                   | 11-4 |

# **Preface**

This book is the primary reference and technical manual for the MiniRISC® LR4500 Superscalar Microprocessor reference device. The book contains a complete functional description of the LR4500, with physical and electrical specifications.

#### **Audience**

This book assumes that you are familiar with microprocessors and related support devices. The book targets:

- Engineers and managers who are evaluating the LR4500 for possible use in system design

- ♦ Engineers who are designing the LR4500 into a system

# Organization

This book has the following chapters:

- Chapter 1, Introduction, provides an overview of the reference device, defines the device's context on an evaluation board, and lists the device's features.

- Chapter 2, Functional Blocks, provides information about all functional blocks that are part of the LR4500: the CW4011 shell, the synchronous DRAM Controller (DRAMC), the SCbus/Lbus Controller (SCLC), the PLL clock circuit, and the ICEport UART. The chapter also describes the LR4500 pipeline architecture.

- Chapter 3, Programming Model, provides information about the LR4500 programming model, including a list of LR4500 registers, information about memory mapping, and descriptions of the LR4500 registers used to configure the system.

Preface ix

- Chapter 4, Instruction Set, lists and describes the instructions that make up the LR4500 instruction set, defines the instruction set extensions, and describes CPU instruction opcode bit encoding.

- Chapter 5, Bus Interface Descriptions, describes the interface signals for the major LR4500 interfaces including the signals that provide the external interface between the LR4500 and external devices, and the interface signals internal to the LR4500. The chapter also describes the buffering required for certain interface signals.

- Chapter 6, DRAM Controller and Memory Bus, describes the synchronous DRAM Controller and the memory bus. It also provides timing information for different DRAM transactions.

- Chapter 7, SCbus and Local I/O Bus Converter Module, describes the Lbus and explains how the LR4500 interacts with the Lbus through the SCLC module.

- Chapter 8, Cache Configuration and Maintenance, describes the I-cache and D-cache configurations and explains how to maintain the caches after power is turned on.

- ◆ Chapter 9, ICEport, describes the ICEport building block that provides a full-duplex serial UART (universal asynchronous receive and transmit) port for the LR4500.

- ◆ Chapter 10, Organization of Clock and Exception Signals, describes the organization of the LR4500 clock signals and the exception-handling signals.

- Chapter 11, Specifications, defines the electrical characteristics of the LR4500. It also provides packaging information, including the mechanical layout of the LR4500, the chip's dimensions, and pin locations.

#### **Related Publications**

MiniRISC CW4011 Superscalar Microprocessor Core Technical Manual, Order Number C14040

MiniRISC BDMR4011 Evaluation Board User's Guide, Order Number C14052.

#### Conventions Used in This Manual

"Assert" means to drive a signal true or active; "deassert" means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x," for example, 0x32CF.

The following notational conventions are used throughout this manual.

| Notation         | Example   | Meaning and Use                                                                                               |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------|

| courier typeface | .nwk file | Names of commands, files, symbols, parts, directories, modules, and macrocells are shown in courier typeface. |

| bold typeface    | fd1sp     | In a command line, keywords are shown in bold, nonitalic typeface. Enter them exactly as shown.               |

Preface xi

# Chapter 1 Introduction

This chapter provides an overview and defines the features of the MiniRISC LR4500 Superscalar Microprocessor reference device.

## 1.1 LR4500 Overview

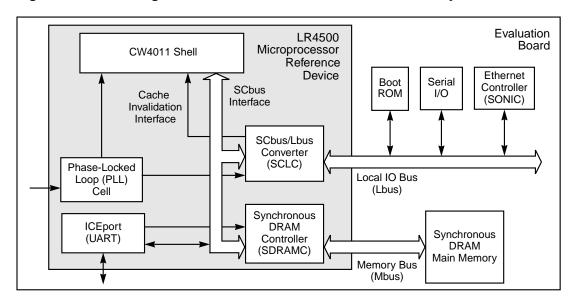

The LR4500 is a chip implementation of the MiniRISC CW4011 microprocessor core and shell. It is the second LSI Logic implementation of a 32-bit MIPS II compatible, superscalar CPU. As shown in Figure 1.1, the LR4500 contains the following circuitry, housed on an evaluation board:

- The maximum configuration CW4011 shell, which is an unencrypted Verilog model that contains

- CW4011 core

- Multiply/Divide unit (MDU)

- Instruction cache (I-cache)

- Data cache (D-cache)

- Memory Management Unit (MMU) without Translation Look-aside Buffer (TLB)

- Write Back Buffer (WB).

You can configure certain modules in the shell by programming the Configuration Register in CW4011 Coprocessor 0 (CP0). For example, you can turn off the MDU and the WB. Depending on the application, the LR4500 generally uses all modules.

- ♦ The DRAM controller that provides the Memory Bus (Mbus) interface between the LR4500 and external synchronous memory devices.

- The SCbus/Lbus Converter that controls the Local I/O bus (Lbus) and external Lbus devices

- ♦ A Phase-Locked Loop (PLL) circuit that supplies clock inputs to the other modules in the LR4500

- The ICEport UART (universal asynchronous receiver/transmitter) is used to download SerialICE™ application software and to debug the LR4500.

Figure 1.1 Block Diagram of LR4500 and Evaluation Board Circuitry

Chapter 2, "Functional Blocks," provides detailed information about the functional elements of the LR4500.

The LR4500 is housed on an evaluation board (BDLR4500) that allows you to use and test the LR4500. In addition to the LR4500, the board contains:

◆ The DRAM array that communicates with the LR4500 through the Mbus.

The Lbus that allows you to plug in devices such as a Boot-ROM, serial I/O devices, and an external Ethernet controller. (The Lbus is a simple, generic interface for peripheral devices such as ROMs, RAMs, UARTs. It has a demultiplexed 32-bit address bus and 32-bit data bus, and it is similar to the 486 VLbus.)

## 1.2 LR4500 Features

The LR4500 Microprocessor has the following features:

- System clock operating at up to 100 MHz, with 150 Dhrystone MIPS performance

- Superscalar microprocessor support for the MIPS II 32-bit instruction set:

- Up to two instructions executed per clock cycle

- Four-deep write buffer

- Load scheduling

- R3000/R4000 compatible mode for the Exception Return and Status Register

- ♦ 32-bit timer (R4000 compatible)

- SCbus watchdog timer with error reporting features

- Full internal SCAN testing

- SerialICE debugging support provided through the ICEport UART interface

- SCbus/Lbus converter to control the Lbus and external Lbus devices

- Easily implemented interface to the SONIC Ethernet controller

- ♦ Synchronous DRAM Controller, with 64-bit wide data transfer, interfaces to the following 16-Mbit SDRAMs (synchronous DRAMs):

- 1-M x 16-bit SDRAM devices in an 8-Mbyte or 16-Mbyte configuration

- 2-M x 8-bit SDRAM devices in a 16-Mbyte or 32-Mbyte configuration

- 4-M x 4-bit SDRAM devices in a 32-Mbyte or 64-Mbyte configuration

LR4500 Features 1-3

- PLL circuit for internal system clock; synchronizes internal system clock with an external clock

- ♦ 3.3 V operation

- ♦ LR4500 power 4.19 mA (at 3.46 V and 100 MHz)

- Packaged in a 256-pin PQFPt (Plastic Quad Flat Package)

- Cache configuration:

- Direct-mapped or two-way set-associative I-cache and D-cache

- 1-Kbyte, 2-Kbyte, 4-Kbyte, or 8-Kbyte cache sets, organized as either direct-mapped (single set) cache with maximum cache size of 8 Kbytes, or as a two-way set-associative cache with a maximum cache size of 16 Kbytes.

- ♦ Simplified kseg0 and kseg1 Memory Management Unit without TLB

- ♦ Fast multiplier supporting multiply-accumulate operations

- High-performance multiplier delivers three-cycle latency and one cycle throughput for MAC (multiply with accumulate) instructions

- ♦ Support for both big-endian and little-endian formats

# Chapter 2 Functional Blocks

This chapter describes each of the LR4500 functional blocks and the LR4500 pipeline architecture.

The chapter is divided into the following sections:

- ◆ "CW4011 Shell," on page 2-2.

- ♦ "Synchronous DRAM Controller," on page 2-4.

- ♦ "SCbus to Local I/O Bus Converter," on page 2-4.

- ♦ "PLL Clock Circuit," on page 2-5.

- ♦ "ICEport UART," on page 2-6.

- "Pipeline Architecture," on page 2-7.

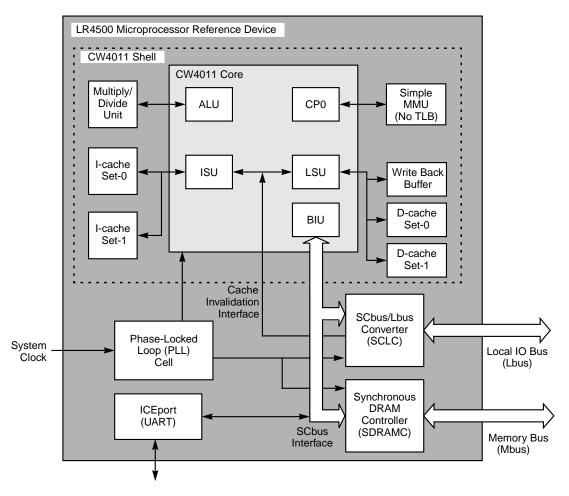

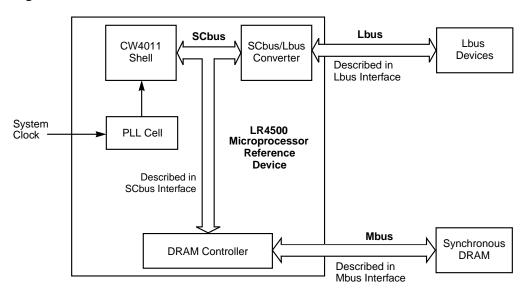

Figure 2.1 LR4500 Block Diagram

# 2.1 CW4011 Shell

The CW4011 shell consists of the CW4011 core, the MDU (Multiply/Divide Unit), the MMU (Memory Management Unit), the WB (Write Back Buffer), the I-cache (instruction cache), and the D-cache (data cache).

With the exception of the CW4011 core, you can turn off certain modules in the CW4011 shell, for example the MDU or the WB, to fit your own ASIC design.

#### 2.1.1 CW4011 Core

The CW4011 core is an encrypted Verilog RTL model that is part of LSI Logic's CoreWare® Library. The CW4011 core is a predefined hardmacro that contains the following basic microprocessor elements:

- Instruction Scheduling Unit (ISU)

- ♦ Load/Store Unit (LSU)

- ♦ Arithmetic Logic Unit (ALU)

- ♦ Coprocessor 0 (CP0)

- ♦ Bus Interface Unit (BIU)

The CW4011 core executes all MIPS II 32-bit based instructions except for multiply/divide instructions. These instructions are handled by the MDU, which is part of the CW4011 shell.

For detailed information about the CW4011 core, refer to the *MiniRISC CW4011 Superscalar Microprocessor Technical Manual*.

### 2.1.2 Multiply/Divide Unit

The multiply/divide unit supports multiply-add/subtract operations as well as multiply and divide. The multiply instruction executes in three cycles. The multiply-add/subtract instruction is optimized to one cycle.

# 2.1.3 Memory Management Unit Shell

The MMU does not have a TLB. *kseg0* and *kseg1* are mapped to the first 512 Mbyte space, which is the bottom of the memory space. The *kuseg* and *kseg2* blocks are directly mapped to the physical address space without any change. "Section 3.2, on page 3-4, provides more information on this subject.

#### 2.1.4 Write Back Buffer

The CW4011 core uses this buffer when the D-cache operates in write back mode. When a cache miss occurs and the victim entry contains a dirty line, the dirty data is written into the Write Back Buffer instead of the main memory. This reduces the latency of the cache refill for missed addresses. Data in the Write Back Buffer is written into the main memory after the refill is completed.

CW4011 Shell 2-3

#### 2.1.5 Caches

The LR4500 has separate instruction and data caches—I-cache and D-cache—that can be organized as direct-mapped or two-way set-associative caches. The cache controllers support configurations of 1, 2, 4, or 8 Kbytes for each set. Thus, the smallest supported configuration is a 1-Kbyte direct-mapped cache, and the largest is a 16-Kbyte two-way set-associative cache, with 8 Kbytes per set. You can select between Write Back and Write Through modes. You can also configure both sets of the D-cache and one set of the I-cache for scratchpad RAM mode. Refer to Chapter 8, "Cache Configuration and Maintenance," for more information on this subject.

# 2.2 Synchronous DRAM Controller

The DRAM Controller is part of the LR4500 reference device, and it is external to the CW4011 shell, as shown in Figure 2.1 on page 2-2. It generates DRAM transactions in response to requests from the CW4011 core or from the SCLC module. The DRAM Controller also generates initialization cycles and refresh cycles for DRAM. Chapter 6, "DRAM Controller and Memory Bus," provides detailed information about DRAM and the DRAM controller.

# 2.3 SCbus to Local I/O Bus Converter

The SCLC module provides an interface between the internal CW4011 microprocessor bus (SCbus) and the external Local I/O bus (Lbus). The Lbus connects such devices as boot-ROM, serial I/O devices, and the Ethernet Controller to the LR4500.

The SCbus is a 32-bit address, 64-bit data bus. The Lbus, which is a subset of the industrial standard VLbus, is a 32-bit address, 32-bit data bus. The CW4011 uses the SCLC module to access devices on the Lbus. Devices on the Lbus access the DRAM main memory through the SCLC module and the DRAM Controller.

The CW4011 microprocessor generally has ownership of the SCbus and the Lbus. When a device on the Lbus wants to access the DRAM, it asserts the bus hold request signal on the Lbus. The SCLC module

detects the asserted signal and then asserts the bus hold request to the CW4011. The CW4011 asserts the grant signal to the SCLC module, and the SCLC module then asserts the hold acknowledge signal to the Lbus device. 'SCbus and Local I/O Bus Converter Module" provides detailed information about the Lbus.

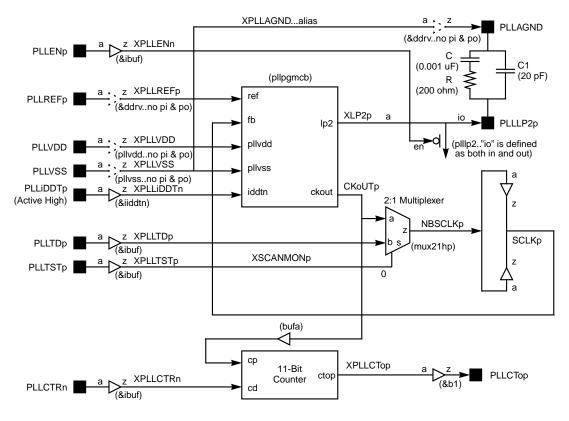

## 2.4 PLL Clock Circuit

The PLL circuit is an LSI Logic PLL cell (pllpgmcb) part that drives the clock signals to the CW4011 shell and the other modules that are part of the LR4500. The system clock, SCLKp, drives the PLLREFp input.

Figure 2.1 on page 2-2 shows the relationship between the PLL circuit and the other LR4500 modules. Figure 2.2 shows the layout of the LR4500 PLL circuit.

When using the PLL circuit, you must observe the following design requirements:

- Provide capacitance devices.

- ♦ Provide a resistor between PLLLP2p and PLLAGND.

- ♦ Connect other PLL circuit inputs to V<sub>DD</sub> or GND.

- ♦ Leave PLLCTop outputs open.

For more information about the PLL circuit, refer to the LSI Logic  $G10^{\text{®}}$ -p Cell-Based ASIC Products Design Manual and G10-p Cell-Based ASIC Products Databook.

PLL Clock Circuit 2-5

Figure 2.2 LR4500 PLL Circuit Diagram

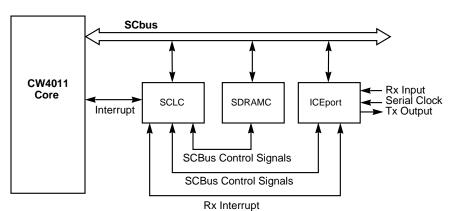

# 2.5 ICEport UART

The ICEport is a full-duplex serial UART port. It is used for downloading application software and debugging the LR4500. The ICEport works with an ICE controller at baud rates up to 1 MBaud, and it is integrated with the SCLC and DRAM controller modules on the SCbus. 'ICEport' 'ICEport' provides detailed information about the ICEport UART.

# 2.6 Pipeline Architecture

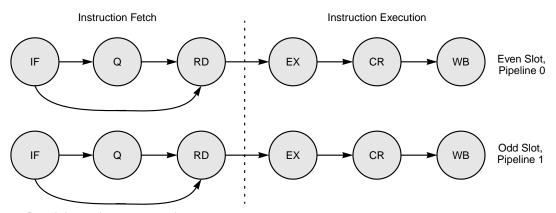

The LR4500 has two identical concurrent five-stage pipelines that are part of the CW4011 core. These pipelines provide the LR4500 with its superscalar capabilities. As shown in Figure 2.3, there is an even pipeline and an odd pipeline.

Each of the five pipeline stages can be viewed as a pair of instruction "slots" (one slot for each pipeline.) So an instruction in the even pipeline at the EX stage may be referred to as 'the even slot of the EX stage.' In addition to the five basic pipeline stages, each pipeline also has a conditional queuing stage (Q).

Figure 2.3 LR4500 Instruction Pipeline

- 1. Branch instruction encountered.

- 2. Q state bypassed.

The first two pipeline stages and the queuing stage are used during instruction fetch, and the last three stages are used during instruction execution. Once a stage has accepted an instruction from the previous stage it must hold the instruction for re-execution in case the pipeline stalls. The pipeline stages perform the following functions:

- IF (Instruction Fetch). The LR4500 fetches the instruction during the first stage.

- Q (Queuing). This conditional queueing stage boosts branch instructions. Depending on the branches and register conflicts, instructions may either enter this stage or be advanced straight to the RD stage.

- ♦ RD (Read). During this stage, any required operands are read from the Register File while the instruction is being decoded.

- EX (Execution). This stage performs a number of functions: all instructions are executed, conditional branches are resolved, the address calculation for load and store instructions is performed.

- CR (Cache Read). This stage is used to access the cache for load and store instructions. Data is returned to the register bypass logic at the end of this stage.

- WB (Write Back). Results are written into the Register File during this stage.

For a more detailed description of the CW4011 pipeline, refer to the *MiniRISC Superscalar Microprocessor Core Technical Manual*.

# **Chapter 3 Programming Model**

This chapter provides information about the LR4500 Microprocessor programming model. The term 'programming model' refers to the way in which data is arranged in registers and in memory.

#### The chapter

- Provides a list of LR4500 registers on page 3-2

- ◆ Describes LR4500 memory mapping on page 3-4

- Describes how to configure the system using LR4500 registers on page 3-5

In addition, the following sections in other chapters of this manual provide supplementary information related to the programming model:

- "DRAM Controller and Memory Bus" on page 6-1

- "SCbus Timeout Watchdog Timer" on page 7-8

- "Cache Configuration and Maintenance" on page 8-1

The MiniRISC CW4011 Superscalar Microprocessor Core Technical Manual describes the Memory Management Unit and Coprocessor 0 (CP0).

# 3.1 Register Set

Table 3.1 lists the LR4500 registers and provides the physical and virtual addresses, and the register numbers. The registers are listed in functional blocks and arranged alphabetically within each functional block.

Table 3.1 LR4500 Registers

| Register Name                                      | Physical<br>Address                    | Virtual<br>Address | Number |

|----------------------------------------------------|----------------------------------------|--------------------|--------|

| CP0 Exception Proces                               | ssing Registers                        |                    |        |

| BadVAddr (Bad Virtual Address)                     | Physical and virtua                    |                    | 8      |

| BDA (Breakpoint Data Address)                      | not applicable to C processing registe |                    | 19     |

| BDAM (Breakpoint Data Address Mask)                |                                        |                    | 21     |

| BPC (Breakpoint Program Counter)                   |                                        |                    | 18     |

| BPCM (Breakpoint PC Mask)                          |                                        |                    | 20     |

| Cause                                              |                                        |                    | 13     |

| CCC (Configuration and Cache Control) <sup>1</sup> |                                        |                    | 16     |

| Compare                                            |                                        |                    | 11     |

| Count                                              |                                        |                    | 9      |

| DCS (Debug Control Status)                         |                                        |                    | 7      |

| EPC (Exception Program Counter)                    |                                        |                    | 14     |

| ErrorPC                                            |                                        |                    | 30     |

| LLAdr (Load Linked Address)                        |                                        |                    | 17     |

| PRId (Processor Revision Identifier)               |                                        |                    | 15     |

| Status                                             |                                        |                    | 12     |

Table 3.1 LR4500 Registers (Cont.)

| Register Name                              | Physical<br>Address      | Virtual<br>Address       | Number |

|--------------------------------------------|--------------------------|--------------------------|--------|

| Lbus Controller                            | Registers                |                          |        |

| External Vectored Interrupt <sup>2</sup>   | 0x 1010 0008             | 0x B010 0008             | N/A    |

| SCbus Error Address <sup>3</sup>           | 0x 1010 0000             | 0x B010 0000             | N/A    |

| SCbus Error Status <sup>4</sup>            | 0x 1010 0004             | 0x B010 0004             | N/A    |

| DRAM Controller                            | Registers                |                          |        |

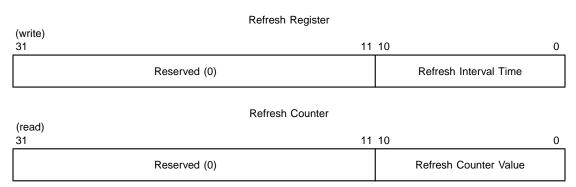

| DRAM Refresh Register <sup>5</sup>         | 0x 1000 0004             | 0x B000 0004             | N/A    |

| DRAM Controller Configuration <sup>6</sup> | 0x 1000 0000             | 0x B000 0000             | N/A    |

| ICEport Reg                                | isters                   | •                        | •      |

| Rx Status <sup>7</sup>                     | 0x10FF 0000 <sup>8</sup> | 0xB0FF 0000 <sup>8</sup> | N/A    |

| Rx Setup <sup>7</sup>                      | 0x10FF 0000 <sup>8</sup> | 0xB0FF 0000 <sup>8</sup> | N/A    |

| Rx Data                                    | 0x10FF 0004              | 0xB0FF 0004              | N/A    |

| Tx Status                                  | 0x10FF 0008              | 0xB0FF 0008              | N/A    |

| Tx Data                                    | 0x10FF 000C              | 0xB0FF 000C              | N/A    |

- 1. See "CCC Register" on page 3-5

- 2. See "External Vectored Interrupt Register" on page 3-11

- 3. See "SCbus Error Address Register" on page 3-10

- 4. See "SCbus Error Status Register" on page 3-10

- 5. See "DRAM Refresh" on page 6-12

- 6. See "DRAM Controller Configuration Register" on page 6-5

- 7. See "ICEport Registers" on page 9-9

- All other registers listed in this table are described in the *MiniRISC CW4011 Superscalar Microprocessor Core Technical Manual*

- 8. The physical address for the Rx Status Register is the same as the physical address for the Rx Setup Register. Similarly, the virtual addresses are the same. The Rx Status Register is a read register and the Rx Setup Register is a write register. This means that when the addresses are accessed, the register accessed depends on the condition of the read/write signal.

Register Set 3-3

# 3.2 Memory Mapping

Figure 3.1 shows the physical memory map of the LR4500 reference device, where the LR4500 is master of the Lbus and an Lbus device is slave, and the physical memory map where an Lbus device is the Lbus master and the LR4500 is slave. In both cases, address spaces are linear 4-Gbyte spaces. Lbus master devices cannot access LR4500 internal memory-mapped registers.

Synchronous DRAM main memory that is interfaced to the LR4500 is located at address space 0x0000 0000 through 0x03FF FFFF. The LR4500 works as an Lbus slave device for this 64-Mbyte memory space. There is no guarantee that memory devices exist in the entire 64-Mbyte area. Software, in the form of a setup/bootstrap utility or equivalent must check installed memory size when the system is initialized. The upper 192-Mbyte space is reserved as an extended main memory area.

LR4500 internal registers for DRAM Controller and error reporting are located in the Internal Registers area between addresses 0x1000 0000 and 0x10FF FFFF. These registers must be accessed through *kseg1*, the uncached unmapped area. The virtual address for these registers is 0xB000 0000 through 0xB0FF FFFF.

LR4500 Master Address Map LR4500 Slave Address Map Highest Order 0xFFFF FFFF 0xFFFF FFFF Lbus Access Area Lbus Access Area 0x1100 0000 0x1100 0000 Internal Register Area Unusable Area 0x1000 0000 0x1000 0000 Reserved Main Memory Area Reserved Main Memory Area 0x0400 0000 0x0400 0000 DRAM Main Memory Area DRAM Main Memory Area Lowest Order 0x0000 0000 Address 0x0000 0000

Figure 3.1 LR4500 Master/Slave Memory Map

# 3.3 System Configuration

LR4500 has a number of features that allow you to modify the system configuration. This section describes the Configuration and Cache Control (CCC) Register, which is part of the CW4011 core, and several Lbus registers, which are part of the SCLC module. You can also configure the DRAM, as described in Chapter 6, "DRAM Controller and Memory Bus."

# 3.3.1 CCC Register

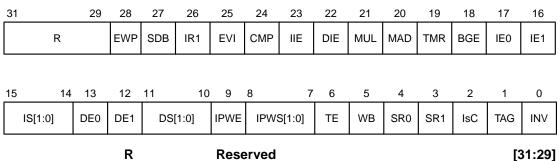

The Configuration and Cache Control (CCC) Register is part of CP0, the system coprocessor. The CCC Register allows you to use software to configure various pieces of the core design, such as the Bus Interface Unit (BIU) and the controllers for the I-cache and D-cache.

You can read from the CCC Register using the MFC0 instruction, and write to it using the MTC0 instruction. Table 4.14 on page 4-14 describes these instructions. The register's address in CP0 is '16.' Figure 3.2 shows the bit configuration of the CCC Register. All bits are initialized to 0 at reset, so that the caches are not available until the register is programmed.

Figure 3.2 CCC Register

This field is reserved. The bits are cleared to 0.

EWP External Write Priority 28

This bit defines the arbitration priority on the SCbus between a data read and data write transaction in the

4-deep write buffer. Clearing the bit to 0 gives a higher priority to a data read request if the read address does not match the write address in the write buffer. Setting the bit to 1 gives higher priority to data write transactions.

#### SDB Scan Debug

27

This bit is reserved. It must be set to 0.

#### IR1 I-cache Scratchpad RAM

26

Setting this bit to 1 enables scratchpad RAM mode in Set-1 of the I-cache. Clearing it to 0 disables scratchpad RAM mode.

#### EVI External Vectored Interrupt

25

This bit enables and disables external vectored interrupt. Setting the bit to 1 enables the interrupt and clearing it to 0 disables the interrupt.

#### CMP R3000 Compatibility

24

This bit enables and disables R3000 compatibility mode. Setting the bit to 1 enables the mode and clearing it to 0 disables the mode.

#### IIE I-cache Invalidate Enable

23

This bit enables and disables the I-cache invalidate request. Setting the bit to 1 enables the request and clearing it to 0 disables the request.

#### DIE D-cache Invalidate Enable

22

This bit enables and disables the D-cache invalidate request. Setting the bit to 1 enables the request and clearing the bit to 0 disables the request.

#### MUL Multiplier

21

This bit enables and disables the hardware multiplier. Setting the bit to 1 enables the multiplier and clearing the bit to 0 disables the multiplier.

### MAD Multiply Accumulate

20

This bit allows the multiplier to support accumulate extensions. Setting the bit to 1 enables the feature and clearing the bit disables the feature. When this bit is set, MUL must also be set.

#### TMR Timer

Setting this bit to 1 enables the timer facility associated with the CW4011 core's Count and Compare Registers. When this bit is set, and the value of the Count Register equals the value of the Compare Register, interrupt bit IP7 in the Cause Register is set. IP7 causes an interrupt in the next execution cycle, provided that interrupts are enabled by setting the Interrupt Enable bit in the Status Register to 1 and clearing the Error Level and Exception Level bits in the Status Register to 0.

#### BGE BIU Bus Grant Enable

18

19

This bit enables and disables the BIU bus grant. Setting this bit to 1 enables the external bus master. Clearing it to 0 causes the CW4011 core to ignore the external bus master.

#### IEO I-cache Set-0 Enable

17

This bit enables and disables Set-0 of the I-cache. Setting the bit to 1 enables Set-0 and clearing the bit to 0 disables Set-0.

#### IE1 I-cache Set-1 Enable

16

This bit enables and disables Set-1 of the I-cache. Setting the bit to 1 enables Set-1 and clearing the bit to 0 disables Set-1.

#### IS[1:0] I-cache Size

[15:14]

The IS[1:0] field determines the size of each I-cache set. The field settings are defined as follows:

| IS1 | IS0 | Cache Set Size |

|-----|-----|----------------|

| 0   | 0   | 1 Kbyte        |

| 0   | 1   | 2 Kbyte        |

| 1   | 0   | 4 Kbyte        |

| 1   | 1   | 8 Kbyte        |

#### DE0 D-cache Set-0 Enable

13

This bit enables and disables Set-0 of the D-cache. Setting the bit to 1 enables Set-0 and clearing the bit to 0 disables Set-0.

#### DE1 D-cache Set-1 Enable

This bit enables and disables Set-1 of the D-cache. Setting the bit to 1 enables Set-1 and clearing it to 0 disables Set-1.

#### DS[1:0] D-cache Size

[15:14]

12

The DS[1:0] field determines the size of each D-cache set. The field settings are defined as follows:

| DS1 | DS0 | Cache Set Size |

|-----|-----|----------------|

| 0   | 0   | 1 Kbyte        |

| 0   | 1   | 2 Kbyte        |

| 1   | 0   | 4 Kbyte        |

| 1   | 1   | 8 Kbyte        |

#### IPWE In-Page Write Enable

9

This bit enables and disables in-page write operations. Setting the bit to 1 enables in-page write and clearing it to 0 disables in-page write.

#### IPWS[1:0] In-Page Write Size

[8:7]

The IPWS[1:0] field determines the size of the I-cache set. The field settings are defined as follows:

| IPWS1 | IPWS0 | In-Page Write Size |

|-------|-------|--------------------|

| 0     | 0     | 1 Kbyte            |

| 0     | 1     | 2 Kbyte            |

| 1     | 0     | 4 Kbyte            |

| 1     | 1     | 8 Kbyte            |

#### TE TLB Enable

6

This bit enables and disables the TLB. Since the LR4500 does not support a full TLB, this bit has no effect.

#### WB Write Back

5

This bit defines the caching algorithm, for *kseg0*. It also defines the caching algorithm for kuseg and *kseg2* if there is no TLB or if the TLB is disabled. Setting the bit to 1 enables a write back operation and clearing the bit to 0 enables a write through operation.

#### SR0 Scratchpad RAM Mode Set-0

This bit enables and disables scratchpad RAM mode for Set-0 of the D-cache. Setting the bit to 1 enables scratchpad mode and clearing it to 0 disables scratchpad mode.

#### SR1 Scratchpad RAM Mode Set-1

This bit enables and disables scratchpad RAM mode for Set-1 of the D-cache. Setting the bit to 1 enables scratchpad mode and clearing it to 0 disables scratchpad mode.

#### IsC Isolate Cache

This bit enables isolate cache mode. This means that stores to the cache are not propagated to external memory. Setting the bit to 1 enables the mode and clearing the bit to 0 disables the mode.

#### TAG Tag Test Mode

This bit enables and disables tag test mode, which is used for cache maintenance. Setting the bit to 1 enables the mode, which means that load and store operations access the Tag RAMs and sample the tag bits Tag Data, Hit, Write Back (D-cache only), and Valid. Clearing the bit to 0 disables tag test mode. This bit is used when IsC = 1.

#### INV Invalidate Cache Mode

This bit enables and disables invalidate cache mode, which is used for cache maintenance. Setting the bit to 1 enables the mode. Clearing the bit to 0 disables invalidate cache mode. This bit is used with IsC = 1.

# 3.3.2 Lbus Controller Registers

The Lbus controller has three 32-bit registers that store information about SCbus errors and interrupts. They are the SCbus Error Status Register, the SCbus Error Address Register, and the External Vectored Interrupt Register. You must access these registers through *kseg1*. Access to an unused address causes an SCbus timeout error.

3

2

1

0

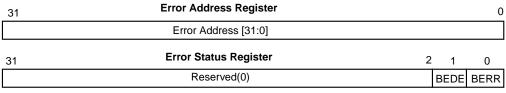

#### 3.3.2.1 SCbus Error Status Register

The SCbus Status Register stores the bus error detect enable bit, BEDE, and the bus error detected bit, BERR. The register's virtual address is 0xB010 0004 and its physical address is 0x1010 0004. For further information about this register, refer to "SCbus Timeout Watchdog Timer" on page 7-8.

Figure 3.3 SCbus Status Register

| 31 |          | 2                                                                                            | 2 1    | 0                  |

|----|----------|----------------------------------------------------------------------------------------------|--------|--------------------|

|    |          | Reserved (0)                                                                                 | BEDE   | BERR               |

|    | Reserved | Reserved This field is reserved. The bits are cleared to                                     |        | [31:2]             |

|    | BEDE     | Bus Error Detect Enable When this bit is set to 1, the LR4500 is enabled to de SCbus errors. |        | 1<br>detect        |

|    | BERR     | Bus Error This bit is set to 1 when a bus error has bee                                      | n dete | <b>0</b><br>ected. |

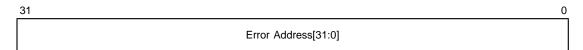

### 3.3.2.2 SCbus Error Address Register

The SCbus Error Address Register stores the address of the transaction that has caused the bus error. The address remains stored during the period that the bus error bit, BERR, is set. The register's virtual address is 0xB010 0000 and its physical address is 0x1010 0000. For further information about this register, refer to "SCbus Timeout Watchdog Timer" on page 7-8.

Figure 3.4 SCbus Error Address Register

### 3.3.2.3 External Vectored Interrupt Register

The External Vectored Interrupt Register supports the LR4500 interrupt exception feature called External Vectored Interrupt. The register's virtual address is 0xB010 0008 and its physical address is 0x1010 0008. For further information about this register, refer to "SCbus Timeout Watchdog Timer" on page 7-8.

Figure 3.5 External Vectored Interrupt Register

| 31 |            | 2                                                                                                                                                                                                         | 2 1    | 0           |

|----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|

|    |            | EVIA[31:2]                                                                                                                                                                                                | HEVI   | SEVI        |

|    | EVIA[31:2] | External Vectored Interrupt Address This field contains the exception vector address.  Hardware External Vectored Interrupt This bit is set when the error that caused the interrupt is a hardware error. |        |             |

|    | HEVI       |                                                                                                                                                                                                           |        |             |

|    | SEVI       | Software External Vectored Interrupt This bit is set when the error that caused the a software error.                                                                                                     | interr | 1<br>upt is |

# Chapter 4 Instruction Set

This chapter provides information about the LR4500 instruction set. It includes:

- A list of the LR4500 instructions and a definition of each instruction.

- Definitions of the instruction set extensions.

- CPU instruction opcode bit encoding.

# 4.1 Instruction Set

Table 4.14 lists and describes the instructions that make up the LR4500 instruction set. The chip supports both MIPS I and 32-bit MIPS II instructions and also implements additional extended instructions that are specific to the LR4500.

The instructions are arranged alphabetically within the following functional groups:

- ◆ Load and Store Instructions, in Table 4.1 on page 4-2

- ◆ Load Linked MIPS II Instructions, in Table 4.2 on page 4-3

- ALU Immediate Instructions, in Table 4.3 on page 4-4

- ALU Three-Operand Register Type Instructions, in Table 4.4 on page 4-5

- ♦ Shift Instructions, in Table 4.5 on page 4-6

- Multiply/Divide Instructions, in Table 4.6 on page 4-7

- ♦ Extended Computational Instructions, in Table 4.7 on page 4-8

- ◆ Jump Instructions, in Table 4.8 on page 4-9

- ♦ Branch Instructions, in Table 4.9 on page 4-10

- ♦ Branch Likely Instructions, in Table 4.10 on page 4-11

- ◆ Trap Instructions, in Table 4.11 on page 4-12

- ♦ Special Instructions, in Table 4.12 on page 4-13

- ♦ CP0 Instructions, in Table 4.13 on page 4-13

- ♦ Cache Maintenance Instructions, in Table 4.14 on page 4-14

Table 4.1 describes the load and store instructions.

**Table 4.1 Load and Store Instructions**

| Instruction            | Format and Description                                                                                                                                                                                                                                                              |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Byte              | LB rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Sign extend the contents of addressed byte and load into rt.                                                                                                            |

| Load Byte Unsigned     | LBU rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Zero extend the contents of addressed byte and load into rt.                                                                                                           |

| Load Halfword          | LH rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Sign extend the contents of addressed halfword and load into rt.                                                                                                        |

| Load Halfword Unsigned | LHU rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Zero extend contents of addressed halfword and load into rt.                                                                                                           |

| Load Word              | LW rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address, and load the addressed word into rt.                                                                                                                                    |

| Load Word Left         | LWL rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Shift addressed word left so that addressed byte is left most byte of a word. Merge bytes from memory with contents of register rt and load result into register rt.   |

| Load Word Right        | LWR rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Shift addressed word right so that addressed byte is right most byte of a word. Merge bytes from memory with contents of register rt and load result into register rt. |

Table 4.1 Load and Store Instructions (Cont.)

| Instruction      | Format and Description                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Store Byte       | SB rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Store least significant byte of register rt at addressed location.                                                                                                                      |

| Store Halfword   | SH rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Store least significant halfword of register rt at addressed location.                                                                                                                  |

| Store Word       | SW rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Store contents of register rt at addressed location.                                                                                                                                    |

| Store Word Left  | SWL rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Shift contents of register rt left so that the left most byte of the word is in the position of the addressed byte. Store word containing shifted bytes into word at addressed byte.   |

| Store Word Right | SWR rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Shift contents of register rt right so that the right most byte of the word is in the position of the addressed byte. Store word containing shifted bytes into word at addressed byte. |

Table 4.2 describes the load linked MIPS II instructions.

Table 4.2 Load Linked MIPS II Instructions

| Instruction       | Format and Description                                                                                                                                                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Linked       | LL rt, offset(base) Sign extend the 16-bit offset and add to the contents of the register base to form the address. Load the addressed word into register rt.                                                         |

| Store Conditional | SC rt, offset(base) Sign extend the 16-bit offset and add to the contents of the register base to form the address. Conditionally store register rt at the address, based on whether the load-link has been "broken." |

| Synchronize       | SYNC Complete all outstanding load and store instructions before allowing any new load or store instruction to start.                                                                                                 |

Table 4.3 describes the ALU immediate instructions.

**Table 4.3 ALU Immediate Instructions**

| Instruction                            | Format and Description                                                                                                                                                                                    |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add Immediate                          | ADDI rt, rs, immediate Add 16-bit, sign extended immediate to register rs and place 32-bit result in register rt. Trap on two's complement overflow.                                                      |

| Add Immediate<br>Unsigned              | ADDIU rt, rs, immediate Add 16-bit, sign extended immediate to register rs and place 32-bit result in register rt. Do not trap on overflow.                                                               |

| AND Immediate                          | ANDI rt, rs, immediate Zero extend 16-bit immediate, AND with contents of register rs, and place result in register rt.                                                                                   |

| Exclusive OR Immediate                 | XORI rt, rs, immediate Zero extend 16-bit immediate, exclusive OR with contents of register rs, and place result in register rt.                                                                          |

| Load Upper Immediate                   | LUI rt, immediate Shift 16-bit immediate left 16 bits. Set least-significant 16 bits of word to zeros. Store result in register rt.                                                                       |

| OR Immediate                           | ORI rt, rs, immediate Zero extend 16-bit immediate, OR with contents of register rs, and place result in register rt.                                                                                     |

| Set on Less than<br>Immediate          | SLTI rt, rs, immediate Compare 16-bit, sign extended immediate with register rs as signed 32-bit integers. Result = 1 if rs is less than immediate; otherwise result = 0. Place result in register rt.    |

| Set on Less than<br>Immediate Unsigned | SLTIU rt, rs, immediate Compare 16-bit, sign extended immediate with register rs as unsigned 32-bit integers. Result = 1 if rs is less than immediate; otherwise result = 0. Place result in register rt. |

Table 4.4 describes the ALU three-operand register type instructions.

**Table 4.4 ALU Three-Operand Register Type Instructions**

| Instruction                  | Format and Description                                                                                                                             |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Add                          | ADD rd, rs, rt Add contents of registers rs and rt and place 32-bit result in register rd. Trap on two's complement overflow.                      |

| Add Unsigned                 | ADDU rd, rs, rt Add contents of registers rs and rt and place 32-bit result in register rd. Do not trap on overflow.                               |

| AND                          | AND rd, rs, rt Bitwise AND contents of registers rs and rt and place result in register rd.                                                        |

| Exclusive OR                 | XOR rd, rs, rt Bitwise exclusive OR contents of registers rs and rt and place result in register rd.                                               |

| NOR                          | NOR rd, rs, rt Bitwise NOR contents of registers rs and rt and place result in register rd.                                                        |

| OR                           | OR rd, rs, rt Bitwise OR contents of registers rs and rt and place result in register rd.                                                          |

| Set on Less than             | SLT rd, rs, rt Compare contents of registers rt and rs (as signed, 32-bit integers). If register rs is less than rt, rd = 1; otherwise, rd = 0.    |

| Set on Less than<br>Unsigned | SLTU rd, rs, rt Compare contents of registers rt and rs (as unsigned, 32-bit integers). If register rs is less than rt, rd = 1; otherwise, rd = 0. |

| Subtract                     | SUB rd, rs, rt Subtract contents of registers rt from rs and place 32-bit result in register rd. Trap on two's complement overflow.                |

| Subtract Unsigned            | SUBU rd, rs, rt Subtract contents of register rt from rs and place 32-bit result in register rd. Do not trap on overflow.                          |

Table 4.5 describes the shift instructions.

**Table 4.5 Shift Instructions**

| Instruction                        | Format and Description                                                                                                                                                                                    |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift Left Logical                 | SLL rd, rt, shamt Shift contents of register rt left by shamt bits, inserting zeros into low- order bits. Place 32-bit result in register rd.                                                             |

| Shift Left Logical<br>Variable     | SLLV rd, rt, rs Shift contents of register rt left. Low-order 5 bits of register rs specify the number of bits to shift. Insert zeros into low-order bits of rt and place 32-bit result in register rd.   |

| Shift Right Arithmetic             | SRA, rd, rt, shamt Shift contents of register rt right by shamt bits, sign extending the high-order bits. Place 32-bit result in register rd.                                                             |

| Shift Right Arithmetic<br>Variable | SRAV rd, rt, rs Shift contents of register rt right. Low-order 5 bits of register rs specify the number of bits to shift. Sign extend the high-order bits of rt and place 32-bit result in register rd.   |

| Shift Right Logical                | SRL rd, rt, shamt Shift contents of register rt right by shamt bits, inserting zeros into high-order bits. Place 32-bit result in register rd.                                                            |

| Shift Right Logical<br>Variable    | SRLV rd, rt, rs Shift contents of register rt right. Low-order 5 bits of register rs specify the number of bits to shift. Insert zeros into high-order bits of rt and place 32-bit result in register rd. |

Table 4.6 describes the multiply/divide instructions.

**Table 4.6 Multiply/Divide Instructions**

| Instruction       | Format and Description                                                                                                                                                                                                                |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Divide            | DIV rs, rt Divide contents of registers rs by the contents of rt as two's complement values. Place the 32-bit quotient in special register EntryLo and the 32-bit remainder in EntryHi.                                               |

| Divide Unsigned   | DIVU rs, rt Divide contents of registers rs by the contents of rt as unsigned values. Place the 32-bit quotient in special register EntryLo and the 32-bit remainder in EntryHi.                                                      |

| Move from HI      | MFHI rd Move contents of special register EntryHi to register rd.                                                                                                                                                                     |

| Move from LO      | MFLO rd Move contents of special register EntryLo to register rd.                                                                                                                                                                     |

| Move to HI        | MTHI rs Move contents of register rs to special register EntryHi.                                                                                                                                                                     |

| Move to LO        | MTLO rs Move contents of register rd to special register EntryLo.                                                                                                                                                                     |

| Multiply          | MULT rs, rt Multiply contents of registers rs and rt as two's complement values. Place the 64-bit results in special registers EntryHi and EntryLo. (The EntryLo and EntryHi Registers are read/write registers that access the TLB.) |

| Multiply Unsigned | MULTU rs, rt Multiply contents of registers rs and rt as unsigned values. Place 64-bit results in special registers EntryHi and EntryLo.                                                                                              |

Table 4.7 describes the extended computational instructions.

**Table 4.7 Extended Computational Instructions**

| Instruction                   | Format and Description                                                                                                                                                                                                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add Circular Immediate        | ADDCIU rt, rs, immediate The 16-bit immediate is sign extended and added to the contents of general register rs, with the result masked by the value in CP0's CMask Register according to the formula: $ \text{rt} = (\text{rs}_{31\text{cmask}}) \mid (\text{rs} + \text{signextended\_imed})_{\text{cmask}} - 10) $ |

| Find First Clear Bit          | FFC rd, rs Starting at the most significant bit in register rs, find the first bit which is set to 0, and return the bit number in register rd. If no bit is set, return with all bits of rd set to 1.                                                                                                                |

| Find First Set Bit            | FFS rd, rs Starting at the most significant bit in register rs, find the first bit which is set to 1, and return the bit number in register rd. If no bit is set, return with all bits of rd set to 1.                                                                                                                |

| Maximum                       | MAX rd, rs, rt Compare the contents of registers rs and rt as two's complement values. The larger value is stored in register rd.                                                                                                                                                                                     |

| Minimum                       | MIN rd, rs, rt Compare the contents of registers rs and rt as two's complement values. The smaller value is stored in register rd.                                                                                                                                                                                    |

| Multiply/Add                  | MADD rs, rt Multiply contents of registers rs and rt as two's complement values. Add 64-bit results to the contents of the EntryLo Register and EntryHi Register, and place the results in EntryLo and EntryHi. (The EntryLo and EntryHi Registers are read/write registers that access the TLB.)                     |

| Multiply/Add Unsigned         | MADDU rs, rt Multiply contents of registers rs and rt as unsigned values. Add 64-bit results to the contents of the EntryLo Register and EntryHi Register, and place the results in EntryLo and EntryHi.                                                                                                              |

| Multiply/Subtract             | MSUB rs, rt Multiply contents of registers rs and rt as two's complement values. Subtract the 64-bit results from the contents of the EntryLo Register and EntryHi Register, and place the results in EntryLo and EntryHi.                                                                                            |

| Multiply/Subtract<br>Unsigned | MSUBU rs, rt Multiply contents of registers rs and rt as unsigned values. Subtract the 64-bit results from the contents of the EntryLo Register and EntryHi Register, and place the results in EntryLo and EntryHi.                                                                                                   |

| (Sheet 1 of 2)                |                                                                                                                                                                                                                                                                                                                       |

**Table 4.7 Extended Computational Instructions (Cont.)**

| Instruction            | Format and Description                                                                                                                                                                                                                                                                              |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select and Shift Left  | SELSL rd, rs, rt Using register rs and rt as a 64-bit register pair, and the contents of the CP0's Rotate Register as the shift count, shift the register pair rs/rt left the number of bits specified in the Rotate Register, and place the most significant 32-bit value in result register rd.   |

| Select and Shift Right | SELSR rd, rs, rt Using register rs and rt as a 64-bit register pair, and the contents of the CP0's Rotate Register as the shift count, shift the register pair rs/rt right the number of bits specified in the Rotate Register, and place the least significant 32-bit value in result register rd. |

| (Sheet 2 of 2)         |                                                                                                                                                                                                                                                                                                     |

Table 4.8 describes the jump instructions.

# **Table 4.8 Jump Instructions**

| Instruction            | Format and Description                                                                                                                                                                                                     |