## LM2685

# **Dual Output Regulated Switched Capacitor Voltage Converter**

### **General Description**

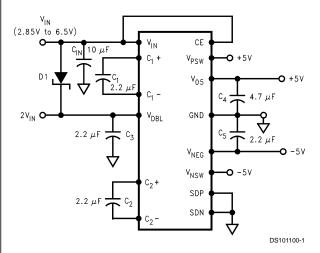

The LM2685 CMOS charge-pump voltage converter operates as an input voltage doubler, +5V regulator and inverter for an input voltage in the range of +2.85V to +6.5V. Five low cost capacitors are used in this circuit to provide up to 50mA of output current at +5V ( $\pm$ 5%), and 15mA at -5V. The LM2685 operates at a 130 kHz switching frequency to reduce output resistance and voltage ripple. With an operating current of only  $800\mu A$  (operating efficiency greater than 80% with most loads) and  $6\mu A$  typical shutdown current, the LM2685 is ideal for use in battery powered systems. The device is in a small 14-pin TSSOP package.

#### **Features**

- +5V regulated output

- Inverts  $V_{05}(+5V)$  to  $V_{NEG}(-5V)$

- Doubles input supply voltage

- TSSOP-14 package

- 80% typical conversion efficiency at 25mA

- Input voltage range of 2.85V to 6.5V

- Independent shutdown control pins

### **Applications**

- Cellular phones

- Pagers

- PDAs

- Handheld instrumentation

- 3.3V to 5V voltage conversion applications

## **Typical Application and Connection Diagram**

## **Ordering Information**

| Order Number | Package Type | NSC Package<br>Drawing | Supplied As               |  |

|--------------|--------------|------------------------|---------------------------|--|

| LM2685MTC    | TSSOP-14     | MTC14                  | 94 Units, Rail            |  |

| LM2685MTCX   | TSSOP-14     | MTC14                  | 2.5k Units, Tape and Reel |  |

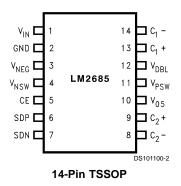

## **Pin Description**

| Pin No. | Name                        | Function                                                                                                                                                                                                                             |  |

|---------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | V <sub>IN</sub>             | Power supply input voltage.                                                                                                                                                                                                          |  |

| 2       | GND                         | Power supply ground.                                                                                                                                                                                                                 |  |

| 3       | $V_{NEG}$                   | Negative output voltage created by inverting V <sub>05</sub> .                                                                                                                                                                       |  |

| 4       | V <sub>NSW</sub>            | V <sub>NEG</sub> output connected through a series switch, NSW.                                                                                                                                                                      |  |

| 5       | CE                          | Chip enable input. This pin is high for normal operation and low for shutdown. (See Shutdown and Load Disconnect section in the Detailed Device Description division).                                                               |  |

| 6       | SDP                         | Positive side shutdown input. This pin is low for normal operation and high for positive side shutdown and V <sub>PSW</sub> load disconnect. (See Shutdown and Load Disconnect section in the Detailed Device Description division). |  |

| 7       | SDN                         | Negative side shutdown input. This pin is low for normal operation and high for negative side shutdown and V <sub>NSW</sub> load disconnect. (See Shutdown and Load Disconnect section in the Detailed Device Description division). |  |

| 8       | C <sub>2</sub> -            | The negative terminal of inverting charge-pump capacitor, C2.                                                                                                                                                                        |  |

| 9       | C <sub>2</sub> +            | The positive terminal of inverting charge-pump capacitor, C2.                                                                                                                                                                        |  |

| 10      | V <sub>05</sub>             | Regulated +5V output.                                                                                                                                                                                                                |  |

| 11      | V <sub>PSW</sub>            | V <sub>05</sub> output connected through a series switch, PSW.                                                                                                                                                                       |  |

| 12      | $V_{DBL}$                   | Voltage Doubler Output. (2.85V $\leq$ V <sub>IN</sub> $\leq$ 5.4V. See Voltage Doubler section).                                                                                                                                     |  |

| 13      | C <sub>1</sub> <sup>+</sup> | The positive terminal of doubling charge-pump capacitor, C1.                                                                                                                                                                         |  |

| 14      | C <sub>1</sub> -            | The negative terminal of doubling charge-pump capacitor, C1.                                                                                                                                                                         |  |

www.national.com

2kV

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (VIN to GND or

GND to  $V_{NEG}$ ) 6.8V SDN, SDP, CE (GND - 0.3V) to

$(V_{IN} + 0.3V)$

V<sub>05</sub> Continuous Output Current

80mA

V<sub>05</sub> Short-Circuit Duration to GND

(Note 2)

(Note 2) Indefinite

Continuous Power Dissipation (TA

ESD Rating (Note 4)

### **Electrical Characteristics**

Limits with standard typeface apply for  $T_J=25^{\circ}C$ , and limits in **boldface type** apply over the full temperature range. Unless otherwise specified  $V_{IN}=3.6V$ ,  $C_1=C_2=C_3=C_5=2.2\mu F$ .  $C_4=4.7\mu F$  (Note 5)

| Symbol               | Parameter                                                     | Conditions                                                 | Min   | Тур  | Max   | Units |

|----------------------|---------------------------------------------------------------|------------------------------------------------------------|-------|------|-------|-------|

| V+                   | Supply Voltage                                                |                                                            | 2.85  |      | 6.5   | V     |

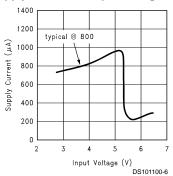

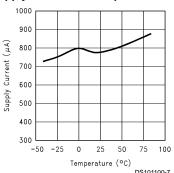

| Ι <sub>Q</sub>       | Supply Current                                                | No Load                                                    |       | 800  | 1600  | μΑ    |

|                      |                                                               | No Load, V <sub>IN</sub> = 6.5V                            |       | 300  | 600   |       |

| I <sub>SD</sub>      | Shutdown Supply Current                                       | V <sub>IN</sub> = 6.5V                                     |       | 6    | 30    | μΑ    |

| V <sub>SD</sub>      | Shutdown Pin Input Voltage for                                | Logic Input High @ 6.5V                                    | 2.4   |      |       | V     |

|                      | CE, SDP, SDN                                                  | Logic Input Low @ 6.5V                                     |       |      | 0.8   |       |

| I <sub>L</sub> (+5V) | Output Current at V <sub>05</sub>                             | 2.85V < V <sub>IN</sub> < 6.5V                             |       |      | 50    | mA    |

| R <sub>O</sub> (-5V) | Output Resistance at V <sub>NEG</sub>                         | I <sub>L</sub> = 15mA (Note 6)                             |       | 20   | 40    | Ω     |

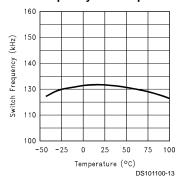

| F <sub>sw</sub>      | Switch Frequency                                              |                                                            | 85    | 130  | 180   | kHz   |

| P <sub>EFF</sub>     | Average Power Efficiency at V <sub>05</sub>                   | $2.85V \le V_{IN} \le 6.5V$<br>$I_L = 25mA \text{ to GND}$ |       | 82   |       | %     |

| V <sub>05</sub>      | Output Regulation                                             | $1mA < I_L < 50mA, V_{IN} = 6.5V$ (Note 7)                 | 4.848 | 5.05 | 5.252 | V     |

|                      |                                                               | $1mA < I_L < 50mA, V_{IN} = 6.5V$ (Note 7)                 | 4.797 | 5.05 | 5.303 |       |

| G <sub>LINE</sub>    | Line Regulation                                               | 2.85V < V <sub>IN</sub> < 3.6V                             |       | 0.25 |       | %/V   |

|                      |                                                               | 3.6V < V <sub>IN</sub> < 6.5V                              |       | 0.05 |       |       |

| G <sub>LOAD</sub>    | Load Regulation                                               | $1 \text{mA} < I_L < 50 \text{mA}, V_{IN} = 6.5 \text{V}$  |       | 0.3  | 1.0   | %     |

| R <sub>sw</sub>      | Series Switch Resistance $V_{\text{NEG}}$ to $V_{\text{NSW}}$ | V <sub>IN</sub> > 2.85V                                    |       | 1.5  |       | Ω     |

|                      | V <sub>05</sub> to V <sub>PSW</sub>                           |                                                            |       | 5.0  |       |       |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2:  $V_{05}$  may be shorted to GND without damage. However, shorting  $V_{NEG}$  to  $V_{05}$  may damage the device and must be avoided. Also, for temperature above 85°C,  $V_{05}$  must not be shorted to GND or device may be damaged.

Note 3: The maximum allowable power dissipation is calculated by using  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$ , where  $T_{JMAX}$  is the maximum junction temperature,  $T_A$  is the ambient temperature and  $\theta_{JA}$  is the junction-to-ambient thermal resistance of the specified package.

Note 4: The human body model is a 100 pF capacitor discharged through a  $1.5 k\Omega$  resistor into each pin.

Note 5: In the typical operating circuit, capacitors  $C_1$  and  $C_2$  are  $2.2\mu F$ ,  $0.3\Omega$  maximum ESR capacitors. Capacitors with higher ESR will increase output resistance, reduce output voltage and efficiency.

Note 6: Specified output resistance includes internal switch resistance and ESR of capacitors. See the Detailed Device Description section.

Note 7: The 50 mA maximum current assumes no current is drawn from V<sub>DBL</sub> pin. See Voltage Doubler section in the Detailed Device Description.

## Typical Performance Characteristics Unless otherwise specified, T<sub>A</sub> = 25°C, V<sub>IN</sub> = 3.6V.

#### Supply Current vs Input Voltage

#### **Supply Current vs Temperature**

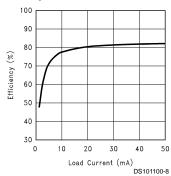

#### Efficiency vs Load Current

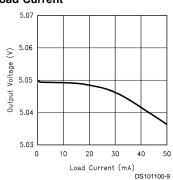

## Output Voltage (V<sub>05</sub>) vs. Load Current

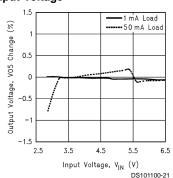

#### V<sub>05</sub> Voltage vs. Input Voltage

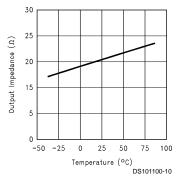

## Output Resistance (VNEG) vs. Temperature

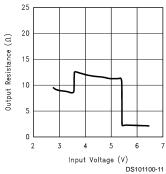

## Output Resistance (VDBL) vs. Input Voltage

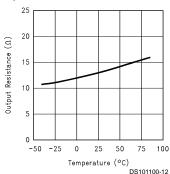

## Output Resistance (VDBL) vs. Temperature

#### Switch Frequency vs. Temperature

## Typical Performance Characteristics Unless otherwise specified, $T_A = 25^{\circ}C$ , $V_{IN} = 10^{\circ}C$

3.6V. (Continued)

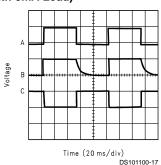

#### Line Transient Response (with 5mA Load)

Time (20 ms/div) DS101100-14

A: INPUT VOLTAGE:  $V_{IN}$  = 3.2V to 6.0V, 5V/div B: OUTPUT VOLTAGE: V<sub>PSW</sub>: 100mV/div C: OUTPUT VOLTAGE:  $V_{NSW}$ : 100mV/div

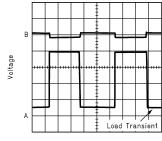

#### V<sub>05</sub> Load Transient Response

Time (20 ms/div) DS101100-15

A: LOAD CURRENT:  $I_{LOAD} = 5mA$  to 39.6mA, 10mA/div

B: OUTPUT VOLTAGE: V<sub>05</sub>: 10mV/div

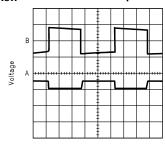

#### **V<sub>NSW</sub> Load Transient Response**

Time (20 ms/div) DS101100-16

A: LOAD CURRENT:  $I_{LOAD} = 4.4$ mA to -9.4mA, 10mA/div

B: OUTPUT VOLTAGE: V<sub>NSW</sub>: 50mV/div

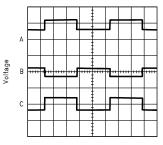

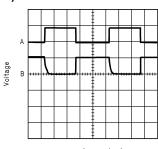

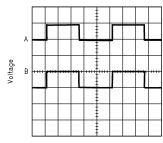

#### $V_{PSW}$ and $V_{NSW}$ Response to CE (with 5mA Load)

A: CE INPUT: 5V/div B: OUTPUT VOLTAGE: V<sub>PSW</sub>: 5V/div C: OUTPUT VOLTAGE: V<sub>NSW</sub>: 5V/div

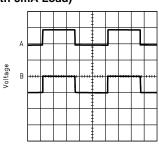

#### V<sub>05</sub> Response to SDP (with 5mA Load)

Time (20 ms/div) DS101100-18

A: SDP INPUT: 5V/div B: OUTPUT VOLTAGE: 5V/div

#### V<sub>NSW</sub> Response to SDP (with 5mA Load)

Time (20 ms/div) DS101100-19

A: SDP INPUT: 5V/div

B: OUTPUT VOLTAGE (V<sub>NSW</sub>): 5V/div

#### **V<sub>NSW</sub>** Response to SDN (with 5mA Load)

Time (20 ms/div)

DS101100-20

A: SDN INPUT: 5V/div

B: OUTPUT VOLTAGE (V<sub>NSW</sub>): 5V/div

### **Detailed Device Description**

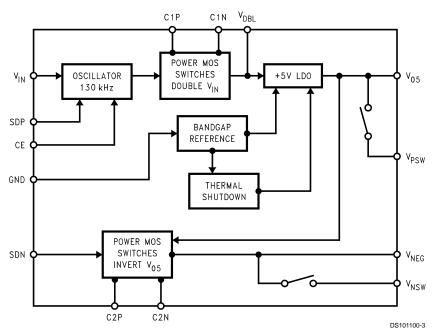

FIGURE 1. Functional Block Diagram

The LM2685 CMOS charge pump voltage converter operates as an input voltage doubler, +5V regulator and inverter for an input voltage in the range of +2.85V to +6.5V. It delivers maximum load currents of 50mA and 15mA for the regulated +5V and the inverted output voltages respectively, with an operating current of only  $800\mu A$ . It also has a typical shutdown current of 6 $\mu A$ . All these performance qualities make the LM2685 an ideal device for battery powered systems.

The LM2685 has three main functional blocks: a voltage doubler, a low dropout (LDO) regulator, and a voltage inverter. *Figure 1* shows the LM2685 functional block diagram.

#### Voltage Doubler

The voltage doubler stage doubles the input voltage  $V_{\rm IN}$ , within the range of +2.85V to +5.4V. For  $V_{\rm IN}$  above 5.4V, the doubler shuts off and the input voltage is passed directly to  $V_{\rm DBL}$  via an internal power switch.

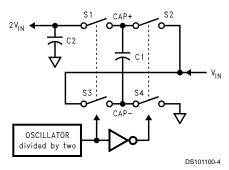

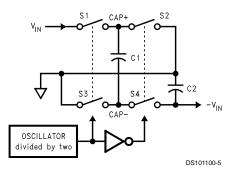

The doubler contains four large CMOS switches which are switched in a sequence to double the input supply voltage. Figure 2 illustrates the voltage conversion scheme. When S2 and S4 are closed, C1 charges to the supply voltage  $V_{\rm IN}$ . During this time interval, switches S1 and S3 are open. In the next time interval, S2 and S4 are opened at the same time, S1 and S3 are closed, the sum of the input voltage  $V_{\rm IN}$  and the voltage across C1 gives the  $2V_{\rm In}$  and the voltage across C2 gives the  $2V_{\rm IN}$  at  $V_{\rm DBL}$  output.  $V_{\rm DBL}$  supplies the LDO regulator. It is recommended not to load  $V_{\rm DBL}$  when  $V_{\rm 05}$  has a load of 50mA. For proper operation, the sum of  $V_{\rm DBL}$  and  $V_{\rm 05}$  loads must not be more than 50mA.

The Schottky diode D1 is only needed for start-up. The internal oscillator circuit uses the  $\rm V_{DBL}$  and GND pins. The voltage across them must be larger than 1.8V to ensure the operation of the oscillator. During start-up, D1 is used to charge up the voltage at  $\rm V_{DBL}$  pin to start the oscillator; it also protects the device from turning on its own parasitic diode and potentially latching up. The diode should have enough current carrying capability to change capacitor C3 at start-up, as well as a low forward voltage to prevent the internal parasitic diode from turning on. A Schottky diode like 1N5817 can be

used for most applications. If the input ramp is less than 10V/ms, a smaller schottky diode like MBR0520LT1 can be used to reduce the circuit size.

FIGURE 2. Voltage Doubler Principle

#### +5 LDO Regulator

$V_{DBL}$  is the input to an LDO regulator that regulates it to a +5 output voltage at  $V_{05}.$   $V_{PSW}$  is tied to  $V_{05}$  through a series switch PSW. The LDO output capacitor (4.7µF Tantalum) may be tied to either  $V_{05}$  or  $V_{PSW}.$

#### Inverter

From the  $V_{05}$  output, a -5V output is created at  $V_{NEG}$  by means of an inverting charge pump. This negative output is unregulated, meaning that it's output will droop as the load current at  $V_{NEG}$  increases. The inverter contains four large CMOS switches which are in a sequence to invert the input supply voltage. *Figure 3* illustrates the voltage conversion scheme. When S1 and S3 are closed, C1 charges to the supply voltage  $V_{05}$ . During this time interval, switches S2 and S4 are open. In the second time interval, S1 and S3 are open;at the same time, S2 and S4 are closed, C1 is charging C2. After a number of cycles, the voltage cross C2 will be pumped to  $V_{05}$ . Since the anode of C2 is connected to ground, the output at the cathode of C2 equals  $-(V_{05})$  when there is no load current. The output voltage drop when a load

### **Detailed Device Description**

(Continued)

is added is determined by the parasitic resistance ( $R_{\rm ds}(on)$ ) of the MOSFET switches and the ESR of the capacitors) and the charge transfer loss between capacitors.

FIGURE 3. Voltage Inverter Principle

#### **Shutdown and Load Disconnect**

In addition to the nominal charge pump and regulator functions, the LM2685 features shutdown and load disconnect circuitry. CE (chip enable) and SDP (shutdown positive) perform the same task with opposite input polarities. When CE is low or SDP is high, all circuit blocks are disabled and  $\rm V_{05}$  falls to ground potential. This is the same result as when the die temperature exceeds 150°C (typical), and the device's internal thermal shutdown is triggered.

Forcing SDN (shutdown negative) high disables only the inverting charge pump. The doubling charge pump and the LDO regulator continue to operate, so the  $\rm V_{05}$  and the  $\rm V_{PSW}$  remain at 5V.

The LM2685 incorporates two low impedance switches tied to the  $\rm V_{05}$  and  $\rm V_{NEG}$  outputs, because some special applications require load disconnect and this is achievable via the switches. Switch PSW connects  $\rm V_{05}$  to  $\rm V_{PSW}$ , and switch NSW connects  $\rm V_{NEG}$  to  $\rm V_{NSW}$ . In normal operation, these switches are closed, allowing 5V loads to be tied to either  $\rm V_{05}$  or  $\rm V_{PSW}$  and –5V loads to be tied to either  $\rm V_{NEG}$  or  $\rm V_{NSW}$ . Driving SDN high opens switch NSW only, while forcing CE low or SDP high, opens both the PSW and NSW.

## **Application Information**

#### **Capacitor Selection**

The output resistance and ripple voltage are dependent on the capacitance and ESR values of the external capacitors.

#### **Voltage Doubler External Capacitors**

The selection of capacitors are based on the specifications of the dropout voltage (which equals  $I_{OUT}$   $R_{OUT}$ ), the output voltage ripple, and the converter efficiency.

$$R_{OUT} = 2 R_{SW} + \frac{2}{f_{OSC} \times C_1} + 4 ESR_{C_1} + ESR_{C_3}$$

where  $R_{\text{SW}}$  is the sum of the ON resistance of the internal MOSFET switches as shown in *Figure 2*.

The peak-to-peak output voltage ripple is determined by the oscillator frequency, the capacitance and ESR of the capacitor C3.

$$V_{RIPPLE} = \frac{I_L}{f_{OSC} \times C_2} + 2 \times I_L \times ESR_{C_3}$$

High capacitance (2.2µF to higher), low ESR capacitors can reduce the output resistance and the voltage ripple.

Power efficiency of =

$$\frac{P_{OUT}}{P_{IN}} = \frac{I_L^2 R_L}{I_L^2 R_L + I_L^2 R_{OUT} + I_O (V+)}$$

where  $I_Q(V+)$  is the quiescent power loss of the IC device, and  $I^2_LR$  is the conversion loss associated with the switch on-resistance, the two external capacitors and their ESRs.

Low ESR capacitors (table to be referenced) are recommended to maximize efficiency, reduce the output voltage drop and voltage ripple.

#### +5 LDO Regulator External Capacitors

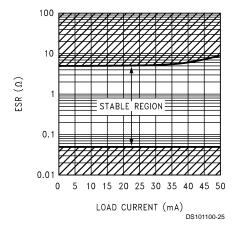

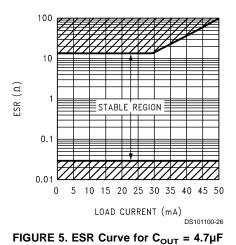

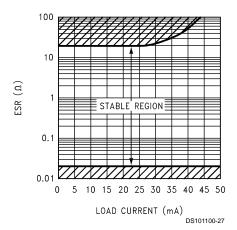

The voltage doubler output capacitor, C3, serves as the input capacitor of the +5 LDO regulator. The output capacitor C4, must meet the requirement for minimum amount of capacitance and appropriate ESR (Equivalent Serving Resistance) for proper operation. The ESR value must remain within the regions of stability as shown in Figure 4, Figure 5 and Figure 6 to ensure output's stability. A minimum capacitance of  $1\mu F$  is required at the output. This can be increased without limit, but a  $4.7\mu F$  tantalum capacitor is recommended for loads ranging upto the maximum specification. With lighter loads of less or equal to 10 mA, ceramic capacitor of at least  $1\mu F$  and ESR in the milliohms can be used. This has to be connected to  $V_{PSW}$  pin instead of the  $V_{OS}$  pin.

Any output capacitor used should have a good tolerance over temperature for capacitance and ESR values. The larger the capacitor, with ESR within the stable region, the better the stability and noise performance.

FIGURE 4. ESR Curve for  $C_{OUT} = 2.2 \mu F$

7 www.national.com

## Application Information (Continued)

FIGURE 6. ESR Curve for  $C_{OUT}$  =10 $\mu F$

#### **Inverter External Capacitors**

As discussed in the +5 LDO Regulator External Capacitors section, the output resistance and ripple voltage are dependent on the capacitance and ESR values of the external capacitors. A minimum of  $1\mu F$  capacitor with good tolerance over temperature for capacitance and ESR values. The capacitance value can be increased without limit while still maintain high low ESR value.  $2.2\mu F$  capacitors are recommended for the two external capacitors,  $C_2$  and  $C_5$  of the inverter.

www.national.com

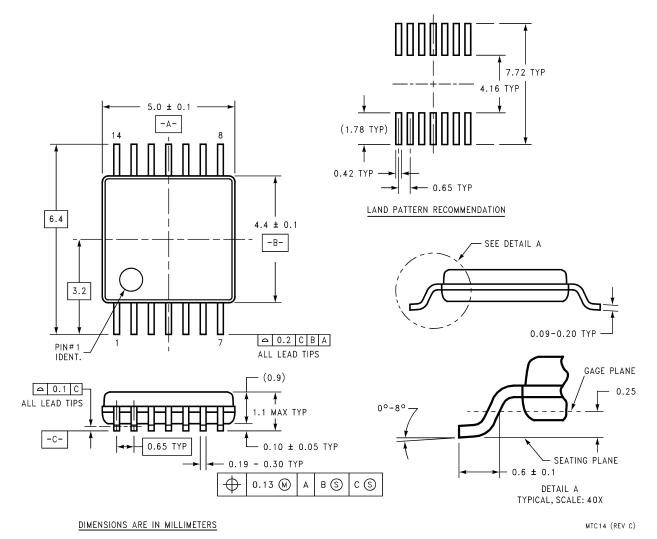

#### Physical Dimensions inches (millimeters) unless otherwise noted

TSSOP-14 Package 14-Lead Thin Shrink Small-Outline Package For Ordering, Refer to Ordering Information Table NS Package Number MTC14

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560 Fax: 81-3-5639-7507