50mV from rails

+310/-410mA

75mA

750µA

24MHz

270ns

11V/µSec

5V to 13V

## LM6584 TFT-LCD Quad, 13V RRIO High Output Current **Operational Amplifier General Description Features**

The LM6584 is a low power, high voltage, rail-to-rail inputoutput amplifier ideally suited for LCD panel  $V_{COM}$  driver and gamma buffer applications. The LM6584 contains four unity gain stable amplifiers in one package. It provides a common mode input ability of 0.5V beyond the supply rails, as well as an output voltage range that extends to within 50mV of either supply rail. With these capabilities, the LM6584 provides maximum dynamic range at any supply voltage. Operating on supplies ranging from 5V to 13V, while consuming only 750µA per amplifier, the LM6584 has a bandwidth of 24MHz (-3dB).

The LM6584 also features fast slewing and settling times, along with a high continuous output capability of 75mA. This output stage is capable of delivering approximately 310mA peak currents in order to charge or discharge capacitive loads. These features are ideal for use in TFT-LCDs.

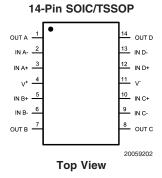

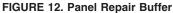

The LM6584 is available in the industry standard 14-pin SO package and in the space-saving 14-pin TSSOP package. The amplifiers are specified for operation over the full -40°C to +85°C temperature range.

$(V_{S} = 5V, T_{A} = 25^{\circ}C$  typical values unless specified)

- Input common mode voltage 0.5V beyond rails

- Output voltage swing  $(R_1 = 2k\Omega)$

- Output short circuit current Continuous output current

- Supply current (per amp, no load)

- Supply voltage range

- Unity gain stable

- -3dB bandwidth (A<sub>V</sub> = +1)

- Slew rate

- Settling time

- SO-14 and TSSOP-14 package

- Manufactured in National Semiconductor's state-of-the-art bonded wafer. trench isolated complementary bipolar VIP10<sup>™</sup> technology for high performance at low power levels

## Applications

- LCD panel V<sub>COM</sub> driver

- LCD panel gamma buffer

- LCD panel repair amp

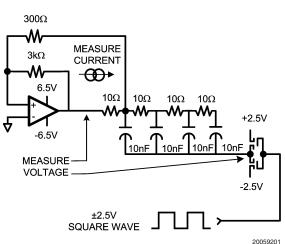

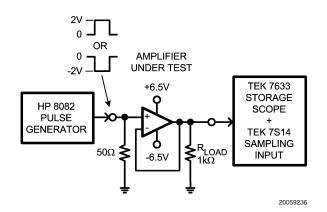

## Test Circuit Diagram

M6584 TFT-LCD Quad, 13V RRIO High Output Current Operational Amplifier

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 2)                  |                |

|-----------------------------------------|----------------|

| Human Body Model                        | 2KV            |

| Machine Model                           | 200V           |

| Supply Voltage (V <sub>+</sub> - V_)    | 14V            |

| Differential Input Voltage              | ±5.5V          |

| Output Short Circuit to Ground (Note 3) | Continuous     |

| Storage Temperature Range               | –65°C to 150°C |

Input Common Mode VoltageV- to V+Junction Temperature (Note 4)150°C

## Operating Ratings (Note 1)

| Supply Voltage                     | $5V \le V_S \le 13V$ |

|------------------------------------|----------------------|

| Temperature Range                  | -40°C to +85°C       |

| Thermal Resistance $(\theta_{JA})$ |                      |

| SOIC-14                            | 145°C/W              |

| TSSOP-14                           | 155°C/W              |

|                                    |                      |

## 13V DC Electrical Characteristics (Note 13)

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V_{CM} = \frac{1}{2}V_S$  and  $R_L = 2k\Omega$ . Boldface limits apply at the temperature extremes.

| Symbol             | Parameter                             | Conditions                                         | Min      | Тур       | Max      | Units |

|--------------------|---------------------------------------|----------------------------------------------------|----------|-----------|----------|-------|

|                    |                                       |                                                    | (Note 6) | (Note 5)  | (Note 6) |       |

| V <sub>os</sub>    | Input Offset Voltage                  |                                                    |          | 0.7       | 4        | mV    |

|                    |                                       |                                                    |          |           | 6        | IIIV  |

| TC V <sub>os</sub> | Input Offset Voltage Average<br>Drift |                                                    |          | 5         |          | µV/°C |

| I <sub>B</sub>     | Input Bias Current                    |                                                    |          | -0.3/+0.3 | ±1       | μA    |

|                    |                                       |                                                    |          |           | ±7       |       |

| l <sub>os</sub>    | Input Offset Current                  |                                                    |          | 16        | 150      | nA    |

|                    |                                       |                                                    |          |           | 300      |       |

| R <sub>IN</sub>    | Input Resistance                      | Common Mode                                        |          | 20        |          | MΩ    |

|                    |                                       | Differential Mode                                  |          | 0.5       |          |       |

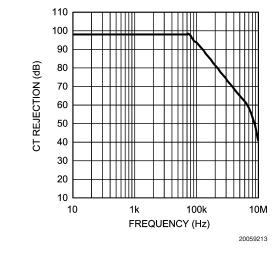

| CMRR               | Common Mode Rejection                 | $V_{CM} = 0$ to +13V                               | 75       | 103       |          |       |

|                    | Ratio                                 |                                                    | 70       |           |          | dB    |

|                    |                                       | V <sub>CM</sub> = 0 to 11.5V                       | 78       | 103       |          |       |

|                    |                                       |                                                    | 72       |           |          |       |

| PSRR               | Power Supply Rejection Ratio          | $V_{CM} = \pm 1 V$                                 | 75       | 103       |          | dB    |

|                    |                                       |                                                    | 70       |           |          |       |

| CMVR               | Input Common-Mode Voltage             | CMRR > 50dB                                        |          | 0         | -0.2     | V     |

|                    | Range                                 |                                                    | 13.2     | 13        |          |       |

| A <sub>V</sub>     | Large Signal Voltage Gain             | $R_{L} = 2k\Omega, V_{O} = 0.5 \text{ to } +12.5V$ | 78       | 108       |          | dB    |

|                    | (Note 7)                              |                                                    | 72       |           |          |       |

| Vo                 | Output Swing High                     | $R_L = 2k\Omega$                                   | 12.85    | 12.9      |          |       |

|                    |                                       |                                                    | 12.7     |           |          | V     |

|                    | Output Swing Low                      | $R_L = 2k\Omega$                                   |          | 0.55      | 0.150    |       |

| I <sub>sc</sub>    | Output Short Circuit Current          | Sourcing                                           | 200      | 320       |          | mA    |

|                    | (Note 11)                             | Sinking                                            | 200      | 420       |          | ШA    |

| I <sub>CONT</sub>  | Continuous Output Current             | Sourcing                                           |          | 75        |          |       |

|                    | (Note 12)                             | Sinking                                            |          | 75        |          | – mA  |

| ls                 | Supply Current (per Amp)              |                                                    |          | 780       | 1100     |       |

| -                  |                                       |                                                    |          |           | 1350     | μΑ    |

## 13V AC Electrical Characteristics (Note 13)

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V_{CM} = \frac{1}{2}V_S$  and  $R_L = 2k\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol | Parameter          | Conditions                    | Min      | Тур      | Мах      | Units |

|--------|--------------------|-------------------------------|----------|----------|----------|-------|

|        |                    |                               | (Note 6) | (Note 5) | (Note 6) |       |

| SR     | Slew Rate (Note 9) | $A_V = +1, V_{IN} = 10V_{PP}$ | 8        | 15       |          | V/µs  |

|        |                    |                               |          |          |          |       |

## 13V AC Electrical Characteristics (Note 13) (Continued)

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}$ C,  $V_{CM} = \frac{1}{2}V_S$  and  $R_L = 2k\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                           | Conditions                                   | Min      | Тур      | Max      | Units  |

|----------------|-------------------------------------|----------------------------------------------|----------|----------|----------|--------|

|                |                                     |                                              | (Note 6) | (Note 5) | (Note 6) |        |

|                | Unity Gain Bandwidth Product        |                                              |          | 15.4     |          | MHz    |

|                | -3dB Frequency                      | $A_{V} = +1$                                 | 10       | 24       |          | MHz    |

| $\Phi_{m}$     | Phase Margin                        |                                              |          | 61       |          | deg    |

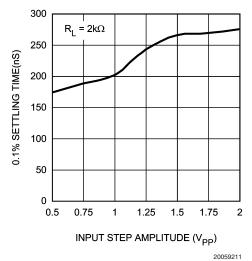

| t <sub>s</sub> | Settling Time (0.1%)                | $A_V = -1, A_O = \pm 5V, R_L = 500\Omega$    |          | 780      |          | ns     |

| t <sub>p</sub> | Propagation Delay                   | $A_V = -2, V_{IN} = \pm 5V, R_L = 500\Omega$ |          | 20       |          | ns     |

| HD2            | 2 <sup>nd</sup> Harmonic Distortion | $V_{OUT} = 2V_{PP}$                          |          | -53      |          | dBc    |

|                | F <sub>IN</sub> = 1MHz (Note 10)    |                                              |          |          |          |        |

| HD3            | 3rd Harmonic Distortion             | $V_{OUT} = 2V_{PP}$                          |          | -40      |          | dBc    |

|                | F <sub>IN</sub> = 1MHz (Note 10)    |                                              |          |          |          |        |

| e <sub>n</sub> | Input-Referred Voltage Noise        | f = 10kHz                                    |          | 23       |          | nV/√Hz |

## 5V DC Electrical Characteristics (Note 13)

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V_{CM} = \frac{1}{2}V_S$  and  $R_L = 2k\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                             | Conditions                                                     | Min      | Тур       | Max               | Units |  |

|--------------------|---------------------------------------|----------------------------------------------------------------|----------|-----------|-------------------|-------|--|

|                    |                                       |                                                                | (Note 6) | (Note 5)  | (Note 6)          |       |  |

| Vos                | Input Offset Voltage                  |                                                                |          | 0.7       | 4                 | mV    |  |

|                    |                                       |                                                                |          |           | 6                 |       |  |

| TC V <sub>os</sub> | Input Offset Voltage Average<br>Drift |                                                                |          | 10        |                   | µV/°C |  |

| I <sub>B</sub>     | Input Bias Current                    |                                                                |          | -0.3/+0.3 | ±1                | μA    |  |

|                    |                                       |                                                                |          |           | ±7                | μΛ    |  |

| I <sub>OS</sub>    | Input Offset Current                  |                                                                |          | 20        | 150<br><b>300</b> | nA    |  |

| R <sub>IN</sub>    | Input Resistance                      | Common Mode                                                    |          | 20        |                   | Мо    |  |

|                    |                                       | Differential Mode                                              |          | 0.5       |                   |       |  |

| CMRR               | Common Mode Rejection                 | V <sub>CM</sub> Stepped from 0 to 5V                           | 72       | 105       |                   |       |  |

|                    | Ratio                                 |                                                                | 68       |           |                   | dB    |  |

|                    |                                       | V <sub>CM</sub> Stepped from 0 to 3.5V                         | 75       | 105       |                   | db    |  |

|                    |                                       |                                                                | 70       |           |                   |       |  |

| PSRR               | Power Supply Rejection Ratio          | Supply Rejection Ratio $V_{\rm S} = V_{\rm CC} = 3.5V$ to 5.5V | 75       | 92        |                   | dB    |  |

|                    |                                       |                                                                | 70       |           |                   | üD    |  |

| CMVR               | Input Common-Mode Voltage             | CMRR > 50dB                                                    |          | 0.0       | -0.2              | V     |  |

|                    | Range                                 |                                                                | 5.2      | 5.0       |                   | •     |  |

| A <sub>V</sub>     | Large Signal Voltage Gain             | $R_L = 2k\Omega$ , $V_O = 0$ to 5V                             | 70       | 106       |                   | dB    |  |

|                    | (Note 7)                              |                                                                | 65       |           |                   |       |  |

| Vo                 | Output Swing High                     | $R_{L} = 2k\Omega$                                             | 4.85     | 4.9       |                   | v     |  |

|                    |                                       |                                                                | 4.7      |           |                   |       |  |

|                    | Output Swing Low                      | $R_L = 2k\Omega$                                               |          | 0.2       | 0.15              |       |  |

| I <sub>SC</sub>    | Output Short Circuit Current          | Sourcing                                                       |          | 310       |                   | mA    |  |

|                    | (Note 11)                             | Sinking                                                        |          | 400       |                   |       |  |

| I <sub>CONT</sub>  | Continuous Output Current             | Sourcing                                                       |          | 75        |                   | mA    |  |

|                    | (Note 12)                             | Sinking                                                        |          | 75        |                   |       |  |

| ls                 | Supply Current (per Amp)              |                                                                |          | 750       | 1000              | μA    |  |

|                    |                                       |                                                                |          |           | 1250              | μΑ    |  |

LM6584

## 5V AC Electrical Characteristics (Note 13)

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V_{CM} = \frac{1}{2}V_S$  and  $R_L = 2k\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                                                               | Conditions                                   | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units  |

|----------------|-------------------------------------------------------------------------|----------------------------------------------|-----------------|-----------------|-----------------|--------|

| SR             | Slew Rate (Note 9)                                                      | $A_V = +1, V_{IN} = 3.5V_{PP}$               |                 | 11              |                 | V/µs   |

|                | Unity Gain Bandwidth Product                                            |                                              |                 | 15.3            |                 | MHz    |

|                | -3dB Frequency                                                          | A <sub>V</sub> = +1                          |                 | 24              |                 | MHz    |

| $\Phi_{m}$     | Phase Margin                                                            |                                              |                 | 56              |                 | deg    |

| t <sub>s</sub> | Settling Time (0.1%)                                                    | $A_V = -1, V_O = \pm 1V, R_L = 500\Omega$    |                 | 270             |                 | ns     |

| t <sub>p</sub> | Propagation Delay                                                       | $A_V = -2, V_{IN} = \pm 1V, R_L = 500\Omega$ |                 | 21              |                 | ns     |

| HD2            | 2 <sup>nd</sup> Harmonic Distortion<br>F <sub>IN</sub> = 1MHz (Note 10) | $V_{OUT} = 2V_{PP}$                          |                 | -53             |                 | dBc    |

| HD3            | 3rd Harmonic Distortion<br>F <sub>IN</sub> = 1MHz (Note 10)             | V <sub>OUT</sub> = 2V <sub>PP</sub>          |                 | -40             |                 | dBc    |

| e <sub>n</sub> | Input-Referred Voltage Noise                                            | f = 10kHz                                    |                 | 23              |                 | nV/√Hz |

Note 1: Absolute maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: For testing purposes, ESD was applied using human body model,  $1.5k\Omega$  in series with 100pF.

Note 3: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

Note 5: Typical values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Large signal voltage gain is the total output swing divided by the input signal required to produce that swing.

Note 8: The open loop output current is guaranteed, by the measurement of the open loop output voltage swing.

**Note 9:** Slew Rate is the average of the raising and falling slew rates.

Note 10: Harmonics are measured with  $A_V$  = +2 and  $R_L$  = 100 $\Omega$  and  $V_{IN}$  = 1 $V_{PP}$  to give  $V_{OUT}$  = 2 $V_{PP}$ .

Note 11: Continuous operation at these output currents will exceed the power dissipation ability of the device

Note 12: Power dissipation limits may be exceeded if all four amplifiers source or sink 75mA. Voltage across the output transistors and their output currents must be taken into account to determine the power dissipation of the device

**Note 13:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self heating where  $T_J > T_A$ . See applications section for information on temperature de-rating of this device.

## **Connection Diagram**

## Ordering Information

| Package                           | Part Number | Package Marking | Transport Media          | NSC Drawing |

|-----------------------------------|-------------|-----------------|--------------------------|-------------|

| 14-Pin SOIC                       | LM6584MA    | LM6584MA        | 95 Units/Rail            | M14A        |

| 14-PIII 5010                      | LM6584MAX   | LIVIODO4IVIA    | 2.5k Units Tape and Reel | IVI 14A     |

| 14-Pin TSSOP LM6584MT 95 Units/Ra |             | 95 Units/Rail   | MTC14                    |             |

| 14-Pin TSSOP                      | LM6584MTX   |                 | 2.5k Units Tape and Reel | MIC14       |

www.national.com

www.national.com

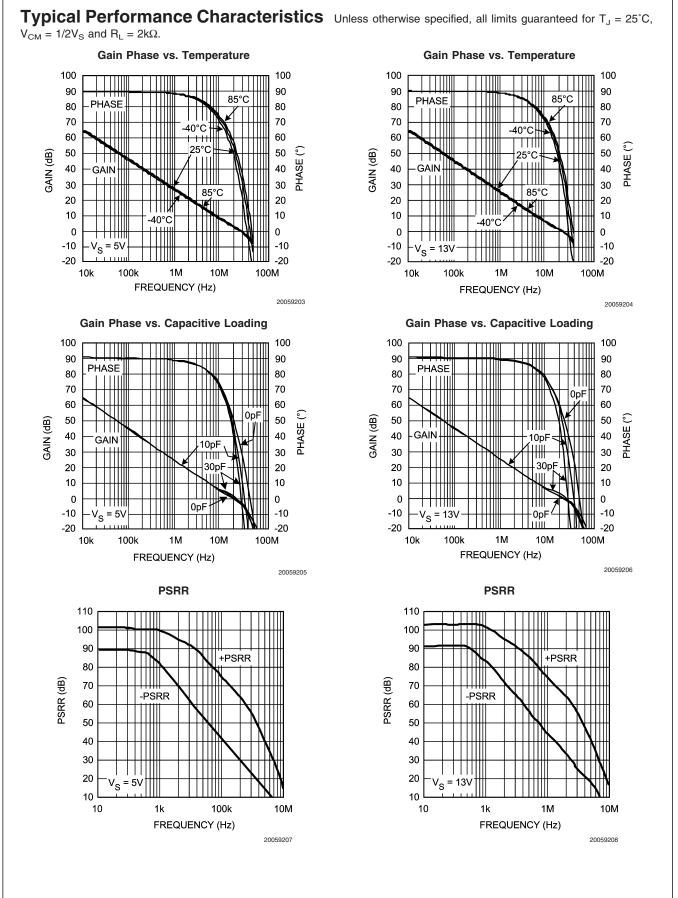

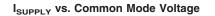

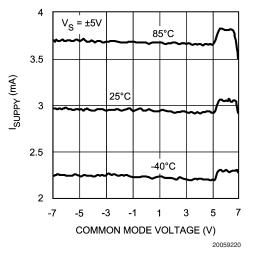

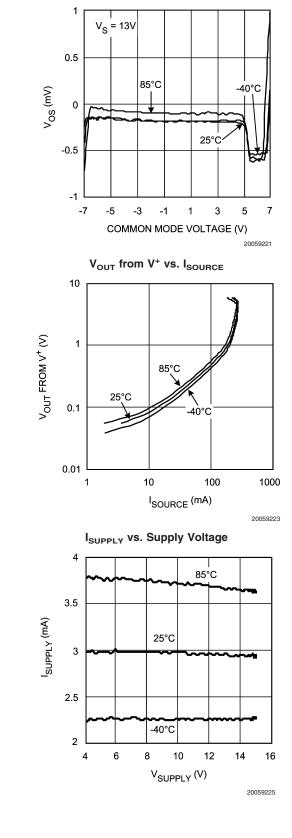

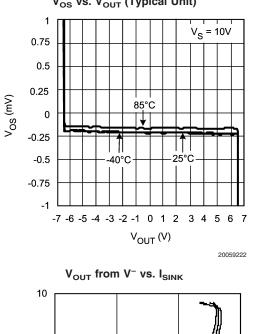

**Typical Performance Characteristics** Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 1/2V_S$  and  $R_L = 2k\Omega$ . (Continued)

CMRR 120 = 5\ 110 100 90 CMRR (dB) 80 70 60 50 40 30 10 1k 1M 10M FREQUENCY (Hz) 20059209

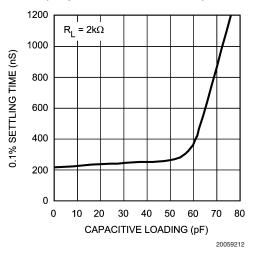

Settling Time vs. Capacitive Loading (Output Slew and Settle Time)

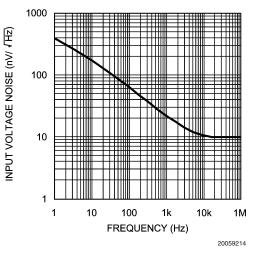

Input Voltage Noise vs. Frequency

**Typical Performance Characteristics** Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = 1/2V_S$  and  $R_L = 2k\Omega$ . (Continued)

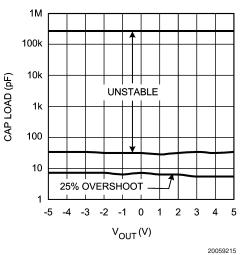

#### Stability vs. Capacitive Load Unity Gain, V<sub>s</sub> = 13V

200

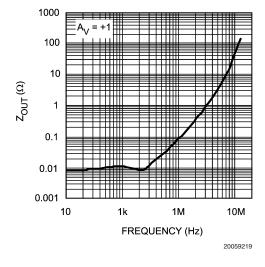

Closed Loop Output Impedance vs. Frequency

LM6584

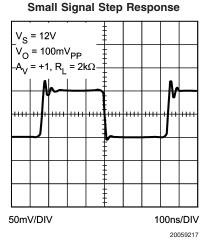

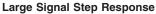

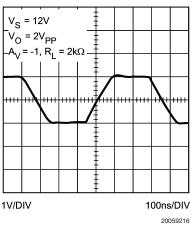

**Small Signal Step Response**

Typical Performance Characteristics $V_{CM} = 1/2V_S$  and  $R_L = 2k\Omega$ . (Continued) $V_{os}$  vs. Common Mode Voltage $V_{os}$  vs.  $V_{out}$  (Typical Unit)

20059224

#### The LM6584 operates from a voltage supply, of V<sup>+</sup> and ground, or from a V<sup>-</sup> and V<sup>+</sup> split supply. Single-ended voltage range is +5V to +13V and split supply range is $\pm 2.5V$ to $\pm 6.5V$ . APPLICATION HINTS POWER SUPPLIES

#### Sequencing

**Output Power**

value of 150° C.

**Power Requirements**

Best practice design technique for operational amplifiers includes careful attention to power sequencing. Although the LM6584 is a bipolar op amp, recommended op amp turn on power sequencing of ground (or V<sup>-</sup>), followed by V<sup>+</sup>, followed by input signal should be observed. Turn off power sequence should be the reverse of the turn-on sequence. Depending on how the amp is biased the outputs may swing to the rails on power-on or power-off. Due to the high output currents and rail to rail output stage in the LM6584 the output may oscillate very slightly if the power is slowly raised between 2V and 4V The part is unconditionally stable at 5V. Quick turn-off and turn-on times will eliminate oscillation problems.

Because of the increased output drive capability, internal heat dissipation must be held to a level that does not in-

crease the junction temperature above its maximum rated

#### **PSRR** and Noise

Care should be taken to minimize the noise in the power supply rails. The figure of merit for an op amp's ability to keep power supply noise out of the signal is called Power Supply Rejection Ratio (PSRR). Observe from the PSRR charts in the Typical Performance Characteristics section that the PSRR falls of dramatically as the frequency of the noise on the power supply line goes up. This is one of the reasons switching power supplies can cause problems. It should also be noticed from the charts that the negative supply pin is far more susceptible to power noise. The design engineer should determine the switching frequencies and ripple voltages of the power supplies in the system. If required, a series resistor or in the case of a high current op amp like the LM6584, a series inductor can be used to filter out the noise.

#### Transients

In addition to the ripple and noise on the power supplies there are also transient voltage changes. This can be caused by another device on the same power supply suddenly drawing current or suddenly stopping a current draw. The design engineer should insure that there are no damaging transients induced on the power supply lines when the op amp suddenly changes current delivery.

### LAYOUT

#### **Ground Planes**

Do not assume the ground (or more properly, the common or return) of the power supply is an ocean of zero impedance. The thinner the trace, the higher the resistance. Thin traces cause tiny inductances in the power lines. These can react against the large currents the LM6584 is capable of delivering to cause oscillations, instability, overshoot and distortion. A ground plane is the most effective way of insuring the

## **Application Notes**

#### CIRCUIT DESCRIPTION GENERAL & SPEC

The LM6584 is a bipolar process operational amplifier. It has an exceptional output current capability of 330mA. The part has both rail to rail inputs and outputs. It has a –3dB bandwidth of 24MHz. The part has input voltage noise of 23nV/ $\sqrt{Hz}$ , and 2<sup>nd</sup> and 3<sup>rd</sup> harmonic distortion of –53dB and –40dB respectively.

#### INPUT SECTION

The LM6584 has rail to rail inputs and thus has an input range over which the device may be biased of V<sup>-</sup> minus 0.5V, and V<sup>+</sup> plus V. The ultimate limit on input voltage excursion is the ESD protection diodes on the input pins. The most important consideration in Rail-to-Rail input op amps is to understand the input structure. Most Rail-to-Rail input amps use two differential input pairs to achieve this function. This is how the LM6584 works. A conventional PNP differential transistor pair provides the input gain from 0.5V below the negative rail to about one volt below the positive rail. At this point internal circuitry activates a differential NPN transistor pair that allows the part to function from 1 volt below the positive rail to 0.5V above the positive rail. The effect on the inputs pins is as if there were two different op amps connected to the inputs. This has several unique implications.

- The input offset voltage will change, sometimes from positive to negative as the inputs transition between the two stages at about a volt below the positive rail. this effect is seen in the V<sub>OS</sub> vs. V<sub>CM</sub> chart in the Typical Performance Characteristics section of this datasheet.

- The input bias currents can be either positive or negative. Do not expect a consistent flow in or out of the pins.

- The part will have different specifications depending on whether the NPN or PNP stage is operating.

- There is a little more input capacitance then a single stage input although the ESD diodes often swamp out the added base capacitance.

- Since the input offset voltages can change from positive to negative the output may not be monotonic when the inputs are transitioning between the two stages and the part is in a high gain configuration.

It should be remembered that swinging the inputs across the input stage transition may cause output distortion and accuracy anomalies. It is also worth noting that anytime any amps inputs are swung near the rails THD and other specs are sure to suffer.

#### **OUTPUT SECTION**

#### **Current Rating**

The LM6584 has an output current rating, sinking or sourcing, of 300mA. The LM6584 is ideally suited to loads that require a high value of peak current but only a reduced value of average current. This condition is typical of driving the gate of a MOSFET. While the output drive rating is 300mA peak, and the output structure supports rail-to-rail operation, the attainable output current is reduced when the gain and drive conditions are such that the output voltage approaches either rail.

### Application Notes (Continued)

ground is a uniform low impedance. If a four layer board cannot be used, consider pouring a plane on one side of a two layer board. If this cannot be done be sure to use as wide a trace as practicable and use extra decoupling capacitors to minimize the AC variations on the ground rail.

#### Decoupling

A high-speed, high-current amp like the LM6584 must have generous decoupling capacitors. They should be as close to the power pins as possible. Putting them on the back side opposite the power pins may give the tightest layout. If ground and power planes are available, the placement of the decoupling caps are not as critical.

#### Breadboards

The high currents and high frequencies the LM6584 operates at, as well as thermal considerations, require that prototyping of the design be done on a circuit board as opposed to a "Proto-Board" style breadboard.

#### STABILITY

#### General

High speed parts with large output current capability require special care to insure lack of oscillations. Keep the "+" pin isolated from the output to insure stability. As noted above care should be take to insure the large output currents do not appear in the ground or ground plane and then get coupled into the "+" pin. As always, good tight layout is essential as is adequate use of decoupling capacitors on the power supplies.

#### Unity Gain

The unity gain or voltage-follower configuration is the most subject to oscillation. If a part is stable at unity gain it is almost certain to work in other configurations. In certain applications where the part is setting a reference voltage or is being used as a buffer greater stability can be achieved by configuring the part as a gain of -1 or -2 or +2.

#### **Phase Margin**

The phase margin of an op amps gain-phase plot is an indication of the stability of the amp. It is desirable to have at least 45°C of phase margin to insure stability in all cases. The LM6584 has 60°C of phase margin even with it's large output currents and Rail-to-Rail output stage, which are generally more prone to stability issues.

#### **Capacitive Load**

The LM6584 can withstand 30pF of capacitive load in a unity gain configuration before stability issues arise. At very large capacitances, the load capacitor will attenuate the gain like any other heavy load and the part becomes stable again. The LM6584 will be stable at 330nF and higher load capacitance. Refer to the chart in the Typical Performance Characteristics section.

#### OUTPUT

#### Swing vs. Current

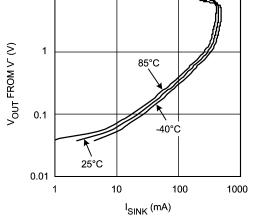

The LM6584 will get to about 25mV or 30mV of either rail when there is no load. The LM6584 can sink or source hundreds of milliamperes while remaining less then 0.5V away from the rail. It should be noted that if the outputs are

driven to the rail and the part can no longer maintain the feedback loop, the internal circuitry will deliver large base currents into the huge output transistors, trying to get the outputs to get past the saturation voltage. The base currents will approach 16 milliamperes and this will appear as an increase in power supply current. Operating at this power dissipation level for extended periods will damage the part, especially in the higher thermal resistance TSSOP package. Because of this phenomenon, unused parts should not have the inputs strapped to either rail, but should have the inputs biased at the midpoint or at least a diode drop (0.6V) within the rails.

#### Self Heating

As discussed above the LM6584 is capable of significant power by virtue of its 300mA current handling capability. A TSSOP package cannot sustain these power levels for more then a brief period.

## **TFT Display Application**

#### INTRODUCTION

In today's high-resolution TFT displays, op amps are used for the following three functions:

- 1. V<sub>COM</sub> Driver

- 2. Gamma Buffer

- 3. Panel Repair Buffer

All of these functions utilize op amps as non-inverting, unitygain buffers. The  $V_{COM}$  Driver and Gamma Buffer are buffers that supply a well regulated DC voltage. A Panel Repair Buffer, on the other hand, provides a high frequency signal that contains part of the display's visual image.

In an effort to reduce production costs, display manufacturers use a minimum variety of different parts in their TFT displays. As a result, the same type of op amp will be used for the  $V_{\rm COM}$  Driver, Gamma Buffer, and Panel Repair Buffer. To perform all these functions, such an op amp must have the following characteristics:

- 1. Large output current drive

- 2. Rail to rail input common mode range

- 3. Rail to rail output swing

- 4. Medium speed gain bandwidth and slew rate

The LM6584 meets these requirements. It has a rail-to-rail input and output, typical gain bandwidth and slew rate of 15MHz and 15V/µs, and it can supply up to 320mA of output current. The following sections will describe the operation of  $V_{\rm COM}$  Drivers, Gamma Buffers, and Panel Repair Buffers, showing how the LM6584 is well suited for each of these functions.

#### BRIEF OVERVIEW OF TFT DISPLAY

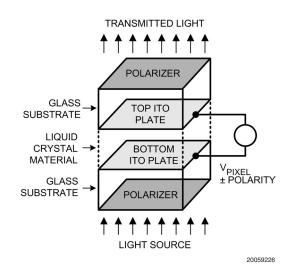

To better understand these op amp applications, let's first review a few basic concepts of how a TFT display operates. *Figure 1* is a simplified illustration of an LCD pixel. The top and bottom plates of each pixel consist of Indium-Tin oxide (ITO), which is a transparent, electrically conductive material. ITO lies on the inner surfaces of two glass substrates that are the front and back glass panels of a TFT display. Sandwiched between the two ITO plates is an insulating material (liquid crystal) that alters the polarization of light to a lesser a greater amount, depending on how much voltage (V<sub>PIXEL</sub>) is applied across the two glass substrates, which in combination with the liquid crystal create a variable

light filter that modulates light transmitted from the back to the front of a display. A pixel's bottom plate lies on the backside of a display where a light source is applied, and the top plate lies on the front, facing the viewer. On a Twisted Neumatic (TN) display, which is typical of most TFT displays, a pixel transmits the greatest amount of light when  $V_{\text{PIXEL}}$  is less ±0.5V, and it becomes less transparent as this voltage increases with either a positive or negative polarity. In short, an LCD pixel can be thought of as a capacitor, through which, a controlled amount of light is transmitted by varying  $V_{\text{PIXEL}}$ .

FIGURE 1. Individual LCD Pixel

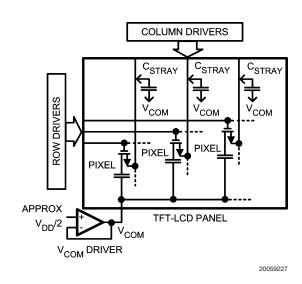

#### FIGURE 2. TFT Display

*Figure 2* is a simplified block diagram of a TFT display, showing how individual pixels are connected to the row, column, and  $V_{COM}$  lines. Each pixel is represented by capacitor with an NMOS transistor connected to its top plate. Pixels in a TFT panel are arranged in rows and columns. Row lines are connected to the NMOS gates, and column lines to the NMOS sources. The back plate of every pixel is connected to a common voltage called  $V_{COM}$ . Pixel brightness is controlled by voltage applied to the top plates, and

the Column Drivers supply this voltage via the column lines. Column Drivers 'write' this voltage to the pixels one row at a time, and this is accomplished by having the Row Drivers select an individual row of pixels when their voltage levels are transmitted by the Column Drivers. The Row Drivers sequentially apply a large positive pulse (typically 25V to 35V) to each row line. This turns-on NMOS transistors connected to an individual row, allowing voltages from the column lines to be transmitted to the pixels.

#### V<sub>COM</sub> DRIVER

The V<sub>COM</sub> driver supplies a common voltage (V<sub>COM</sub>) to all the pixels in a TFT panel. V<sub>COM</sub> is a constant DC voltage that lies in the middle of the column drivers' output voltage range. As a result, when the column drivers write to a row of pixels, they apply voltages that are either positive or negative with respect to V<sub>COM</sub>. In fact, the polarity of a pixel is reversed each time its row is selected. This allows the column drivers to apply an alternating voltage to the pixels rather than a DC signal, which can 'burn' a pattern into an LCD display.

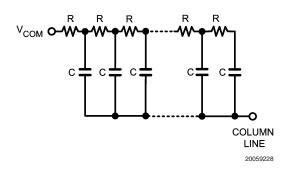

When column drivers write to the pixels, current pulses are injected onto the  $V_{\rm COM}$  line. These pulses result from charging stray capacitance between V<sub>COM</sub> and the column lines (see Figure 2), which ranges typically from 16pF to 33pF per column. Pixel capacitance contributes very little to these pulses because only one pixel at a time is connected to a column, and the capacitance of a single pixel is on the order of only 0.5pF. Each column line has a significant amount of series resistance (typically  $2k\Omega$  to  $40k\Omega$ ), so the stray capacitance is distributed along the entire length of a column. This can be modeled by the multi-segment RC network shown in Figure 3. The total capacitance between V<sub>COM</sub> and the column lines can range from 25nF to 100nF, and charging this capacitance can result in positive or negative current pulses of 100mA, or more. In addition, a similar distributed capacitance of approximately the same value exists between  $V_{COM}$  and the row lines. Therefore, the  $V_{COM}$  driver's load is the sum of these distributed RC networks with a total capacitance of 50nF to 200nF, and this load can modeled like the circuit in Figure 3.

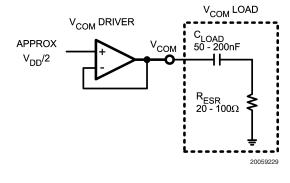

#### FIGURE 3. Model of Impedance between V<sub>COM</sub> and Column Lines

A V<sub>COM</sub> driver is essentially a voltage regulator that can source and sink current into a large capacitive load. To simplify the analysis of this driver, the distributed RC network of *Figure 3* has been reduced to a single RC load in *Figure* 4. This load places a large capacitance on the V<sub>COM</sub> driver output, resulting in an additional pole in the op amp's feedback loop. However, the op amp remains stable because  $C_{LOAD}$  and  $R_{ESR}$  create a zero that cancels the effect of this pole. The range of  $C_{LOAD}$  is 50nF to 200nF and  $R_{ESR}$  is 20 $\Omega$ to 100 $\Omega$ , so this zero will have a frequency in the range of

8KHz to160KHz, which is much lower than the gain bandwidth of most op amps. As a result, the V<sub>COM</sub> load adds very little phase lag when op amp loop gain is unity, and this allows the V<sub>COM</sub> Driver to remain stable. This was verified by measuring the small-signal bandwidth of the LM6584 with the RC load of *Figure 4*. When driving an RC load of 50nF and 20 $\Omega$ , the LM6584 has a unity gain frequency of 6.12MHz with 41.5°C of phase margin. If the load capacitor is increased to 200nF and the resistance remains 20 $\Omega$ , the unity gain frequency is virtually unchanged: 6.05MHz with 42.9°C of phase margin.

FIGURE 4. V<sub>COM</sub> Driver with Simplified Load

A V<sub>COM</sub> Driver's large-signal response time is determined by the op amp's maximum output current, not by its slew rate. This is easily shown by calculating how much output current is required to slew a 50nF load capacitance at the LM6584 slew rate of 14V/ $\mu$ s:

700mA exceeds the maximum current specification for the LM6584 and almost all other op amps, confirming that a  $V_{\rm COM}$  driver's speed is limited by its peak output current. In order to minimize  $V_{\rm COM}$  transients, the op amp used as a  $V_{\rm COM}$  Driver must supply large values of output current.

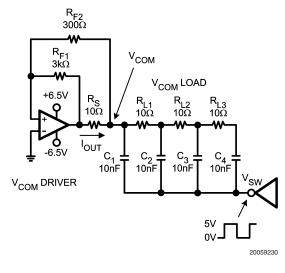

FIGURE 5. V<sub>COM</sub> Driver Test Circuit

Figure 5 is a common test circuit used for measuring  $V_{COM}$  driver response time. The RC network of  $R_{L1}$  to  $R_{L3}$  and  $C_1$

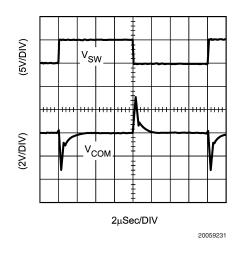

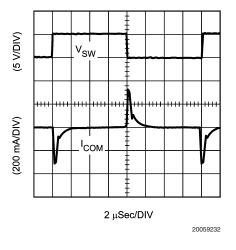

to C<sub>4</sub> models the distributed RC load of a V<sub>COM</sub> line. This RC network is a gross simplification of what the actual impedance is on a TFT panel. However, it does provide a useful test for measuring the op amp's transient response when driving a large capacitive load. A low impedance MOSFET driver applies a 5V square wave to V<sub>SW</sub>, generating large current pulses in the RC network. Scope photos from this circuit are shown in Figure 6 and Figure 7. Figure 6 shows the test circuit generates positive and negative voltage spikes with an amplitude of  $\pm 3.2V$  at the V<sub>COM</sub> node, and both transients settle-out in approximately 2µs. As mentioned before, the speed at which these transients settle-out is a function of the op amp's peak output current. The IOUT trace in Figure 7 shows that the LM6584 can sink and source peak currents of -310mA and 320mA. This ability to supply large values of output current makes the LM6584 extremely well suited for  $V_{COM}$  Driver applications.

FIGURE 6. V<sub>SW</sub> and V<sub>COM</sub> Waveforms from V<sub>COM</sub>

FIGURE 7.  $V_{\text{SW}}$  and  $I_{\text{OUT}}$  Waveforms from  $V_{\text{COM}}$  Test Circuit

#### GAMMA BUFFER

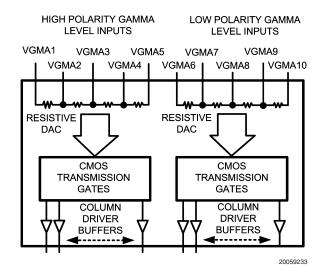

Illumination in a TFT display, also referred to as grayscale, is set by a series of discrete voltage levels that are applied to each LCD pixel. These voltage levels are generated by resistive DAC networks that reside inside each of the column driver ICs. For example, a column driver with 64 Grayscale

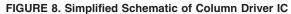

levels has a two 6 bit resistive DACs. Typically, the two DACs will have their 64 resistors grouped into four segments, as shown in *Figure 8*. Each of these segments is connected to external voltage lines, VGMA1 to VGMA10, which are the Gamma Levels. VGMA1 to VGMA5 set gray-scale voltage levels that are positive with respect to V<sub>COM</sub> (high polarity gamma levels). VGMA6 to VGMA10 set gray-scale voltages negative with respect to V<sub>COM</sub> (low polarity gamma levels).

Figure 9 shows how column drivers in a TFT display are connected to the gamma levels. VGMA1, VGMA5, VGMA6, and VGMA10 are driven by the Gamma Buffers. These buffers serve as low impedance voltage sources that generate the display's gamma levels. The Gamma Buffers' outputs are set by a simple resistive ladder, as shown in Figure 9. Note that VGMA2 to VGMA4 and VGMA7 to VGMA9 are usually connected to the column drivers even though they are not driven by external buffers. Doing so, forces the gamma levels in all the column drivers to be identical, minimizing grayscale mismatch between column drivers. Referring again to Figure 9, the resistive load of a column driver DAC (i.e. resistance between GMA1 to GMA5) is typically  $10k\Omega$  to  $15k\Omega$ . On a typical display such as XGA, there can be up to 10 column drivers, so the total resistive load on a Gamma Buffer output can be as low as  $1k\Omega$ . The voltage between VGMA1 and VGMA5 can range from 3V to 6V, depending on the type of TFT panel. Therefore, maximum load current supplied by a Gamma Buffer is approximately  $6V/1k\Omega = 6mA$ , which is a relatively light load for most op amps. In many displays, VGMA1 can be less than 500mV below  $V_{\text{DD}},$  and VGMA10 can be less than 500mV above ground. Under these conditions, an op amp used for the Gamma Buffer must have rail-to-rail inputs and outputs, like the LM6584.

FIGURE 9. Basic Gamma Buffer Configuration

Another important specification for Gamma Buffers is small signal bandwidth and slew rate. When column drivers select which voltage levels are written to a row of pixels, their internal DACs inject current spikes into the Gamma Lines. This generates voltage transients at the Gamma Buffer outputs, and they should settle-out in less than 1µs to insure a steady output voltage from the column drivers. Typically, these transients have a maximum amplitude of 2V, so a gamma buffer must have sufficient bandwidth and slew rate to recover from a 2V transient in 1µs or less.

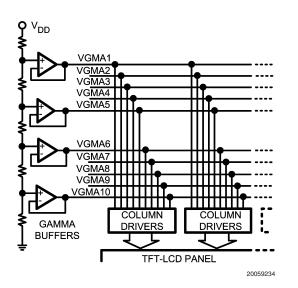

FIGURE 10. Large Signal Transient Response of an Operational Amplifier

*Figure 10* illustrates how an op amp responds to a largesignal transient. When such a transient occurs at t = 0, the output does not start changing until  $T_{PD}$ , which is the op amp's propagation delay time (typically 20ns for the LM6584). The output then changes at the op amp's slew rate from t =  $T_{PD}$  to  $T_{SR}$ . From t =  $T_{SR}$  to  $T_{SE}$ T, the output settles to its final value (V<sub>F</sub>) at a speed determined by the op amp's small-signal frequency response. Although propagation de-

lay and slew limited response time (t = 0 to  $T_{SR}$ ) can be calculated from data sheet specifications, the small signal settling time ( $T_{SR}$  to  $T_{SET}$ ) cannot. This is because an op amp's gain vs. frequency has multiple poles, and as a result, small-signal settling time can not be calculated as a simple function of the op amp's gain bandwidth. Therefore, the only accurate method for determining op amp settling time is to measure it directly.

FIGURE 11. Gamma Buffer Settling Time Test Circuit

The test circuit in *Figure 11* was used to measure LM6584 settling time for a 2V pulse and  $1k\Omega$  load, which represents the maximum transient amplitude and output load for a gamma buffer. With this test system, the LM6584 settled to within ±30mV of 2V pulse in approximately 170ns. Settling time for a 0 to -2V pulse was slightly less, 150ns. These values are much smaller than the desired response time of 1µs, so the LM6584 has sufficient bandwidth and slew rate for regulating gamma line transients.

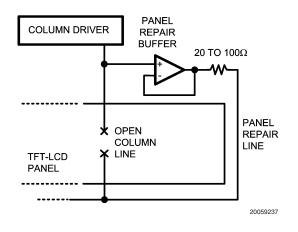

#### PANEL REPAIR BUFFER

It is not uncommon for a TFT panel to be manufactured with an open in one or two of its column or row lines. In order to repair these opens, TFT panels have uncommitted repair lines that run along their periphery. When an open line is identified during a panel's final assembly, a repair line reroutes its signal past the open. Figure 12 illustrates how a column is repaired. The column driver's output is sent to the other end of an open column via a repair line, and the repair line is driven by a panel repair buffer. When a column or row line is repaired, the capacitance on that line increases substantially. For instance, a column typically has 50pF to 100pF of line capacitance, but a repaired column can have up to 200pF. Column drivers are not designed to drive this extra capacitance, so a panel repair buffer provides additional output current to the repaired column line. Note that there is typically a  $20\Omega$  to  $100\Omega$  resistor in series with the buffer output. This resistor isolates the output from the 200pF of capacitance on a repaired column line, ensuring that the buffer remains stable. A pole is created by this resistor and capacitance, but its frequency will be in the range of 8MHz to 40MHz, so it will have only a minor effect on the buffer's transient response time. Panel repair buffers transmit a column driver signal, and as mentioned in the gamma buffer section, this signal is set by the gamma levels. It was also mentioned that many displays have upper and lower gamma levels that are within 500mV of the supply rails. Therefore, op amps used as panel repair buffers should have rail-to-rail input and stages. Otherwise, they may clip the column driver signal.

The signal from a panel repair buffer is stored by a pixel when the pixel's row is selected. In high-resolution displays, each row is selected for as little as 11µs. To insure that a pixel has adequate time to settle-out during this brief period, a panel repair buffer should settle to within 1% of its final value approximately 1µs after a row is selected. This is hardest to achieve when transmitting a column line's maximum voltage swing, which is the difference between the upper and lower gamma levels (i.e. voltage between VGMA1 and VGMA10). For a LM6584, the most demanding application occurs in displays that operate from a 13V supply. In these displays, voltage difference between the top and bottom gamma levels can be as large as 12V, so the LM6584 needs to transmit a ±12V pulse and settle to within 60mV of its final value in approximately 1µs (60mV is approximately 1% of the dynamic range of the high or low polarity gamma levels). LM6584 settling times for 12V and -12V pulses were measured in a test circuit similar to the one in Figure 11. V<sup>+</sup> and V<sup>-</sup> were set to 12.5V and -0.5V, respectively, when measuring settling time for a 0V to 12V pulse. Likewise, V+ and V<sup>-</sup> were set to 0.5V and -12.5V when measuring settling time for a 0V to -12V pulse. In both cases, the LM6584 output was connected to a series RC load of 51 Ω and 200 pF. When tested this way, the LM6584 settled to within 60mV of 12V or -12V in approximately 1.1µs. These observed values are very close to the desired 1µs specification, demonstrating that the LM6584 has the bandwidth and slew rate required for repair buffers in high-resolution TFT displays.

#### SUMMARY

This application note provided a basic explanation of how op-amps are used in TFT displays, and it also presented the specifications required for these op amps. There are three major op amp applications in a display:  $V_{COM}$  Driver, Gamma Buffer, and Panel Repair Buffer, and the LM6584 can be used for all of them. As a  $V_{COM}$  Driver, the LM6584 can supply large values of output current to regulate  $V_{COM}$  load transients. It has rail-to-rail input common-mode range and output swing required for gamma buffers and panel repair buffers. It also has the necessary gain bandwidth and slew-rate for regulating gamma levels and driving column repair lines. All these features make the LM6584 very well suited for use in TFT displays.

## Notes

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.