# LU5M31 Gigabit Ethernet Media Access Controller (MAC)

#### Overview

The LU5M31 is a single-port 1 Gbit/s MAC that incorporates physical coding sublayer (PCS) functionality. The LU5M31 is intended to enhance 10/100 Mbits/s Ethernet frame switching, multiple port bridging, and routing applications by providing a 1 Gbit/s uplink port to a high-speed Ethernet backbone. The LU5M31 operates in full-duplex mode and is intended to be used with a physical layer device (PHY) that supports a 10b encoded data interface at 125 MHz.

PCS support is provided including an 8b/10b encoder/decoder for direct connection to a PHY. The PCS encodes 8-bit transmit data into 10-bit data codes required by the transceiver, and decodes 10-bit data codes received by the transceiver into 8-bit data. In addition, the PCS manages the autonegotiation and link synchronization functions required by *IEEE* 802.3z.

Full-duplex GMII support is provided for an interconnection between the LU5M31 and the plug. It provides an independent eight-bit-wide transmit and receive data paths, and has stations management to and from the PHY device. This GMII interface is based on the *IEEE* 802.32 clause 35 standard.

The LU5M31 allows single-clock cycle data transfers directly to and from its internal transmit and receive FIFOs. The receive FIFO uses programmable watermarks to initiate flow control in order to prevent FIFO overflow.

The LU5M31 provides configuration and management support through CPU interface accessing onchip registers and event counters. The event counters maintained by the LU5M31 are derived from the RMON MIB and provide enough raw data to implement the Ethernet statistics group. Other groups within RMON can also use the data collected by the event counters.

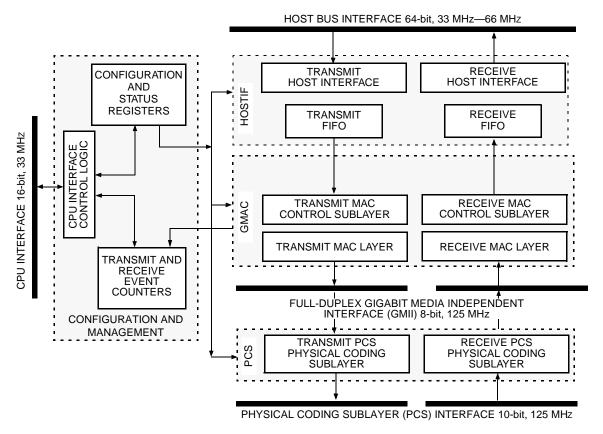

The LU5M31 comprises four main functional blocks:

- The PCS block provides support for autonegotiation, internal loopback, random jitter testing, and encoding and decoding of data transferred to or from a GMAC block across an internal GMII compliant interface.

- The GMAC block operates between the host and the PCS and implements all the full-duplex functions of the media access protocol. The GMAC block is subdivided into a MAC layer (managing data transfer), and a full-duplex MAC control sublayer which handles all control functions required by the MAC sublayer.

- The host interface provides a high-speed interface between the LU5M31 and the host to allow buffering for receive and transmit data.

- The configuration and management block provides the host with synchronous CPU access to both registers and event counters, allowing the host system to configure and monitor the device independent of the data path.

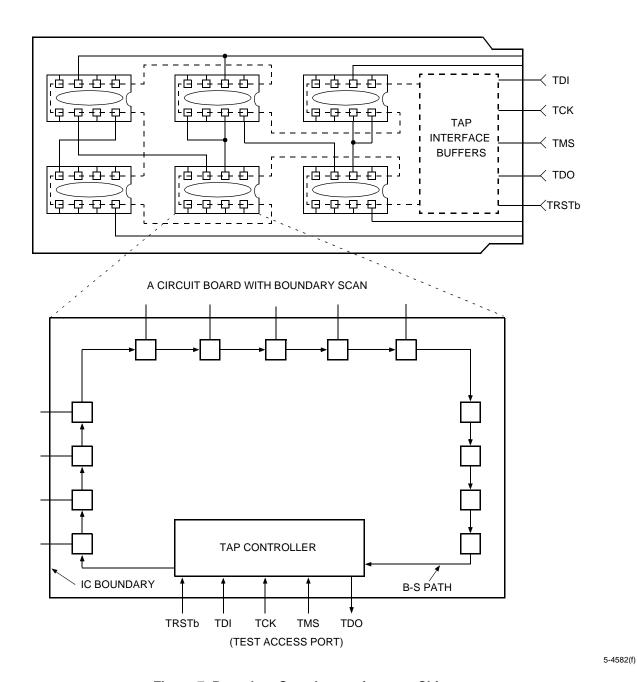

The LU5M31 is a full-scan device that is *IEEE* 1149.1 (JTAG) compliant providing support for built-in self-test (BIST) for automated memory testing.

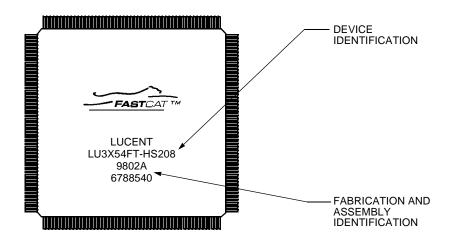

The device is designed in 0.35 µm CMOS and is packaged in a 208-pin SQFP.

Figure 1 illustrates the LU5M31 architecture.

#### **Features**

- 1 Gbit/s full-duplex Ethernet MAC integrated with separate transmit and receive port FIFOs:

- Adds a 1 Gbit/s uplink to existing 10/100 Mbits/s switches and routers.

- Supports ISO 8802.3 standard and IEEE\* 802.3z MAC parameters, repeater and management parameters for 1000 Mbits/s operation.

- IEEE 802.3x frame-based flow control.

#### Features (continued)

- Internal PCS layer including 8b/10b encoding/decoding provides 10b interface to an external transceiver including the ability to enable lock to reference and comma detection.

- GMII interface provides connectivity to 1000 base media access controllers and various PHYs.

- Autonegotiation used to advertise speed and duplex capability and to determine flow control symmetry.

- 64-bit bidirectional data bus.

- Host clock operates from 33 MHz to 66 MHz.

- Byte lane enables on each write to the LU5M31.

- Transmit and receive operations are under hardware control.

- CRC generation can be enabled on a per-frame basis while transmitting frames.

- CRC can be removed from receive frames before being read from the LU5M31.

- Programmable word count threshold determines burst size for FIFO read and write.

- Network management support through on-chip receive and transmit event counters.

- 33 MHz synchronous CPU interface with burst support for event counter reads.

- Event counters are based on the remote monitor (RMON) management information base (MIB) and Chapter 30 of IEEE 802.3u/IEEE 802.3z.

- Frame statistics are appended to every receive frame.

- Interrupt signal alerts the host of transmit and receive bus errors or CPU interface errors as well as event counter overflows.

- Separate 2048-byte transmit and 8192-byte receive FIFOs allow on-chip buffering of entire frame:

- Transmit and receive FIFOs can hold multiple frames.

- Independent thresholds allow filtering of undersized frames and fragments.

- Independent transmit thresholds allow host to set the number of words that must be written to the transmit FIFO before the transmission on the Ethernet starts.

- User-selectable watermarks control when flow control frames are transmitted by the LU5M31.

- Internal and external loopback support provides debug capability to the host.

- Internally generated random jitter test pattern capability

- Testability functions:

- JTAG boundary scan.

- Full internal scan.

- Built-in self test (BIST) for internal memories.

- 0.35 µm CMOS technology.

- 3.3 V power supply.

- 5 V input tolerance capability (uses separate supply).

- 208-pin SQFP package.

<sup>\*</sup> IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers, Inc.

## **Table of Contents**

| Contents                                                                  | Page |

|---------------------------------------------------------------------------|------|

| Overview                                                                  | 1    |

| Features                                                                  | 1    |

| Description                                                               | 6    |

| Architecture                                                              | 6    |

| Pin Information                                                           |      |

| Signal Configuration                                                      | 7    |

| Preliminary Pin Diagram                                                   | 8    |

| Signal Pins                                                               |      |

| Register Information                                                      |      |

| Register Address Map                                                      |      |

| Register Descriptions                                                     |      |

| Identification Register                                                   |      |

| Global Configuration Register                                             |      |

| Global FIFO Configuration Register                                        |      |

| Transmit Frame Configuration RegisterReceive Frame Configuration Register |      |

| One-Level VLAN Tag Register                                               | 20   |

| Two-Level VLAN Tag Register                                               |      |

| Source Address (SA) Register                                              |      |

| Transmit Pause Frame Timer Register                                       |      |

| Interrupt Identification Register                                         |      |

| Interrupt Mask Register                                                   |      |

| Interrupt Register                                                        |      |

| Receive Counter Interrupt Mask Register                                   |      |

| Receive Counter Interrupt Register                                        |      |

| Transmit Counter Interrupt Mask Register                                  |      |

| Transmit Counter Interrupt Register                                       | 36   |

| Receive Port Diagnostic Register                                          | 37   |

| GMII Control Register                                                     | 38   |

| GMII Status Register                                                      |      |

| Autonegotiation Advertisement Register                                    |      |

| Autonegotiation Link Partner Ability Base Page Register                   |      |

| Autonegotiation Expansion Register                                        |      |

| Autonegotiation Next Page Transmit Register                               |      |

| Autonegotiation Link Partner Ability Next Page Register                   |      |

| MII Data Register                                                         |      |

| MII Control Register                                                      |      |

| PCS Status RegisterFunctional Description                                 |      |

| Event Counters                                                            |      |

| Host Interface                                                            |      |

| Link Interface                                                            |      |

| Embedded Gigabit MAC                                                      |      |

| CPU Interface                                                             |      |

| Gigabit Management Interface                                              |      |

| Reset Operation                                                           |      |

| Circuit Board Manufacturing Testability                                   |      |

| Power Supply Considerations                                               | 67   |

| Absolute Maximum Ratings                                                  | 68   |

| Handling Precautions                                                      | 68   |

| Electrical Characteristics                                                | 68   |

| Timing Characteristics (Preliminary)                                      |      |

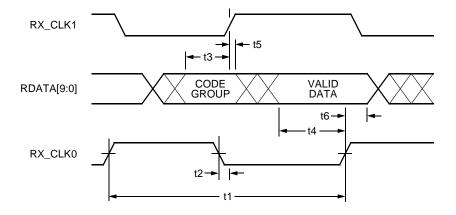

| PCS Receive Interface                                                     |      |

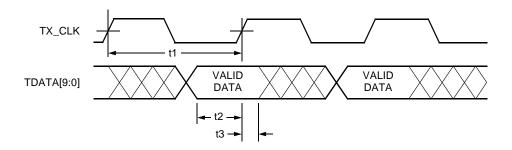

| PCS Transmit Interface                                                    |      |

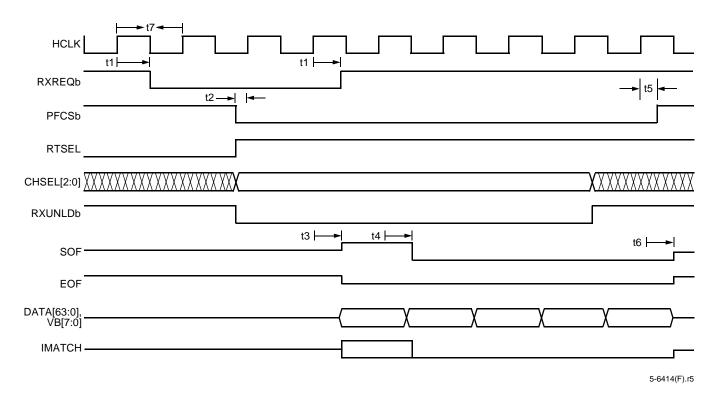

| Host Interface                                                            |      |

| CPU Timing                                                                |      |

| Outline Diagram                                                           |      |

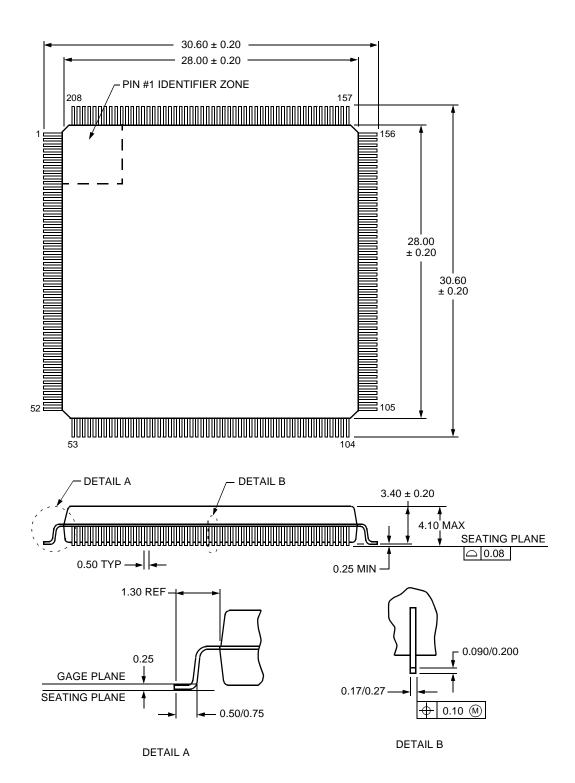

| 208-Pin SQFP Package Outline                                              |      |

| FASTCAT Ethernet IC Naming Convention                                     |      |

| Ordering Information                                                      |      |

## **Table of Contents** (continued)

| Tables                                                                            | Page |

|-----------------------------------------------------------------------------------|------|

| Table 1. LU5M31 Signals According to Pin Number in Numeric Sequence               | 9    |

| Table 2. LU5M31 Signals According to Pin Number in Alphanumeric Sequence          |      |

| Table 3. Physical Coding Sublayer (PCS) Signal Pins (3.3 V Only)                  | 11   |

| Table 4. Host Interface Signal Pins (3.3 V Only)                                  |      |

| Table 5. CPU Interface Pins (5.0 V Tolerant Inputs)                               |      |

| Table 6. Global Signal Pins (5.0 V Tolerant Inputs)                               |      |

| Table 7. JTAG Test Signal Pins (5.0 V Tolerant Inputs)                            |      |

| Table 8. Address Map                                                              |      |

| Table 9. Identification Register Bit Map                                          |      |

| Table 10. Global Configuration Register Bit Map, High Word                        |      |

| Table 11. Global Configuration Register Bit Map, Low Word                         |      |

| Table 12. Global Configuration Register Bit Definitions                           | 22   |

| Table 13. Global FIFO Configuration Register Bit Map, High Word                   |      |

| Table 14. Global FIFO Configuration Register Bit Map, Low Word                    |      |

| Table 15. Global FIFO Configuration Register Bit Definitions                      |      |

| Table 16. Transmit Frame Configuration Register Bit Map                           |      |

| Table 17. Transmit Frame Configuration Register Bit Definitions                   |      |

| Table 18. Receive Frame Configuration Register Bit Map                            |      |

| Table 19. Receive Frame Configuration Register Bit Definitions                    |      |

| Table 20. One-Level VLAN Tag Register Bit Map                                     |      |

| Table 21. Two-Level VLAN Tag Register Bit Map                                     |      |

| Table 22. SA Bit Map, Most Significant Word                                       |      |

| Table 23. SA Bit Map, Middle Significant Word                                     |      |

| Table 24. SA Bit Map, Least Significant Word                                      |      |

| Table 25. Transmit Pause Frame Timer Register Bit Map                             |      |

| Table 26. Transmit Pause Frame Timer Register Bit Definitions                     |      |

| Table 27. Interrupt Identification Register Bit Map                               |      |

| Table 28. Interrupt Identification Register Bit Definitions                       |      |

| Table 29. Interrupt Mask Register Bit Map                                         |      |

| Table 30. Interrupt Mask Register Bit Definitions                                 |      |

| Table 31. Interrupt Register Bit Map                                              |      |

| Table 32. Interrupt Register Bit Definitions                                      |      |

| Table 33. Receive Counter Interrupt Mask Register Bit Map, High Word              |      |

| Table 34. Receive Counter Interrupt Mask Register Bit Map, Low Word               |      |

| Table 35. Receive Counter Interrupt Mask Register Bit Definitions                 | 33   |

| Table 36. Receive Counter Interrupt Register Bit Map, High Word                   |      |

| Table 37. Receive Counter Interrupt Register Bit Map, Low Word                    |      |

| Table 38. Receive Counter Interrupt Register Bit Definitions                      |      |

| Table 39. Transmit Counter Interrupt Register Bit Map, High Word                  |      |

| Table 40. Transmit Counter Interrupt Register Bit Map, Low Word                   |      |

| Table 41. Transmit Counter Interrupt Register Bit Definitions                     | 35   |

| Table 42. Transmit Counter Interrupt Register Bit Map, High Word                  | 36   |

| Table 43. Transmit Counter Interrupt Register Bit Map, Low Word                   | 36   |

| Table 44. Transmit Counter Interrupt Register Bit Definitions                     | 36   |

| Table 45. Receive Port Diagnostic Register Bit Map                                | 37   |

| Table 46. Receive Port Diagnostic Register Bit Definitions                        | 37   |

| Table 47. GMII Control Register Bit Map                                           | 38   |

| Table 48. GMII Control Register Bit Definitions                                   | 38   |

| Table 49. GMII Status Register Bit Map                                            | 39   |

| Table 50. GMII Status Register Bit Definitions                                    |      |

| Table 51. Autonegotiation Advertisement Register Bit Map                          | 40   |

| Table 52. Autonegotiation Advertisement Register Bit Definitions                  |      |

| Table 53. Autonegotiation Link Partner Ability Base Page Register Bit Map         |      |

| Table 54. Autonegotiation Link Partner Ability Base Page Register Bit Definitions |      |

| Table 55. Autonegotiation Expansion Register Bit Map                              | 42   |

| Table 56. Autonegotiation Expansion Register Bit Definitions                      |      |

## Table of Contents (continued)

| Tables                                                                                             | Page |

|----------------------------------------------------------------------------------------------------|------|

| Table 57. Autonegotiation Next Page Transmit Register Bit Map                                      | 43   |

| Table 58. Autonegotiation Next Page Transmit Register Bit Definitions                              |      |

| Table 59. Autonegotiation Link Partner Ability Next Page Register Bit Map                          | 44   |

| Table 60. Autonegotiation Link Partner Ability Next Page Register Bit Definitions                  | 44   |

| Table 61. MII Data Register                                                                        |      |

| Table 62. MII Data Register Bit Descriptions (Address = 0x44)                                      |      |

| Table 63. MII Control Register Bit Map                                                             |      |

| Table 64. MII Control Register Bit Descriptions (Address = 0x46)                                   |      |

| Table 65. PCS Status Register Bit Map (Address = 0x48)                                             |      |

| Table 66. MII Control Register Bit Descriptions                                                    |      |

| Table 67. Valid Byte Reference                                                                     |      |

| Table 68. Padding Conditions                                                                       |      |

| Table 69. Big Endian Data Format                                                                   |      |

| Table 70. MII Management Interface Frame Format                                                    |      |

| Table 71. Absolute Maximum Ratings                                                                 |      |

| Table 72. Receive Bus ac Specifications                                                            |      |

| Table 73. Transmit Bus ac Specifications                                                           |      |

| Table 74. DMA Receive Timing                                                                       |      |

| Table 75. DMA Transmit Timing                                                                      |      |

| Table 76. Hardware Reset Timing Parameters  Table 77. CPU Timing Parameters                        |      |

| Figures                                                                                            | Page |

| Figure 1. LU5M31 Architecture                                                                      | 6    |

| Figure 2. LU5M31 Signal Group Configuration                                                        |      |

| Figure 3. LU5M31 Pinout—Top View                                                                   |      |

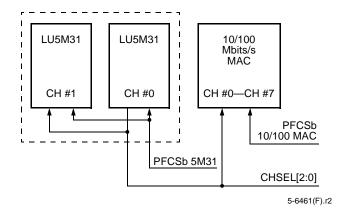

| Figure 4. Channel Assignment                                                                       |      |

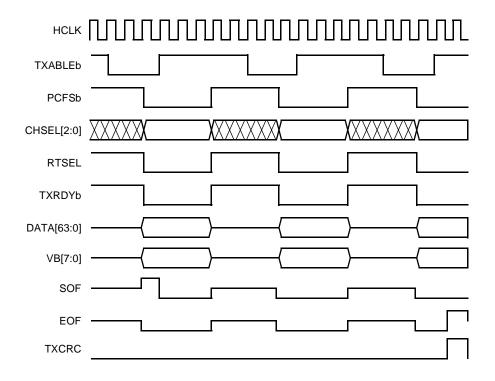

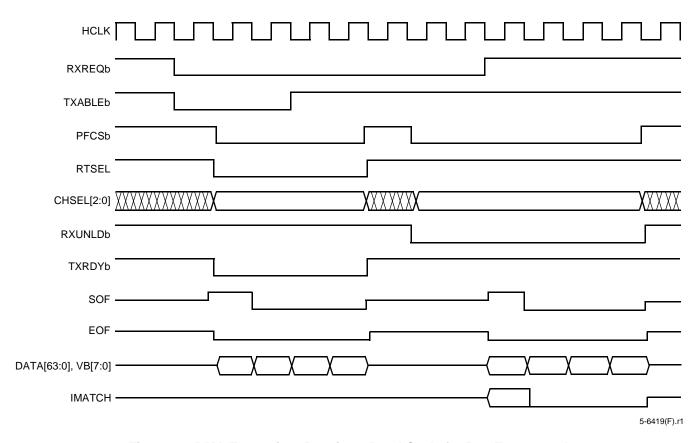

| Figure 5. TXWRITE: Timing Diagram for Write Procedure                                              |      |

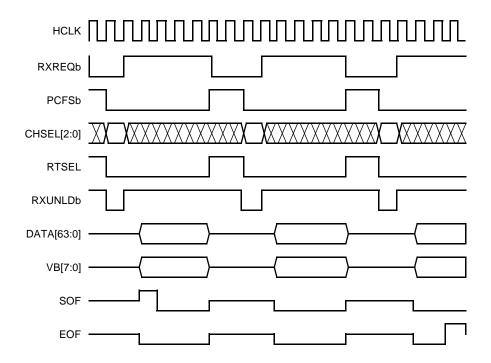

| Figure 6. RXREAD: Timing Diagram for Read Procedure                                                |      |

| Figure 7. Boundary-Scan Interaction on a Chip                                                      |      |

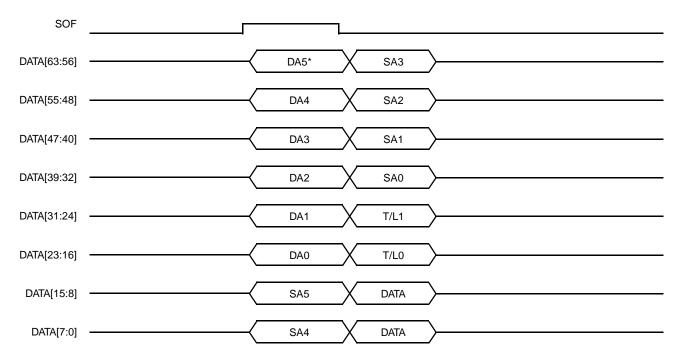

| Figure 8. Ethernet Frame Data First Byte Received or Transmitted                                   |      |

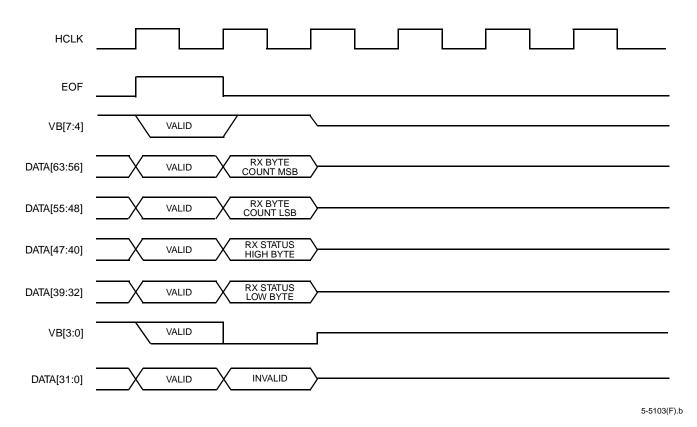

| Figure 9. Byte Order on Host Interface Data Bus During Receive Statistics                          |      |

| Figure 10. PCS Receive Interface Timing                                                            |      |

| Figure 11. PCS Transmit Interface Timing                                                           |      |

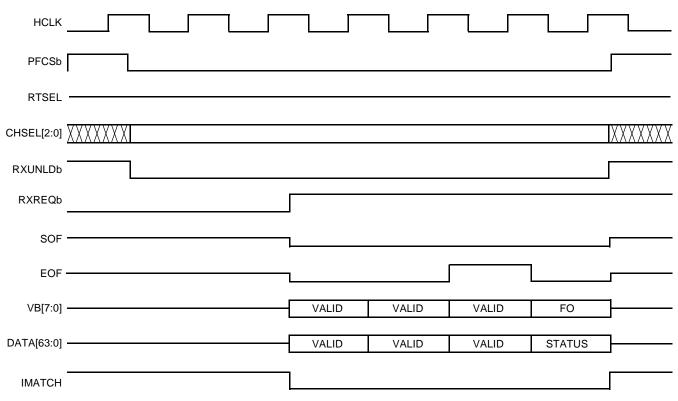

| Figure 12. DMA Receive Timing                                                                      |      |

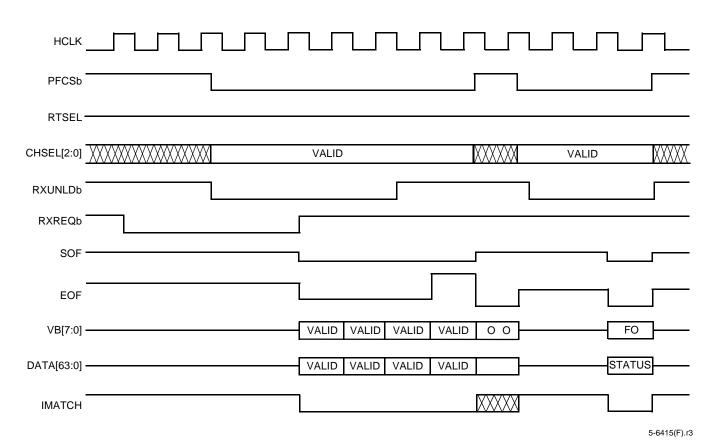

| Figure 13. DMA Receive with EOF on Lost Word of Burst                                              |      |

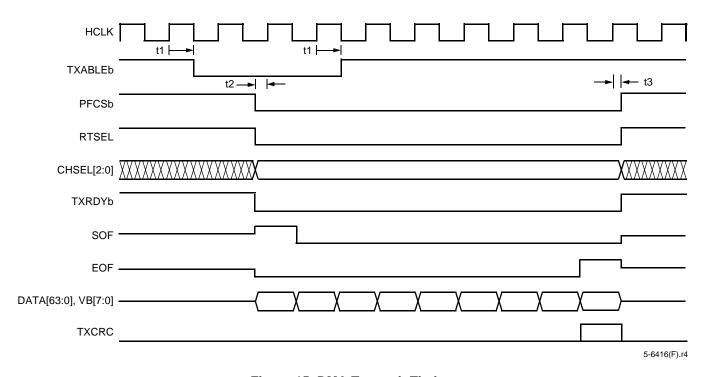

| Figure 14. DMA Receive with EOF on Last Word of Burst                                              |      |

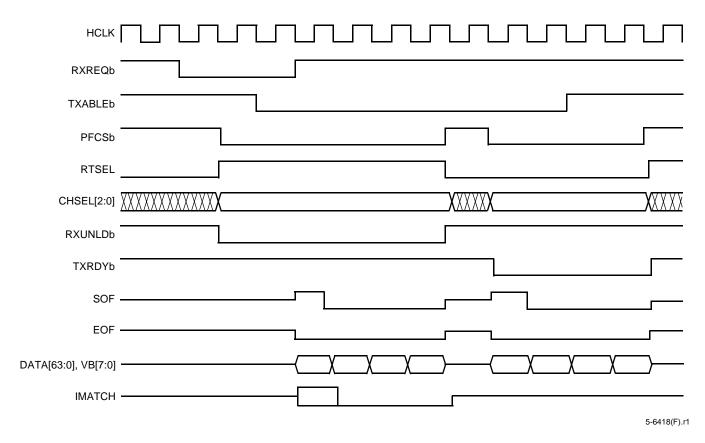

| Figure 15. DMA Transmit Timing  Figure 16. DMA Receive to Transmit 1 Dead Cycle for Bus Turnaround |      |

| Figure 17. DMA Transmit to Receive 1 Dead Cycle for Bus Turnaround                                 |      |

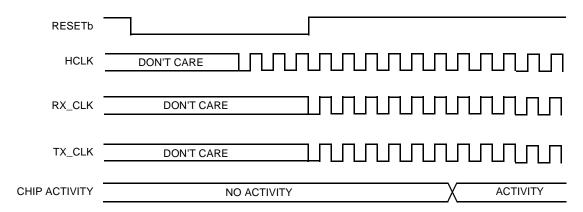

| Figure 18. DMA Hardware Reset Timing                                                               |      |

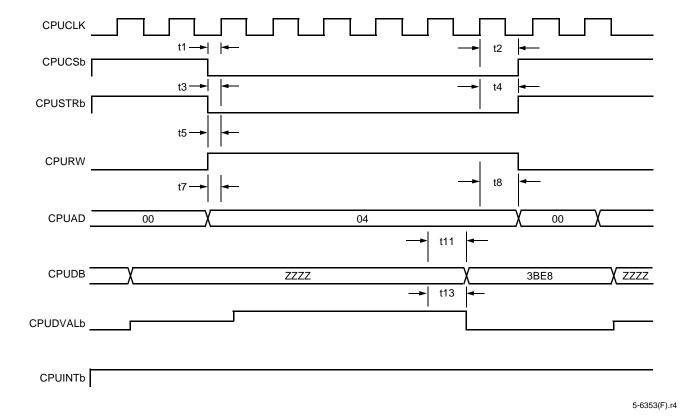

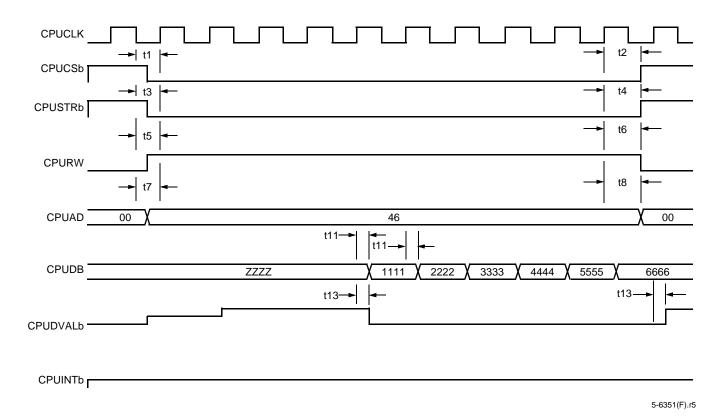

| Figure 19. Single Read                                                                             |      |

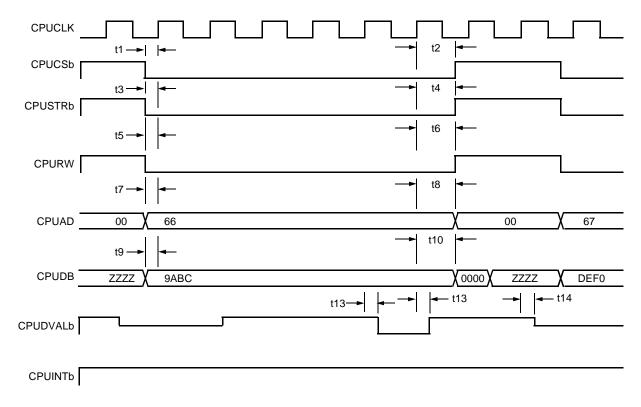

| Figure 20. 16-Bit Register/Counter Write                                                           |      |

| Figure 21. Burst Read                                                                              |      |

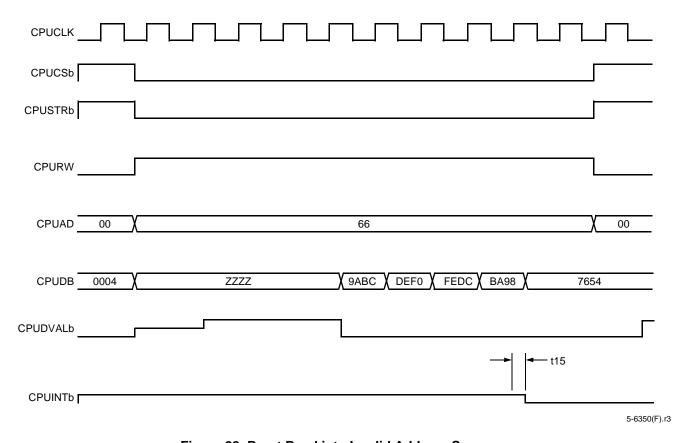

| Figure 22. Burst Read into Invalid Address Space                                                   |      |

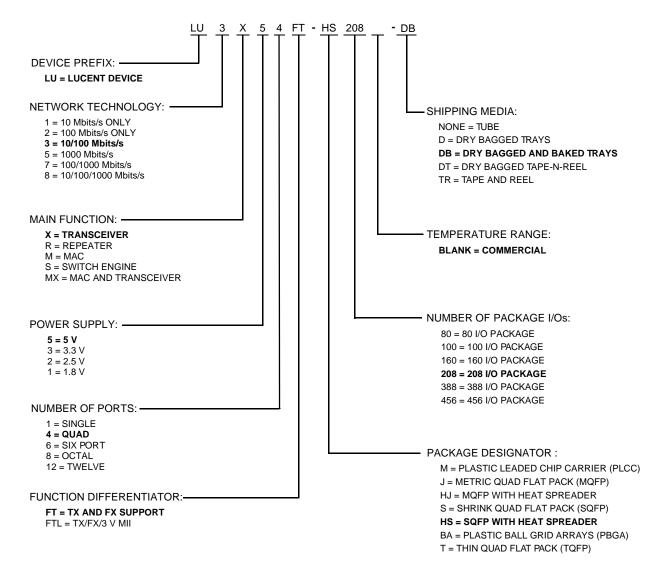

| Figure 23. Device Nomenclature: Codes and Definitions                                              |      |

| Figure 24. Top View of I/O Package                                                                 |      |

## **Description**

#### **Architecture**

5-6354(F).r5

Figure 1. LU5M31 Architecture

#### Pin Information

#### **Signal Configuration**

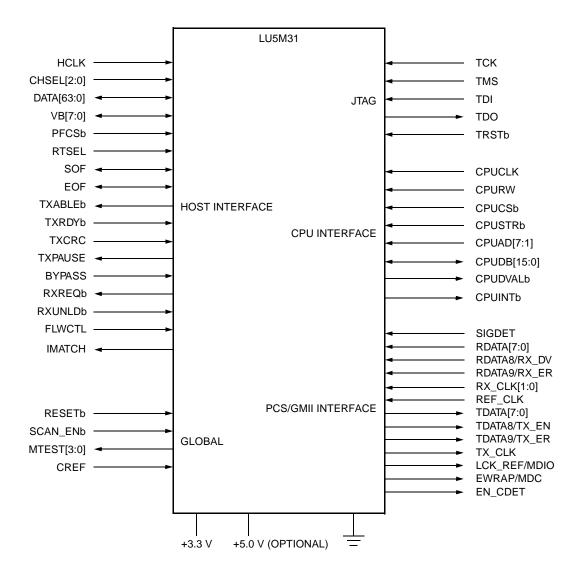

This section describes each LU5M31 signal and its function. Further information on these signals and how they interact can be found in the appropriate functional section of this data sheet.

Figure 2 shows the LU5M31 signal configuration. The signals are grouped into functional sections representing the primary interfaces on the device. The arrows shown indicate the signal's direction (input and/or output).

5-6300(F).r2

Figure 2. LU5M31 Signal Group Configuration

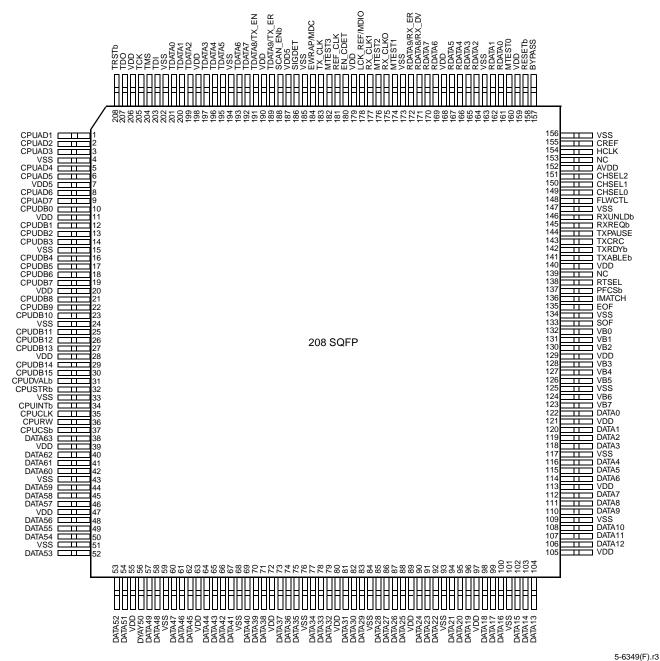

## **Preliminary Pin Diagram**

Figure 3. LU5M31 Pinout—Top View

Table 1. LU5M31 Signals According to Pin Number in Numeric Sequence

| Number | Name     | Number | Pin Name | Number | Name    | Number | Name           |

|--------|----------|--------|----------|--------|---------|--------|----------------|

| 1      | CPUAD1   | 55     | Vdd      | 109    | Vss     | 163    | Vss            |

| 2      | CPUAD2   | 56     | DATA50   | 110    | DATA9   | 164    | RDATA2         |

| 3      | CPUAD3   | 57     | DATA49   | 111    | DATA8   | 165    | RDATA3         |

| 4      | Vss      | 58     | DATA48   | 112    | DATA7   | 166    | RDATA4         |

| 5      | CPUAD4   | 59     | Vss      | 113    | VDD     | 167    | RDATA5         |

| 6      | CPUAD5   | 60     | DATA47   | 114    | DATA6   | 168    | Vdd            |

| 7      | VDD5     | 61     | DATA46   | 115    | DATA5   | 169    | RDATA6         |

| 8      | CPUAD6   | 62     | DATA45   | 116    | DATA4   | 170    | RDATA7         |

| 9      | CPUAD7   | 63     | Vdd      | 117    | Vss     | 171    | RDATA8/        |

| 10     | CPUDB0   | 64     | DATA44   | 118    | DATA3   | 171    | RX_DV          |

| 11     | VDD      | 65     | DATA43   | 119    | DATA2   | 172    | RDATA9/        |

| 12     | CPUDB1   | 66     | DATA42   | 120    | DATA1   |        | RX_ER          |

| 13     | CPUDB2   | 67     | DATA41   | 121    | VDD     | 173    | Vss            |

| 14     | CPUDB3   | 68     | Vss      | 122    | DATA0   | 174    | MTEST1         |

| 15     | Vss      | 69     | DATA40   | 123    | VB7     | 175    | RX_CLK0        |

| 16     | CPUDB4   | 70     | DATA39   | 124    | VB6     | 176    | MTEST2         |

| 17     | CPUDB5   | 71     | DATA38   | 125    | Vss     | 177    | RX_CLK1        |

| 18     | CPUDB6   | 72     | Vdd      | 126    | VB5     | 178    | LCK_REF/       |

| 19     | CPUDB7   | 73     | DATA37   | 127    | VB4     |        | MDIO           |

| 20     | VDD      | 74     | DATA36   | 128    | VB3     | 179    | VDD            |

| 21     | CPUDB8   | 75     | DATA35   | 129    | Vdd     | 180    | EN_CDET        |

| 22     | CPUDB9   | 76     | Vss      | 130    | VB2     | 181    | REF_CLK        |

| 23     | CPUDB10  | 77     | DATA34   | 131    | VB1     | 182    | MTEST3         |

| 24     | Vss      | 78     | DATA33   | 132    | VB0     | 183    | TX_CLK         |

| 25     | CPUDB11  | 79     | DATA32   | 133    | SOF     | 184    | EWRAP/         |

| 26     | CPUDB12  | 80     | Vdd      | 134    | Vss     |        | MDC            |

| 27     | CPUDB13  | 81     | DATA31   | 135    | EOF     | 185    | Vss            |

| 28     | VDD      | 82     | DATA30   | 136    | IMATCH  | 186    | SIGDET         |

| 29     | CPUDB14  | 83     | DATA29   | 137    | PFCSb   | 187    | VDD5           |

| 30     | CPUDB15  | 84     | Vss      | 138    | RTSEL   | 188    | SCAN_ENb       |

| 31     | CPUDVALb | 85     | DATA28   | 139    | NC      | 189    | TDATA9/        |

| 32     | CPUSTRb  | 86     | DATA27   | 140    | VDD     | 400    | TX_ER          |

| 33     | Vss      | 87     | DATA26   | 141    | TXABLEb | 190    | VDD<br>TDATA8/ |

| 34     | CPUINTb  | 88     | DATA25   | 142    | TXRDYb  | 191    | TX_EN          |

| 35     | CPUCLK   | 89     | Vdd      | 143    | TXCRC   | 192    | TDATA7         |

| 36     | CPURW    | 90     | DATA24   | 144    | TXPAUSE | 193    | TDATA6         |

| 37     | CPUCSb   | 91     | DATA23   | 145    | RXREQb  | 193    | Vss            |

| 38     | DATA63   | 92     | DATA22   | 146    | RXUNLDb | 195    | TDATA5         |

| 39     | VDD      | 93     | Vss      | 147    | Vss     | 195    | TDATA4         |

| 40     | DATA62   | 94     | DATA21   | 148    | FLWCTL  | 197    | TDATA3         |

| 41     | DATA61   | 95     | DATA20   | 149    | CHSEL0  | 198    | VDD            |

| 42     | DATA60   | 96     | DATA19   | 150    | CHSEL1  | 199    | TDATA2         |

| 43     | Vss      | 97     | VDD      | 151    | CHSEL2  | 200    | TDATA1         |

| 44     | DATA59   | 98     | DATA18   | 152    | AVDD    | 200    | TDATA1         |

| 45     | DATA58   | 99     | DATA17   | 153    | NC      | 202    | Vss            |

| 46     | DATA57   | 100    | DATA16   | 154    | HCLK    | 202    | TDI            |

| 47     | VDD      | 101    | Vss      | 155    | CREF    | 204    | TMS            |

| 48     | DATA56   | 102    | DATA15   | 156    | Vss     | 205    | TCK            |

| 49     | DATA55   | 103    | DATA14   | 157    | BYPASS  | 206    | VDD            |

| 50     | DATA54   | 104    | DATA13   | 158    | RESETb  | 207    | TDO            |

| 51     | Vss      | 105    | VDD      | 159    | VDD     | 208    | TRSTb          |

| 52     | DATA53   | 106    | DATA12   | 160    | MTEST0  | 200    | 11.010         |

| 53     | DATA52   | 107    | DATA11   | 161    | RDATA0  |        |                |

| 54     | DATA51   | 108    | DATA10   | 162    | RDATA1  |        |                |

Table 2. LU5M31 Signals According to Pin Number in Alphanumeric Sequence

| Number | Name             | Number   | Name             | Number | Name              | Number      | Pin Name   |

|--------|------------------|----------|------------------|--------|-------------------|-------------|------------|

| 152    | AVDD             | 87       | DATA26           | 160    | MTEST0            | 128         | VB3        |

| 157    | BYPASS           | 86       | DATA27           | 174    | MTEST1            | 127         | VB4        |

| 149    | CHSEL0           | 85       | DATA28           | 176    | MTEST2            | 126         | VB5        |

| 150    | CHSEL1           | 83       | DATA29           | 182    | MTEST3            | 124         | VB6        |

| 151    | CHSEL2           | 118      | DATA3            | 139    | NC                | 123         | VB7        |

| 1      | CPUAD1           | 82       | DATA30           | 153    | NC                | 11          | Vdd        |

| 2      | CPUAD2           | 81       | DATA31           | 137    | PFCSb             | 20          | VDD        |

| 3      | CPUAD3           | 79       | DATA32           | 161    | RDATA0            | 28          | VDD        |

| 5      | CPUAD4           | 78       | DATA33           | 162    | RDATA1            | 39          | VDD        |

| 6      | CPUAD5           | 77       | DATA34           | 164    | RDATA2            | 47          | VDD        |

| 8      | CPUAD6           | 75       | DATA35           | 165    | RDATA3            | 55          | VDD        |

| 9      | CPUAD7           | 74       | DATA36           | 166    | RDATA4            | 63          | VDD        |

| 35     | CPUCLK           | 73       | DATA37           | 167    | RDATA5            | 72          | Vdd        |

| 37     | CPUCSb           | 71       | DATA38           | 169    | RDATA6            | 80          | VDD        |

| 10     | CPUDB0           | 70       | DATA39           | 170    | RDATA7            | 89          | VDD        |

| 12     | CPUDB1           | 116      | DATA4            |        | RDATA8/           | 97          | VDD        |

| 23     | CPUDB10          | 69       | DATA40           | 171    | RX_DV             | 105         | VDD        |

| 25     | CPUDB11          | 67       | DATA41           |        | RDATA9/           | 113         | VDD        |

| 26     | CPUDB12          | 66       | DATA42           | 172    | RX_ER             | 121         | VDD        |

| 27     | CPUDB13          | 65       | DATA43           | 181    | REF_CLK           | 129         | VDD        |

| 29     | CPUDB14          | 64       | DATA44           | 158    | RESETb            | 140         | VDD        |

| 30     | CPUDB15          | 62       | DATA45           | 138    | RTSEL             | 159         | VDD        |

| 13     | CPUDB2           | 61       | DATA46           | 175    | RX_CLK0           | 168         | VDD        |

| 14     | CPUDB3           | 60       | DATA47           | 177    | RX_CLK1           | 179         | VDD        |

| 16     | CPUDB4           | 58       | DATA48           | 145    | RXREQb            | 190         | VDD        |

| 17     | CPUDB5           | 57       | DATA48<br>DATA49 | 146    | RXUNLDb           | 198         | VDD        |

| 18     | CPUDB6           | 115      | DATA49<br>DATA5  | 188    | SCAN_ENb          | 206         | VDD        |

| 19     | CPUDB7           | 56       | DATA50           | 186    | SIGDET            | 7           | VDD5       |

| 21     | CPUDB8           | 54       | DATA50<br>DATA51 | 133    | SOF               | 187         | VDD5       |

| 22     | CPUDB9           | 53       | DATA51<br>DATA52 | 205    | TCK               | 4           | VSS        |

| 31     | CPUDVALb         | 52       | DATA53           | 201    | TDATA0            | 15          | Vss        |

| 34     | CPUINTb          | 50       | DATA53<br>DATA54 | 200    | TDATA1            | 24          | Vss        |

| 36     | CPURW            | 49       | DATA54<br>DATA55 | 199    | TDATA2            | 33          | Vss        |

| 32     | CPUSTRb          | 48       | DATA56           | 197    | TDATA3            | 43          | Vss        |

| 155    | CREF             |          |                  | 196    | TDATA4            | 51          |            |

| 122    | DATA0            | 46<br>45 | DATA57<br>DATA58 | 195    | TDATA5            | 59          | Vss        |

| 120    | DATA0<br>DATA1   | 45       | DATA56           | 193    | TDATA6            | 68          | Vss<br>Vss |

|        |                  |          |                  | 192    | TDATA7            | <del></del> |            |

| 108    | DATA10           | 114      | DATA60           |        | TDATA8/           | 76<br>84    | Vss        |

| 107    | DATA11<br>DATA12 | 42       | DATA60<br>DATA61 | 191    | TX_EN             | 93          | Vss        |

|        |                  | 41       | DATA62           |        | TDATA9/           |             | Vss        |

| 104    | DATA13           | 40       |                  | 189    | TX_ER             | 101         | Vss        |

| 103    | DATA14           | 38       | DATA63           | 203    | TDI               | 109         | Vss        |

| 102    | DATA15           | 112      | DATA 7           | 207    | TDO               | 117         | Vss        |

| 100    | DATA16           | 111      | DATA8            | 204    | TMS               | 125         | Vss        |

| 99     | DATA 17          | 110      | DATA9            | 208    | TRSTb             | 134         | Vss        |

| 98     | DATA18           | 180      | EN_CDET          | 183    | TX_CLK            | 147         | Vss        |

| 96     | DATA19           | 135      | EOF              | 141    | TX_CLK<br>TXABLEb | 156         | Vss        |

| 119    | DATA2            | 184      | EWRAP/           | 141    | TXCRC             | 163         | Vss        |

| 95     | DATA20           |          | MDC              |        |                   | 173         | Vss        |

| 94     | DATA21           | 148      | FLWCTL           | 144    | TXPAUSE           | 185         | Vss        |

| 92     | DATA22           | 154      | HCLK             | 142    | TXRDYb            | 194         | Vss        |

| 91     | DATA23           | 136      | IMATCH           | 132    | VB0               | 202         | Vss        |

| 90     | DATA24           | 178      | LCK_REF/         | 131    | VB1               |             |            |

| 88     | DATA25           |          | MDIO             | 130    | VB2               |             |            |

## **Signal Pins**

The LU5M31 uses the signals listed in the following tables. Signal names ending in a lower case <b> are active-low signals. Signal type is designated as input (I), output (O), 3-state bidirectional (B), or power (PWR).

Table 3. Physical Coding Sublayer (PCS) Signal Pins (3.3 V Only)

| Pin          | Туре | Name/Description                                                                                                                                         |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_CLK       | 0    | Transmit Clock. 125 MHz transmit clock. TDATA[9:0] is driven by the LU5M31 on                                                                            |

|              |      | the rising edge of this clock.                                                                                                                           |

| TDATA[7:0]   | 0    | In PCS Mode:                                                                                                                                             |

| TDATA8/TX_EN |      | Transmit Data. The TDATA[9:0] outputs provide 10b code groups to the external                                                                            |

| TDATA9/TX_ER |      | Serdes. TDATA[9:0] is driven by the LU5M31 on the rising edge of TX_CLK.                                                                                 |

|              |      | Bypass PCS Mode:                                                                                                                                         |

|              |      | <b>Transmit Data.</b> The TDATA[7:0] outputs provide 8-bit wide data on each rising edge of TX_CLK to the external Gigabit PHY.                          |

|              |      | Transmit Enable. Transmit enable is an output of the LU5M31 that indicates a                                                                             |

|              |      | transmission is starting. This signal is asserted by the LU5M31 synchronously with                                                                       |

|              |      | the first byte of preamble, and it remains asserted while all bytes are transmited.                                                                      |

|              |      | TX_CLK following the transmission of the final byte of the frame. TX_EN is syn-                                                                          |

|              |      | chronous to TX_CLK.                                                                                                                                      |

|              |      | <b>Transmit Error.</b> TX_ER indicates that LU5M31 is requesting that the PHY transmit                                                                   |

|              |      | a coding error, as per Section 35.2.2.8                                                                                                                  |

| LCK_REF/MDIO | 0    | Lock PHY Clock. In PCS mode this signal mirrors lckref (bit 15 in the global con-                                                                        |

|              |      | figuration register) and allows the LU5M31 to drive the LCK_REF input to a serde's                                                                       |

|              |      | device. This signal will be high after reset.                                                                                                            |

|              |      | Management Data Input/Output. In bypass PCS mode MDIO is a bidirectional data signal used for reading status data and writing control data between the   |

|              |      | LU5M31 and a physical layer device. As an input or an output, MDIO is synchro-                                                                           |

|              |      | nous to MDC. An external 2 k $\Omega$ ± 5% pull-down resistor is required on this signal.                                                                |

| EWRAP/MDC    | 0    | PHY Loopback. In PCS mode this signal is asserted when external Loopback (bit                                                                            |

|              |      | 14 in the GMII control register) is set allowing the LU5M31 to drive the EWRAP                                                                           |

|              |      | input to a PHY. This signal will be low after reset.                                                                                                     |

|              |      | Management Data Clock. In bypass PCS mode MDC is sourced by the LU5M31                                                                                   |

|              |      | when the LU5M31 needs to read management status or write management control                                                                              |

|              |      | to the PHY. Data is read by the LU5M31 on the rising edge, and is driven by the                                                                          |

|              |      | LU5M31 on the falling edge of MDC when management registers are not being                                                                                |

|              |      | accessed. MDC is held low and MDIO is 3-stated. MDC is aperiodic, with a minimum low and high time of 160 ns. When SpeedSel=1. MDC frequency is HCLK/32. |

|              |      | When SpeedSel=0, MDC frequency is HCLK/16. When Fast_MDC is set, MDC fre-                                                                                |

|              |      | quency is HCLK/8, regardless of SpeedSel.                                                                                                                |

| EN_CDET      | 0    | Enable Comma Detect. This signal mirrors encomdet (bit 14 in the global config-                                                                          |

|              |      | uration register) and allows the LU5M31 to drive the EN_CDET input to a PHY.                                                                             |

|              |      | This signal will be high after reset.                                                                                                                    |

| RX_CLK[1:0]  | I    | Receive Clock. These recovered clocks are sourced by the PHY. RX_CLK[1:0] are                                                                            |

|              |      | 62.5 MHz clocks, 180 degrees out of phase. RX_CLK1 is used to clock even-code                                                                            |

|              |      | groups on RDATA[9:0], and RX_CLK0 is used to clock odd code groups on                                                                                    |

|              |      | RDATA[9:0]. In addition, RX_CLK[1] is the 125 MHz clock in the bypass PCS mode                                                                           |

|              |      | and is used to clock in RDATA[7:0].                                                                                                                      |

Table 3. Physical Coding Sublayer (PCS) Signal Pins (3.3 V Only) (continued)

| Pin                                        | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDATA[7:0]<br>RDATA8/RX_DV<br>RDATA9/RX_ER | ı    | In PCS Mode: Receive Data. The LU5M31 samples 10b code groups from the external PHY on the RDATA[9:0] pins. RDATA[9:0] are sampled by the LU5M31 on the rising edges of RX_CLK[1:0]. Bypass Mode: Receive Data. RDATA[7:0] is a bundle of eight data signals. Receive Data Valid. RX_DV is asserted by the PHY to indicate that recovered and decoded data bytes are valid on RXD. RX_DV remains asserted high from the first byte of receive data through to the final byte received. RX_DV is asserted synchronously to RX_CLK, and is deasserted prior to the first RX_CLK after the final byte is read. Receive Error. RX_ER is asserted by the PHY when it has detected an error that the LU5M31 may not be able to detect in the frame currently being received. RX_ER is asserted synchronously to RX_CLK. |

| REF_CLK                                    | I    | <b>Reference Clock.</b> This 125 MHz reference clock input is used by the LU5M31 to generate TX_CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SIGDET                                     | I    | <b>Signal Detect</b> . This signal provides an indication from the PHY that the PMD is detecting light when asserted. This signal should be pulled high on the board if not used. External pull-up recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 4. Host Interface Signal Pins (3.3 V Only)

| Pin        | Туре         | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYPASS     | I            | Phase-Locked Loop (PLL) Bypass. This signal is used to bypass the PLL. BYPASS should be low during normal operation.                                                                                                                                                                                                                                                                                                                                                    |

| HCLK       | I            | Host Clock. 33 MHz—66 MHz host clock. This clock is used to control the transfer of data between the host and the LU5M31, as well as providing a local clock within the LU5M31 to manage the host interface logic. All transfers on the host interface are synchronous to the rising edge of HCLK.                                                                                                                                                                      |

| CHSEL[2:0] | I            | Channel Select. These signals provide the host with a method to address a specific LU5M31 in a system via a port address. The value on this bus is compared to the value stored in the global configuration register to determine if the device is selected. This comparison can be disabled on receive or transmit by clearing rxchsel or txchsel (bits 8 and 9, respectively, in the global configuration register).                                                  |

| PFCSb      | I            | <b>LU5M31 Chip Select.</b> The LU5M31 chip select, when asserted low, is used to select the appropriate LU5M31 device.                                                                                                                                                                                                                                                                                                                                                  |

| RTSEL      | I            | <b>Receive-Transmit Select.</b> The receive-transmit select input determines the direction of the LU5M31 DATA[63:0] bus. When high, the LU5M31 DATA[63:0] bus is an output. When low, the DATA[63:0] bus is an input.                                                                                                                                                                                                                                                   |

| DATA[63:0] | B<br>3-state | <b>Data Bus.</b> The data bus is a 64-bit bidirectional bus. Data is transferred to and from the LU5M31 via the DATA[63:0] bus on the rising edge of HCLK. RTSEL qualifies the data bus as an input or output. The bus is in 3-state when a transfer is not in progress. External 10 k $\Omega$ pull-down resistors are recommended.                                                                                                                                    |

| VB[7:0]    | B<br>3-state | <b>Valid Bytes.</b> VB[7:0] is a bidirectional, 3-state bus used to indicate which byte lanes in a data transfer are valid. RTSEL qualifies VB[7:0] as an input or an output. VB[7:0] is in 3-state when the LU5M31 host bus is not enabled. External 10 k $\Omega$ pull-down resistors are recommended.                                                                                                                                                                |

| SOF        | B<br>3-state | <b>Start of Frame.</b> The start-of-frame signal indicates the start of a receive or transmit frame. While RTSEL is high (receive), SOF is an output and indicates that the current data transfer contains the first byte of a received frame. While RTSEL is low (transmit), SOF is an input and should be asserted high when the first word of a transmit frame is valid during the current data access. An external 10 k $\Omega$ pull-down resistor is recommended. |

| EOF        | B<br>3-state | <b>End of Frame.</b> The end-of-frame signal indicates the end of a receive or transmit frame. While RTSEL is high (receive), EOF is an output and indicates that the current data transfer contains the last byte of a received frame. While RTSEL is low (transmit), EOF is an input and should be asserted high when the last word of a transmit frame is written to the LU5M31. An external 10 k $\Omega$ pull-down resistor is recommended.                        |

| FLWCTL     | I            | <b>Flow Control</b> . Asserting this signal high will force the LU5M31 to transmit a MAC control frame that contains a valid PAUSE opcode and a preprogrammed number that represents the number of pause quantums the receiving station should pause for. This signal must be asserted for at least two HCLK cycles.                                                                                                                                                    |

| TXABLEb    | 0            | Host Transmit Request. The LU5M31 asserts this signal low when the transmit FIFO is capable of accepting data. When TXABLEb is asserted low, the available space in the transmit FIFO will be equal to or greater than the transmit word count threshold set in the global FIFO configuration register.                                                                                                                                                                 |

Table 4. Host Interface Signal Pins (3.3 V Only) (continued)

| Pin     | Туре         | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXRDYb  | I            | Host Transmit Ready. The LU5M31 clocks data into the transmit FIFO from the DATA[63:0] bus on the rising edge of HCLK while TXRDYb and RTSEL are low and the LU5M31 host bus is enabled.                                                                                                                                                                                                                                                                                                      |

| TXCRC   | I            | <b>Transmit CRC Checksum.</b> When asserted high, in conjunction with <b>hwcrc</b> (bit 2 of the transmit frame configuration register), this signal is used to inform the LU5M31 that a CRC checksum is to be calculated for the current frame and appended to the end of the frame prior to transmission. TXCRC must be asserted with EOF during a write to the LU5M31.                                                                                                                     |

| TXPAUSE | 0            | <b>Transmission Paused.</b> This signal is asserted high by the LU5M31 while the LU5M31 transmitter is paused due to reception of a valid MAC control frame with a PAUSE opcode.                                                                                                                                                                                                                                                                                                              |

| RXREQb  | 0            | <b>Receive Request</b> . RXREQb is asserted low when the receive threshold conditions (as defined in the global FIFO configuration register) have been met. The assertion of this signal indicates that data in the receive FIFO is available to be read by the host.                                                                                                                                                                                                                         |

| RXUNLDb | I            | Host Receive Unload. The host asserts this signal low to acknowledge a receive request from the LU5M31. When the host bus is enabled and this signal is asserted low, a burst read from the LU5M31 will start. The burst length will be equal to the burst size defined by the receive word count threshold.                                                                                                                                                                                  |

| IMATCH  | O<br>3-state | Address Match. The address match signal will be asserted high by the LU5M31 when the frame, currently being read from the receive FIFO, has a destination address that matches the Ethernet address loaded in the source address registers of the LU5M31. This signal will be asserted for one HCLK cycle with SOF if a match is made. This signal will not be asserted if the address in the source address register is 0x0000. An external 10 k $\Omega$ pull-down resistor is recommended. |

Table 5. CPU Interface Pins (5.0 V Tolerant Inputs)

| Pin         | Туре            | Name/Description                                                                                                                                                                                                                                                                                      |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUCLK      | I               | <b>CPU Clock.</b> 33 MHz CPU clock. This clock is used to control transfer of data between the LU5M31 and the CPU, as well as providing an internal clock for the CPU interface logic. All transfers on the CPU interface are synchronous to the rising edge of CPUCLK.                               |

| CPUCSb      | _               | <b>CPU Interface Chip Select</b> . This signal must be asserted low in order to access a register or counter in the LU5M31. All CPU accesses are qualified with CPUCSb. When CPUCSb is sampled high, the CPU data bus (CPUDB) will be in 3-state one CPU clock cycle later.                           |

| CPUSTRb     | I               | <b>CPU Strobe</b> . When asserted low, this signal initiates a CPU transaction. When deasserted high, this signal indicates the end of a CPU transaction.                                                                                                                                             |

| CPUAD[7:1]  | I               | <b>CPU Address Bus.</b> The address for the register or event counter being accessed is provided on this bus. All LU5M31 registers and event counters are 16-bit word aligned, irrespective of their size.                                                                                            |

| CPUDB[15:0] | B<br>3-state    | <b>CPU Data Bus</b> . Data is transferred to or from the LU5M31 registers or event counters via CPUDB[15:0]. The state of CPURW determines whether this bus is an input or an output. This bus is qualified with both CPUSTRb and CPUCSb. External 10 k $\Omega$ pull-down resistors are recommended. |

| CPURW       | I               | <b>CPU Read or Write</b> . This signal must be high for a read and low for a write and determines the direction of the CPU data bus.                                                                                                                                                                  |

| CPUDVALb    | O<br>3-state    | <b>CPU Data Valid</b> . For a read, CPUDVALb is asserted low while there is valid data being presented on the CPU data bus. For a write, CPUDVALb is asserted low for one CPUCLK cycle to indicate data has been registered by the LU5M31. An external 1 $k\Omega$ pull-up resistor is recommended.   |

| CPUINTb     | O<br>Open Drain | <b>CPU Interrupt.</b> The CPU interrupt is asserted low when any interrupt bit is asserted and not masked. This signal will remain asserted low until the interrupt register causing the interrupt is read. An external 1 k $\Omega$ pull-up resistor is recommended.                                 |

Table 6. Global Signal Pins (5.0 V Tolerant Inputs)

| Pin        | Туре                     | Name/Description                                                                                                                                                                                                                                                                                        |

|------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETb     | I                        | <b>Hardware Reset.</b> This signal, when asserted low, performs a complete asynchronous reset of the LU5M31, including the PLL. The LU5M31 will be functional 250 ms after the completion of reset (RESETb deasserted high).                                                                            |

| SCAN_ENb   | I<br>Internal<br>Pull-up | <b>Scan Enable.</b> While asserted low, this signal enables the shifting of data through scan chains when the associated scan clock is pulsed. While deasserted high, scan chain shifting is disabled and the device is in functional mode. This signal should be deasserted high for normal operation. |

| MTEST[3:0] | 0                        | <b>Factory Test</b> . These pins are used for factory test and should not be connected on a production board.                                                                                                                                                                                           |

| CREF       | I                        | PLL Reference Voltage. This pin provides the dc reference voltage for the PLL. This pin must be connected to ground through a 1.0 nF ± 10% capacitor.                                                                                                                                                   |

| Vdd        | PWR                      | 3.3 V Power.                                                                                                                                                                                                                                                                                            |

| AVdd       | PWR                      | 3.3 V Analog Power.                                                                                                                                                                                                                                                                                     |

| VDD5       | PWR                      | 5.0 V Power (Optional).                                                                                                                                                                                                                                                                                 |

| Vss        | PWR                      | Digital Ground.                                                                                                                                                                                                                                                                                         |

| NC         | _                        | No Connect. These pins should be left unconnected.                                                                                                                                                                                                                                                      |

**Table 7. JTAG Test Signal Pins (5.0 V Tolerant Inputs)**

| Pin   | Туре                     | Name/Description                                                                                                                                                    |

|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                          | Refer to IEEE 1149.1                                                                                                                                                |

| TCK   | I                        | <b>Test Clock</b> . This signal provides the clock for the test logic defined by the <i>IEEE</i> 1149.1 standard.                                                   |

| TMS   | I<br>Internal<br>Pull-up | <b>Test Mode Select</b> . This signal is decoded by the TAP controller to control test operations.                                                                  |

| TDI   | I<br>Internal<br>Pull-up | <b>Test Data Input</b> . Serial test instructions and data are received by the test logic through this signal.                                                      |

| TDO   | 0                        | <b>Test Data Output</b> . Serial data and instructions from the test logic are provided by this signal.                                                             |

| TRSTb | I                        | <b>Test Reset</b> . When asserted low, this signal provides an asynchronous reset of the TAP controller. This signal needs to be asserted low for normal operation. |

#### **Register Information**

#### **Register Address Map**

The LU5M31 has several configuration registers. These registers all reset to known default values that enable the LU5M31 to transmit and receive frames. These registers should be updated if the default configuration does not suit the needs of the host system. The LU5M31 resets to a default configuration. The registers are addressed in memory space through the LU5M31 CPU interface.

Configuration registers should only be written at device initialization or after a hardware reset (RESETb) or a global software reset. The **gsrst** bit (bit 3 set in the global configuration register) resets all registers, except the global configuration register, to their default values as shown in parenthesis in the Register Descriptions section. In general, they should not be updated while the LU5M31 is transmitting or receiving frames. Table 8 lists the address map for the LU5M31 registers.

Table 8. Address Map

| Address[7:0]     | Register/Event Counter                                  | Reset<br>Value | Read/Write<br>(R/W) |

|------------------|---------------------------------------------------------|----------------|---------------------|

| Configuration/St | atus Registers                                          | •              | •                   |

| 0x00             | Identification Register                                 | 0x0800         | R                   |

| 0x02             | Global Configuration Register, Low Word                 | 0xEB00         | R/W                 |

| 0x04             | Global Configuration Register, High Word                | 0x0000         | R/W                 |

| 0x06             | Global FIFO Configuration Register, Low Word            | 0x5558         | R/W                 |

| 0x08             | Global FIFO Configuration Register, High Word           | 0x3BE8         | R/W                 |

| 0x0A             | Transmit Frame Configuration Register                   | 0x005C         | R/W                 |

| 0x0C             | Receive Frame Configuration Register                    | 0x0020         | R/W                 |

| 0x0E             | One-level VLAN Tag Register                             | 0x0000         | R/W                 |

| 0x10             | Two-level VLAN Tag Register                             | 0x0000         | R/W                 |

| 0x12             | Source Address Register, Low Word                       | 0x0000         | R/W                 |

| 0x14             | Source Address Register, Middle Word                    | 0x0000         | R/W                 |

| 0x16             | Source Address Register, High Word                      | 0x0000         | R/W                 |

| 0x18             | Transmit Pause Frame Timer Register                     | 0x0000         | R/W                 |

| 0x1A             | Interrupt Identification Register                       | 0x0000         | R                   |

| 0x1C             | Interrupt Mask Register                                 | 0xFFE7         | R/W                 |

| 0x1E             | Interrupt Register                                      | 0x0000         | R                   |

| 0x20             | Receive Counter Interrupt Mask Register, Low Word       | 0xFFFF         | R/W                 |

| 0x22             | Receive Counter Interrupt Mask Register, High Word      | 0xFFFF         | R/W                 |

| 0x24             | Receive Counter Interrupt Register, Low Word            | 0x0000         | R                   |

| 0x26             | Receive Counter Interrupt Register, High Word           | 0x0000         | R                   |

| 0x28             | Transmit Counter Interrupt Mask Register, Low Word      | 0xFFFF         | R/W                 |

| 0x2A             | Transmit Counter Interrupt Mask Register, High Word     | 0xFFFF         | R/W                 |

| 0x2C             | Transmit Counter Interrupt Register, Low Word           | 0x0000         | R                   |

| 0x2E             | Transmit Counter Interrupt Register, High Word          | 0x0000         | R                   |

| 0x30             | Receive Port Diagnostic Register                        | 0x0000         | R                   |

| 0x32             | GMII Control Register                                   | 0x0120         | R/W                 |

| 0x34             | GMII Status Register                                    | 0x0009         | R                   |

| 0x36             | Autonegotiation Advertisement Register                  | 0x01A0         | R/W                 |

| 0x38             | Autonegotiation Link Partner Ability Base Page Register | 0x0000         | R                   |

| 0x3A             | Autonegotiation Expansion Register                      | 0x0004         | R                   |

| 0x3C             | Autonegotiation Next Page Transmit Register             | 0x0000         | R/W                 |

| 0x3E             | Autonegotiation Link Partner Ability Next Page Register | 0x0000         | R                   |

| 0x40—0x42        | Reserved                                                | _              | _                   |

| 0x44             | MII Data Register                                       | 0x0000         | R/W                 |

## Register Information (continued)

Table 8. Address Map (continued)

| Address[7:0]     | Register/Event Counter                                      | Reset<br>Value | Read/Write<br>(R/W) |

|------------------|-------------------------------------------------------------|----------------|---------------------|

| 0x46             | MII Control Register                                        | 0x0000         | R/W                 |

| Configuration/St | atus Registers (continued)                                  |                |                     |

| 0x48             | PCS Data Register                                           | 0x0000         | R                   |

| 0x4A—0x4E        | Reserved                                                    | _              | _                   |

| Transmit Event ( | Counters                                                    | •              |                     |

| 0x50             | Frames Transmitted (64 Octets), Low Word                    | 0x0000         | R/W                 |

| 0x52             | Frames Transmitted (64 Octets), Middle Word                 | 0x0000         | R/W                 |

| 0x54             | Frames Transmitted (64 Octets), High Word                   | 0x0000         | R/W                 |

| 0x56             | Frames Transmitted (65 to 127 Octets), Low Word             | 0x0000         | R/W                 |

| 0x58             | Frames Transmitted (65 to 127 Octets), Middle Word          | 0x0000         | R/W                 |

| 0x5A             | Frames Transmitted (65 to 127 Octets), High Word            | 0x0000         | R/W                 |

| 0x5C             | Frames Transmitted (128 to 255 Octets), Low Word            | 0x0000         | R/W                 |

| 0x5E             | Frames Transmitted (128 to 255 Octets), High Word           | 0x0000         | R/W                 |

| 0x60             | Frames Transmitted (256 to 511 Octets), Low Word            | 0x0000         | R/W                 |

| 0x62             | Frames Transmitted (256 to 511 Octets), High Word           | 0x0000         | R/W                 |

| 0x64             | Frames Transmitted (512 to 1023 Octets), Low Word           | 0x0000         | R/W                 |

| 0x66             | Frames Transmitted (512 to 1023 Octets), High Word          | 0x0000         | R/W                 |

| 0x68             | Frames Transmitted (1024 to maximum size octets), Low Word  | 0x0000         | R/W                 |

| 0x6A             | Frames Transmitted (1024 to maximum size octets), High Word | 0x0000         | R/W                 |

| 0x6C             | Long Frames Transmitted, Low Word                           | 0x0000         | R/W                 |

| 0x6E             | Long Frames Transmitted, High Word                          | 0x0000         | R/W                 |

| 0x70             | Total Good Frames Transmitted, Low Word                     | 0x0000         | R/W                 |

| 0x72             | Total Good Frames Transmitted, Middle Word                  | 0x0000         | R/W                 |

| 0x74             | Total Good Frames Transmitted, High Word                    | 0x0000         | R/W                 |

| 0x76             | MAC Pause Frames Transmitted                                | 0x0000         | R/W                 |

| 0x78             | Multicast Frames Transmitted, Low Word                      | 0x0000         | R/W                 |

| 0x7A             | Multicast Frames Transmitted, High Word                     | 0x0000         | R/W                 |

| 0x7C             | Broadcast Frames Transmitted, Low Word                      | 0x0000         | R/W                 |

| 0x7E             | Broadcast Frames Transmitted, High Word                     | 0x0000         | R/W                 |

| 0x80             | Total Octets Transmitted, Low Word                          | 0x0000         | R/W                 |

| 0x82             | Total Octets Transmitted, Middle Word                       | 0x0000         | R/W                 |

| 0x84             | Total Octets Transmitted, High Word                         | 0x0000         | R/W                 |

| 0x86             | Transmit Underruns                                          | 0x0000         | R/W                 |

| Receive Event C  | ounters                                                     | · ·            | 1                   |

| 0x88             | Frames Received (64 Octets), Low Word                       | 0x0000         | R/W                 |

| 0x8A             | Frames Received (64 Octets), Middle Word                    | 0x0000         | R/W                 |

| 0x8C             | Frames Received (64 Octets), High Word                      | 0x0000         | R/W                 |

| 0x8E             | Frames Received (65 to 127 Octets), Low Word                | 0x0000         | R/W                 |

| 0x90             | Frames Received (65 to 127 Octets), Middle Word             | 0x0000         | R/W                 |

| 0x92             | Frames Received (65 to 127 Octets), High Word               | 0x0000         | R/W                 |

| 0x94             | Frames Received (128 to 255 Octets), Low Word               | 0x0000         | R/W                 |

| 0x96             | Frames Received (128 to 255 Octets), High Word              | 0x0000         | R/W                 |

| 0x98             | Frames Received (256 to 511 Octets), Low Word               | 0x0000         | R/W                 |

| 0x9A             | Frames Received (256 to 511 Octets), High Word              | 0x0000         | R/W                 |

| 0x9C             | Frames Received (512 to 1023 Octets), Low Word              | 0x0000         | R/W                 |

## Register Information (continued)

Table 8. Address Map (continued)

| Address[7:0]    | Register/Event Counter                                   | Reset<br>Value | Read/Write<br>(R/W) |  |

|-----------------|----------------------------------------------------------|----------------|---------------------|--|

| 0x9E            | Frames Received (512 to 1023 Octets), High Word          | 0x0000         | R/W                 |  |

| 0xA0            | Frames Received (1024 to maximum size octets), Low Word  | 0x0000         | R/W                 |  |

| Receive Event C | counters (continued)                                     | l.             | •                   |  |

| 0xA2            | Frames Received (1024 to maximum size octets), High Word | 0x0000         | R/W                 |  |

| 0xA4            | Long Frames Received, Low Word                           | 0x0000         | R/W                 |  |

| 0xA6            | Long Frames Received, High Word                          | 0x0000         | R/W                 |  |